# Design Guide: TIDA-070001 3- to 7-V<sub>IN</sub>, Space-Grade Point-of-Load (POL) Reference Design with Redundant eFuse Inputs for OCP

# Texas Instruments

# Description

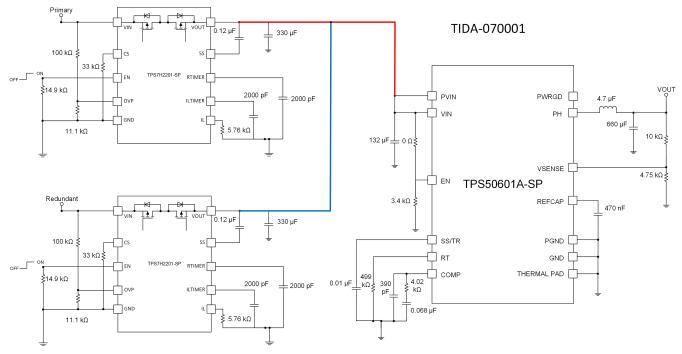

Redundancy is often employed in spacecraft applications to enhance reliability, this reference design shows how redundancy can be implemented at the input of a Point-of-Load (POL) supply using two TPS7H2201-SP radiation hardened eFuse load switches. Using two load switches allows for a primary and redundant voltage to be supplied to the rad hardened POL step-down converter TPS50601A-SP, the load switch provides an adjustable over-current protection (OCP) limit for protection along with a current sense ouput pin allows for monitoring and protection, the load switch also features adjustable over-voltage protection (OVP). The POL converter also has a current limit providing additional protection to shorts.

### Features

- Adjustable over-current protection (OCP) limit

- Adjustable over-voltage (OVP) limit

- Redundant inputs

- Configurable soft start

- Enable/disable functionality

# Applications

- · Command and data handling

- Satellite electric power system (EPS)

- Optical imaging payload

- Radar imaging payload

- Communications payload

### Resources

| TIDA-070001  |  |

|--------------|--|

| TPS7H2201-SP |  |

| TPS50601A-SP |  |

Design Files Product Folder Product Folder

ASK Our E2E<sup>™</sup> Experts

1

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

#### **System Description** 1

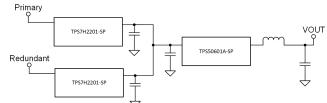

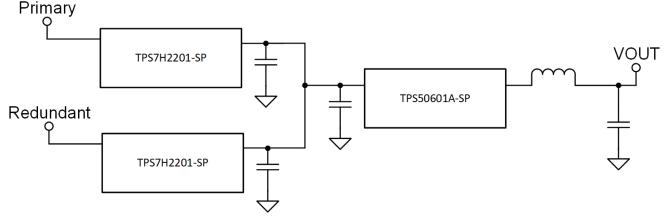

The design consists of two TPS7H2201-SP load switches supplying input power for a TPS50601A-SP point of load converter in a redundancy configuration. The redundancy of the input voltage to the point of load converter is critical in keeping important power lines to high priority parts of a satellite such as an FPGA or microcontroller functioning.

#### 1.1 **Key System Specifications**

| PARAMETER                       | OPERATING<br>SPECIFICATIONS | MAXIMUM SPECIFICATIONS                        | DETAILS       |

|---------------------------------|-----------------------------|-----------------------------------------------|---------------|

| Input power supply              | 0 to 5 VDC                  | 0 to 7 VDC                                    | Section 3.1.1 |

| Input current requirement       | 0 to 3.5 A                  | 0 to 7.5 A (set by load switch current limit) | Section 3.1.1 |

| Output voltage of POL converter | 2.5 VDC                     | 2.5 VDC                                       | Section 3.1.1 |

| Output current of POL converter | 0 to 6 A                    | 0 to 13 A (set by POL current limit)          | Section 3.1.1 |

| Operating temperature           | 25°C                        | –55°C to 125°C                                | Section 3.1.1 |

### Table 1. Key System Specifications

# 2 System Overview

# 2.1 Block Diagram

# 2.2 Design Considerations

When using the TPS7H2201-SP as a current limiting load switch, the current limit must be calculated based on the duty cycle and efficiency of the TPS50601A-SP. Since the load switch is limiting the input and not the output current for the load switch, the input current will heavily depend on the duty cycle and efficiency of the converter. The output voltage of the TPS7H2201-SP will degrade slowly after the TPS50601A-SP turns off. The TPS50601A-SP has a minimum input voltage of 3 V. When the output voltage of the TPS7H2201-SP is below 3 V and disabled, the TPS50601A-SP will stop lowering the voltage and the charge stored on those capacitors will very slowly decrease. Enabling the TPS7H2201-SP during this time may result in the TPS50601A-SP turning on faster than anticipated.

# 2.3 Highlighted Products

### 2.3.1 TPS7H2201-SP

- Radiation Performance:

- Radiation Hardness Assurance (RHA) up to TID 100 krad(Si)

- Single Event Latch-up (SEL), Single Event Burnout (SEB), and Single Event Gate Rupture (SEGR) Immune to LET = 75 MeV-cm<sup>2</sup>/mg

- SEFI Immune to LET = 65 MeV-cm<sup>2</sup>/mg

- SET Characterized to LET = 65 MeV-cm<sup>2</sup>/mg

- Integrated Single Channel Load Switch

- Input Voltage Range: 1.5 V to 7 V

- Low On-Resistance ( $R_{ON}$ ) of 34-m $\Omega$  Maximum at 25°C and VIN = 5 V

- 6-A Maximum Continuous Switch Current

- Low Control Input Threshold Enables Use of 1.2-V, 1.8-V, 2.5-V, and 3.3-V Logic

- Configurable Rise Time (Soft Start)

- Reverse Current Protection (TPS7H2201-SP)

- Programmable and Internal Current Limiting (FastTrip)

- Programmable Fault Timer (Current Limit and Retry Modes)

- Thermal Shutdown

- Ceramic Package With Thermal Pad

Texas STRUMENTS

www.ti.com

System Overview

#### 2.3.2 **TPS50601A-SP**

- Radiation Performance:

- Radiation Hardened up to TID 100 krad(Si)

- ELDRS Free 100 krad(Si) to 10 mrad(Si)/s

- Single Event Latch-up (SEL) Immune to LET = 75 MeV-cm<sup>2</sup>/mg

- SEB and SEGR Immune to 75 MeV-cm<sup>2</sup>/mg, SOA Curve Available

- SET/SEFI Cross-Section Plot Available

- Peak Efficiency: 96.6% (VO = 3.3 V)

- Integrated 58-m $\Omega$ /50-m $\Omega$  MOSFETs

- Power Rail: 3 V to 7 V on VIN

- 6-A Maximum Output Current

- Flexible Switching Frequency Options:

- 100-kHz to 1-MHz Adjustable Internal Oscillator

- External Sync Capability: 100 kHz to 1 MHz

- Sync Pin Can Be Configured as a 500-kHz Output for Master/Slave Applications

- 0.804-V ±1.5% Voltage Reference Overtemperature, Radiation, and Line and Load Regulation

- Monotonic Start-Up Into Prebiased Outputs

- Adjustable Soft Start Through External Capacitor

- Input Enable and Power-Good Output for Power Sequencing

- Power-Good Output Monitor for Undervoltage and Overvoltage

- Adjustable Input Undervoltage Lockout (UVLO)

- 20-Pin Ultra-Small, Thermally-Enhanced Ceramic Flatpack Package (HKH) for Space Applications ٠

#### 2.4 System Design Theory

The TPS7H2201-SP is a smart power load switch that allows multiple input voltages to supply the same TPS50601A-SP allowing for redundancy in input power supplies. The redundancy allows for a high reliability power supply for critical power rails. The TPS7H2201-SP also allows for current sensing of the input voltage of the TPS50601A-SP for monitoring the health of the power supply.

Copyright © 2018–2019, Texas Instruments Incorporated

# 3 Hardware, Software, Testing Requirements, and Test Results

# 3.1 Required Hardware and Software

### 3.1.1 Hardware

Two power supplies are needed to provide voltage to the TPS7H2201-SP, up to 7 V, which is the maximum voltage for the load switch. The power supplies in the following test setup need to supply up to 7.5 A of current set by the IL resistor of the individual load switches. The output load needs to be able to sink up to 13 A from the TPS50601A-SP when the device output is shorted. The TPS50601A-SP was set to an output of 2.5-V nominal. The surrounding temperature will be determined by the thermal maximum of the TPS50601A-SP and the TPS7H2201-SP, which have a temperature range of –55°C to 125°C.

#### 3.2 Testing and Results

#### 3.2.1 **Test Setup**

6

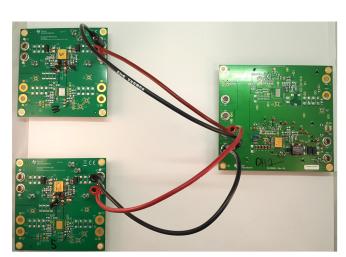

Tests were done with the following configuration, unless otherwise specified.

Figure 2. Test Setup

The tests were done with the following inputs/outputs, unless otherwise specified.

| PARAMETER                        | SPECIFICATIONS |

|----------------------------------|----------------|

| Input power supply               | 5 VDC          |

| Output voltage                   | 2.5 VDC        |

| Output current                   | 6 A            |

| Operating temperature            | 25°C           |

| LSW EN threshold                 | 4.85 V         |

| LSW OVP threshold                | 6 V            |

| LSW current limit, IL            | 7.5 A          |

| LSW current limit timer, ILTIMER | 1 ms           |

| LSW retry timer, RTIMER          | 1 ms           |

| LSW soft start                   | 9 ms           |

| LSW maximum CS pin voltage       | 4.6 V          |

| POL soft start                   | 4 ms           |

| POL UVLO threshold               | 2.75 V         |

**Table 2. Key System Specifications**

Hardware, Software, Testing Requirements, and Test Results

# www.ti.com

# 3.2.2 Test Results

# 3.2.2.1 Leakage Current

Current flowing through disabled load switch was measured at no load and full load.

| TEST DONE                                                              | RESULT  |

|------------------------------------------------------------------------|---------|

| Leakage current of disabled load switch with no load on POL converter  | 1.6 µA  |

| Leakage current of disabled load switch with 6-A load on POL converter | 0.75 µA |

| Operating temperature                                                  | 25°C    |

### Table 3. Test Data

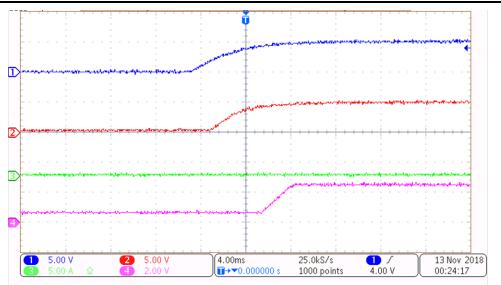

# 3.2.2.2 Start-up

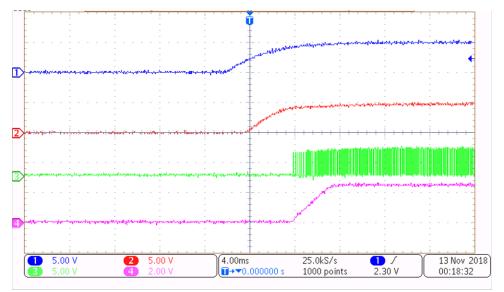

# Figure 3. Start-up Waveform Full Load With Phase Node

# Table 4. Waveforms for Figure 3

| Waveform Number | Signal                          | Values                                 |

|-----------------|---------------------------------|----------------------------------------|

| 1               | Input Voltage to Load Switch    | 0 to 5 V                               |

| 2               | Output Voltage of Load Switch   | 0 to 5 V                               |

| 3               | Phase Node of POL Converter     | 0 to 5 V @ 100-kHz Switching Frequency |

| 4               | Output Voltage of POL Converter | 0 to 2.5 V                             |

Figure 4. Start-up Waveform Full Load With Output Current

For the tests in Figure 3 and Figure 4, the input power to the load switch was ramped up with the load switch and the POL converter enabled. 6 A of current was drawn from the output of the POL converter.

#### Table 5. Waveforms for Figure 4

| Waveform Number | Signal                          | Values     |

|-----------------|---------------------------------|------------|

| 1               | Input Voltage to Load Switch    | 0 to 5 V   |

| 2               | Output Voltage of Load Switch   | 0 to 5 V   |

| 3               | Output Current of POL Converter | 0 to 6 A   |

| 4               | Output Voltage of POL Converter | 0 to 2.5 V |

Hardware, Software, Testing Requirements, and Test Results

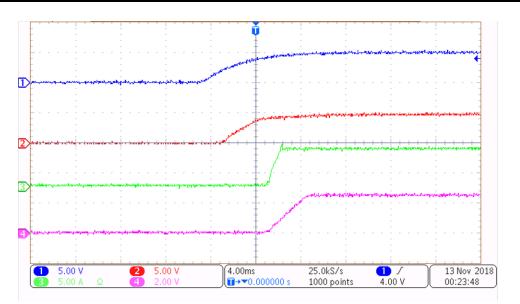

Figure 5. Start-up Waveform No Load With Phase Node

# Table 6. Waveforms for Figure 5

| Waveform Number | Signal                          | Values                                 |

|-----------------|---------------------------------|----------------------------------------|

| 1               | Input Voltage to Load Switch    | 0 to 5 V                               |

| 2               | Output Voltage of Load Switch   | 0 to 5 V                               |

| 3               | Phase Node of POL Converter     | 0 to 5 V @ 100-kHz Switching Frequency |

| 4               | Output Voltage of POL Converter | 0 to 2.5 V                             |

Hardware, Software, Testing Requirements, and Test Results

Figure 6. Start-up Waveform No Load With Output Current Node

For the tests in Figure 5 and Figure 6, the input power to the load switch was ramped up with the load switch and the POL converter enabled. 0 A of current was drawn from the output of the POL converter.

# Table 7. Waveforms for Figure 6

| Waveform Number | Signal                          | Values     |

|-----------------|---------------------------------|------------|

| 1               | Input Voltage to Load Switch    | 0 to 5 V   |

| 2               | Output Voltage of Load Switch   | 0 to 5 V   |

| 3               | Output Current of POL Converter | 0 A        |

| 4               | Output Voltage of POL Converter | 0 to 2.5 V |

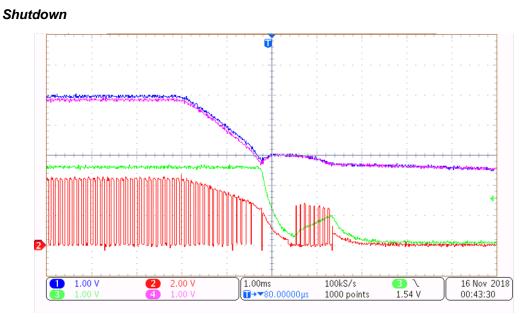

3.2.2.3

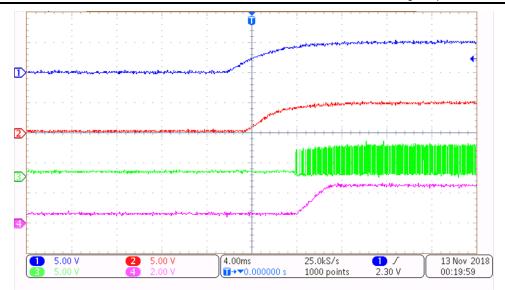

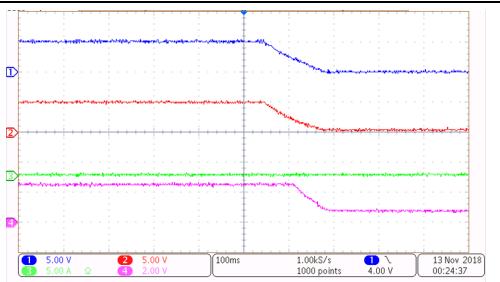

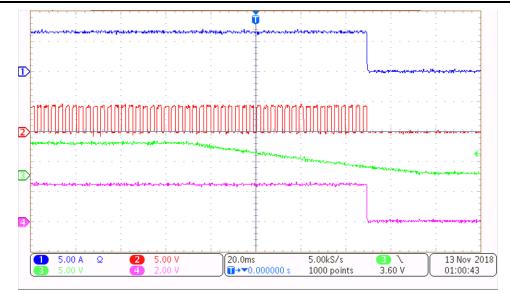

Figure 7. Shutdown Waveform Full Load With Phase Node

# Table 8. Waveforms for Figure 7

| Waveform Number | Signal                          | Values                                 |

|-----------------|---------------------------------|----------------------------------------|

| 1               | Input Voltage to Load Switch    | 5 to 2.5 V                             |

| 2               | Phase Node of POL Converter     | 0 to 5 V @ 100-kHz Switching Frequency |

| 3               | Output Voltage of POL Converter | 2.5 to 0 V                             |

| 4               | Output Voltage of Load Switch   | 5 to 2.5 V                             |

#### Hardware, Software, Testing Requirements, and Test Results

Figure 8. Shutdown Waveform Full Load With Output Current

For the test in Figure 7 and Figure 8, the input power to the load switch was ramped down. 6 A of current was drawn from the output of the POL converter using a resistive load. The input voltage of the POL converter dips below the UVLO and the device starts to turn off. The input voltage of the POL converter then starts to increase because of the large dip in output current. This increase causes the POL to switch a few times and discharge capacitors on the input of the POL converter.

#### Table 9. Waveforms for Figure 8

| Waveform Number | Signal                          | Values     |

|-----------------|---------------------------------|------------|

| 1               | Input Voltage to Load Switch    | 5 to 2.5 V |

| 2               | Output Current of POL Converter | 6 to 0 A   |

| 3               | Output Voltage of POL Converter | 2.5 to 0 V |

| 4               | Output Voltage of Load Switch   | 5 to 2.5 V |

Hardware, Software, Testing Requirements, and Test Results

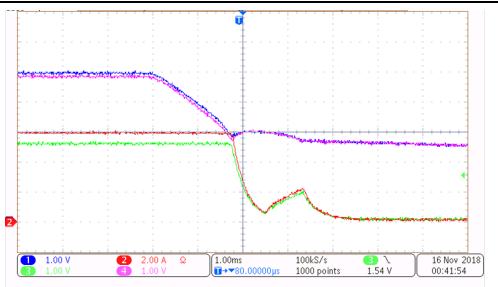

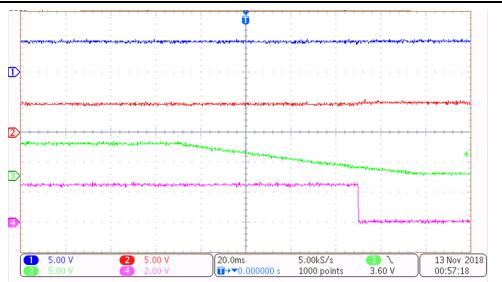

Figure 9. Shutdown Waveform No Load With Phase Node

# Table 10. Waveforms for Figure 9

| Waveform Number | Signal                          | Values                                 |

|-----------------|---------------------------------|----------------------------------------|

| 1               | Input Voltage to Load Switch    | 5 to 0 V                               |

| 2               | Output Voltage of Load Switch   | 5 to 0 V                               |

| 3               | Phase Node of POL Converter     | 5 to 0 V @ 100-kHz Switching Frequency |

| 4               | Output Voltage of POL Converter | 2.5 to 0 V                             |

Hardware, Software, Testing Requirements, and Test Results

Figure 10. Shutdown Waveform No Load With Output Current

For the tests in Figure 9 and Figure 10, the input power to the load switch was ramped down. 0 A of current was drawn from the output of the POL converter.

# Table 11. Waveforms for Figure 10

| Waveform Number | Signal                          | Values     |

|-----------------|---------------------------------|------------|

| 1               | Input Voltage to Load Switch    | 5 to 0 V   |

| 2               | Output Voltage of Load Switch   | 5 to 0 V   |

| 3               | Output Current of POL Converter | 0 A        |

| 4               | Output Voltage of POL Converter | 2.5 to 0 V |

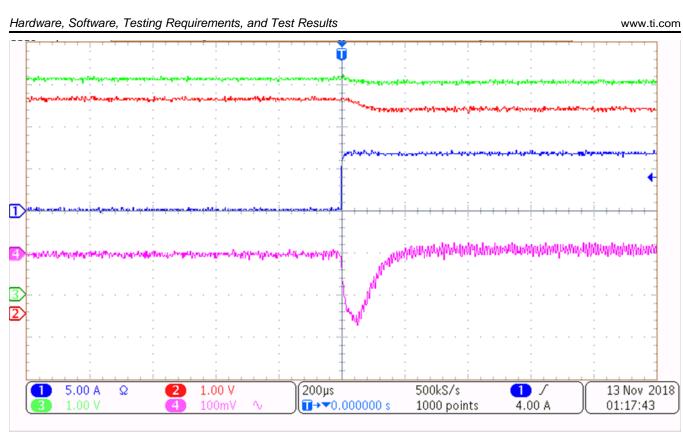

Figure 11. Negative Load Step With Phase Node

| Waveform Number | Signal                          | Values                                 |

|-----------------|---------------------------------|----------------------------------------|

| 1               | Phase Node of POL Converter     | 0 to 5 V @ 100-kHz Switching Frequency |

| 2               | CS Pin Voltage                  | 2.36 to 0 V                            |

| 3               | Output Current of POL Converter | 6 to 0 A                               |

| 4               | Output Voltage of Load Switch   | 4.8 to 5.2 V                           |

Figure 12. Negative Load Step With Input Voltage

For the tests in Figure 11 and Figure 12, the output current of the POL converter was stepped from 6 A to 0 A.

| Table 13 | . Waveforms f | or Figure 12 |

|----------|---------------|--------------|

|----------|---------------|--------------|

| Waveform Number | Signal                          | Values          |

|-----------------|---------------------------------|-----------------|

| 1               | Output Current of POL Converter | 6 to 0 A        |

| 2               | Output Voltage of Load Switch   | 4.8 to 5.2 V    |

| 3               | Input Voltage of Load Switch    | 5 to 5.2 A      |

| 4               | Output Voltage of POL Converter | 170-mV Increase |

Hardware, Software, Testing Requirements, and Test Results

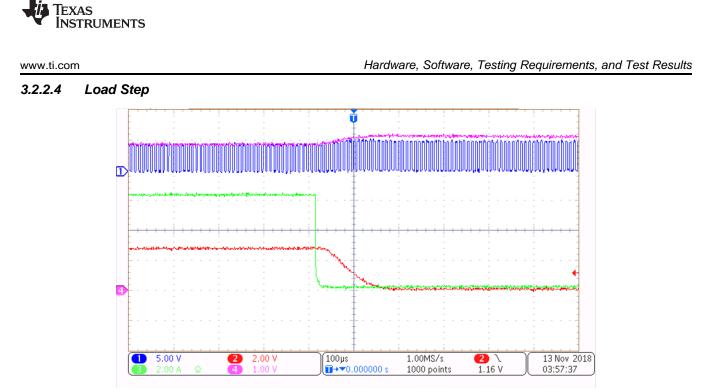

Figure 13. Positive Load Step With Phase Node

| Waveform Number | Signal                           | Values                                 |

|-----------------|----------------------------------|----------------------------------------|

| 1               | Phase Node of POL Converter      | 0 to 5 V @ 100-kHz Switching Frequency |

| 2               | Current Sense Pin of Load Switch | 0 to 2.36 V                            |

| 3               | Output Current of POL Converter  | 0 to 6 A                               |

| 4               | Output Voltage of Load Switch    | 5.2 to 4.8 V                           |

Figure 14. Positive Load Step With Input Voltage

For the tests in Figure 13 and Figure 14, the output current of the POL converter was stepped from 0 A to 6 A.

| Table 15. Waveforms for Figure 1 | 14 | iqure | or Fi | Waveforms | 15. | Table |

|----------------------------------|----|-------|-------|-----------|-----|-------|

|----------------------------------|----|-------|-------|-----------|-----|-------|

| Waveform Number | Signal                          | Values          |

|-----------------|---------------------------------|-----------------|

| 1               | Input Voltage of Load Switch    | 0 to 6 A        |

| 2               | Output Voltage of Load Switch   | 5.2 to 4.8 V    |

| 3               | Output Current of POL Converter | 5.2 to 5 A      |

| 4               | Output Voltage of POL Converter | 180-mV Increase |

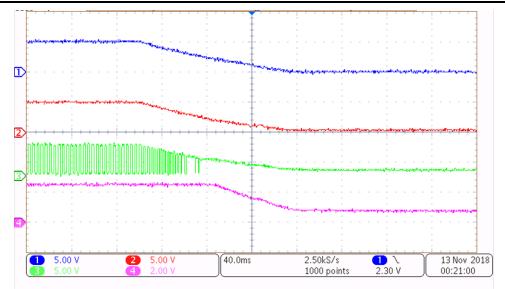

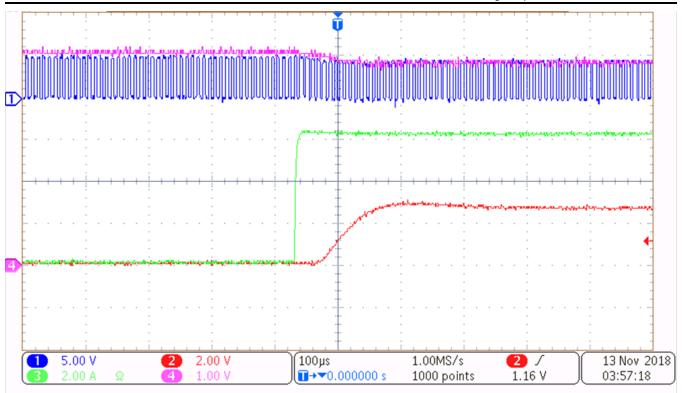

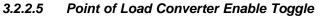

# Figure 15. POL Enable Toggle High With Phase Node

# Table 16. Waveforms for Figure 15

| Waveform Number | Signal                          | Value        |

|-----------------|---------------------------------|--------------|

| 1               | Output Current of POL Converter | 0 to 6 A     |

| 2               | Phase Node of POL Converter     | 4.8 V to 5 V |

| 3               | Enable Pin of POL Converter     | 5 to 0 V     |

| 4               | Output Voltage of POL Converter | 2.5 to 0 V   |

Hardware, Software, Testing Requirements, and Test Results

Figure 16. POL Enable Toggle High With Input Voltage

For tests in Figure 15 and Figure 16, the enable of the POL converter was brought high with the load switch already enabled.

# Table 17. Waveforms for Figure 16

| Waveform Number | Signal                          | Value      |

|-----------------|---------------------------------|------------|

| 1               | Input Voltage of Load Switch    | 5 V        |

| 2               | Output Voltage of Load Switch   | 5 to 4.8 V |

| 3               | Enable Pin of POL Converter     | 0 to 5 V   |

| 4               | Output Voltage of POL Converter | 0 to 2.5 V |

Hardware, Software, Testing Requirements, and Test Results

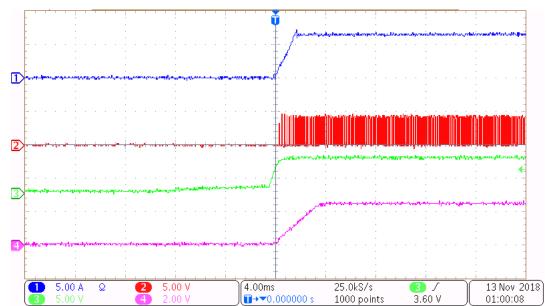

Figure 17. POL Enable Toggle Low With Phase Node

# Table 18. Waveforms for Figure 17

| Waveform Number | Signal                          | Value      |

|-----------------|---------------------------------|------------|

| 1               | Output Current of POL Converter | 6 to 0 A   |

| 2               | Phase Node of POL Converter     | 5 to 4.8 V |

| 3               | Enable Pin of POL Converter     | 0 to 5 V   |

| 4               | Output Voltage of POL Converter | 0 to 2.5 V |

#### Hardware, Software, Testing Requirements, and Test Results

Figure 18. POL Enable Toggle Low With Input Voltage

For the tests in Figure 17 and Figure 18, the enable of the POL converter was brought low with the load switch enabled.

# Table 19. Waveforms for Figure 18

| Waveform Number | Signal                          | Value      |

|-----------------|---------------------------------|------------|

| 1               | Input Voltage of Load Switch    | 5 V        |

| 2               | Output Voltage of POL Converter | 4.8 to 5 V |

| 3               | Enable Pin of POL Converter     | 5 to 0 V   |

| 4               | Output Voltage of POL Converter | 2.5 to 0 V |

Hardware, Software, Testing Requirements, and Test Results

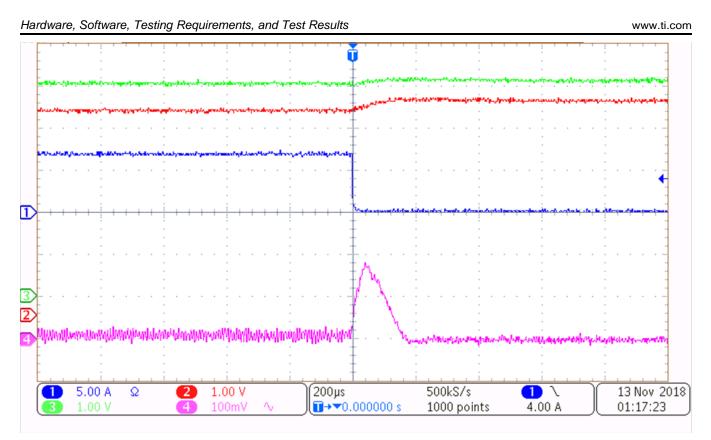

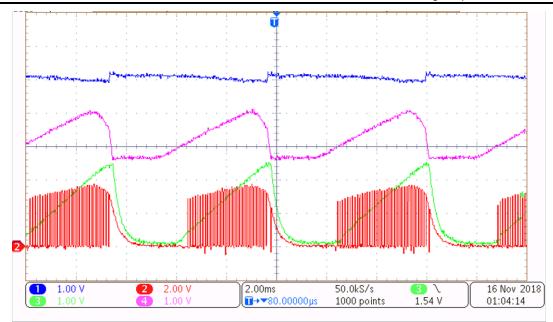

Figure 19. Load Switch Current Limit With Phase Node

# Table 20. Waveforms for Figure 19

| Waveform Number | Signal                          | Value                                  |

|-----------------|---------------------------------|----------------------------------------|

| 1               | Input Voltage of Load Switch    | 5 and 5.2 V                            |

| 2               | Phase Node of POL Converter     | 0 to 4 V @ 100-kHz Switching Frequency |

| 3               | Output Voltage of POL Converter | 0 to 2.5 V                             |

| 4               | Output Voltage of Load Switch   | 0.85 to 4 V                            |

#### Hardware, Software, Testing Requirements, and Test Results

# Figure 20. Load Switch Current Limit With Timer Pins

### Table 21. Waveforms for Figure 20

| Waveform Number | Signal                        | Value       |

|-----------------|-------------------------------|-------------|

| 1               | Input Voltage of Load Switch  | 5 and 5.2 V |

| 2               | RLTimer Pin of Load Switch    | 0.5 V       |

| 3               | ILTimer Pin of Load Switch    | 0 to 0.6 V  |

| 4               | Output Voltage of Load Switch | 0.85 to 4 V |

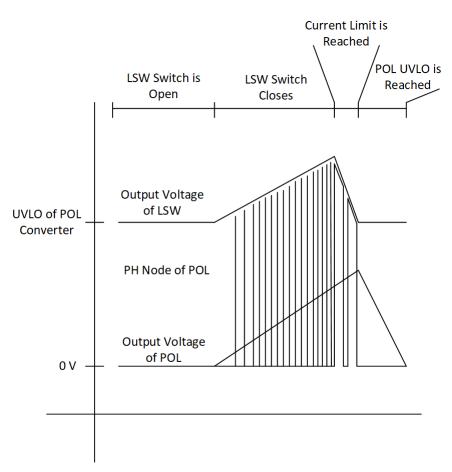

For the tests in Figure 19 and Figure 20, the load switch current limit was set to 3 A by changing the IL resistor to 15.4 k $\Omega$  and the output current of the POL Converter was kept at 6 A. This behavior shown is the result of the load switch stopping current flow. Since the current flow is stopping the output voltage of the load switch will drop until it hits the undervoltage lockout of the POL converter. Once the undervoltage lockout of the POL converter is reached the POL converter will turn off stopping the short. Since the short on the output has stopped, the load switch will let current through again and increase the load switch output voltage of the load switch increases and turns on the POL converter. This process will repeat until either the short on the output goes away or one of the devices is disabled.

www.ti.com

25

Figure 21. Breakdown of Load Switch Current Limit

### Hardware, Software, Testing Requirements, and Test Results

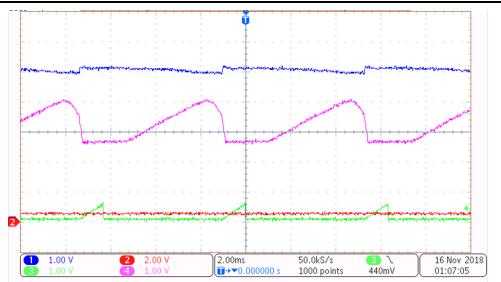

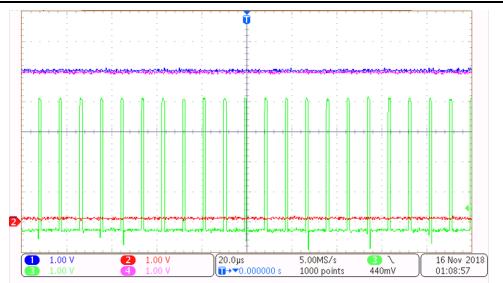

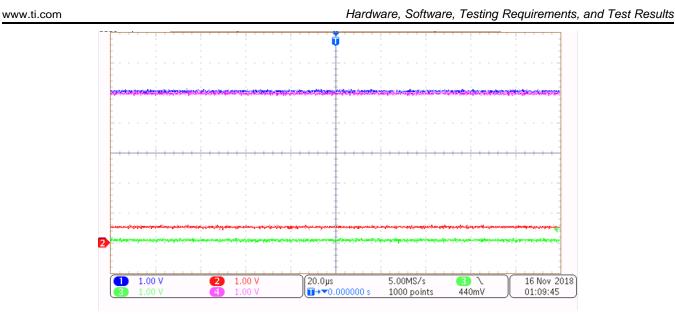

Figure 22. POL Current Limit With Phase Node

# Table 22. Waveforms for Figure 22

| Waveform Number | Signal                          | Values                                 |

|-----------------|---------------------------------|----------------------------------------|

| 1               | Input Voltage of Load Switch    | 5 V                                    |

| 2               | Output Voltage of POL Converter | 0 V                                    |

| 3               | Phase Node of POL Converter     | 0 to 5 V @ 100-kHz Switching Frequency |

| 4               | Output Voltage of Load Switch   | 5 V                                    |

Figure 23. POL Current Limit With Timer Pins

In this test, the current limit of the load switch was set at 7.5 A. The POL converter has an internal current limit of 11 A to 13 A on the output that was tripped. This causes the POL converter to limit the input current to around 3 A with the output voltage of the POL converter dropping. Since the current limit of the POL converter limit of the input current of the POL converter, the current limit of the load switch was not tripped and continued functioning. The duty cycle commanded will be determined by the minimum on time of the POL converter.

| Waveform Number | Signal                        | Values |

|-----------------|-------------------------------|--------|

| 1               | Input Voltage of Load Switch  | 5 V    |

| 2               | RLTimer Pin of Load Switch    | 0.5 V  |

| 3               | ILTimer Pin of Load Switch    | 0 V    |

| 4               | Output Voltage of Load Switch | 5 V    |

### Table 23. Waveforms for Figure 23

TEXAS INSTRUMENTS

Design Files

# 4 Design Files

www.ti.com

# 4.1 Schematics

To download the schematics, see the design files at TIDA-070001.

# 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-070001.

# 4.3 PCB Layout Recommendations

The TPS7H2201-SP EVM has power planes for VIN1, VIN2, VOUT, and GND on the top layer. Layers 2 and 3 are mostly all GND, with some signal routing on layer 3. Layer 4 contains more power planes for VIN1, VIN2, VOUT, and GND. Having multiple layers for each power plane allows for increased current carrying capacity and very low trace resistance. Vias are placed under the TPS7H2201-SP to allow for a thermal path from the top layer to the bottom layer.

For the TPS50601A-SP EVM that was used, it has PVIN, VIN, VOUT, and VPHASE all placed on the top layer. PVIN, VIN, and VOUT are also placed on the bottom of the board to increase current carrying capacity of the traces. The input decoupling capacitors (C8, C9, C10, C11, C12, C3, C4) are all located as close to the IC as possible. Placing the capacitors close is required to help with mitigating high frequency noise. The feedback resistors need to be placed as close to the FB pin as possible to prevent high frequency noise as well. The voltage set point divider, frequency set resistor, slow start capacitor, and compensation components are all routed to ground and placed close to a via to allow for high accuracy to the ground of the circuit board.

### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-070001.

# 4.4 Altium Project

To download the Altium Designer® project files, see the design files at TIDA-070001.

### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-070001.

### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-070001.

# 5 Related Documentation

- 1. TPS7H2201-SP Radiation Hardened 1.5-V to 7-V, 6-A Load Switch, SLVSDO0

- 2. TPS50601A-SP Radiation Hardened 3-V to 7-V Input, 6-A Synchronous Buck Converter, SLVSDF5

### 5.1 Trademarks

E2E is a trademark of Texas Instruments. Altium Designer is a registered trademark of Altium LLC or its affiliated companies. All other trademarks are the property of their respective owners.

# 5.2 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Original (December 2018) to A Revision

Page

| • | Changed title from "Switched Input Buck Converter Reference Design" to "3- to 7-V <sub>IN</sub> , Space-Grade Point-of-Load (POL) Reference Design with Redundant eFuse Inputs for OCP"                                           |   |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| • | Changed Description paragraph                                                                                                                                                                                                     | 1 |

| • | Changed "Overcurrent limit; Overvoltage limit; Input voltage redundancy; and Soft start" to " Adjustable over-current protection (OCP) limit; Adjustable over-voltage (OVP) limit; Redundant inputs; and Configurable soft start" | 1 |

| • | Deleted Satellite Power Dstribution for FPGAs, Microcontrollers, Data Converters, and ASICs; Radiation Hardened Applications, and Space Satellite Payloads Applications                                                           | 1 |

| • | Added Command and data handling; Satellite electric power system (EPS); Optical imaging payload; Radar imaging payload; and Communications payload applications                                                                   | 1 |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated