TI Designs: TIDA-01639

# Isolated Shunt Current Measurement Reference Design With Standalone Digital Filters

# Description

This reference design implements a class 0.5 three-phase energy measurement system with isolated shunt sensors by using isolated modulators and independent digital filters, enabling a wider choice of host microcontrollers (MCU) as integrated sync filters are no longer required. In this design, currents sensed by the isolated modulators and phase voltages sensed by the host microcontroller are synchronized; supporting the addition of advanced metrology algorithms using the SimpleLink™ ARM® Cortex® M4 host MCU. The design is immune from magnetic tamper attacks through the use of current sensors and power supplies that do not use any transformers or other magnetic components. This subsystem design is tested and includes hardware.

#### Resources

TIDA-01639 Design Folder AMC1106M05 Product Folder AMC1210 Product Folder Product Folder TLV9001 MSP432P4111 Product Folder **TPS3850** Product Folder TVS0500 Product Folder TPD1E04U04 Product Folder

ASK Our E2E™ Experts

# **Features**

- Class 0.5 three-phase metrology with galvanically isolated (up to 600 V<sub>RMS</sub> and peak isolation voltage of 4 kV<sub>RMS</sub>) shunt current sensors

- Galvanically isolated shunt current sensors and cap-drop supplies enable magnetic immunity

- Standalone digital filters enable using host microcontrollers without digital filters, thereby increasing design portability

- Synchronized voltage and current samples across all phases along with ARM® Cortex® M4 host MCU supports adding advanced metrology algorithms

- Active and reactive energy, root mean square (RMS) current and voltage, power factor, and line frequency calculations

# **Applications**

- Electricity Meter

- Power Quality Meter

System Description www.ti.com

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 1 System Description

Three-phase electricity meters measure the energy consumption at a businesses or industrial sites. To properly sense energy consumption, voltage and current sensors translate mains voltage and current to a voltage range that an ADC can sense. For three-phase electricity meters, it is necessary for the current sensors to be isolated so they can properly sense the energy consumption of multiple phases without damaging the ADC. As a result, current transformers, which inherently have isolation, have historically been used for the current sensors for three-phase electricity meters. One disadvantage of current transformers (and many transformers in general) is that they can be paralyzed by applying a strong enough magnetic field so that the sensed energy consumption is less than the actual energy consumption. Due to this weakness of current transformers against magnetic fields, it is common for people to try to tamper with a meter by placing a strong magnet outside the electricity meter to try to paralyze the current transformers to steal electricity. This reference design prevents magnetic tampering by using isolated shunts as current sensors instead of current transformers.

In this reference design, a class 0.5 three-phase transformerless energy measurement system is implemented with isolated shunt sensors by using isolated delta-sigma modulators. The inputs to these delta-sigma modulators are supplementally protected using ESD and TVS surge protection diodes. The delta-sigma modulators have their output circuitry capacitively isolated from input circuitry, which thereby provides transformerless data isolation. The high-side of each modulator is powered by a capacitive-drop supply that is also transformerless. Because a transformer is not used in this design (whether a power supply transformer or current transformer), the TIDA-01639 is inherently magnetically immune, thereby preventing electricity theft due to magnetic tampering. In addition, using the high-side cap-drop power supply has the following additional advantages:

- Reduces the entire system cost

- Inherently low conducted and radiated emissions

- Reduces the current consumption drawn from the low-side power supply since the high-side is separately powered from mains instead of being derived from the low-side controller power supply

A standalone digital filter device takes the different bitstreams from the isolated modulators and uses its digital filters to produce ADC sample readings that correspond to the voltages sensed across the shunts. The use of the standalone filter device enables the flexibility of selecting a host MCU that does not have digital filters integrated. The host MCU communicates with the standalone filter device via SPI to get the current samples. Since the host MCU only needs to communicate with one standalone digital filter device to get access to all the current samples, a communication multiplexing scheme is not needed to get the ADC samples of the different phases.

The host MCU also senses the phase voltage. Since the ADC of the host MCU that is used to sense voltage cannot sense below 0 V and the mains have both positive and negative voltages, an op amp is used to level shift the signal fed into the MCU ADC so that these signals are above 0 V.

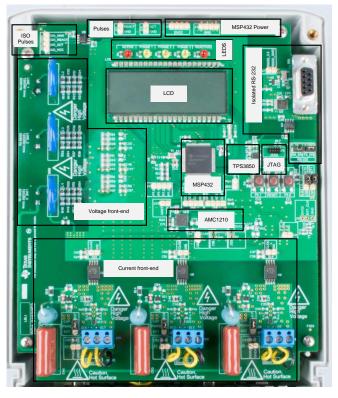

In addition to communicating to the standalone digital filter device and sensing the phase voltage, the host MCU also performs the following tasks:

- Calculates metrology parameter values

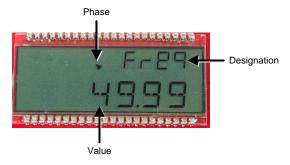

- Drives the liquid crystal display (LCD) of the board

- Communicates to a PC GUI through the isolated RS-232 circuitry of the board

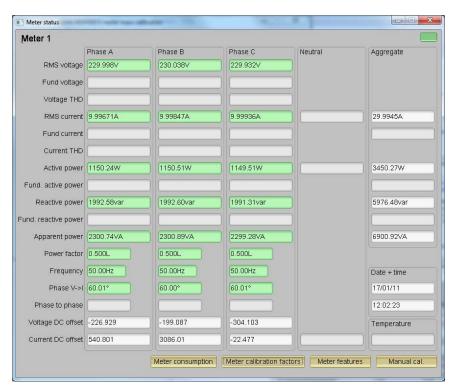

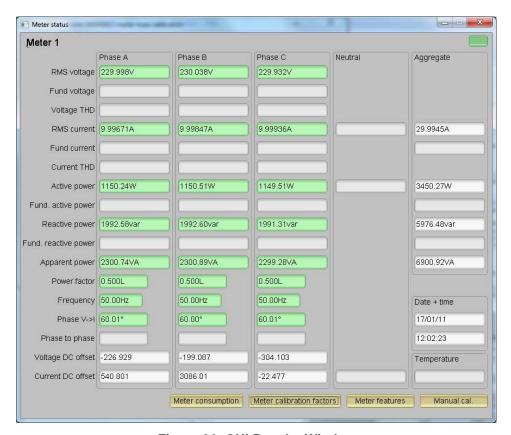

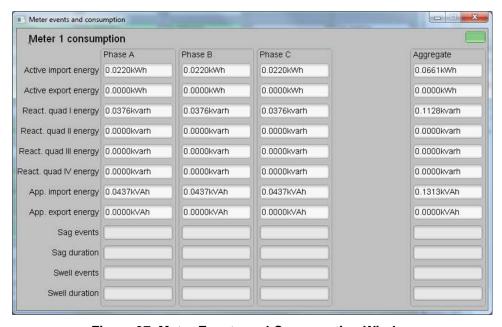

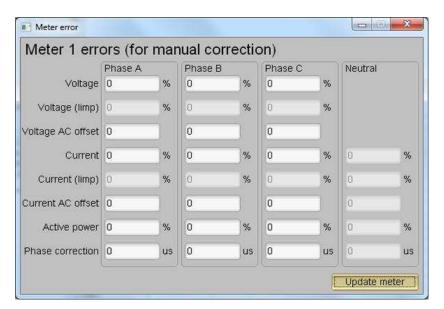

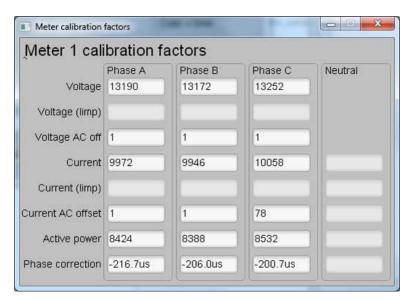

In regard to metrology, the test software supports calculation of various parameters for up to three-phase energy measurement. The key parameters calculated during energy measurements are: RMS current and voltage; active and reactive power and energies; power factor; and frequency. These parameters can be viewed either from the calibration GUI or LCD. Since the host MCU has access to all of the voltage and current channels of all the phases, the design also supports adding advanced metrology algorithms that need raw ADC data.

www.ti.com System Description

Another advantage of using shunts is that it does not share the same degradation in metrology results that current transformers show when harmonics are present in a system. As a result, these isolated shunt current sensors may also be used for equipment that perform harmonic analysis, such as power quality meters or power quality analyzers.

# 1.1 Key System Specifications

**Table 1. Key System Specifications**

| FEATURES                                                                 | DESCRIPTION                                                                                                                                                       |  |  |  |  |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Number of phases                                                         | 3                                                                                                                                                                 |  |  |  |  |

| Accuracy class                                                           | Class 0.5                                                                                                                                                         |  |  |  |  |

| Current sensor                                                           | Shunt                                                                                                                                                             |  |  |  |  |

| Voltage ADC type                                                         | SAR (MSP432P4111)                                                                                                                                                 |  |  |  |  |

| Delta-sigma (for current channels) modulation clock frequency            | 6,000,000 Hz                                                                                                                                                      |  |  |  |  |

| Digital filter sample oversampling ratio (SOSR) from filter unit         | 128                                                                                                                                                               |  |  |  |  |

| Digital filter integrator oversampling ratio (IOSR) from integrator unit | 8                                                                                                                                                                 |  |  |  |  |

| Digital filter effective oversampling ratio (EOSR)                       | 1024                                                                                                                                                              |  |  |  |  |

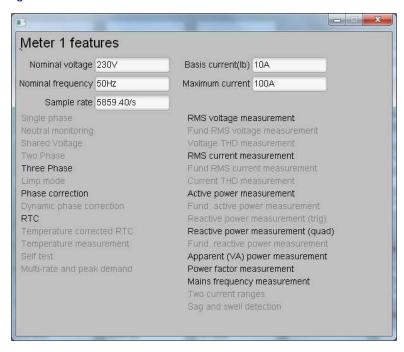

| Digital filter output sample rate                                        | 5,859.4 samples per second                                                                                                                                        |  |  |  |  |

| Ratio of skipped samples in software to total samples                    | 0/5                                                                                                                                                               |  |  |  |  |

| Effective sample rate (for both current and voltage)                     | 5,859.4 kHz samples per second                                                                                                                                    |  |  |  |  |

| Phase compensation implementation                                        | Software                                                                                                                                                          |  |  |  |  |

| Phase compensation resolution                                            | 198.68 ns = 0.0120° at 50 Hz or 0.0144° at 60 Hz                                                                                                                  |  |  |  |  |

| Selected CPU clock frequency                                             | 48 MHz                                                                                                                                                            |  |  |  |  |

| System nominal frequency                                                 | 50 or 60 Hz                                                                                                                                                       |  |  |  |  |

| Measured parameters                                                      | <ul> <li>Active, reactive, apparent power and energy</li> <li>Root mean square (RMS) current and voltage</li> <li>Power factor</li> <li>Line frequency</li> </ul> |  |  |  |  |

| Utilized LEDs                                                            | Total active energy and total reactive energy                                                                                                                     |  |  |  |  |

| Isolated modulator high-side power                                       | Option 1: Power derived from mains using cap-drop supply; Option 2: External power                                                                                |  |  |  |  |

# 2 System Overview

# 2.1 Block Diagram

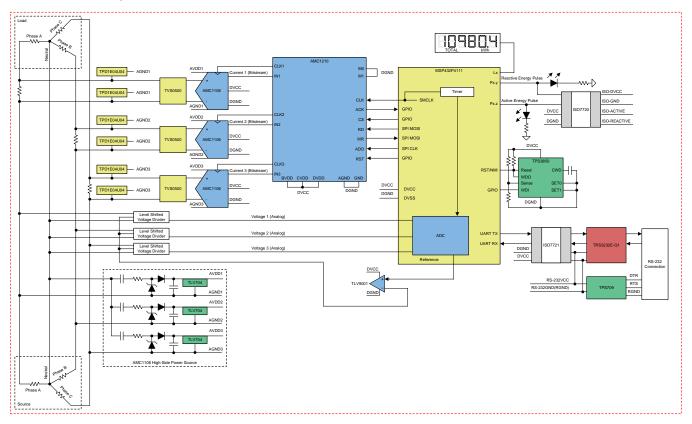

Figure 1. TIDA-01639 Block Diagram

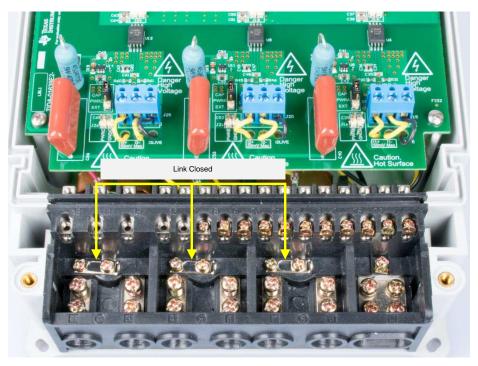

Figure 1 depicts a block diagram that shows the high-level interface used for a MSP432P4111-based three-phase energy measurement application with isolated shunts using AMC1106 isolated modulator devices and an AMC1210 digital filter device. Figure 1 particularly shows a three-phase, four-wire star connection to the AC mains. In this reference design, each phase has a shunt current sensor and an AMC1106 device for measuring the voltage across the shunt current sensor. The resistance of the shunt is selected based on the current range required for energy measurements and also the minimization of the maximum power dissipation of the shunt.

In this design, the modulator clock used by the AMC1106 devices is provided from the SMCLK clock signal output of the MSP432 that is connected to the CLK pin of the AMC1210. The AMC1210 is configured to output the clock fed to its CLK pin to its CLK1, CLK2, and CLK3 pins, which are connected to the corresponding modulator clock inputs of the isolated modulators. By configuring the AMC1210 to output the modulator clock that is at its CLK pin to the CLK1, CLK2, and CLK3 pins, it reduces layout complexity since it enables connecting the three isolated modulator clocks to one clock without having to route this clock across the PCB of the design.

The shunt input to each AMC1106 is supplementally protected by a TVS0500 surge protection device and the TPD1E04U04 ESD protection diodes. Once the modulator clock is provided to the AMC1106 devices, the AMC1106 devices output bitstreams that correspond to the voltages they sense across their shunt inputs. The bitstream from each AMC1106 is fed into a different digital filter of the AMC1210 device. Once the bitstreams are output by the AMC1106, the following steps occur:

- 1. The digital filters take the bitstream and generate ADC samples to correspond to the voltage sensed across the shunt by the AMC1106 devices.

- For each new ADC sample, the AMC1210 asserts its ACK pin, which alerts the MSP432 that new samples are available.

3. After being alerted of new samples, the AMC1210 uses one of its SPI interfaces to get the current samples from the AMC1210.

Since each high side of the AMC1106 devices is referenced from a different line, a different power supply is needed for the high-side of each AMC1106 device. Each implemented power supply provides power to the associated AMC1106 device by using a cap-drop power supply from the line of that phase and neutral. In contrast, for powering the controller-side of the AMC1106 chips, all AMC1106s are powered from the same source that powers the MSP432 and AMC1210 devices.

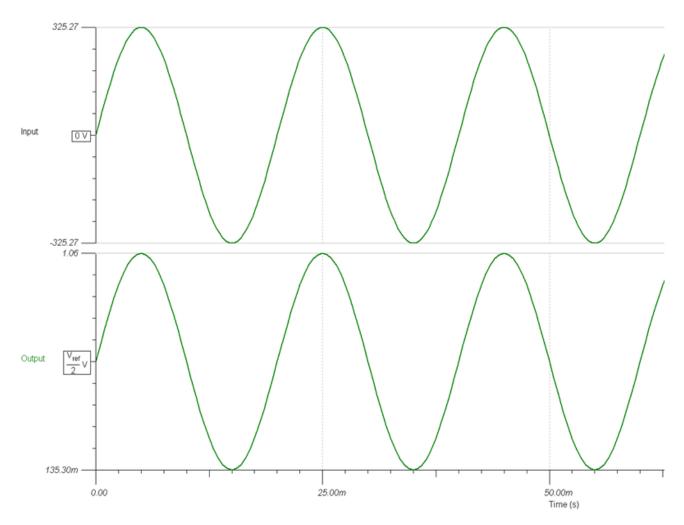

The 14-bit SAR ADC of the MSP432 senses the phase voltages in this design. In the Magnetically Immune Transformerless Power Supply for Isolated Shunt Current Measurement reference design, it was shown that a 10-bit ADC is sufficient for measuring phase voltage so the 14-bit SAR ADC in this design is more than sufficient for measuring phase voltage. The SAR ADC of the MSP432 can sense voltages from 0-V<sub>RFF</sub> V , where V<sub>RFF</sub> is the voltage of the selected reference used by the SAR ADC for conversion. For a given Mains voltage input to a voltage front-end circuit, Figure 2 shows an example output voltage waveform that can be sensed by the SAR ADC of the MSP432 if a 1.2 V V<sub>REF</sub> value is used. To generate the desired output voltage from the votlage front-end circuit, a voltage divider is used to divide down the Mains voltage to a range that can be sensed by the SAR ADC of the MSP432. Since the output of the voltage divider has half of its waveform below 0 V and the SAR ADC of the MSP432 cannot sense below 0 V, a level shifter is also necessary to level shift the voltage fed to the SAR ADC above 0 V. To maximize the useable range of the ADC, the ideal level shift amount is equal to  $V_{\text{REF}}$  / 2 . The level shift is implemented by the reference voltage used by the SAR ADC being output by the MSP342 and fed into a TLV9001 op amp, which acts as a buffer. The output of the op amp then drives a voltage divider that is used to create the V<sub>REF</sub> / 2 shift voltage. An op amp is needed for this level shifter implementation because the reference voltage output from the MSP432 cannot directly drive the voltage divider used to create the  $V_{RFF}$  / 2 voltage.

Figure 2. Voltage Front-End Input Voltage and Output Voltage Waveforms

For the proper calculation of power readings, the voltage and current samples must be synchronized. This synchronization is done by having the modulator clock used by the AMC1106 and AMC1210 also fed to an internal timer of the MSP432. The output of this timer is used to automatically trigger in hardware the SAR ADC to sample the voltages of the different phases. The timer is setup to count up to the effective OSR number of the AMC1210 so that the timing mimics the timing of the AMC1210, and there is one voltage sample produced for each current sample.

In this design, a TPS3850 device is also used as a SVS and watchdog for the MSP432. Although the MSP432 has an internal watchdog and SVS that suffices for this application, the TPS3850 standalone watchdog is used because there is additional security in having a watchdog and SVS that is independent of the MCU.

Other signals of interest in Figure 1 are the active and reactive energy pulses used for accuracy measurement and calibration. The ISO7720 provides an isolated connection for these pulses for connecting to non-isolated equipment. In addition to isolated pulses, the design supports isolated RS-232 communication through the use of the TPS70933, ISO7721, and TRS3232E-Q1 devices.

# 2.2 Highlighted Products

#### 2.2.1 AMC1106M05

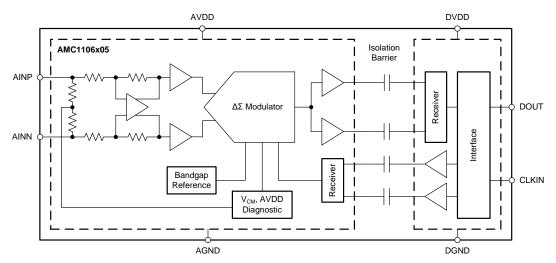

The AMC1106 device is a precision, delta-sigma ( $\Delta\Sigma$ ) modulator with the output separated from the input circuitry by a capacitive isolation barrier that is highly resistant to magnetic interference. On the high-side of the AMC1106, the modulator can be supplied by a 3.3-V or 5-V power supply (AVDD). The isolated digital interface operates from a 3.0-V, 3.3-V, or 5-V power supply (DVDD).

The AMC1106 is used to provide isolated current measurement for the shunt current sensors of the design. This isolated current measurement is accomplished by the AMC1106 providing a modulation bit-stream output that is capacitively isolated from the analog signal fed from the shunts to the AMC1106, as Figure 3 shows.

Figure 3. AMC1106 Functional Block Diagram

In Figure 3, the shunt current measurement is made by measuring the voltage across terminals AINP and AINN of the AMC1106, which are connected to the shunt outputs. If the input voltage value exceeds ±50 mV, there is degradation in the accuracy of readings. The third terminal of the shunt is then connected to AGND of the AMC1106. To perform measurements, 3.3 V or 5 V must be fed between AVDD and AGND.

To properly power the controller side, pins DVDD and DGND on the AMC1106 must be connected to DVCC and DVSS of the MSP432. In addition, the modulation clock used by the AMC1210 digital filters must be connected to CLKIN. This modulation clock must be between 5 to 20 MHz for the AMC1106 to properly work and can be generated from the SMCLK clock output of the MSP432. With a proper clock fed into CLKIN of an AMC1106 device, a delta-sigma bit-stream is output from the DOUT pin of the AMC1106. This DOUT pin must be connected to the bit-stream input of the corresponding digital filter within the AMC1210 device.

#### 2.2.2 AMC1210

The AMC1210 is a four-channel digital filter designed specifically for current measurement and resolver position decoding in motor control applications. Each input can receive an independent delta-sigma modulator bit stream. The bit streams are processed by four individually-programmable digital decimation filters. The AMC1210 also offers a flexible interface and a comprehensive interrupt unit, allowing customized digital functionality and immediate digital threshold comparisons for over-current monitoring.

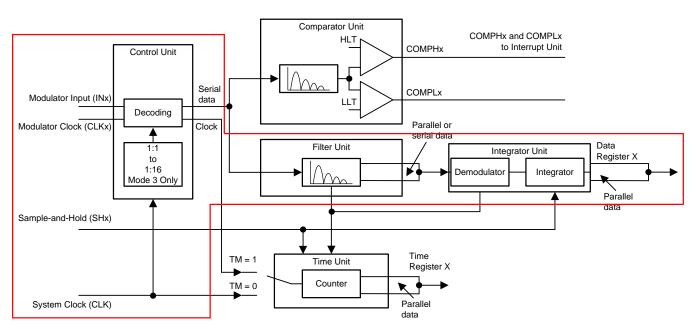

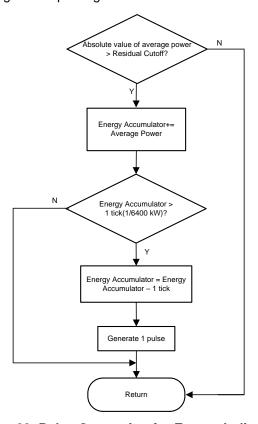

In this reference design, the AMC1210 device is used to decimate the bitstreams from the AMC1106 devices. The AMC1210 has four independent filter modules. Figure 4 shows the block diagram of a AMC1210 filter module. The portion within the red box represents the parts of the filter module that are used in this reference design.

Figure 4. AMC1210 Filter Module Block Diagram

The AMC1210 has the capability to internally output the system clock, which is fed into the CLK pin of the device, onto each of the CLKx pins. By connecting the CLKx pins of the AMC1210 to the CLKIN pin of the AMC1106, configuring the AMC1210 to internally output the clock on its CLK pin to its CLKx pins connects the isolated modulators to the modulator clock. This feature can be used so that the modulator clock only has to be fed from its source to the CLK pin of the AMC1210 and not to the individual modulators.

Within the filter module, the type of filter (sinc¹, sinc², or sinc³) can be selected as well as a sample OSR value up to 128. The output from the filter unit can then be fed into the integrator unit. The integrator unit allows summation of a defined number of samples from the filter unit. After the user-defined number of samples, which is called the integrator OSR, from the filter unit has been summed, the ACK pin on the AMC1210 is asserted to alert the MCU that new samples are ready. The integrator can be used to divide down the effective sample rate so that less processing is necessary from the host MCU. As an example, with an integrator OSR of 8, sample filter OSR of 128, the timing of an OSR = 1024 filter can be mimicked. With a 6 MHz modulation clock frequency, the resulting effective OSR produces a smaller effective sample rate of 5,859.375 Hz instead of the resulting sample rate of 46,875 if the integrator unit is not used.

To save cost, internal ADCs of a host MCU can be used to measure the phase voltage instead of using additional isolated modulators and an extra AMC1210 device to measure phase voltage. To calculate power readings properly, the voltage and current sampling have to be synchronized. This voltage and current synchronization can be done by using a timer to trigger voltage conversions and having the timer's timing to mimic the timing of the AMC1210 so that there is a voltage sample produced for each current sample.

# 2.2.3 TLV9001

The TLV900x family includes single (TLV9001), dual (TLV9002), and quad-channel (TLV9004) low-voltage (1.8 V to 5.5 V) operational amplifiers (op amps) with rail-to-rail input and output swing capabilities. These op amps provide a cost-effective solution for space-constrained applications. These op amps are designed specifically for low-voltage operation (1.8 V to 5.5 V) with performance specifications similar to the TLV600x devices. The robust design of the TLV900x family simplifies circuit design. The op amps feature unity-gain stability, an integrated RFI and EMI rejection filter, and no-phase reversal in overdrive conditions. Micro-size packages, such as SOT-553 and WSON, are offered for all channel variants (single, dual, and quad), along with industry-standard packages such as SOIC, MSOP, SOT-23 and TSSOP packages.

The TLV9001 buffers the internal reference used by the SAR ADC of the MSP432 so that it can be fed into a voltage divider to create a  $V_{REF}$  / 2 DC voltage signal. The reference voltage output from the MSP432 cannot directly drive the  $V_{REF}$  / 2 voltage divider, which is why the TLV9001 device is used. The  $V_{REF}$  / 2 voltage signal is used to level shift the output from the Mains voltage divider so that the resulting signal fed into the SAR of the MSP432 is within its acceptable input voltage range.

For this design, the TLV9001 device was specifically selected for the reference buffer in this design because of its low cost. In addition, the low offset voltage of this op amp for the given cost enables the accurate generation of the  $V_{REF}$  / 2 offset needed for level shifting the signal fed into the SAR ADC.

#### 2.2.4 MSP432P4111

The SimpleLink™ MSP432P4111 MCUs are optimized MCUs that deliver ultra-low-power performance with FPU and DSP extensions. This device has an Arm® 32-Bit Cortex®-M4F CPU with Floating-Point Unit and Memory Protection Unit, a real-time clock, LCD driver, port mappable GPIOs, an AES encryption and decryption accelerator, and multiple serial communication options. The MSP432P4111 device is part of the SimpleLink MCU platform, which consists of Wi-Fi®, *Bluetooth*® low energy, Sub-1 GHz, and host MCUs. All of these devices share a common, easy-to-use development environment with a single-core software development kit (SDK) and rich tool set.

The MSP432 in this design senses the phase voltages, retrieves current samples from the AMC1210, and calculates metrology parameters. In addition, the device also keeps track of time with its RTC module, drives the LCD on the board with its internal LCD driver module, and uses one of its UART interfaces to communicate to a PC GUI using the isolated RS-232 circuit of the board.

#### 2.2.5 TPS3850

The TPS3850 combines a precision voltage supervisor with a programmable window watchdog timer. The TPS3850 window comparator achieves 0.8% accuracy ( $-40^{\circ}$ C to +125°C) for the undervoltage ( $V_{\text{IT-(UV)}}$ ) threshold. The TPS3850 also includes accurate hysteresis on the threshold, making the device ideal for use with tight tolerance systems. The supervisor RESET delay can be set by factory-programmed default delay settings, or programmed by an external capacitor. The factory-programmed RESET delay features a 15% accuracy, high-precision delay timing. The TPS3850 includes a programmable window watchdog timer for a wide variety of applications. The dedicated watchdog output (WDO) enables increased resolution to help determine the nature of fault conditions. The window watchdog timeouts can be set by factory-programmed default delay settings, or programmed by an external capacitor. The watchdog can be disabled via logic pins to avoid undesired watchdog timeouts during the development process. The TPS3850 is available in a small 3.00-mm × 3.00-mm, 10-pin VSON package.

For electricity meters, some manufacturers prefer to have external SVS and watchdog timer devices to reset any microcontrollers in the system, even if the microcontrollers already have an internal SVS and watchdog timer. External SVS and watchdog timers are sometimes preferred over using the SVS and watchdog timer within a microcontroller because the external option can be more secure than the internal option since the external devices function independently of the microcontroller. Although the SVS and watchdog timer of the MSP432 suffices for this application, the TPS3850 external SVS and watchdog timer device is added to this design for an additional level of security.

In this design, the TPS3850H01 variant is specifically used, which enables the undervoltage threshold value to be programmed by external resistors. This variant was also selected because it does not function as a window comparator like the other TPS3850 variants. This variant only monitors the undervoltage threshold and does not have an overvoltage threshold. If the monitored voltage falls below the undervoltage threshold, the RESET pin of the TPS3850 is asserted low. In addition to serving as an SVS device, the device functions as an external watchdog as well. A pulse is output by the MSP342 and fed to the WDI pin of the TPS3850. If the time between successive falling edges on the WDI pin is not within the allowed lower and upper watchdog window boundaries, the WDO pin of the TPS3850 is asserted low. The RESET and WDO output pins of the TPS3850 are connected to each other and the reset of the MSP432 so that the MSP432 is reset whenever the WDO or RESET pins of the TPS3850 are asserted low.

#### 2.2.6 TVS0500

The TVS0500 robustly shunts up to 43 A of IEC 61000-4-5 fault current to protect systems from high power transients or lightning strikes. The device offers a solution to the common industrial signal line EMC requirement to survive up to 2 kV IEC 61000-4-5 open circuit voltage coupled through a 42  $\Omega$  impedance. The TVS0500 uses a unique feedback mechanism to ensure precise flat clamping during a fault, assuring system exposure below 10 V. The tight voltage regulation allows designers to confidently select system components with a lower voltage tolerance, lowering system costs and complexity without sacrificing robustness. In addition, the TVS0500 is available in a small 2 mm  $\times$  2 mm SON footprint which is ideal for space constrained applications, offering a 70 percent reduction in size compared to industry standard SMA and SMB packages. The extremely low device leakage and capacitance ensure a minimal effect on the protected line. To ensure robust protection over the lifetime of the product, TI tests the TVS0500 against 5000 repetitive surge strikes at high temperature with no shift in device performance. In this design, the TVS0500 is placed in the current front-end circuitry to protect the analog input pins of the AMC1106.

#### 2.2.7 TPD1E04U04

The TPD1E04U04 is a unidirectional TVS ESD protection diode for HDMI 2.0 and USB 3.0 circuit protection. The TPD1E04U04 is rated to dissipate ESD strikes above the maximum level specified in the IEC 61000-4-2 international standard (Level 4). This device features a 0.5-pF IO capacitance making it ideal for protecting high-speed interfaces up to 6 Gbps such as HDMI 2.0 and USB 3.0. The low dynamic resistance and ultra-low clamping voltage ensure system level protection against transient events for sensitive SoCs. The TPD1E04U04 is offered in the industry standard 0402 (DPY) and 0201 (DPL) packages. In this design, the TPD1E04U04 is placed in the current front-end circuitry for additional protection of the analog input pins of the AMC1106.

#### 2.2.8 TLV704

The TLV70433 low-dropout (LDO) regulator is an ultra-low quiescent current device designed for extremely power-sensitive applications. Quiescent current is virtually constant over the complete load current and ambient temperature range. The TLV70433 operates over a wide operating input voltage of 2.5 V to 24 V. Thus, the device is an excellent choice for both battery-powered systems as well as industrial applications that undergo large line transients. The TLV70433 is used as the LDO within the cap-drop high-side power supplies of the AMC1106 devices. Cap-drop supplies can only support a small load current. The TLV70433 was selected for the cap-drop LDO because it has a small quiescent current, which allows more of the limited load current of the cap-drop supply to be used to power the high-side of the AMC1106 devices.

# 2.2.9 TRS3232E-Q1

To properly interface with the RS-232 standard, a voltage translation system is required to convert between the 3.3-V domain on the board and from the 12 V on the port itself. To facilitate the translation, the design uses a TRS3232E-Q1 device. The TRS3232E-Q1 device is capable of driving the higher voltage signals on the RS-232 port from only the 3.3-V DVCC through a charge pump system.

The TRS3232E-Q1 device consists of two line drivers, two line receivers, and a dual charge-pump circuit with ±15-kV electrostatic discharge (ESD) protection pin-to-pin (serial-port connection pins, including GND). The device meets the requirements of the Telecommunications Industry Association and Electronic Industries Alliance TIA/EIA-232-F and provides the electrical interface between an asynchronous communication controller and the serial-port connector. The charge pump and four small external capacitors allow operation from a single 3-V to 5.5-V supply. The devices operate at data signaling rates up to 250 kbps and a maximum of 30-V/µs driver output slew rate.

#### 2.2.10 ISO7721

To add isolation to the RS-232 connection to a PC, the isolated RS-232 portion of this reference design uses capacitive galvanic isolation, which has an inherent lifespan advantage over an opto-isolator. In particular, industrial devices are usually pressed into service for much longer periods of time than consumer electronics; therefore, maintenance of effective isolation over a period of 15 years or longer is important.

The variant of the ISO7721 used in the RS-232 circuitry of this reference design provides galvanic isolation up to  $3.0~\rm kV_{RMS}$  for one minute per UL. This digital isolator has two isolated channels where one is a forward channel and the other is a reverse channel. Each isolation channel has a logic input and output buffer separated by a silicon dioxide ( $\rm SiO_2$ ) insulation barrier. This chip supports a signaling rate of 100 Mbps. The chips can operate from a 3.3-V and 5-V supply and logic levels.

#### 2.2.11 TPS709

To power the data terminal equipment (DTE) side of the isolation boundary and the RS-232 charge pump, there are two choices. The interface can either implement an isolated power supply or harvest power from the RS-232 line. Integrating a power supply adds cost and complexity to the system, which is difficult to justify in low-cost sensing applications.

To implement the second option of harvesting power from the RS-232 port itself, this reference design uses the flow control lines that are ignored in most embedded applications. The RS-232 specification (when properly implemented on a host computer or adapter cable), keeps the request to send (RTS) and data terminal ready (DTR) lines high when the port is active. As long as the host has the COM port open, these two lines retain voltage on them. This voltage can vary from 5 V to 12 V, depending on the driver implementation. The 5 V to 12 V is sufficient for the use requirements in this design.

The voltage is put through a diode arrangement to block signals from entering back into the pins. The voltage charges a capacitor to store energy. The capacitor releases this energy when the barrier and charge pump pull more current than what is instantaneously allowed. The TPS70933 is used to bring the line voltage down to a working voltage for the charge pump and isolation device.

The TPS70933 linear regulator is an ultra-low quiescent current devices designed for power-sensitive applications. A precision band-gap and error amplifier provides 2% accuracy over temperature. A quiescent current of only 1 µA makes these devices ideal solutions for battery-powered, always-on systems that require very little idle-state power dissipation. These devices have thermal-shutdown, current-limit, and reverse-current protections for added safety. These regulators can be put into shutdown mode by pulling the EN pin low. The shutdown current in this mode goes down to 150 nA (typical).

# 2.2.12 ISO7720

The ISO772x devices are high-performance, dual-channel digital isolators with 5000  $V_{RMS}$  (DW package) and 3000  $V_{RMS}$  (D package) isolation ratings per UL 1577. These devices are also certified by VDE, TUV, CSA, and CQC. The ISO772x devices provide high electromagnetic immunity and low emissions at low power consumption, while isolating CMOS or LVCMOS digital I/Os. Each isolation channel has a logic input and output buffer separated by a silicon dioxide (SiO2) insulation barrier. The ISO7720 device has both channels in the same direction while the ISO7721 device has both channels in the opposite direction. In the event of input power or signal loss, the default output is high for devices without suffix F and low for devices with suffix F. Through innovative chip design and layout techniques, the electromagnetic compatibility of the ISO772x devices has been significantly enhanced to ease system-level ESD, EFT, surge, and emissions compliance. The ISO772x family of devices is available in 16-pin SOIC wide-body (DW) and 8-pin SOIC narrow-body (D) packages.

To test the active energy and reactive energy accuracy of a meter, pulses are output at a rate proportional to the amount of energy consumed. A reference meter can then determine the accuracy of the e-meter by calculating the error based on these pulses and how much energy is provided to the meter. In this reference design, pulses are output through headers for the cumulative active and reactive energy consumption. Using the ISO7720 provides an isolated version of these headers for connection to non-isolated equipment. In this design, the D package of the ISO7720 is used, which provides an isolation voltage of 3000  $V_{RMS}$  for these signals. These isolated active and reactive signals can be set to have either a 3.3- or 5-V maximum voltage output by applying the selected maximum voltage output between the VCC (ISO\_VCC) and GND (ISO\_GND) of the isolated side.

# 2.3 System Design Theory

# 2.3.1 Design Hardware Implementation

# 2.3.1.1 TPS3850H01 SVS and Watchdog Timer

The TPS3850H01 is an external supply voltage supervisor (SVS) and watchdog timer that is used to externally reset the MSP432. The MSP432 has an internal watchdog timer and SVS device that can be used as well, which will suffice for this application; however, meter manufacturers sometimes use external SVS and watchdog timer devices instead of an internal SVS and watchdog timer of the microcontroller because they add an additional layer of security since they are independent of the microcontroller, and therefore, are less affected by any issues that affect the microcontroller itself.

The TPS3850H01 device variant is specifically an undervoltage monitor. Whenever the monitored voltage is below the undervoltage threshold, the RESET pin of the TPS3850 is asserted low. When the monitored voltage rises above the undervoltage threshold plus hysteresis voltage value, the RESET pin of the TPS3850 is pulled back high after a  $t_{RST}$  user-defined delay elapses. The TPS3850H01 variant does not have an overvoltage monitoring feature like the other TPS3850 variants, which enables the voltage rail that is supervised to detect under voltage conditions when monitoring supply ranges that may vary over a wide range of voltages (such as 2 V to 3.6 V).

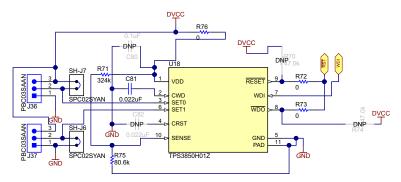

For the TPS3850H01 variant, the undervoltage threshold can be set by connecting a resistor divider to the SENSE pin of the TPS3850H01. The values of the two resistors in the voltage divider as well as the monitored supply voltage determine the undervoltage threshold. Figure 5 shows the TPS3850H01 circuit used in this design with R71 (324 k $\Omega$ ) and R75 (80.6 k $\Omega$ ) being the two resistors that determine the undervoltage threshold

Figure 5. TPS3850H01 Circuit

The threshold voltage is calculated with Equation 1:

$$V_{MON} = V_{IT(ADJ)} \times \left(1 + \frac{R_{71}}{R_{75}}\right)$$

where

The typical value of V<sub>IT(ADJ)</sub> is 0.4 V (taken from the TPS3850 datasheeet)

Given the nominal values for R71 and R75 used in this design, the undervoltage threshold is approximately 2.0 V.

In addition to acting as an undervoltage monitor, the TPS3850H01 device is also configured to act as a watchdog timer. A pulse is output by the MSP342 and fed to the WDI pin of the TPS3850. If the time between successive falling edges on the WDI pin is not within the allowed lower and upper watchdog window boundaries, the WDO pin of the TPS3850 is asserted low for  $t_{RST}$ .  $t_{RST}$  is programmed by either connecting a capacitor, connecting a pullup resistor, or not connecting anything to the CRST pin of the TPS3850. In this design, nothing is connected to the CRST pin, which results in a typical  $t_{RST}$  time of 200 ms.

(1)

The time between successive falling edges on the WDI pin should be between a lower ( $t_{WDL(max)}$ ) and upper ( $t_{WDU(min)}$ ) time interval. If the time between successive falling edges is not within this window, then the WDO pin is asserted low for a time of  $t_{RST}$ .  $t_{WDU(min)}$  is determined based on  $t_{WDU(typ)}$ , which is programmed by either connecting a capacitor, connecting a pullup resistor, or not connecting anything to the CWD pin of the TPS3850.  $t_{WDL(max)}$  is determined by  $t_{WDU(typ)}$  as well as the state of the SET0 and SET1 pins. The state of the SET0 and SET1 pins are set by connecting the pins to either GND(0) or VDD(1). Figure 6 shows the formula for  $t_{WDL(max)}$  in the green box, and the formula for  $t_{WDL(max)}$  in the red box. The calculation of  $t_{WDL(max)}$  is derived from the  $t_{WDL(max)}$  calculation, which is in the blue box.

| Input |      |      | Watchdog Lower Boundary (t <sub>WDL</sub> ) |                          |                               | Watchdog Upper Boundary (t <sub>WDU</sub> ) |                                   |                              |      |  |

|-------|------|------|---------------------------------------------|--------------------------|-------------------------------|---------------------------------------------|-----------------------------------|------------------------------|------|--|

| CWD   | SET0 | SET1 | MIN                                         | TYP                      | MAX                           | MIN TYP                                     |                                   | MAX                          | Unit |  |

| Ccwd  | 0    | 0    | t <sub>WDU(min)</sub> x 0.125               | t <sub>WDU</sub> x 0.125 | t <sub>WDU(max)</sub> x 0.125 | 0.85 x t <sub>WD</sub>                      | $t_{WDU(typ)}$ $t_{WDU(typ)}$ (1) | 1.15 x t <sub>WDU(typ)</sub> | S    |  |

|       | 0    | 1    | t <sub>WDU(min)</sub> x 0.75                | t <sub>WDU</sub> x 0.75  | t <sub>WDU(max)</sub> x 0.75  | 0.85 x t <sub>WD</sub>                      | $t_{WDU(typ)}$ $t_{WDU(typ)}$ (1) | 1.15 x t <sub>WDU(typ)</sub> | S    |  |

|       | 1    | 0    |                                             | Watchdog disabled        |                               |                                             | Watchdog disabled                 | 1                            |      |  |

|       | 1    | 1    | t <sub>WDU(min)</sub> x 0.5                 | t <sub>WDU</sub> x 0.5   | t <sub>WDU(max)</sub> x 0.5   | 0.85 x t <sub>WD</sub>                      | $t_{WDU(typ)}$ $t_{WDU(typ)}$ (1) | 1.15 x t <sub>WDU(typ)</sub> | S    |  |

Figure 6. Watchdog Timer Window Calculations

In the TPS3850 circuit, a 0.022- $\mu$ F capacitor is connected to the CWD pin to set  $t_{WDU(typ)}$ .  $t_{WDU(typ)}$  is calculated with Equation 2:

$$t_{WDU(typ)} = 77.4 \times C_{CWD} + 0.055$$

where

C<sub>CWD</sub> is in units of microfarads in this formula

(2)

Based on a nominal capacitor value of  $0.022~\mu F$ , a 1.7578 seconds  $t_{WDU(typ)}$  value results. If SET0 = 0 and SET1 = 0,  $t_{WDU(min)}$  = 1.49413 s,  $t_{WDU(max)}$  = 2.02147 s, and  $t_{WDL(min)}$  = 0.2527 s for the nominal capacitor value. As a result, if we are assuming the nominal  $0.22-\mu F$  capacitor value, the time between successive falling edges on the WDI pin should be from 0.2527-1.49413 seconds to prevent the WDO output of the TPS3850 from being asserted low. If the capacitor has a tolerance of  $\pm 10\%$ , the watchdog timer interval is decreased from 0.2527-1.49413 s to approximately 0.277-1.349 s. In the test software, the WDI pin of the TPS3850 is asserted so that the time between successive edges is normally approximately 1 second, which is within the 0.277-1.349 second watchdog timer window. If there is an issue with the MSP432 where the WDI pin is not asserted at the appropriate time, the WDO pin is asserted low.

In this design, the SET0 and SET1 state is set by adding jumpers to the J36 and J37 headers at the appropriate locations. To maximize the window between the lower and upper watchdog time intervals when the MSP432 is running, SET0 and SET1 are both connected to GND by placing jumpers at the appropriate locations on the J36 and J37 headers. When programming the MSP432 on this board, it is necessary to disable the watchdog feature of the TPS3850, which is done by setting SET0 = 1 and SET1 = 0.

The WDO output and RESET pins of the TPS3850 are connected together in this design. Since the WDO and RESET pins are open-drain, by connecting these pins together and then connecting the shared connection to the RST pin of the MSP432, the TPS3850 is able to reset the MSP432 whenever the WDO or RESET pin of the TPS3850 is asserted low. Because the WDO and RESET pins are open-drain, a pullup resistor is needed from this shared connection to VDD. Since the pins are connected to each other, only one pullup resistor is needed. This pullup resistor is set to be 47-k $\Omega$  based on the recommended JTAG circuit of the MSP432. The pullup resistor is not shown in Figure 5 since this is located in the JTAG portion of the schematic instead.

#### 2.3.1.2 Analog Inputs

The design of the front end consists of the three AMC1106 chips used for measuring current, a 14-bit SAR ADC module (referred to as the ADC14 module) integrated within the MSP432 for measuring the phase voltages, and a MSP432 timer for synchronizing the AMC1210 with the SAR ADC of the MSP432.

For maximum accuracy, the AMC1106 requires that the input analog signal voltage does not exceed ±50 mV. In addition, the AMC1106 has differential inputs; therefore, the AC current signal from mains can be directly interfaced without the requirement for level shifters.

In contrast, the ADC14 module of the MSP432 has single-ended inputs that cannot accept voltages below 0 V. Therefore, the ADC14 requires that the sensed voltage is between 0-V<sub>REF</sub> volts, with the option to select the V<sub>RFF</sub> source and voltage in the software. As a result, after the mains voltage is divided down for sensing, the voltage front-end circuitry requires a level shifter to properly interface to the ADC14 module.

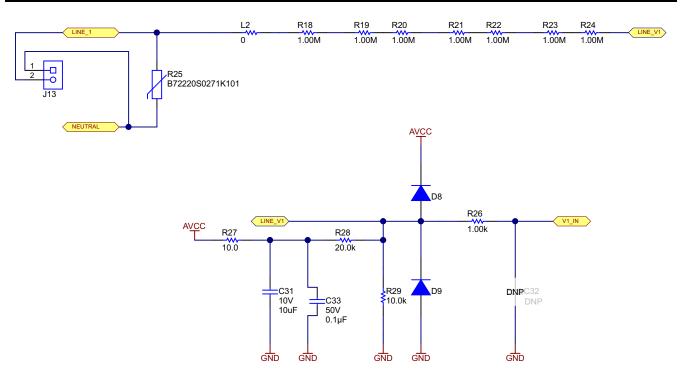

#### 2.3.1.2.1 Voltage Analog Front-End

The voltage from the mains is usually 230 V or 120 V and must be brought down to within 0-V<sub>REF</sub> volts. Because Mains is a signal with negative and positive voltages but the selected SAR ADC cannot take negative voltages, the voltage front-end circuit requires that a level shifter is used in addition to the voltage division scheme that is used. The analog front-end for voltage in this design consists of spike protection varistors, voltage divider and shifter network, and a RC low-pass filter that functions like an anti-alias filter.

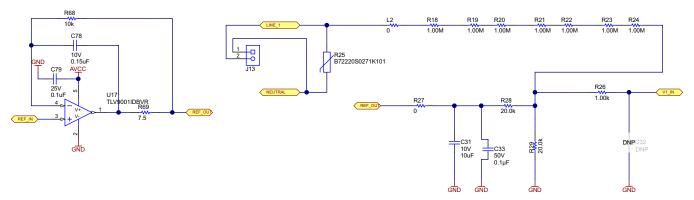

Figure 7 shows the analog front-end used in this design for one-phase for the voltage inputs for a mains voltage of 230 V. The voltage is brought down and shifted to a range within 0-V<sub>RFF</sub> volts, where V<sub>RFF</sub> is selected to be the 1.2-V reference produced by the internal reference module of the MSP432. In this circuit, only one op amp is needed for all three phases. One Mains voltage divider and reference voltage divider is needed for each phase (three in total).

Figure 7. Analog Front-End for Voltage Inputs

In the voltage analog front-end circuit, the voltage reference used by the SAR ADC is output by the MSP432 and fed to a TLV9001 op amp, which acts as a buffer. The output from the op amp is then fed to a voltage divider to generate a  $V_{REF}$  / 2 offset voltage that the signals fed to the SAR ADC are shifted by. The op amp is used to drive the reference voltage divider circuit instead of using the direct reference voltage output from the microcontroller because the reference voltage output of the microcontroller can only drive loads less than 10 μA of current, as Figure 8 shows. This 10-μA maximum load current is not enough to drive the reference voltage divider, which is why an op amp is used as a buffer by connecting the reference voltage output to the input of the op amp and connecting the output of the op amp to the reference voltage divider.

| PARAMETER                                                         | TEST CONDITIONS                                                                                                  | V <sub>CC</sub> | MIN   | TYP | MAX | UNIT |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------|-------|-----|-----|------|

| I <sub>O(REF+)</sub> VREF maximum load current,<br>VREF+ terminal | REFVSEL = (0, 1, 3),<br>AV <sub>CC</sub> = AV <sub>CC(MIN)</sub> for each reference level,<br>REFON = REFOUT = 1 |                 | -1000 |     | 10  | μΑ   |

Figure 8. Maximum Load Current of Reference Voltage Output on MSP432

To calculate the voltage that is fed to the SAR ADC of the MSP432 (V1\_IN in Figure 7 or VADC in the following formulas) when using the voltage front-end circuit as Figure 7 shows, the following equations are used:

$$R_{S} = R_{18} + R_{19} + R_{20} + R_{21} + R_{22} + R_{23} + R_{24}$$

$$R_{S} \times R_{20}$$

(3)

$$R_{eq1} = \frac{R_S \times R_{29}}{R_S + R_{29}} \tag{4}$$

$$V_{\text{offset}} = V_{\text{reference}} \left( \frac{R_{\text{eq1}}}{R_{\text{eq1}} + R_{28}} \right) \approx V_{\text{reference}} \left( \frac{R_{29}}{R_{29} + R_{28}} \right)$$

(5)

$$V_{\text{peak}} = V_{\text{RMS}} \times \sqrt{2}$$

(6)

$$R_{eq2} = \frac{R_{28} \times R_{29}}{R_{28} + R_{29}} \tag{7}$$

$$V_{ADC\_Swing} = V_{peak} \left( \frac{R_{eq2}}{R_{eq2} + R_{S}} \right)$$

(8)

$$V_{ADC} = V_{offset} \pm V_{ADC\_Swing}$$

(9)

To determine the voltage swing from the offset voltage,  $V_{ADC\_Swing}$ , the voltage that is fed into the SAR ADC of the MSP432 can be thought as a voltage divider with the Mains voltage as the voltage source to the following series resistors:  $R_s$  (R18 + R19 + R20 + R21 + R22 + R23 + R24)and  $R_{eq2}$  (the equivalent resistor for the parallel combination of R28 and R29).  $V_{ADC\_Swing}$  is the voltage across  $R_{eq2}$  within the Mains voltage divider. If we apply a 230  $V_{RMS}$  signal to the voltage front-end circuit in Figure 7 and a 1.2-V reference is used, based on the formulas above  $V_{offset} \approx 0.6$  V and  $V_{ADC\_Swing} \approx \pm 0.464$  V. As a result, the voltage fed to the SAR ADC is from 0.136 V to 1.064 V, which is within the 0- to 1.2-V input range for the SAR ADC for the selected 1.2-V reference.

In the  $V_{\text{offset}}$  formula, an ideal op amp with zero offset voltage is assumed; however, a real op amp has an offset adds to  $V_{\text{offset}}$ . For the  $V_{\text{REF}}$  voltage divider and op-amp implementation, the TLV9001 device was specifically selected for the reference buffer in this design because of its low cost and the low offset voltage of this op amp for the given cost, which enables the accurate generation of the  $V_{\text{REF}}$  / 2 offset needed for level shifting the signals fed into the SAR ADC.

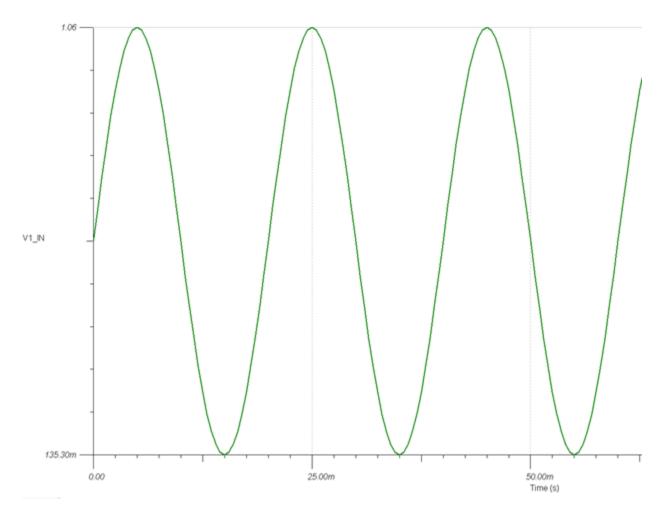

In the design files of this reference design, a voltage front-end simulation file is included, which can be used to simulate the expected waveforms that are fed into the SAR ADC given the selected op amp and input Mains voltage. Figure 9 shows the V1\_IN simulation waveform obtained with the simulation file and the conditions used for the calculations in this section. From these results, it can be observed that the simulation waveform closely matches the calculations in Equation 3 to Equation 9 of the range of voltages that are fed into the SAR ADC.

Figure 9. Simulated Waveform for Voltage Front-end Circuit

Using this voltage front-end circuit and selected values of  $V_{\text{ADC\_Swing}}$ , Mains peak voltage ( $V_{\text{peak})_{,}}$  and  $R_{\text{S}}$ , the resistor values to be used in the voltage front-end circuit can be calculated by first calculating  $R_{\text{eq2}}$  from the formulas in Equation 3 to Equation 9. If  $R_{\text{S}} >> R_{29}$ , the offset voltage that the SAR ADC waveform is shifted by ( $V_{\text{offset}}$ ) can be approximated using a voltage divider equation, where the reference voltage is the voltage source and only R28 and R29 are the series resistors. Given this approximation, select the same resistance value for R28 and R29 to generate a  $V_{\text{REF}}$  / 2 offset voltage, which means that R28 and R29 should be selected to have twice the resistance value of the calculated  $R_{\text{eo2}}$  value.

An alternative implementation for level shifting is to try to create the desired  $V_{REF}$  / 2 level shift voltage by an AVCC based voltage divider, as Figure 10 shows, instead of a  $V_{REF}$  based voltage divider. This AVCC based implementation does not require an op amp; however, with this AVCC-based implementation, in many cases the resistance value options available for the resistors in the AVCC voltage divider cannot accurately create the ideal  $V_{REF}$  / 2 offset voltage like the  $V_{REF}$  voltage divider and op-amp implementation. As an example, Figure 10 was designed for a 2-V reference so a 1.0 V  $V_{offset}$  value would be ideal; however, given the selected resistor values and a 3.3-V AVCC value, an offset of approximately 1.1 V results instead of 1.0 V. As a result, the AVCC voltage divider implementation has an offset in ADC readings that could cause voltage readings longer to settle and also cause not being able to use the full ADC range when compared to the  $V_{REF}$  voltage divider and op-amp implementation. These disadvantages of the AVCC voltage divider implementation for level shifting is why the  $V_{REF}$  voltage divider and op-amp implementation in Figure 7 is utilized for the PCB revision used in this design instead of the AVCC based voltage divider and no op-amp implementation in Figure 10.

Figure 10. Alternative Analog Front-End for Voltage Inputs Not Used in Design

#### 2.3.1.2.2 Current Front-End

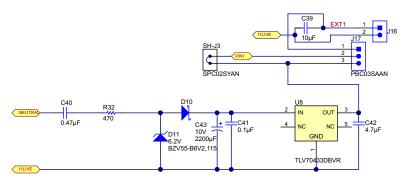

#### 2.3.1.2.2.1 AMC1106 High-Side Power Supply

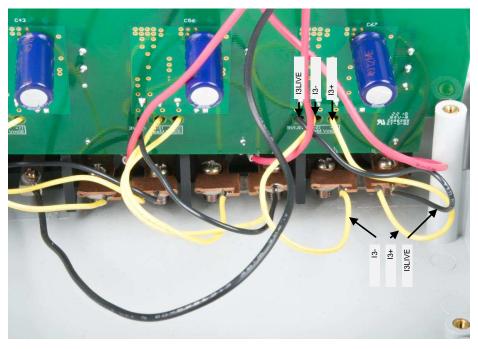

To sense the voltage across the shunt, the high-side of each AMC1106 device must be powered. Because each AMC1106 should be referenced from a different line, a different power supply is required for each AMC1106. In this design, there are two options for powering the high-side of the AMC1106 devices: an onboard half-bridge cap-drop power supply or an off-board, custom power supply.

There are multiple advantages to using the onboard cap-drop high-side power supply. First, this cap-drop power supply does not have any magnetic components so the power supply should be magnetically immune to magnetic fields instead of only being magnetically tolerant to a certain limit. Additionally, cap-drop supplies are relatively inexpensive compared to alternative power supply options. Also, LDO-based cap-drop power supplies inherently have low conducted and radiated emissions compared to SMPS power supplies. Finally, because the power to each AMC1106 high side is derived directly from mains instead of from the controller-side power supply, less current is drawn from the controller-side power supply allowing the specifications on the controller-side power supply maximum current drive capability to be relaxed.

Figure 11 shows the implementation of the half-bridge cap-drop high-side power supply in the design. In this implementation, VIN1, which is the regulated output from the TLV70433 LDO, is fed directly into the AVDD pin of the AMC1106 to provide power to it. As an alternative to using the onboard cap-drop power supply, the design has the option to instead power the AMC1106 by providing the necessary 3.3 V or 5 V from an external isolated voltage supply to the associated terminal block (J26 in Figure 11).

Figure 11. AMC1106 High-Side Power Options

Minimizing the modulation clock frequency reduces the current consumption of the AMC high-side, thereby allowing the relaxation of the maximum current drive specification on the cap-drop supply. For this design, the modulation clock frequency is selected to be 6 MHz because this is the minimum clock frequency that can be derived from the clocks of the MSP432 clocks that is still above the 5-MHz minimum modulation clock frequency necessary for the AMC1106 to function. In this design, the onboard cap-drop power supplies are able to power the high-side of the AMC devices for voltages as low as 80  $V_{\rm RMS}$  at 50 and 60 Hz .

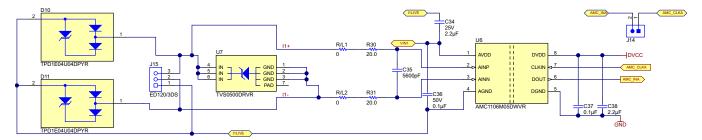

#### 2.3.1.2.2.2 Current Sensing

The analog front-end for current inputs is different from the analog front-end for the voltage inputs. Figure 12 shows the analog front-end used for a current channel.

Figure 12. Analog Front-End for Current Inputs

The analog front-end for current consists of supplemental TPD1E04U04 ESD protection diodes, a supplemental TVS0500 surge protection diode, footprints (R/L1 and R/L2) that could be replaced with inductors for EMI suppression (these footprints are populated with  $0-\Omega$  resistors by default), an anti-alias filter (R30, R31, and C35), and the AMC1106 isolated delta-sigma modulator.

In Figure 12, the three-terminal shunt used for current measurement is to be connected to J15. The value of this shunt is selected based on balancing maximizing the peak analog voltage input into the AMC1106 with minimizing the power dissipation of the shunt. In particular, for optimal accuracy, the peak DC voltage fed into the AMC must be as close as possible to 50 mV without surpassing this voltage. This peak voltage is dependent on the rated maximum current of the system and the resistance of the selected shunt. For example, this design uses 400- $\mu\Omega$  shunts . With these 400- $\mu\Omega$  shunts and a maximum RMS current of 90 A, the maximum DC voltage fed into the AMC is 90 ×  $\sqrt{2}$  × (400 × 10<sup>-6</sup>) ≈ 50 mV. To minimize the power dissipation in the shunt, a smaller value shunt can also be used. In this design, 220- $\mu\Omega$  shunts are also used. However, by using smaller value shunts, the voltage fed into the AMC is also reduced. As a result, there is a tradeoff in accuracy. Based on the requirements of the system, the tradeoff in accuracy from using a shunt with a small resistance and the reduced power dissipation from choosing the smaller shunt must be taken into account when selecting the proper shunt value.

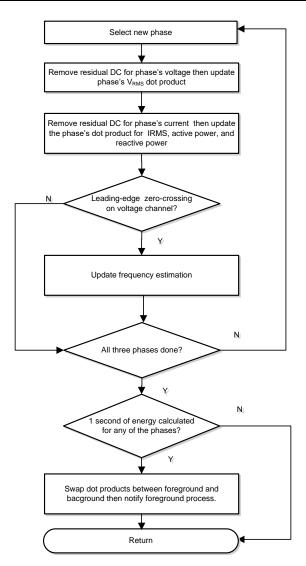

# 2.3.2 How to implement software for metrology testing

The MSP432 software used for evaluating this design is test software. This section discusses the features of the test software, which should provide insights on how to implement custom software for metrology testing. The first subsection discusses the setup of the AMC1210 and various peripherals on the MSP432. Subsequently, the metrology software is described as two major processes: the foreground process and background process.

# 2.3.2.1 Setup

#### 2.3.2.1.1 Clock

The MSP432 is configured to have its CPU clock (MCLK) set at 48 MHz and its subsystem master clock (SMCLK) set to 6 MHz. The clock source for MCLK and SMCLK is an external 48-MHz crystal. An external 32.768-kHz crystal is used as the clock source for the auxiliary clock (ACLK) of the device. This ACLK clock is set to a frequency of 32.768 kHz.

# 2.3.2.1.2 Port Map

The MSP432 has a port mapping controller that allows a flexible mapping of digital functions to port pins. The set of digital functions that can be ported to other pins is dependent on the device. For the MSP432 device in particular, the EUSCIB0 SPI module's SPI clock, SOMI, and SIMO functionality are all available options to port to ports P2, P3, and P7. In addition, the SMCLK clock output and SAR ADC triggering timer output are also available for output to ports P2, P3, and P7. In the test software, this port mapping feature is used for providing flexibility in the PCB layout.

Using the port mapping controller, the following mappings are used:

- PMAP\_UCB0SIMO (EUSCIB0 SPI SIMO) → Port P2.2 (connected to the AD0 pin of the AMC1210)

- PMAP UCB0CLK (EUSCIB0 SPI Clock) → Port P2.3 (connected to the WR pin of the AMC1210)

- PMAP UCB0SOMI (EUSCIB0 SPI SOMI) → Port P2.4 (connected to the RD pin of the AMC1210)

- PMAP\_SMCLK (SMCLK clock output) → Port P2.6 (connected to CLK pin of the AMC1210 so that it

can be used as the modulator clock of the AMC1210 and AMC1106 devices; however, please note

that this mapping is not enabled initially and is only enabled after the AMC1210 and SAR ADC have

been initialized)

- PMAP\_TA0CCR1A (timer output used to trigger SAR ADC )→ Port P2.7 (this is not connecting to anything on the AMC1210 and is only used for debugging purposes)

# 2.3.2.1.3 UART Setup for GUI Communication

The MSP432 is configured to communicate to the PC GUI through the RS-232 connection on this reference design. The MSP432 communicates to the PC GUI using a UART module configured for 8N1 at 9600 baud.

# 2.3.2.1.4 Real Time Clock (RTC)

The real-time clock module of the MSP432 is configured to give precise one second interrupts and update the time and date as necessary. Based off of these one second interrupts, a flag is updated to let the foreground process know when to output a high logic level on the WDI pin. After setting the WDI pin high, a timer is triggered that is used to toggle the logic level on the WDI pin back to a low logic state. Providing this pulse on the WDI pin of the TPS3850 is used to prevent the TPS3850 from resetting the MSP432.

#### 2.3.2.1.5 LCD Controller

The LCD controller on the MSP432P4111 can support up to 8-mux displays and 320 segments or 4-mux displays and 176 segment displays. In the current design, the LCD controller is configured to work in 4-mux mode using 144 segments. The eight segment lines not used in the 4-mux mode of this design are used for the port mapping functionality. In this reference design, the LCD is configured for a refresh rate set to ACLK / 64, which is 512 Hz. For contrast control, external resistors are added between the R23, R13, R03 pins and GND, as Figure 13 shows.

Figure 13. LCD External Resistors

# 2.3.2.1.6 Direct Memory Access (DMA)

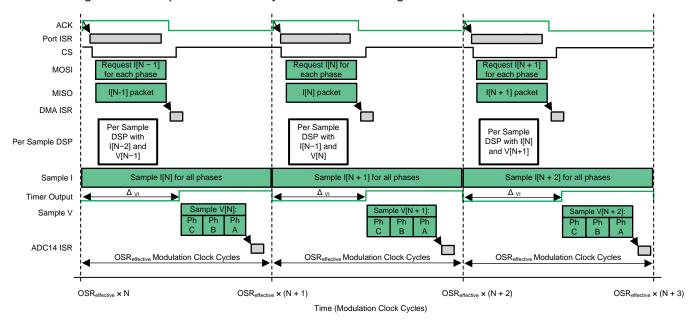

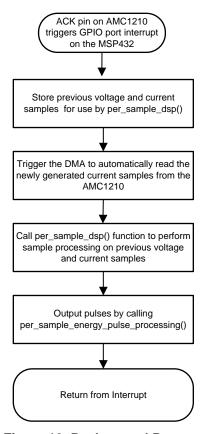

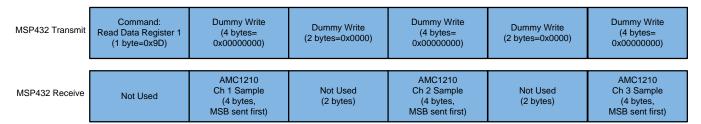

The direct memory access (DMA) module transfers packets between the MSP432 and AMC1210 with minimal bandwidth requirements from the MSP432 CPU. Two DMA channels are used for communicating to the AMC1210. One channel (channel 0) is used to send data to the AMC1210 and the other channel (channel 1) is used to receive data from the AMC1210. Once a complete packet has been received from the AMC1210, an interrupt is generated to complete any necessary post-transfer processing. Figure 19 shows the packets that are sent and received using the DMA of the MSP432.

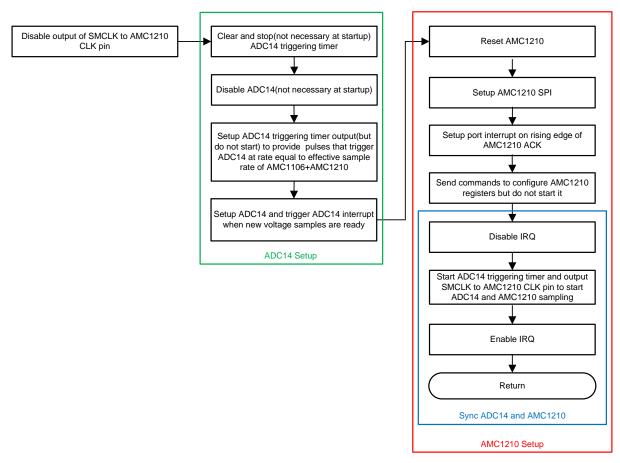

#### 2.3.2.1.7 ADC Setup

To get synchronized voltage and current samples, the AMC1210 device and the ADC14 module of the MSP432 must be properly initialized. Figure 14 shows the process that is followed in this design to initialize and synchronize the AMC1210 and the ADC14 module of the MSP432. Before setting up the AMC1210 and the ADC14 module of the MSP432, the modulator clock of the AMC1106 is disabled to prevent the AMC1210 from generating new samples while trying to set it up. After this, the ADC14 module of the MSP432 is setup, the AMC1210 device is setup, and then the ADC14 module and AMC1210 are synchronized and started. The following sections provide details on this process.

Figure 14. ADC Initialization and Synchronization Process

# 2.3.2.1.7.1 ADC14 Setup

The ADC14 is used to sample the three phase voltages and is triggered by the output of a timer. When setting up the ADC14, the ADC14 and triggering timer settings are reset in case the ADC14 and timer were previously initialized. After resetting the ADC14 and triggering timer, the triggering timer and its output that is used to trigger the timer are first initialized. Specifically, timer A0 is the triggering timer and its OUT1 (also referred to as TA0.1, TA0CCR1A, or TA0 CCR1 compare output OUT1) output is the specific output that triggers the SAR ADC using pulses.

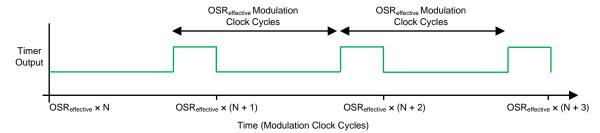

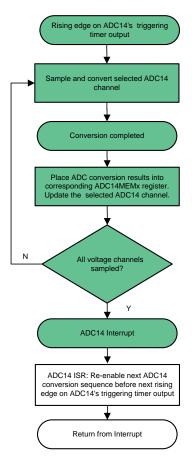

To synchronize the voltage and current samples, the clock source of Timer A0 is set to the SMCLK clock, which is also used as the modulator clock by the AMC1106 devices and the AMC1210. Timer A0 counts SMCLK clock cycles until the number of clock cycles counted equals the effective oversampling ratio (EOSR) of the AMC1210, where the EOSR is the ratio of the modulation clock frequency to the effective sample rate of the AMC1210. As a result of counting up to the EOSR number of SMCLK clock cycles, the frequency of the pulses on the OUT1 pin is equal to the effective sample rate of the AMC1210.

The falling edge of the OUT1 pulses will occur right after timer A0 has just counted EOSR SMCLK clock cycles. The OUT1 rising edge, which is what actually triggers the SAR ADC, is set to occur before the OUT1 falling edge occurs in the present cycle. The location of the rising edge does not affect the OUT1 pulse frequency like the OUT1 falling edge so the OUT1 rising edge can occur anywhere within the present cycle before the OUT1 falling edge occurs as long as the time interval between rising edges is always fixed, similar to the example waveform as Figure 15 shows. It is important that the interval between OUT1 rising edges is fixed to ensure that the delay between voltage and current samples is also fixed and not variable, which is necessary for accurately calculating power and energy-based metrology readings. By having both the rising edge and falling edge of the ADC triggering output set in hardware using a timer instead of doing it manually in software, a fixed time between rising edges on the triggering output is created. To ensure that there is one set of voltage ADC samples for each pulse on OUT1, the total time to

sample all the phase voltages should be less than the time between two pulses on the OUT1 pin. Since in this design the OUT1 pulses trigger the SAR ADC and the total sample time for the phase voltages is less than the time between OUT1 pulses, the sample rate of the SAR ADC is equal to the sample rate of the current samples from the AMC1210, which is necessary for synchronizing the voltage and current samples.

Figure 15. Example Waveform for Triggering Timer Output

Please note that after setting up the triggering timer , the timer is not started until after the ADC14 and AMC1210 are initialized and ready to be synchronized with each other. When setting up the ADC14, the ADC14 is configured to be in autoscan mode, which is a mode that allows the ADC14 to sample all the voltage channels sequentially every time conversions are triggered by the timer output. In the test software, the clock to the ADC14 is set to 3 MHz. Also, the conversion time for each sample is set so that the time it takes to sample all three voltage samples is much smaller than the time it takes to get one sample from the AMC1210. Specifically, the sample and hold time for each converter is 4 cycles and the conversion time is 16 cycles, which results in an approximate 20-cycle (approximately 7  $\mu$ s) delay between conversion results of adjacent converters. The ADC14 is configured to generate an interrupt when a complete sequence of voltage samples are ready.

In the design, the ADC14 selects its reference voltage to be the 1.2-V reference from the REF\_A module of the MSP432. This reference voltage is also output on a pin of the MSP432 so that it can be fed into the TLV9001 op amp for level shifting the voltage waveforms fed into the SAR ADC.

Additionally, the ADC14 is configured so that its 14-bit results are scaled to 16-bit twos complement numbers. This configuration allows the ADC results from the ADC14 to be treated as a 16-bit signed number when performing mathematical operations.

In this application, the following are the relevant ADC14 channel associations:

- A2 → Voltage V1 (Phase A)

- A1 → Voltage V2 (Phase B)

- A0 → Voltage V3 (Phase C)

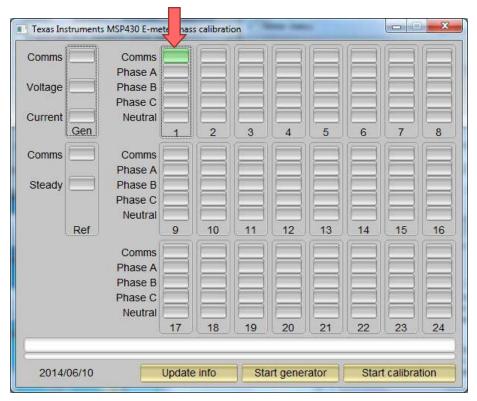

# 2.3.2.1.7.2 AMC1210 Setup

After the ADC14 is initialized, the AMC1210 is then reset to get the device in a known state before initializing it. Next, the EUSCIB0 SPI module of the MSP432 is configured for communication to the AMC1210. The EUSCIB0 SPI module is specifically configured as a master device that uses 3 wire mode (the chip select signal is manually asserted high and low in the test software instead of using the chip select feature of the SPI module) and has a 3-MHz SPI clock that is derived from the 6-MHz SMCLK clock. In addition, the MSP432 is also configured to generate a port interrupt whenever a rising edge occurs on the ACK pin, which would indicate that the AMC1210 has new current samples that are available.

With the communication interface of the MSP432 to the AMC1210 setup, the MSP432 then sends commands to the AMC1210 to configure it. Please note that the modulation clock is not output by the MSP432 to the AMC1210 and AMC1106 until the ADC14 and AMC1210 synchronization function is called, which means that current sampling will not be started until after the AMC1210 registers are initialized to their proper values. By sending commands to the AMC1210 to initialize the AMC1210 registers, the AMC1210 is configured for the following:

Three of the four AMC1210 digital filters are enabled. Filter module 1 is connected to the AMC1106 for Phase C, filter module 2 is connected to the AMC1106 for Phase B, and filter module 3 is connected to

the AMC1106 for Phase A. Filter module 4 is not used in this design but is brought out to a header on the board if it is desired to connect to an additional, external isolated modulator device.

- Each digital filter has a separate register that is used to store the most recent current samples. This data register is configured to be 32-bits instead of 16-bits.

- Each of the three AMC1210 digital filters are set to output the modulator clock that is fed to the "CLK" pin of the AMC1210 to the different CLKx pins of the AMC1210 once the modulator clock is finally output by the MSP432. Outputting the modulator clock to the different CLKx pins, allows the modulator clock to be output to the different AMC1106 devices without having to route this clock across the PCB.

- Each filter unit of the digital filter is set to use a SINC<sup>3</sup> digital filter with a sampling oversampling ratio (SOSR) of 128. The output from a filter unit of the digital filter is fed to its corresponding integrator unit. The integrator unit is configured to sum a user-defined number of samples from the filter unit, referred to as the integrator oversampling ratio (IOSR), to produce one effective sample. The IOSR for each digital filter is set to 8. With a SOSR of 128 and a IOSR of 8, an EOSR of 1024 results. Given a modulator clock frequency of 6 MHz, the 1024 EOSR value means that the effective sample rate of the AMC1210 is 6,000,000 / 1024 = 5859.4 Hz.

- Every time a new effective sample is ready from the AMC1210, the ACK pin of the AMC1210 is set to logic high until all of the current samples are read from the AMC1210 by the MSP432.

Once all of the AMC1210 registers have been initialized, the sync\_voltage\_and\_current function is called.

# 2.3.2.1.7.3 ADC14 and AMC1210 Synchronization

After the ADC14 module and AMC1210 registers are initialized, the sync\_voltage\_and\_current is called. This function first starts by disabling interrupts. Disabling interrupts is done to ensure that the timing of when the voltage starts with respect to current is not affected by interrupts so that this timing is always the same every time this function is called. After disabling interrupts, the triggering timer of the ADC14 is started, which enables the SAR ADC for sensing voltage. Next, the modulation clock is output by the MSP432 so that the AMC1106 and AMC1210 could start current sensing. After starting the ADC14 and AMC1210 devices on the MSP432, interrupts are then enabled again.

# 2.3.2.2 Foreground Process

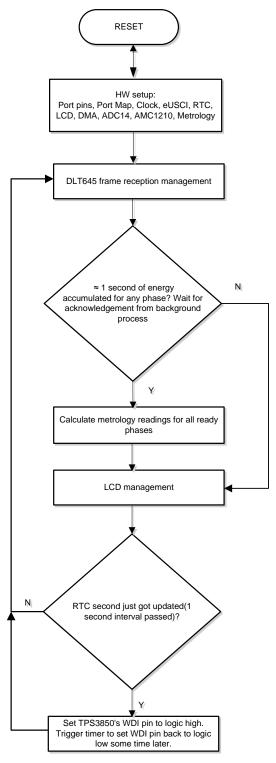

The foreground process includes the initial setup of the MSP432 hardware and software and the AMC1210 registers immediately after a device RESET. Figure 16 shows the flowchart for this process.

**Figure 16. Foreground Process**

The initialization routines involve the setup of the MSP432 general purpose input/output (GPIO) port pins and associated port map controller; MSP432 clock system; MSP432 USCI\_A0 for UART functionality; MSP432 RTC module for clock functionality; MSP432 LCD; MSP432 DMA; MSP432 ADC14 module; AMC1210 registers; and MSP432 metrology variables.

After the hardware is setup, any received frames from the GUI are processed. Subsequently, the foreground process checks whether the background process has notified the foreground process to calculate new metering parameters. This notification is accomplished through the assertion of the "PHASE\_STATUS\_NEW\_LOG" status flag whenever a frame of data is available for processing. The data frame consists of the processed dot products that were accumulated for approximately one second in the background process. This is equivalent to an accumulation of 50 or 60 cycles of data synchronized to the incoming voltage signal. In addition, a sample counter keeps track of how many samples accumulate over this frame period. This count can vary as the software synchronizes with the incoming mains frequency.

The processed dot products include the  $V_{\text{RMS}}$ ,  $I_{\text{RMS}}$ , active power, and reactive power. These dot products are used by the foreground process to calculate the corresponding metrology readings in real-world units. Processed voltage dot products are accumulated in 48-bit registers. In contrast, processed current dot products, active energy dot products, and reactive energy dot products are accumulated in separate 64-bit registers to further process and obtain the RMS and mean values. Using the calculated values of active and reactive power of the foreground process, the apparent power is calculated. The frequency (in Hz) and power factor are also calculated using parameters calculated by the background process using the formulas in Section 2.3.2.2.1.

The foreground process also updates the LCD. The LCD display item is changed every two seconds. See Section 3.1.4.2.1 for more information about the different items displayed on the LCD.

In addition, the foreground process checks if a one-second RTC flag is set. This flag is set at a rate of once a second within the RTC ISR. If this flag is asserted, the MSP432 sets its GPIO pin that is connected to the WDI pin of the TPS3850 to a logic high. Once this GPIO pin is set to logic high, a timer is triggered, which is used to let the MSP432 know when to set the GPIO pin state back to logic low.

#### 2.3.2.2.1 Formulae

This section briefly describes the formulas used for the voltage, current, power, and energy calculations. As previously described, voltage and current samples are obtained at a sampling rate of 5859.4 Hz. All of the samples that are taken in approximately one second frames are kept and used to obtain the RMS values for voltage and current for each phase. The RMS values are obtained with the following formulas:

$$V_{RMS,ph} = K_{v,ph} \times \sqrt{\frac{\displaystyle\sum_{n=1}^{Sample} v_{ph}(n) \times v_{ph}(n)}{Sample \ count}} - v_{offset,ph}$$

$$I_{RMS,ph} = K_{i,ph} \times \sqrt{\frac{\displaystyle\sum_{n=1}^{Sample} i_{ph}(n) \times i_{ph}(n)}{Sample \ count}} - i_{offset,ph}$$

$$(10)$$

where

- ph = Phase parameters that are being calculated [that is, Phase A (= 1), B (= 2), or C (= 3)],

- V<sub>ph</sub>(n) = Voltage sample at a sample instant n,

- V<sub>offset,ph</sub> = Offset used to subtract effects of the additive white Gaussian noise from the voltage converter,

- I<sub>ph</sub>(n) = Each current sample at a sample instant n,

- I<sub>offset.ph</sub> = Offset used to subtract effects of the additive white Gaussian noise from the current converter,

- Sample count = Number of samples within the present frame,

K<sub>v,ph</sub> = Scaling factor for voltage,

•

$$K_{i,oh}$$

= Scaling factor for current. (11)

Power and energy are calculated for active and reactive energy samples of one frame. These samples are phase corrected and passed on to the foreground process, which uses the number of samples (sample count) to calculate phase active and reactive powers through the following formulas:

$$P_{ACT,ph} = K_{ACT,ph} \frac{\sum_{n=1}^{Sample Count} v(n) \times i_{ph} (n)}{Sample Count} - P_{ACT\_Offset,ph}$$

(12)

$$P_{REACT,ph} = K_{REACT,ph} \frac{\sum_{n=1}^{Sample Count} V_{90,ph}(n) \times i_{ph}(n)}{Sample Count} - P_{React\_Offset,ph}$$

(13)

$$P_{APP,ph}^{2} = \sqrt{P_{ACT,ph}^{2} + P_{REACT,ph}^{2}}$$

where

- V<sub>90</sub>(n) = Voltage sample at a sample instant 'n' shifted by 90°,

- K<sub>ACT,ph</sub> = Scaling factor for active power,

- K<sub>REACT,ph</sub> = Scaling factor for reactive power,

- P<sub>ACT\_offset.ph</sub> = Offset used to subtract effects of crosstalk on the active power measurements from other phases and the neutral,

- P<sub>REACT\_offset,ph</sub> = Offset used to subtract effects of crosstalk on the reactive power measurements from other phases and the neutral. (14)

Note that for reactive energy, the 90° phase shift approach is used for two reasons:

- 1. This approach allows accurate measurement of the reactive power for very small currents.

- 2. This approach conforms to the measurement method specified by IEC and ANSI standards.

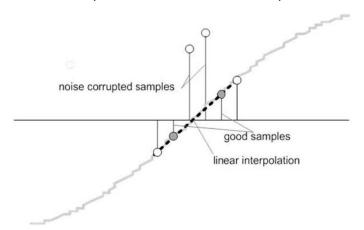

The calculated mains frequency is used to calculate the 90 degrees-shifted voltage sample. Because the frequency of the mains varies, the mains frequency is first measured accurately to phase shift the voltage samples accordingly.

To get an exact 90° phase shift, interpolation is used between two samples. For these two samples, a voltage sample slightly more than 90 degrees before the current sample and a voltage sample slightly less than 90 degrees before the current sample are used. The phase shift implementation of the application consists of an integer part and a fractional part. The integer part is realized by providing an N samples delay. The fractional part is realized by a one-tap FIR filter. In the test software, a lookup table provides the filter coefficients that are used to create the fractional delays.

In addition to calculating the per-phase active and reactive powers, the cumulative sum of these parameters are also calculated by the following Equation 15, Equation 16, and Equation 17:

$$P_{ACT,Cumulative} = \sum_{ph=1}^{3} P_{ACT,ph}$$

(15)

$$P_{REACT,Cumulative} = \sum_{ph=1}^{3} P_{REACT,ph}$$

(16)

$$P_{APP,Cumulative} = \sum_{ph=1}^{3} P_{APP,ph}$$

(17)

Using the calculated powers, energies are calculated with the following formulas in Equation 18:

$$E_{ACT,ph} = P_{ACT,ph} \times Sample count$$

$$E_{REACT.ph} = P_{REACT.ph} \times Sample count$$

$$E_{APP,ph} = P_{APP,ph} \times Sample count$$

(18)