Garrett Satterfield

#### Design Goals

| VCC | DAC Output<br>Voltage | Output Current | Error      | Maximum Resistive<br>Load |

|-----|-----------------------|----------------|------------|---------------------------|

| 5V  | 0mV – 510mV           | 0mA – 100mA    | <0.25% FSR | 44.9Ω                     |

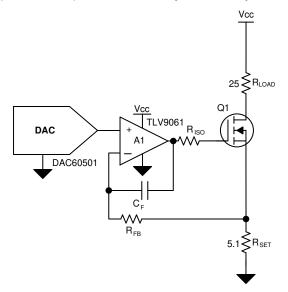

#### **Design Description**

The programmable low-side current sink sets the current through a load based on the DAC output voltage. The current is sensed through  $R_{SET}$  and the op amp biases a transistor regulate the current through the load. Components  $C_F$ ,  $R_{ISO}$ , and  $R_{FB}$  provide compensation to verify the stability of the circuit.

### **Design Notes**

- 1. Choose a DAC with low offset error, gain error, and drift. Use RRIO op amps to reduce error near the rails and maximize resistive load drive. Choose an op amp with low offset voltage to minimize error.

- 2. Use a high-precision, low-drift resistor for R<sub>SET</sub> for accurate current regulation.

- R<sub>SET</sub> should be minimized for efficiency and power dissipation. Most of the power dissipation should occur through R<sub>LOAD</sub>

- 4. To drive large R<sub>LOAD</sub>, use a separate high voltage supply for driving the current to the load.

#### **Design Steps**

1. Calculate the R<sub>SET</sub> value for the maximum DAC output voltage and desired maximum output current.

$$R_{SET} = \frac{V_{DAC,max}}{I_{OUT,max}} = \frac{510mV}{100mA} = 5.1\Omega$$

1

2. The maximum resistive load is given by:

$$R_{\text{LOAD,max}} = \frac{Vcc - I_{\text{SET,max}}R_{\text{SET}}}{I_{\text{SET,max}}} = \frac{5V - 100\text{mA} \times 5.1}{100\text{mA}} = 44.9\Omega$$

3. Verify that Q1 is rated for the power dissipation at maximum current.

$P_{\text{Diss},\text{Q2}} = \text{Vcc} \times \text{I}_{\text{SET},\text{max}} - \text{I}_{\text{SET},\text{max}}^2 \times (\text{R}_{\text{LOAD}} + \text{R}_{\text{SET}}) = 5\text{V} \times 100\text{mA} - 100\text{mA}^2 \times (25\Omega + 5.1\Omega) = 0.2\text{W}$

4. The output error can be approximated based on DAC TUE, amplifier offset voltage, resistor tolerance, and reference initial accuracy using root sum square (RSS) analysis.

Output TUE(%FSR) =

$$\sqrt{\text{TUE}_{DAC}^2 + \left(\frac{V_{OS,Amplifier}}{FSR} \times 100\right)^2 + \text{Tol}_{R_{SET}}^2 + \text{Accuracy}_{Ref}^2} = \sqrt{0.1^2 + \left(\frac{0.3mV}{510mV} \times 100\right)^2 + 0.1^2 + 0.1^2} = 0.183\%$$

FSR

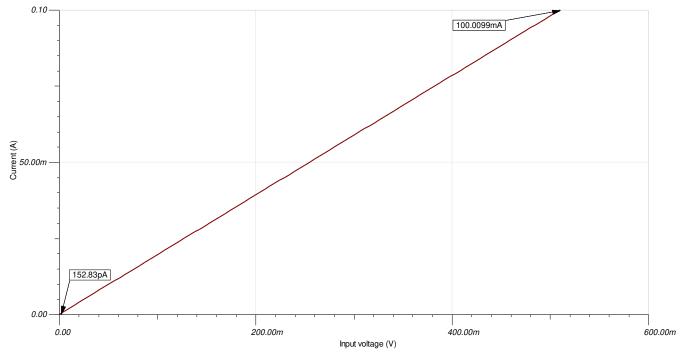

#### **DC Transfer Characteristic**

#### Trademarks

| Device     | Key Features                                                                                                  | Link                                                                                                    | Other Possible Devices              |

|------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------|

|            | Rey reatures                                                                                                  |                                                                                                         | Other Possible Devices              |

| DACs       |                                                                                                               |                                                                                                         |                                     |

| DAC60501   | 12-bit resolution, 1LSB INL, Single-Channel, Voltage Output DAC with 5ppm/°C Internal Reference               | True 12-bit, 1-ch, SPI/I2C, voltage-<br>output DAC in WSON package with<br>precision internal reference | Precision DACs (≤10 MSPS)           |

| DAC80501   | 16-bit resolution, 1LSB INL, Single-Channel, Voltage Output DAC with 5ppm/°C Internal Reference               | True 16-bit, 1-ch, SPI/I2C, voltage-<br>output DAC in WSON package with<br>precision internal reference | Precision DACs (≤10 MSPS)           |

| DAC8830    | 16-bit resolution, single channel, ultra-low power, unbuffered output, 1<br>LSB INL, SPI, 2.7V to 5.5V supply | 16-bit, single-channel, ultra-low power, voltage output DAC                                             | Precision DACs (≤10 MSPS)           |

| Amplifiers |                                                                                                               |                                                                                                         | ·                                   |

| TLV9061    | Ultra-Small, 0.3-mV Offset, Rail-to-Rail I/O, 1.8V to 5.5V supply                                             | Single, 5.5V, 10MHz, RRIO<br>operational amplifier for cost-<br>optimized applications                  | Operational amplifiers (op<br>amps) |

| OPA317     | Zero-Drift, Low-Offset, Rail-to-Rail I/O, 35-µA supply current max, 2.5V to 5.5V supply                       | Low Offset, Rail-to-Rail I/O<br>Operational Amplifier                                                   | Operational amplifiers (op<br>amps) |

| OPA388     | Precision, Zero-Drift, Zero-Crossover, Low Noise Rail-to-Rail I/O, 2.5V to 5.5V supply                        | Single, 10MHz, CMOS, zero-drift,<br>zero-crossover, true RRIO precision<br>operational amplifier        | Operational amplifiers (op<br>amps) |

# Trademarks

All trademarks are the property of their respective owners.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated