# AM62x-SIP SK Evaluation Module

# **Description**

The SK-AM62-SIP starter kit (SK) evaluation module (EVM) is a stand-alone test and development platform built around the AM6254 system-on-a-chip (SoC) with integrated 512MB LPDDR4 SDRAM in a single package. AM625SIP processors are comprised of a quad-core 64-bit Arm®-Cortex®-A53 microprocessor and single-core Arm Cortex-M4F MCU.

SK-AM62-SIP allows the user to experience a dual-display feature with 3D GPU through high-definition multimedia interface (HDMI<sup>™</sup>) over dots per inch (DPI) and low-voltage differential signaling (LVDS), as well as industrial communication applications using serial, Ethernet, USB and other interfaces.

# **Get Started**

- 1. Order the EVM at SK-AM62-SIP.

- 2. Download the EVM design files.

- 3. Download the reference software for many applications from AM62x Development Portal.

- 4. The EVM Users Guide is here.

### **Features**

- USB-C powered standalone mode of operation

- Power optimized discrete DC-DC power management

- Onboard XDS110 JTAG interface with USB connectivity for code development and debugging

- Onboard 32 GB eMMC memory and 512 Mb OSPI NOR Flash

- 2x RGMII RJ45 connectors

- 2x USB 2.0 on type A and type C connectors

- · Test automation interface through XDS110

- Expansion econnectors to access the interfaces

- M.2 connector for Wi-Fi/BT module

# 1 Evaluation Module Overview

### 1.1 Introduction

This technical User's Guide describes the hardware architecture of the SK-AM62-SIP EVM, a low cost Starter Kit built around the AM62x SIP SoC. The AM62x SIP processor comprises of a Quad-Core 64-bit Arm®-Cortex® A53 microprocessor, Single-core Arm Cortex-R5F MCU and an Arm Cortex-M4F MCU.

SK-AM62-SIP includes high-security field-securable (HS-FS) silicon to optionally customize keys and encryption for security applications.

SK-AM62-SIP can be used for display applications (for example, human machine interface (HMI) and control panel) with either an HDMI display and an external LVDS panel, up to 2K 60fps resolution. The powerful Arm performance of quad-A53 at 1.4 GHz with rich industrial interfaces, offers good control and communication capabilities for a wide range of applications, such as programmable logic controllers (PLC), automation control, gateway, EV charging, medical, or building automation systems.

### 1.2 Kit Contents

- SK-AM62-SIP EVM

- · EVM user guide pamphlet

- · EVM disclaimer and standard terms

# 1.3 Specification

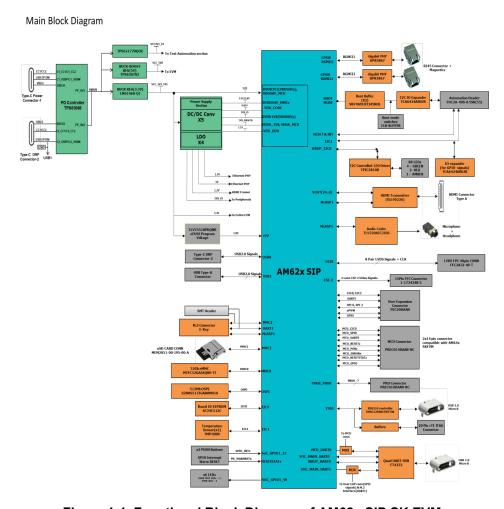

The figure below shows the functional block diagram of the AM62x SIP SK EVM.

Figure 1-1. Functional Block Diagram of AM62x SIP SK EVM

### 1.4 Device Information

In addition, SK-AM62-SIP can communicate with other processors or systems and act as a communication gateway. SK-AM62-SIP can directly operate as a standard remote I/O system or simple sensor connected to an industrial communication network.

The embedded emulation logic allows for emulation and debugging using standard development tools such as the Code Composer Studio<sup>™</sup> integrated development environment (IDE) (CCSTUDIO). Reference software for many applications can be downloaded from AM62x Development Portal.

Hardware Vincom

Vinco

# 2 Hardware

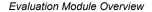

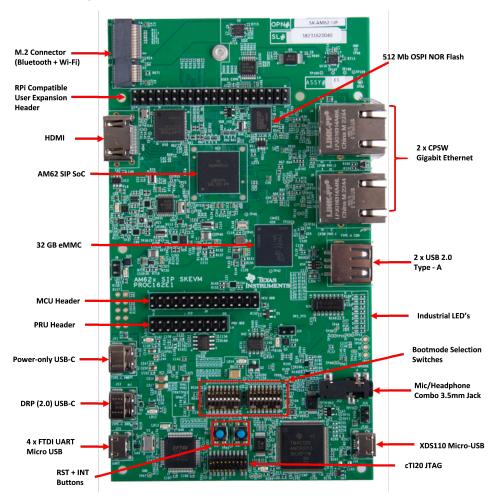

# 2.1 Additional Images

This section shows the EVM pictures and the location of various blocks on the board.

Figure 2-1. EVM Top Side

Figure 2-2. EVM Bottom Side

# 2.2 Key Features

The AM62x SIP SK EVM is a high performance, standalone development platform that enable users to evaluate and develop industrial applications for the Texas Instrument's AM62x SIP System-on-Chip (SoC).

The following sections discuss the SK EVM's key features.

### 2.2.1 Processor

AM62x SIPSoC, 13 mm x 13 mm, 0.5 mm pitch, 425-pin VCA FBGA

### 2.2.2 Power Supply

- Two USB Type-C ports (5 V-15 V input range)

- · Optimized power solution with discrete regulators and LDOs for the processor and peripherals

# **2.2.3 Memory**

- MicroSD Card slot with UHS-1 support

- 512MbitOctal SPI Flash memory

- 512Kbit Inter-Integrated Circuit (I2C) board ID EEPROM

- · 32GBeMMC Flash with HS-400 support

# 2.2.4 JTAG/Emulator

- XDS110 On-Board Emulator

- · Supports20-pin JTAG connection from external emulator

Hardware Very INSTRUMENTS

www.ti.com

# 2.2.5 Support Interfaces and Peripherals

- 1xUSB2.0 Type C interface, support DFP and UFP roles

- · 1xUSB2.0 Host interface, Type A

- 1xHDMI interface

- Audio line in and mic + headphone out

- M.2 Key E interface support for both Wi-Fi and Bluetooth modules

- 2x Gigabit Ethernet ports supporting 10/100/1000 Mbps data rate on two RJ45 connectors

- · Quadport UART to USB circuit over microB USB connector

- Industrial ethernet LEDs

- · INA devices for current monitoring

- 1x Temperature sensor near SoC for thermal monitoring

# 2.2.6 Expansion Connectors/Headers

- · CSI Camera Header

- · LVDS Display connector

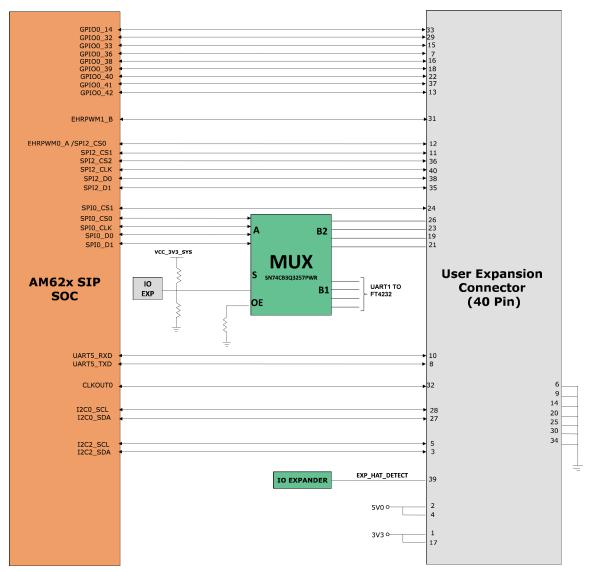

- · User Expansion connector

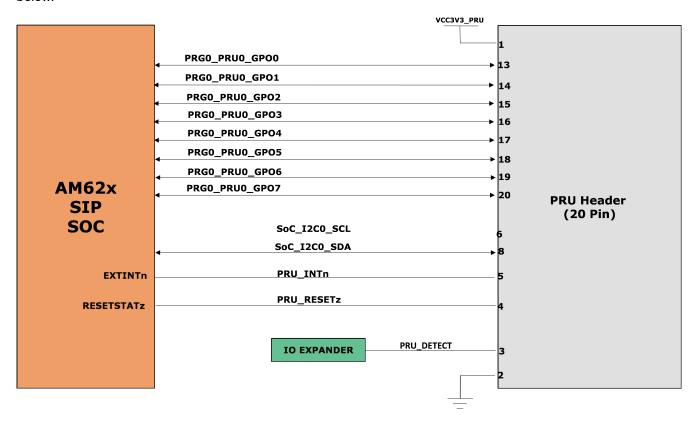

- PRU Header

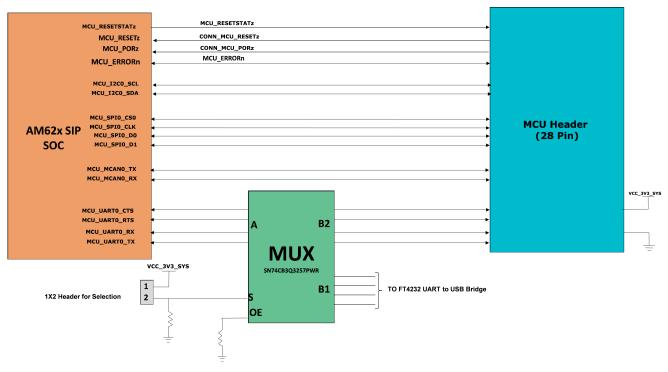

- MCU Header

# 2.3 Interface Mapping

**Table 2-1. Interface Mapping**

| Interface Name                      | Port on SoC                                                    | Device Part Number                             |

|-------------------------------------|----------------------------------------------------------------|------------------------------------------------|

| Memory – OSPI                       | OSPI0                                                          | S28HS512TGABHM010                              |

| Memory – Micro SD Socket            | MMC1                                                           | MEM2051-00-195-00-A                            |

| Memory – eMMC                       | MMC0                                                           | MTFC32GAZAQHD-IT                               |

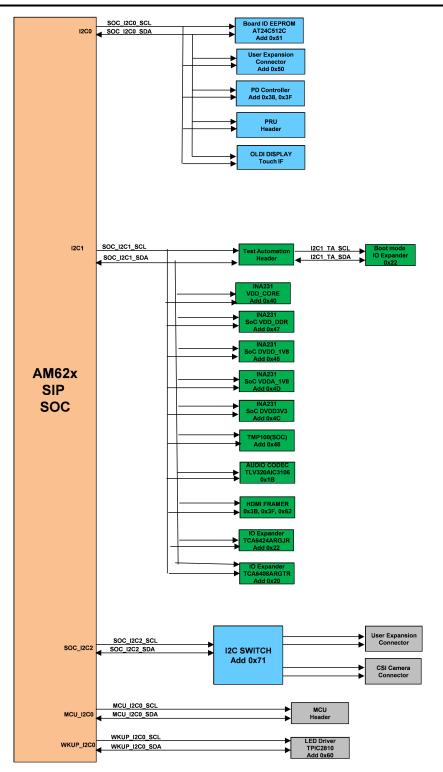

| Memory – Board ID EEPROM            | SoC_I2C0                                                       | AT24C512C-MAHM-T                               |

| Ethernet 1 – RGMII                  | SoC_RGMII1                                                     | DP83867IRRGZ                                   |

| Ethernet 2 – RGMII                  | SoC_RGMII2                                                     | DP83867IRRGZ                                   |

| LED Driver – 8 Communication LEDs   | WKUP_I2C0                                                      | TPIC2810D                                      |

| PRU Header – 2x10 HDR               | PR0_PRU0_GPO and SoC_I2C0                                      | PREC010DAAN-RC                                 |

| User Expansion Connector – 2x20 HDR | SPI0, SPI2, UART5, SoC_I2C0, SoC_I2C2 and GPIOs                | PEC20DAAN                                      |

| MCU Header – 2x14 HDR               | MCU_UART0,MCU_MCAN0, MCU_SPI0,<br>MCU_I2C0 and MCU GPIOs       | PREC014DAAN-RC                                 |

| USB- 2.0 Type C                     | USB0                                                           | 2012670005                                     |

| USB- 2.0 Type A                     | USB1                                                           | 629104151021                                   |

| LVDS Display Connector              | OLDI0                                                          | FFC2A32-40-T                                   |

| CSI Interface                       | CSI0                                                           | 1-1734248-5                                    |

| HDMI                                | VOUT0                                                          | Sil9022ACNU + TPD12S016PWR<br>+10029449-001RLF |

| AudioCodec                          | McASP2and SoC_I2C1                                             | TLV320AIC3106IRGZT+ SJ-43514-SMT               |

| GPIO Port Expander                  | SoC_I2C1                                                       | TCA6424ARGJR                                   |

| UART Terminal (UART-to-USB)         | 3) SoC_UART[1:0], WKUP_UART0 and FT4232HL+ 629105<br>MCU_UART0 |                                                |

| Test Automation Header              | SoC_I2C1                                                       | FH12A-40S-0.5SH                                |

| Temperature Sensor                  | SoC_I2C1                                                       | TMP100NA/3K                                    |

| Current Monitors                    | SoC_I2C1                                                       | INA231AIYFDR                                   |

| Connectivity– M.2 Key E             | MMC2, McASP1 and SoC_UART1                                     | 2199119-4                                      |

#### 2.4 Power ON/OFF Procedure

Power to the EVM is provided through an external power supply providing PD voltage and current to the either of the two USB Type-C Ports.

#### Note

The maximum length of the IO cables shall not exceed 3 meters.

#### 2.4.1 Power ON Procedure

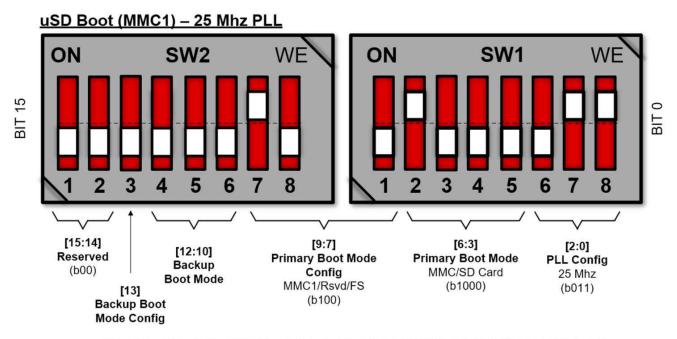

- 1. Place the SK EVM boot switch selectors (SW1, SW2) into selected boot mode. Example boot-modes for SDcard and no-boot are shown below.

- 2. Connect your boot media (if applicable).

- 3. Attach the PD capable USB Type-C cable to the SKEVM Type-C (J11 or J13) Connector.

- 4. Connect the other end of the Type-C cable to the source, either AC Power Adapter, or Type C source device (such as a Laptop computer).

- 5. Visually inspect that either LD10 or LD12 LED are illuminated.

- 6. XDS110JTAG and UART debug console output are routed to micro-USB ports J16 and J15, respectively.

Note: Actual Board Silkscreen May Appear Inverted in this Orientation. Follow Physical Switch Text

Figure 2-3. SD Boot Mode Switch Setting Example

#### 2.4.2 Power OFF Procedure

- 1. Disconnect AC power from AC/DC converter.

- 2. Remove the USB Type-C cable from the SK EVM.

**STRUMENTS** Hardware www.ti.com

### 2.4.3 Power Test Points

Test points for each power output on the board is mentioned in the table below.

**Table 2-2. Power Test Points**

| S.No | Power Supply   | Test Point | Voltage   |

|------|----------------|------------|-----------|

| 1    | VBUS_TYPEC1    | C398.1     | 5V-15V    |

| 2    | VBUS_TYPEC2    | C415.1     | 5V-15V    |

| 3    | VMAIN          | TP95       | 5V-15V    |

| 4    | VCC_5V0        | TP70       | 5 V       |

| 5    | VCC_3V3_SYS    | TP51       | 3.3V      |

| 6    | VDD_2V5        | TP42       | 2.5V      |

| 7    | VPP_1V8        | TP31       | 1.8V      |

| 8    | VDD_1V0        | TP33       | 1.0V      |

| 9    | VDD_1V2        | TP10       | 1.2V      |

| 10   | VDDA1V8        | TP36       | 1.8V      |

| 11   | VCC_1V8        | TP41       | 1.8V      |

| 12   | VDDSHV_SDIO    | TP29       | 1.8V/3.3V |

| 13   | VCC1V1_DDR     | TP40       | 1.1V      |

| 14   | VCC_CORE       | TP45       | 0.85V     |

| 15   | VDD_CORE       | TP46       | 0.85V     |

| 16   | VCC3V3_TA      | TP87       | 3.3V      |

| 17   | VCC3V3_XDS     | TP77       | 3.3V      |

| 18   | VCC_3V3_FT4232 | C482.1     | 3.3V      |

# 2.5 Clocking

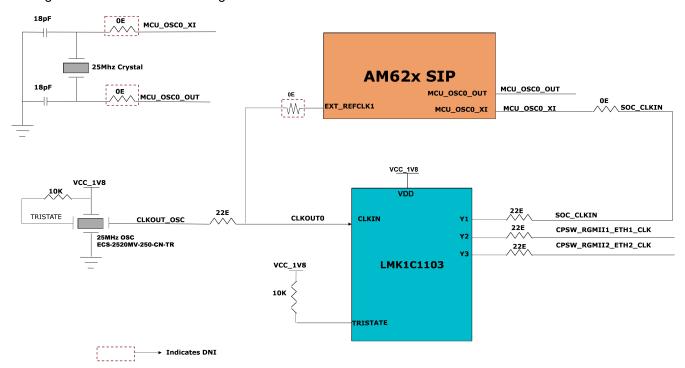

The figure below shows the clocking architecture of the AM62x SIP SK EVM.

Figure 2-4. Clock Architecture

A clock generator of part number LMK1C1103PWR is used to drive the 25 MHz clock to the SoC and two Ethernet PHYs. LMK1C1103PWR is a 1:3 LVCMOS clock buffer, which takes the 25 MHz crystal/LVCMOS reference input and provides three 25 MHz LVCMOS clock outputs. The source for the clock buffer shall be either the CLKOUT0 pin from the SoC or a 25 MHz oscillator; the selection is made using a set of resistors. By default, an oscillator is used as input to the clock buffer on the AM62x SIP SKEVM. Output Y2 and Y3 of the clock buffer are used as reference clock inputs] for two Gigabit Ethernet PHYs.

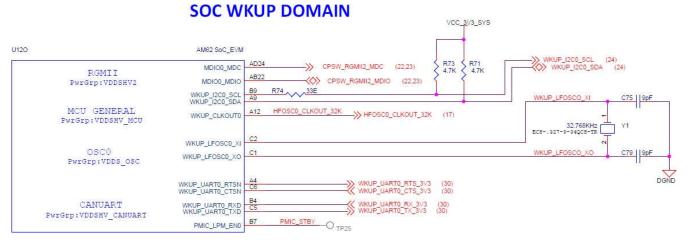

There is one external crystal attached to the AM62x SIP SoC to provide clock to the WKUP domain of the SoC (32.768 KHz).

Figure 2-5. SoC WKUP Domain

# 2.5.1 Peripheral Ref Clock

Clock inputs required for peripherals such as XDS110, FT4232, HDMI Transmitter and Audio Codecare generated locally using separate crystals or oscillators. Crystals or Oscillators used to provide the reference clocks to the EVM peripherals are shown in the table below.

| Peripheral       | Mfr. Part Number      | Description             | Frequency |

|------------------|-----------------------|-------------------------|-----------|

| XDS110 Emulator  | XRCGB16M000FXN01R0    | CRY 16.000MHz 8 pF SMD  | 16.000MHz |

| FT4232 Bridge    | ECS-120-18-30B-AGN-TR | CRY12.000 MHz 18 pF SMD | 12.000MHz |

| Audio Codec      | KC2520Z12.2880C1KX00  | OSC12.288 MHz CMOS SMD  | 12.288MHz |

| HDMI Transmitter | KC2520Z12.2880C1KX00  | OSC12.288 MHz CMOS SMD  | 12.288MHz |

Table 2-3. Clock Table

The clock required by the HDMI Transmitter can be provided by either the on board oscillator or the SoC's AUDIO\_EXT\_REFCLK1, which can be selected through a resistor mux. SoC's EXT\_REFCLK1 is used to provide clock to the User Expansion Connector on the SKEVM. The 32.768 KHz clock to the M.2 module is provided by WKUP CLKOUT0 of AM62x SIP SoC through a voltage translational buffer.

Instruments Hardware www.ti.com

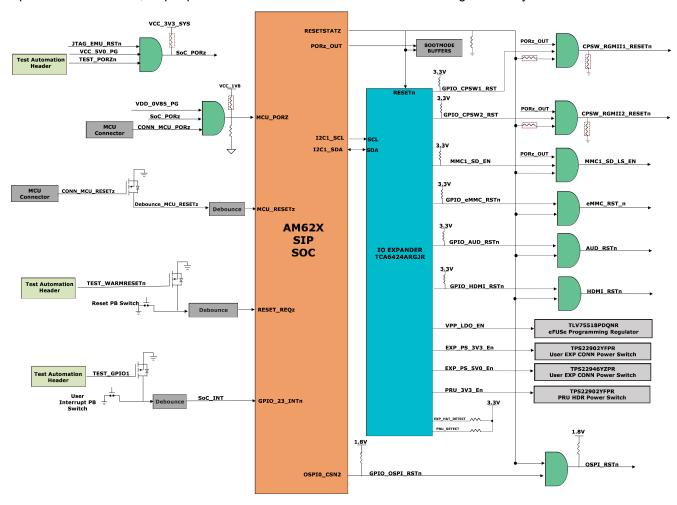

#### 2.6 Reset

The Reset Architecture of AM62x SIP SK EVM is shown below.

The SoC has following resets:

- RESETSTATz is the Main domain warm reset status output

- PORz OUT is the Main domain power ON reset status output

- RESET REQz is the Main domain warm reset input

- MCU\_PORz is the MCU domain power ON/ Cold Reset input

- MCU RESETz is the MCU domain warm reset input

- MCU RESETSTATz is the MCU domain warm reset status output

Upon Power on Reset, all peripheral devices connected to the main domain get reset by RESETSTATz.

Figure 2-6. Reset Architecture

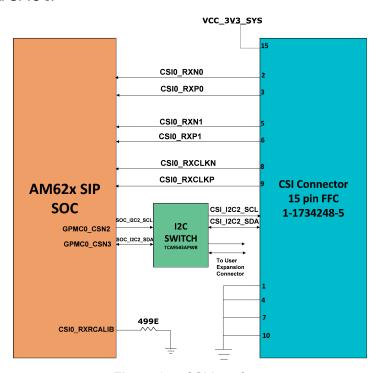

### 2.7 CSI Interface

The CSI-2 interface from the AM62x SIP SoC is terminated to a 15 pin Camera FPC connector 1-1734248-5 compatible with the RPi Camera Modules. These modules support 2 Lane CSI RX signals. While the SoC supports 4 CSI RX Lanes, only two are pinned out on the SK EVM.

The CSI connector pin-out is compatible with the RPi camera connector. The below table shows 15 pin CSI Connector pin-out. SoC I2C2 signals are also connected to the CSI Header. IO Expander GPIO signals are connected to the camera GPIO's.

Figure 2-7. CSI Interface

Table 2-4. CSI Camera Connector J19 Pinout

| Pin No. | Pin Description |  |

|---------|-----------------|--|

| 1       | GND             |  |

| 2       | CSI0_RXN0       |  |

| 3       | CSI0_RXP0       |  |

| 4       | GND             |  |

| 5       | CSI0_RXN1       |  |

| 6       | CSI0_RXP1       |  |

| 7       | GND             |  |

| 8       | CSI0_RXCLKN     |  |

| 9       | CSI0_RXCLKP     |  |

| 10      | GND             |  |

| 11      | CSI_GPIO1       |  |

| 12      | CSI_GPIO2       |  |

| 13      | CSI_I2C2_SCL    |  |

| 14      | CSI_I2C2_SDA    |  |

| 15      | VCC_3V3_SYS     |  |

Hardware www.ti.com

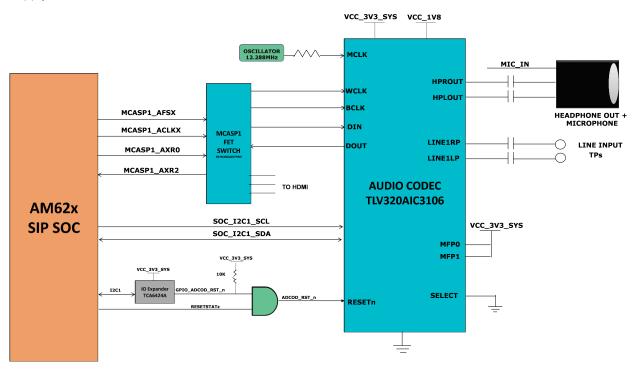

### 2.8 Audio Codec Interface

AM62x SIP SK EVM has TI's Low-Power TLV320AIC3106 Stereo Audio Codec to interface with AM62x SIP via McASP.

TLV320AIC3106 is a low-power stereo audio codec with stereo headphone amplifier, as well as multiple inputs and outputs programmable in single ended or fully differential configurations. The record path of the TLV320AIC3106 contains integrated microphone bias, digitally controlled stereo microphone preamplifier and automatic gain control (AGC) with mix/Mux capability among the multiple analog inputs. The stereo audio DAC supports sampling rates from 8 kHz to 96 kHz.

1xStandard 3.5 mm TRRS Audio Jack connector Mfr. Part# SJ-43514 shall be provided for MIC and Headphone output. Audio Codec's Line inputs are terminated to Test points.

SELECT pin shall be held LOW to select I2C as control interface. Codec can be configured over I2C interface, where I2C address can be set by driving pins MFP0 and MFP1 pin either high or low. Both these pins are set to high, so the Device address is set to 0x1B. Unused inputs and outputs of the Audio Codec are connected to ground.

The Controller Clock input, MCLK to the Audio Codec is provided through a 12.288MHz Oscillator. Audio serial data bus bit clock BCLK of the codec is driven by the AM62x SIP SoC through a buffer. Audio serial data bus input and output DIN, DOUT are connected to SoC's MCASP1 AXR0 and MCASP1 AXR2 through buffers. An AND output of RESETSTATz and a GPIO sourced via IO expander are used to reset the Audio codec.

The TLV 320 AIC 3106 is powered by an analog supply of 3.3 V, a digital core supply of 1.8 V, and a digital I/O supply 3.3 V.

Figure 2-8. Audio Codec Interface

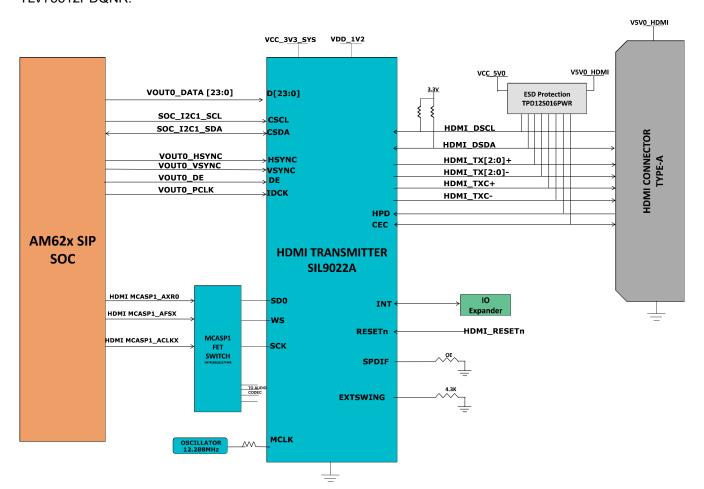

# 2.9 HDMI Display Interface

The DSS (Display Sub system) interface from AM62x SIP SoC is used on the SKEVM to provide a HDMI Interface through a standard Type-A Connector. The SKEVM features a SiI9022A HDMI Transmitter from Lattice semiconductors to convert the 24-bit Parallel RGB DSS output stream as well as a McASP to a HDMI-compliant digital audio and video signal.

The Data mapping format used is RGB888. The data bus width is 24-bits.

SoC\_I2C1 is connected to the HDMI Transmitter to access the compatible mode registers, the TPI registers, and the CPI registers. To use the SiI9022A, the SoC needs to set up the device by the I2C interface between the SoC and the SiI9022A. Audio Data is sent from SoC to HDMI transmitter through the McASP1 instance. HDMI I2C Bus accesses the EDID and HDCP data on an attached sink device.

TMDS Differential data pairs along with the differential clock signals from the transmitter are connected to the HDMI connector through HDMI ESD device Mfr Part# TPD12S016PWR which also acts as a load switch to limit current supplied to the HDMI connector from board 5 V supply.

The HDMI Framer is powered using 3.3 V Board IO Supply and 1.2 V by a dedicated LDO Mfr Part#-TLV75512PDQNR.

Figure 2-9. HDMI Interface

Hardware Www.ti.com

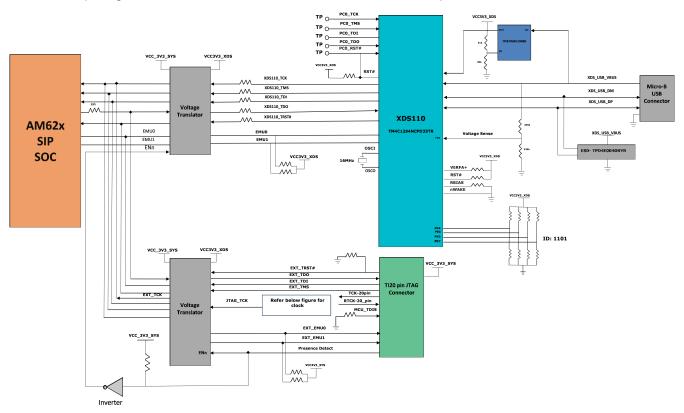

# 2.10 JTAG Interface

AM62x SIP SK EVM board include XDS110 class on board emulation. The connection for the emulator uses an USB 2.0 micro-B connector and the circuit act as a bus-powered USB device. The VBUS power from the connector is used to power the emulation circuit so that connection to the emulator is not lost when the power to the SK EVM is removed. Voltage translation buffers are used to isolate the XDS110 circuit from the rest of the SK EVM.

Optionally, JTAG Interface on SK EVM is also provided through 20 Pin Standard JTAG cTI Header J17. This allows the user to connect an external JTAG Emulator Cable. Voltage translation buffers are used to isolate the JTAG signals from cTI header from the rest of the SK EVM. The output from the voltage translators from XDS110 Section and cTI Header Section are muxed and connected to AM62x SIP JTAG Interface. If a connection to the cTI 20 Pin JTAG connector is sensed using a presence detect circuit, then the mux is set to route the 20 pin signals from the cTI connector to the AM62x SIP SoC in place of the on-board emulation circuit.

Figure 2-10. JTAG Interface

The pin-outs of the cTI 20 pin JTAG connector are given in the table below. An ESD-protection part number TPD4E004 is provided on USB signals to steer ESD current pulses to VCC or GND. TPD4E004 protects against ESD pulses up to ±15-kV Human-Body Model (HBM) as specified in IEC 61000-4-2 and provides ±8-kV contact discharge and ±12- kV air-gap discharge.

Table 2-5. JTAG Connector (J17) Pin-Out

| Table 2-3. 3 TAG Confinector (3 Tr) T III-Out |                |  |  |  |

|-----------------------------------------------|----------------|--|--|--|

| Pin No.                                       | Signal         |  |  |  |

| 1                                             | JTAG_TMS       |  |  |  |

| 2                                             | JTAG_TRST#     |  |  |  |

| 3                                             | JTAG_TDI       |  |  |  |

| 4                                             | JTAG_TDIS      |  |  |  |

| 5                                             | VCC3V3_SYS     |  |  |  |

| 6                                             | NC             |  |  |  |

| 7                                             | JTAG_TDO       |  |  |  |

| 8                                             | SEL_XDS110_INV |  |  |  |

| 9                                             | JTAG_cTI_RTCK  |  |  |  |

| 10                                            | DGND           |  |  |  |

| 11                                            | JTAG_cTI_TCK   |  |  |  |

| 12                                            | DGND           |  |  |  |

| 13                                            | JTAG_EMU0      |  |  |  |

| 14                                            | JTAG_EMU1      |  |  |  |

| 15                                            | JTAG_EMU_RSTn  |  |  |  |

| 16                                            | DGND           |  |  |  |

| 17                                            | NC             |  |  |  |

| 18                                            | NC             |  |  |  |

| 19                                            | NC             |  |  |  |

| 20                                            | DGND           |  |  |  |

Hardware Very INSTRUMENTS

www.ti.com

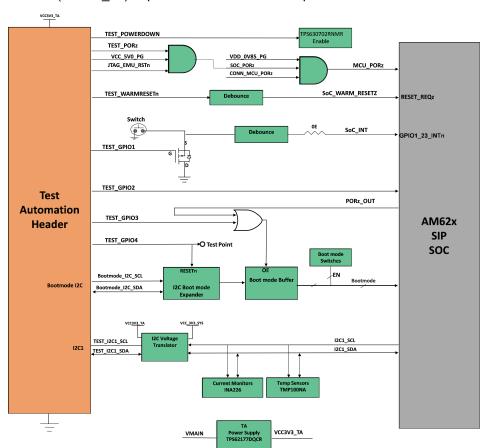

#### 2.11 Test Automation Header

AM62x SIP SK EVM has a 40-pin test automation header (FH12A-40S-0.5SH) to allow an external controller to manipulate some basic operations like Power Down, POR, Warm Reset, Boot Mode control, and so forth.

The Test Automation Circuit is powered by the 3.3 V supply generated by a dedicated regulator Mfr. Part# TPS62177DQCR. The SoC's I2C1 is connected to the test automation header. Another I2C instance (BOOTMODE\_I2C) from the Test Automation Header is connected to the 24-bit I2C boot mode IO Expander of Mfr. Part# TCA6424ARGJR to allow control of the boot modes for the AM62x SIP SoC.

The test automation circuit has voltage translation circuits so that the controller is isolated from the IO voltages used by the AM62x SIP. Boot mode for the AM62x SIP must be controlled by either the user using DIP Switches or the test automation header through the I2C IO Expander. Boot Mode Buffers are used to isolate the Boot Mode controls driven through DIP Switches or I2C IO Expander. The boot mode is controlled by the user using two 8-bit DIP switches on the board, which connects a pull-up resistor to the output of a buffer when the switch is set to the ON position and to weaker pull-down resistor when set to the OFF position. The output of the buffer is connected to the boot mode pins on the AM62x SIP SoC and the output is enabled when the boot mode is needed during a reset cycle.

When boot mode is to be set through Test Automation header, the required switch values are set at the I2C IO expander output, which overwrites the DIP switch values to give the desired boot values to the SoC. The pins used for boot mode also have other functions which is isolated by disabling the boot mode buffer during normal operation.

The power down signal from the Test automation header instructs the SK EVM to power down all the rails except for dedicated power supplies on the board. Similarly PORZn signal is also provided to give a hard reset to the SoC and WARM\_RESETn for warm reset of the SoC. One Interrupt signal from the Test Automation header is routed to the SoC GPIO (GPIO1 23) to provide an external Interrupt.

Figure 2-11. Test Automation

# Table 2-6. Test Automation Connector (J23) Pin-Out

| Pin No. | Signal    | IO Direction         | Pin No. | Signal               | IO Direction  |

|---------|-----------|----------------------|---------|----------------------|---------------|

| 1       | VCC3V3_TA | Power                | 21      | NC                   | NA            |

| 2       | VCC3V3_TA | Power                | 22      | NC                   | NA            |

| 3       | VCC3V3_TA | Power                | 23      | NC                   | NA            |

| 4       | NC        | NA                   | 24      | NC                   | NA            |

| 5       | NC        | NA                   | 25      | DGND                 | Power         |

| 6       | NC        | NA                   | 26      | TEST_POWERDOW N      | Input         |

| 7       | DGND      | Power                | 27      | TEST_PORz            | Input         |

| 8       | NC        | NA                   | 28      | TEST_WARMRESET n     | Input         |

| 9       | NC        | NA                   | 29      | NC                   | NA            |

| 10      | NC        | NA                   | 30      | TEST_GPIO1           | Bidirectional |

| 11      | NC        | NA                   | 31      | TEST_GPIO2           | Bidirectional |

| 12      | NC        | NA                   | 32      | TEST_GPIO3           | Input         |

| 13      | NC        | NA 33                |         | TEST_GPIO4           | Input         |

| 14      | NC        | NA                   | 34      | DGND                 | Power         |

| 15      | NC        | NA                   | 35      | NC                   | NA            |

| 16      | DGND      | Power                | 36      | SoC_I2C1_TA_SCL      | Bidirectional |

| 17      | NC        | NA                   | 37      | BOOTMODE_I2C_S<br>CL | Bidirectional |

| 18      | NC        | NA                   | 38      | SoC_I2C1_TA_SDA      | Bidirectional |

| 19      | NC        | NA 39 BOOTMODE<br>DA |         | BOOTMODE_I2C_S<br>DA | Bidirectional |

| 20      | NC        | NA                   | 40      | DGND                 | Power         |

Hardware Very INSTRUMENTS

www.ti.com

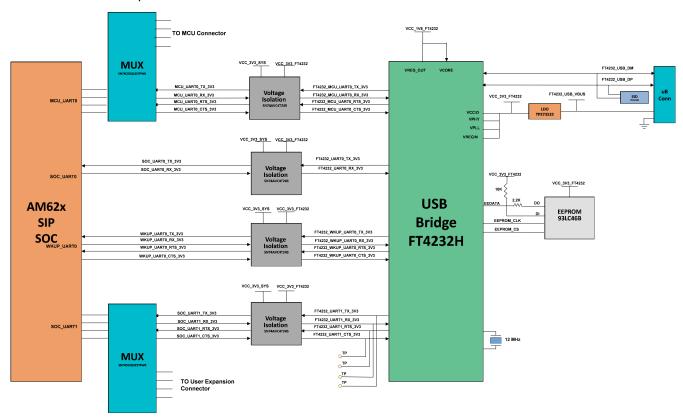

#### 2.12 UART Interface

The four UART ports of the SoC (MCU UART0, WKUP UART0, SoC UART0 and SoC UART1) provided by the AM62x SIP are interfaced with an FTDI FT4232HL for UART-to-USB functionality and terminated on a USB micro-B connector (J15) on board. When the AM62x SIP SKEVM is connected to a Host using USB cable, the computer can establish a Virtual COM Port which can be used with any terminal emulation application. The FT4232HL is bus powered.

Since the circuit is powered through BUS power, the connection to the COM port is not lost when the SKEVM power is removed.

| UART Port  | USB to UART Bridge | USB Connector | COM Port |

|------------|--------------------|---------------|----------|

| SoC_UART0  |                    |               | COM1     |

| SoC_UART1  | FT4232HL           | J15           | COM2     |

| WKUP_UART0 | F14232FL           | J 15          | COM3     |

| MCU_UART0  |                    |               | COM4     |

Table 2-7. UART Port Interface

The FT4232 chip is configured to operate in *Single chip USB to four channel UART* mode and takes the configuration file from the external SPI EEPROM connected to the FT4232 chip. The EEPROM (93LC46B) supports 1Mbit/s clock rate. The EEPROM is programmable in-circuit over USB using a utility program called FT\_PROG available from the FTDI web site. The FT\_PROG is also used for programming the board serial number for users to identify the connected COM port with board serial number when one or more boards are connected to the computer.

Figure 2-12. UART Interface

### 2.13 USB Interface

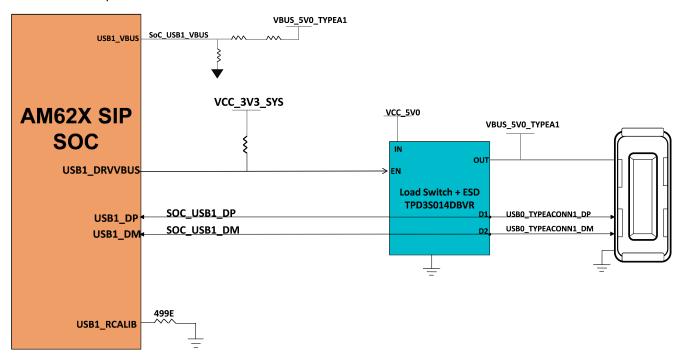

# 2.13.1 USB 2.0 Type A Interface

On SK EVM, USB 2.0 HOST Interface is offered through a Type-A Ports using Type-A Connector Mfr Part# 629104151021. USB1 Port of AM62x SIP SoC is used for USB 2.0 Type-A Host Interface.

USB Data lines from Type-A connectors are connected to the Current Limit Load Switch and ESD Protection IC Mfr Part# TPD3S014DBVR. This switch limits the current to 500 mA and dissipates the ESD strikes above the maximum level specified in the IEC 61000-4-2.

Figure 2-13. USB 2.0 Type A Interface

Hardware www.ti.com

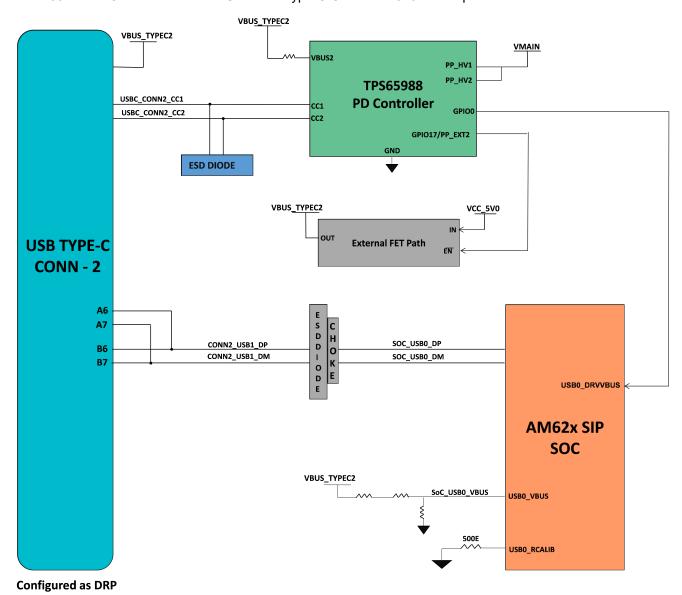

### 2.13.2 USB 2.0 Type C Interface

On SK EVM, USB 2.0 Interface is offered through USB Type-C Connector J13 Mfr part# 2012670005, which supports data rate up to 480Mbps. J13 is used for Data communication and also as power connector. J13 is configured as DRP port using PD controller TPS65988DHRSHR IC, so J13 can act as either host or device. The power role of the port depends on the type of the device getting connected on the connector and the ability to either sink or source. When the port is acting as DFP, the port can source up to 5V@500mA.

A GPIO from the PD controller is connected to USB0 DRVVBUS pin of the SoC to indicate the data role of the device connected to J13 Type-C connector. The GPIO is configured to output HIGH/LOW depending on the HOST/ DEVICE behavior of the J13 connector.

USB2.0 Data lines DP and DM from J13 are connected to the USB0 interface of AM62x SIP SoC via choke and ESD protection device. USB0 VBUS to the SoC is provided through a resistor divider network.

A common mode choke of Mfr Part# DLW21SZ900HQ2B is provided on USB Data lines to take care of EMI/ EMC. An ESD protection device of part number ESD122DMXR is included to dissipate ESD strikes on USB2.0 DP/DM Signals. An ESD protection device of part number TPD1E01B04DPLT is included on CC signals and TVS2200DRVR IC is included on VBUS rail of Type-C Connector J13 to dissipate ESD strikes.

Figure 2-14. USB 2.0 Type C Interface

# 2.14 Memory Interfaces

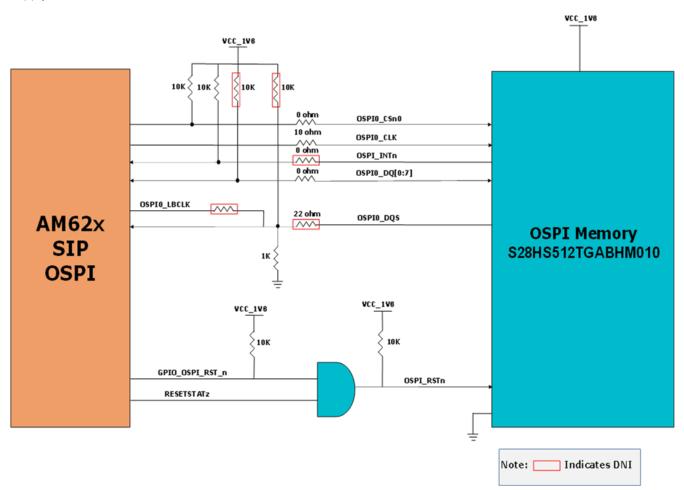

# 2.14.1 OSPI Interface

AM62x SIP SK EVM board has a 512-Mbit OSPI memory device from Cypress Part# S28HS512TGABHM010, which is connected to the OSPI0 interface of the AM62x SIP SoC. The OSPI interface supports single and double data rates with memory speeds up to 200MBps SDR and 400MBps DDR (200 MHz clock speed).

OSPI & QSPI implementation: 0 ohm resistors are provided for DATA[7:0], DQS, INT# and CLK signals. Footprints to mount external pull up resistors are provided on DATA[7:0] to prevent bus floating. The footprint for the OSPI memory also allows the installation of either a QSPI memory or an OSPI memory. The 0 ohm series resistors provided for pins OSPI DATA[4:7] are removed if QSPI flash is to be mounted.

Reset: The reset for the OSPI flash is connected to a circuit that ANDs the RESETSTATz from the AM62x with the signal GPIO\_OSPI\_RSTn from the SoC GPIO. This applies to reset for warm and cold reset. A pull-up is provided on GPIO\_OSPI\_RSTn coming from SoC pin to set the default active state.

Power: The OSPI flash is powered by 1.8 V IO supply. The 1.8 V supply is provided to both VCC and VCCQ pins of the OSPI flash memory.

The OSPI interface of the SoC is powered by VDDSHV1 Power group of SoC and is connected to 1.8V IO supply.

Figure 2-15. OSPI Interface

STRUMENTS Hardware www.ti.com

#### 2.14.2 MMC Interfaces

AM62x SIP SoC has three MMC (MMC0, MMC1 and MMC2) ports. MMC0 is connected to eMMC flash, MMC1 is interfaced with Micro SD Socket on the board and MMC2 is connected to M.2 module for Wi-Fi and BT Interface.

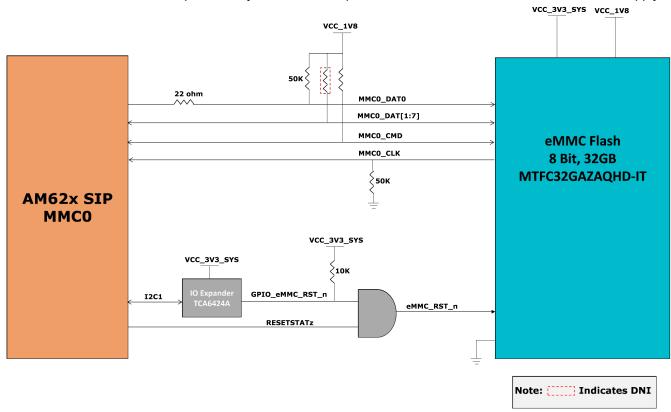

### 2.14.2.1 MMC0 - eMMC Interface

The SK EVM board contains 32GB of eMMC flash memory from Micron Part# MTFC32GAZAQHD-IT connected to MMC0 port of the AM62x SIP SoC. The flash is connected to 8 bits of the MMC0 interface supporting HS400 double data rates up to 200 MHz.

The eMMC device requires two power supplies, 3.3 V for NAND memory and 1.8 V for the eMMC interface. The MMC0 interface of the SoC is powered by the VDDSHV4 power domain, which is connected to 1.8 V IO supply.

Figure 2-16. eMMC Interface

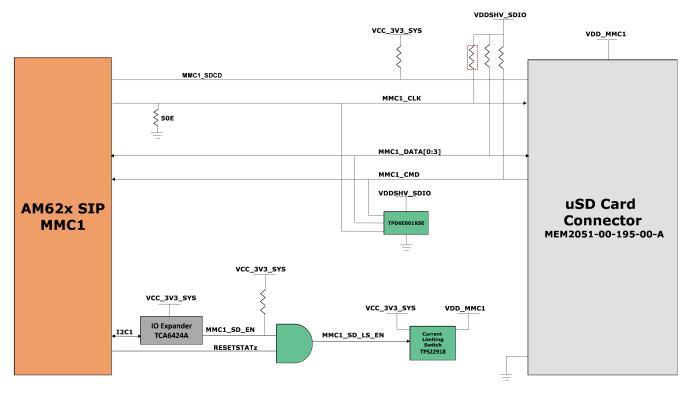

#### 2.14.2.2 MMC1 - Micro SD Interface

The SK EVM board provides a micro SD card interface connected to the MMC1 port of the AM62x SIP SoC. The Micro SD card socket of Mfr. Part# MEM2051-00-195-00-A is used to interface with the MMC1 port of the SoC. UHS1 operation is supported, including IO operations at both 1.8V and 3.3V. The Micro SD card interface is set to operate in SD mode by default. For high-speed cards, the ROM Code of the SoC attempts to find the fastest speed that the card and controller can support and can have a transition to 1.8V.

The SD Card connector power is provided using a load switch of Mfr. Part # TPS22918DBVR, which is controlled by ANDing the output of RESETSTATz, PORz\_OUT and a GPIO from an IO Expander. An ESD protection device of part number TPD6E001RSE is provided for data, clock, and command signals. TPD6E001RSE is a line termination device with integrated TVS diodes providing system-level IEC 61000-4-2 ESD protection, ± 8-kV contact discharge and ± 15kV air-gap discharge.

Figure 2-17. Micro SD Interface

ISTRUMENTS Hardware www.ti.com

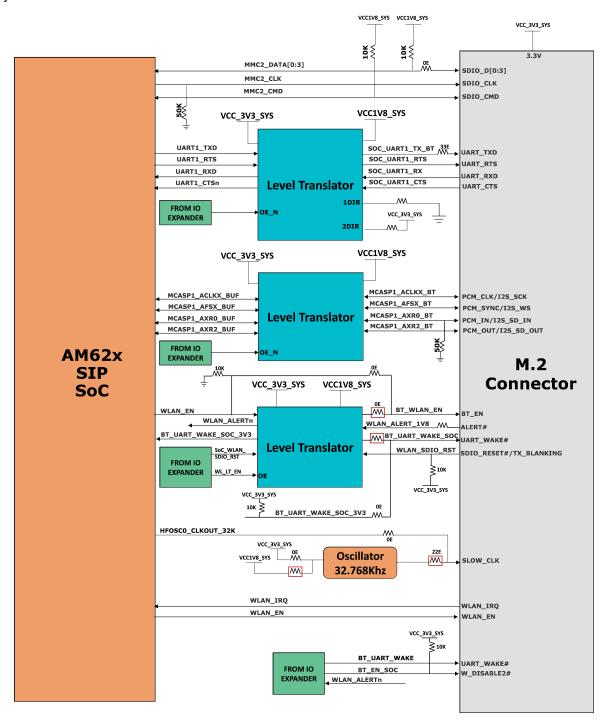

### 2.14.2.3 MMC2 - M.2 Key E Interface

AM62x SIP SK EVM has a M.2 Key E interface for connecting Wi-Fi BT modules connected to MMC2, UART1 instances and McASP1 interface through buffers. The M.2 Module is connected to 4-bit IO of the MMC2 interface.

The Module requires one power supply, 3.3V. Power to M.2 module is supplied from on board Power supply rails.

The MMC2 interface of the SoC is powered by the VDDSHV6 power domain, which is connected to 1.8 V IO

Figure 2-18. Wi-Fi Interface

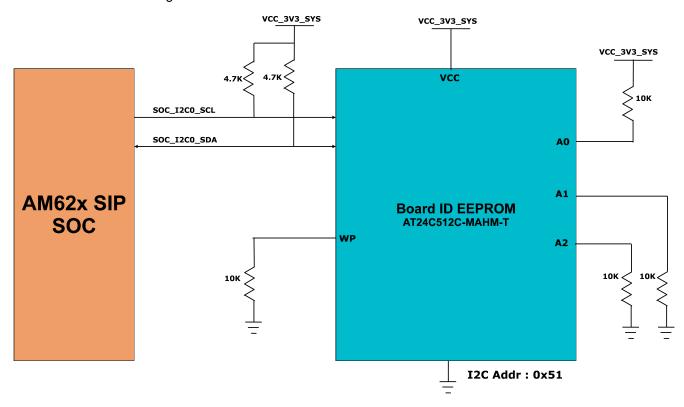

#### 2.14.3 Board ID EEPROM

AM62x SIP SK EVM boards can be identified remotely from the version and serial number, which are stored on the onboard EEPROM. The EEPROM is accessible from SoC I2C0 port of AM62x SIP SoC.

The Board ID EEPROM I2C address is set to 0x51.

AM62x SIP SK EVM includes an AT24C512C-MAHM-T 512kb EEPROM. The first 259 bytes of memory are pre-programmed with identification information for each board. The remaining 65277 bytes are available to the user for data or code storage.

Figure 2-19. Board ID EEPROM

**INSTRUMENTS** Hardware www.ti.com

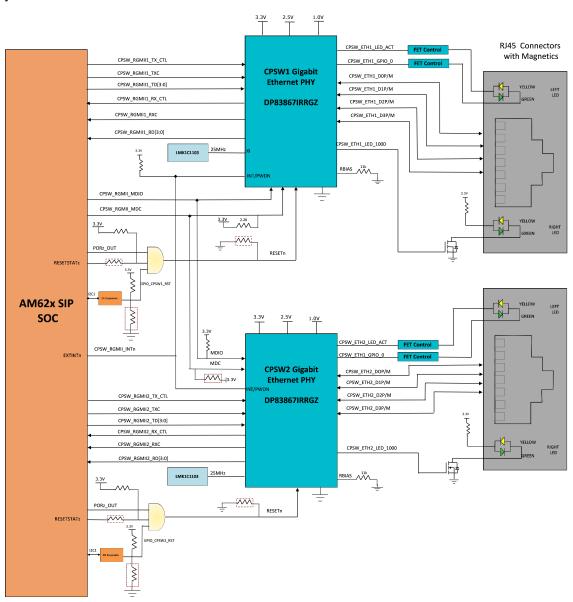

# 2.15 Ethernet Interface

The AM62x SIP SK EVM offers two Ethernet Ports of 1 Gigabit Speed for external Communication. Two channels of RGMII Gigabit Ethernet CPSW Ports from AM62x SIP SoC are connected to separate Gigabit Ethernet PHY Transceivers DP83867, which are finally terminated on two RJ45 connectors with integrated magnetics.

The 48pin version of the PHY DP83867 is configured to advertise 1-Gb operation with the internal delay set to accommodate the internal delay inside the AM62x. CPSW\_RGMII1 and CPSW\_RGMII2 Ports share a common MDIO Bus to communicate with the external PHY Transceiver.

Two Single port RJ45 Connectors Mfr Part# LPJG16314A4NL from Link-PP are used on the board for Ethernet 10/100/1G Connectivity. RJ45 Connectors have integrated magnetics and LEDs for indicating 1000BASE-T link as well as receive or transmit Activity.

IOsupply to the Ethernet PHY is set 3.3V level.

Figure 2-20. Ethernet Interface

### 2.15.1 CPSW Ethernet PHY 1 Default Configuration

The default configuration of the DP83867 is determined using a number of resistor pull-up and pull-down values on specific pins of the PHY. Depending on the values installed, each of the configuration pins can be set to one of four modes by using the pull up and pull down options provided. The AM62x SIP SK EVM uses the 48-pin QFN package which supports the RGMII interface.

The DP83867 PHY uses four level configurations based on resistor strapping which generate four distinct voltages ranges. The resistors are connected to the RX data and control pins which are normally driven by the PHY and are inputs to the processor. The voltage range for each mode is shown below:

Mode1 - 0 V to 0.3 V

Mode2 - 0.462 V to 0.6303 V

Mode3 - 0.7425 V to 0.9372 V

Mode4 - 2.2902 V to 2.9304 V

Footprint for both pull-up and pull-down is provided on all the strapping pins except LED\_0. LED\_0 is for Mirror Enable, which is set to mode 1 by default, Mode 4 is not applicable and Mode2, Mode3 option is not desired.

CPSW\_RGMII1 port of the AM62x SIP SoC is connected to DP83867 whose configuration is as given below:

PHYADDR: 00000

Auto\_neg: Enabled

ANGsel 10/100/1000

RGMII Clk skew Tx: 2 ns

RGMII Clk skew Rx: 2 ns

### 2.15.2 CPSW Ethernet PHY 2 Default Configuration

CPSW\_RGMII2 port of the AM62x SIP SoC is connected to DP83867 whose configuration is as given below:

PHYADDR: 00001

Auto\_neg: Enabled

ANGsel 10/100/1000

RGMIIClk skew Tx: 2 ns

RGMII Clk skew Rx: 2 ns

The interrupts generated from two CPSW RGMII PHYs are tied together and is connected to EXTINTn pin of AM62x SIP SoC.

LED1 is connected to RJ45 Right LED (Green) to indicate 1000 MHz link.

LED2 is connected to RJ45 Left LED (Yellow) to indicate transmit/receive activity. GPIO\_0 is connected to RJ45 Left LED (Green) to indicate 10/100MHz link.

LED Control is achieved through an external MOSFET.

Hardware www.ti.com

# 2.16 GPIO Port Expander

The I/O Expander used in the AM62x SIP SK EVM is a 24-Bit I2C based I/O Expander, which is used for daughter card plug-in detection and for generating resets and enable signals to various peripheral devices connected to the I/O Expander. The SoC\_I2C1 bus of the AM62x SIP SoC is used to interface with the I/O Expander. The I2C device address of the I/O Expander is 0x21. See the tables below for the list of signals being controlled by the Expander.

Table 2-8. IO Expander 1 Signal Details

| B: N .     | Table 2-0. 10 Expander 1 Signal Details |           |                                               |  |  |  |  |

|------------|-----------------------------------------|-----------|-----------------------------------------------|--|--|--|--|

| Pin Number | SIGNAL                                  | DIRECTION | DEVICE                                        |  |  |  |  |

| P00        | GPIO_CPSW2_RST                          | OUTPUT    | CPSW Ethernet PHY-2 Reset Control GPIO        |  |  |  |  |

| P01        | GPIO_CPSW1_RST                          | OUTPUT    | CPSW Ethernet PHY-1 Reset Control GPIO        |  |  |  |  |

| P02        | PRU_DETECT                              | INPUT     | PRU Board Detection                           |  |  |  |  |

| P03        | MMC1_SD_EN                              | OUTPUT    | SD Card Load Switch Enable                    |  |  |  |  |

| P04        | VPP_LDO_EN                              | OUTPUT    | SOC eFuse Voltage (VPP=1.8V) Regulator Enable |  |  |  |  |

| P05        | EXP_PS_3V3_EN                           | OUTPUT    | EXP CONN 3.3V Power Switch Enable             |  |  |  |  |

| P06        | EXP_PS_5V0_EN                           | OUTPUT    | EXP CONN 5 V Power Switch Enable              |  |  |  |  |

| P07        | EXP_HAT_DETECT                          | INPUT     | EXP CONN HAT Board Detection                  |  |  |  |  |

| P10        | WLAN_ALERT_3V3                          | OUTPUT    | Wi-Fi card alert - M.2 module                 |  |  |  |  |

| P11        | BT_UART_WAKE_SOC_3V3                    | INPUT     | BT UART WKUP Signal                           |  |  |  |  |

| P12        | UART1_FET_BUF_EN                        | OUTPUT    | SOC UART1 buffer enable                       |  |  |  |  |

| P13        | WL_LT_EN                                | OUTPUT    | Enable for Wilink Level Translators           |  |  |  |  |

| P14        | GPIO_HDMI_RSTn                          | OUTPUT    | HDMI Transmitter Reset Control GPIO           |  |  |  |  |

| P15        | CSI_GPIO1                               | NA        | Raspberry Pi Camera CSI0 GPIO1                |  |  |  |  |

| P16        | CSI_GPIO2                               | NA        | Raspberry Pi Camera CSI0 GPIO2                |  |  |  |  |

| P17        | PRU_3V3_EN                              | OUTPUT    | PRU Power Switch Enable                       |  |  |  |  |

| P20        | HDMI_INTn                               | INPUT     | HDMI Interrupt                                |  |  |  |  |

| P21        | PD_I2C_IRQ                              | INPUT     | Interrupt from PD controller                  |  |  |  |  |

| P22        | MCASP1_FET_EN                           | OUTPUT    | MCASP1 Enable and Direction Control           |  |  |  |  |

| P23        | MCASP1_BUF_BT_EN                        | OUTPUT    |                                               |  |  |  |  |

| P24        | MCASP1_FET_SEL                          | OUTPUT    |                                               |  |  |  |  |

| P25        | UART1_FET_SEL                           | OUTPUT    | SOC UART1 FET selection                       |  |  |  |  |

| P26        | TS_INT#                                 | INPUT     | OLDI Display Touch Interrupt                  |  |  |  |  |

| P27        | IO_EXP_TEST_LED                         | OUTPUT    | User Test LED 2                               |  |  |  |  |

# Table 2-9. IO Expander 2 Signal Details

| Pin Number | SIGNAL            | DIRECTION | DEVICE                                |

|------------|-------------------|-----------|---------------------------------------|

| P0         | WLAN_SDIO_RST_3V3 | OUTPUT    | M.2 Connector SDIO Reset Control GPIO |

| P1         | GPIO_TS_RSTn      | OUTPUT    | OLDI Display Reset control            |

| P2         | GPIO_AUD_RSTn     | OUTPUT    | Audio Codec Reset Control GPIO        |

| P3         | GPIO_eMMC_RSTn    | OUTPUT    | eMMC Reset control GPIO               |

# 2.17 GPIO Mapping

The table below describes the detailed GPIO mapping of AM62x SIP SoC with AM62x SIP SK EVM peripherals.

| SL NO. | GPIO DESCRIPTION                                                         | GPIO NETNAME             | Functionality                         | GPIO USED         | SOC MUXED SIGNAL NAME | DIRECTION WITH<br>RESPECT TO<br>CONTROL | DEFAULT<br>STATE | ACTIVE<br>STATE | VOLTAGE DOMAIN ON<br>SOC SIDE | VOLTAGE CONNECTED<br>ON SKEVM |

|--------|--------------------------------------------------------------------------|--------------------------|---------------------------------------|-------------------|-----------------------|-----------------------------------------|------------------|-----------------|-------------------------------|-------------------------------|

| 1      | Enable for WLAN Interface                                                | SoC_WLAN_EN_1V8          | ENABLE                                | GPIO0_71          | MMC2_SDCD             | OUTPUT                                  | LOW              | HIGH            | VDD\$HV6                      | SoC_DVDD1V8                   |

| 2      | WLAN Interrupt                                                           | SoC_WLAN_IRQ_1V8         | INTERRUPT                             | GPIO0_72          | MMC2_SDWP             | INPUT                                   | HIGH             | LOW             | VDDSHV6                       | SoC_DVDD1V8                   |

| 3      | Enable for BT Interface                                                  | BT_EN_SOC_3V3            | ENABLE                                | MCU_GPIO0_1       | MCU_SPI0_CS0          | OUTPUT                                  | HIGH             | LOW             | VDDSHV_MCU                    | SoC_DVDD3V3                   |

|        | CPSW Ethernet PHY Interrupt                                              |                          |                                       |                   |                       |                                         |                  |                 |                               |                               |

| 4      | PRU Connector Interrupt PMIC_INTn                                        | CPSW_RGMII_INTn/PRU_INTn | INTERRUPT                             | GPIO1_31          | EXTINTn               | INPUT                                   | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 5      | OSPI Reset Control GPIO                                                  | GPIO_OSPI_RSTn           | RESET                                 | GPIO0_12          | OSPIO_CSn1            | OUTPUT                                  | HIGH             | LOW             | VDDSHV1                       | SoC_DVDD1V8                   |

| 6      | OSPI Interrupt                                                           | OSPI_INTn                | INTERRUPT                             | GPIO0_13          | OSPIO_CSn2            | INPUT                                   | HIGH             | LOW             | VDDSHV1                       | SoC_DVDD1V8                   |

| 7      | SD Card IO Voltage Select                                                | VSEL_SD                  | ENABLE                                | GPIO0_31          | GPMC0_CLK             | OUTPUT                                  | LOW              | HIGH            | VDDSHV3                       | SoC_DVDD3V3                   |

| 8      | IO Expander Interrupt                                                    |                          |                                       |                   |                       |                                         |                  |                 |                               |                               |

| 9      | TEST GPIO1 from Test Automation<br>Connector/ User Interrupt Push Button | MCU_GPIO0_15             | INTERRUPT                             | MCU_GPI00_15      | MCU_MCAN1_TX          | INPUT                                   | HIGH             | LOW             | VDDSHV_CANUART                | SoC_DVDD3V3                   |

| 10     | User Test LED 1                                                          | SOC_GPIO1_49             | GPIO                                  | GPIO1_49          | MMC1_SDWP             | OUTPUT                                  | LOW              | HIGH            | VDDSHV0                       | SoC_DVDD3V3                   |

|        |                                                                          |                          |                                       | IO EXPAN          | DER - 01              | l I                                     |                  |                 |                               |                               |

| 1      | CPSW Ethernet PHY-2 Reset Control<br>GPIO                                | GPIO_CPSW2_RST           | RESET                                 | IO EXPANDER - P00 |                       | ОИТРИТ                                  | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 2      | CPSW Ethernet PHY-1 Reset Control<br>GPIO                                | GPIO_CPSW1_RST           | RESET                                 | IO EXPANDER - P01 |                       | ОИТРИТ                                  | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 3      | PRU Board Detection                                                      | PRU_DETECT               | DETECTION                             | IO EXPANDER - P02 |                       | INPUT                                   | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 4      | SD Card Load Switch Enable                                               | MMC1_SD_EN               | ENABLE                                | IO EXPANDER -P03  |                       | OUTPUT                                  | нібн             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 5      | SOC eFuse Voltage(VPP=1.8V) Regulator<br>Enable                          | VPP_LDO_EN               | ENABLE                                | IO EXPANDER - P04 |                       | ОИТРИТ                                  | LOW              | HIGH            | VDDSHV0                       | SoC_DVDD3V3                   |

| 6      | EXP CONN 3.3V Power Switch Enable                                        | EXP_PS_3V3_EN            | ENABLE                                | IO EXPANDER - P05 |                       | ОИТРИТ                                  | LOW              | HIGH            | VDDSHV0                       | SoC_DVDD3V3                   |

| 7      | EXP CONN 5V Power Switch Enable                                          | EXP_PS_5VO_EN            | ENABLE                                | IO EXPANDER - P06 |                       | OUTPUT                                  | LOW              | HIGH            | VDDSHV0                       | SoC_DVDD3V3                   |

| 8      | EXP CONN HAT Board Detection                                             | RPI_HAT_DETECT           | DETECTION                             | IO EXPANDER - P07 |                       | INPUT                                   | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 9      | M.2 Connector Alert                                                      | WLAN_ALERT_3V3           | ALERT                                 | IO EXPANDER – P10 |                       | OUTPUT                                  | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 10     | M.2 Connector WAKEUP                                                     | BT_UART_WAKE_SOC_3V3     | WAKEUP                                | IO EXPANDER – P11 |                       | OUTPUT                                  | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 11     | SOC UART1 Mux Select                                                     | UART1_MUX_SEL            | SELECT                                | IO EXPANDER - P12 |                       | OUTPUT                                  | LOW              | HIGH            | VDDSHV0                       | SoC_DVDD3V3                   |

| 12     | Enable for Wilink Level Translators                                      | WL_LT_EN                 | ENABLE                                | IO EXPANDER - P13 |                       | OUTPUT                                  | LOW              | нібн            | VDDSHV0                       | SoC_DVDD3V3                   |

| 13     | HDMI Transmitter Reset Control GPIO                                      | GPIO_HDMI_RSTn           | RESET                                 | IO EXPANDER - P14 |                       | ОИТРИТ                                  | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 14     | Raspberry Pi Camera CSI0 GPIO1                                           | CSI_GPIO1                | INPUT/OUTPUT                          | IO EXPANDER - P15 |                       | NA NA                                   | NA               | NA              | VDDSHV0                       | SoC_DVDD3V3                   |

| 15     | Raspberry Pi Camera CSI0 GPIO2                                           | CSI_GPIO2                | INPUT/OUTPUT                          | IO EXPANDER - P16 |                       | NA                                      | NA               | NA              | VDDSHV0                       | SoC_DVDD3V3                   |

| 16     | PRU Power Switch Enable                                                  | PRU_3V3_EN               | ENABLE                                | IO EXPANDER - P17 |                       | OUTPUT                                  | LOW              | HIGH            | VDDSHV0                       | SoC_DVDD3V3                   |

| 17     | HDMI Interrupt                                                           | HDMI_INTn                | INTERRUPT                             | IO EXPANDER - P20 |                       | INPUT                                   | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 18     | TEST GPIO2 from Test Automation<br>Connector                             | TEST_GPIO2               | GPIO for communications<br>with AM62x | IO EXPANDER - P21 |                       | INPUT                                   | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 19     |                                                                          | AUD_BUF_EN               | ENABLE                                | IO EXPANDER - P22 |                       | OUTPUT                                  | LOW              | HIGH            | VDDSHV0                       | SoC_DVDD3V3                   |

| 20     |                                                                          | WL_BUF_EN                | ENABLE                                | IO EXPANDER - P23 |                       | OUTPUT                                  | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 21     | MCASP2 Enable and Direction Control                                      | AUD_BUF_CLK_DIR          | DIRECTION CONTROL                     | IO EXPANDER - P24 |                       | OUTPUT                                  | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 22     |                                                                          | WL_BUF_CLK_DIR           | DIRECTION CONTROL                     | IO EXPANDER - P25 |                       | OUTPUT                                  | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 23     | OLDI Display Touch Interrupt                                             | TS_INT#                  | INTERRUPT                             | IO EXPANDER - P26 |                       | INPUT                                   | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 24     | User Test LED 2                                                          | IO_EXP_TEST_LED          | GPIO                                  | IO EXPANDER - P27 |                       | OUTPUT                                  | LOW              | HIGH            | VDDSHV0                       | SoC_DVDD3V3                   |

|        |                                                                          |                          |                                       | IO EXPAN          | DER - 02              | · · · · · · · · · · · · · · · · · · ·   |                  |                 |                               |                               |

|        | M.2 Connector SDIO Reset Control GPIO                                    | WLAN_SDIO_RST_3V3        | RESET                                 | IO EXPANDER – PO  |                       | INPUT                                   | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 2      | OLDI Display Reset control                                               | GPIO_TS_RSTn             | RESET                                 | IO EXPANDER – P1  |                       | INPUT                                   | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 3      | Audio Codec Reset Control GPIO                                           | GPIO_AUD_RSTn            | DETECTION                             | IO EXPANDER – P2  |                       | INPUT                                   | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

| 4      | eMMC Reset control GPIO                                                  | GPIO_eMMC_RSTn           | RESET                                 | IO EXPANDER – P3  |                       | OUTPUT                                  | HIGH             | LOW             | VDDSHV0                       | SoC_DVDD3V3                   |

|        |                                                                          |                          |                                       |                   |                       |                                         |                  |                 |                               |                               |

|        |                                                                          |                          |                                       |                   |                       |                                         |                  |                 |                               |                               |

|        |                                                                          |                          |                                       |                   |                       |                                         |                  |                 |                               |                               |

|        |                                                                          |                          |                                       |                   |                       |                                         |                  |                 | -                             |                               |

|        |                                                                          |                          |                                       |                   |                       |                                         |                  |                 |                               |                               |

Figure 2-21. GPIO Mapping

Hardware www.ti.com

# 2.18 OLDI Display Interface

The OLDIO Display interface of the AM62x SIP SoC is connected to a 40 pin LVDS display connector (J21) Mfr. Part# FFC2A32-40-T from GCT. The OLDI Interface supports dual channel 8-bit LVDS output.

The Pin-out details of the Display connector are given in below table.

**Table 2-10. OLDI Display Connector Pinout**

| Pin No. | Signal Pin No.           |    | Signal        |

|---------|--------------------------|----|---------------|

| 1       | VCC_3V3_SYS (EEPROM_VDD) | 21 | CH1_LVDS_A2P  |

| 2       | SoC_I2C0_SCL             | 22 | GND           |

| 3       | SoC_I2C0_SDA             | 23 | CH1_LVDS_A3N  |

| 4       | NC                       | 24 | CH1_LVDS_A3P  |

| 5       | NC                       | 25 | GND           |

| 6       | GND                      | 26 | CH1_LVDS_A0N  |

| 7       | GND                      | 27 | CH1_LVDS_A0P  |

| 8       | OLDI_RESETn              | 28 | GND           |

| 9       | TS_INT#                  | 29 | CH2_LVDS_A1N  |

| 10      | GND                      | 30 | CH2_LVDS_A1P  |

| 11      | CH1_LVDS_A0N             | 31 | GND           |

| 12      | CH1_LVDS_A0P             | 32 | CH2_LVDS_CLKN |

| 13      | GND                      | 33 | CH2_LVDS_CLKP |

| 14      | CH1_LVDS_A1N             | 34 | GND           |

| 15      | CH1_LVDS_A1P             | 35 | CH2_LVDS_A2N  |

| 16      | GND                      | 36 | CH2_LVDS_A2P  |

| 17      | CH1_LVDS_CLKN            | 37 | GND           |

| 18      | CH1_LVDS_CLKP            | 38 | CH2_LVDS_A3N  |

| 19      | GND                      | 39 | CH2_LVDS_A3P  |

| 20      | CH1_LVDS_A2N             | 40 | GND           |

#### **2.19 Power**

# 2.19.1 Power Requirements

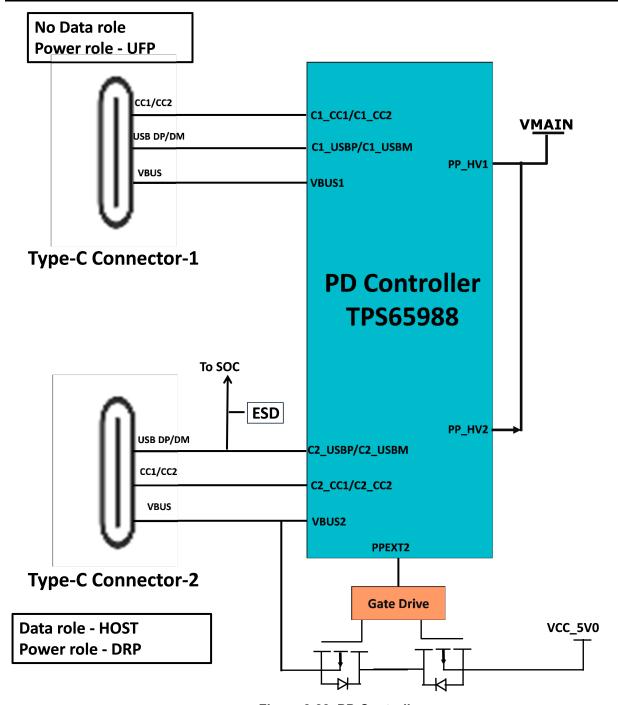

AM62x SIP SKEVM can be powered through either of the two USB Type C Connectors:

- Connector 1 (J11) Power role SINK, No Data role

- Connector 2 (J13) Power role DRP, Data role USB2.0 DFP or UFP

The AM62x SIP SK EVM supports voltage input ranges of 5 V - 15 V and 3 A of current. A USB PD controller Mfr.Part# TPS65988DHRSHR is used for PD negotiation upon cable detection to get necessary power required for the board. Connector 1 is configured to be an UFP Port and has no Data role. Connector 2 is configured as a DRP port and can act as DFP only when the board is being powered by Connector 1. When both the connectors are connected to external power supply, the port with highest PD power contract is selected to power the board.

**Table 2-11. Type-C Port Power Roles**

| J11(UFP)   | J13(DRP)   | Board Power    | Remarks                                                                             |

|------------|------------|----------------|-------------------------------------------------------------------------------------|

| Plugged in | NC         | ON- J11        | J11is UFP and only sinks power and J13 can act as DFP if a peripheral is connected. |

| NC         | Plugged in | ON - J13       | J13 is UFP and can only sink power.                                                 |

| Plugged in | Plugged in | ON- J11 or J13 | Board is powered by the port with highest PD power contract.                        |

The PD IC uses a SPI EEPROM to load the necessary configuration on power up so the PD IC can negotiate a power contract with a compatible power source.

The configuration file is loaded to the EEPROM using header J22. Once the EEPROM is programmed the PD obtains the configuration files via SPI communication. Upon loading the configuration files the PD negotiates with the source to obtain the necessary power requirement.

#### Note

The EEPROM is pre-programmed with the configuration file for the operation of the PD controller.

Power indication LEDs are provided for both the Type-C connectors for the user to identify which connector is powering the SK EVM Board.

An external power supply (Type-C output) can be used to power the EVM but is not included as part of the SK EVM kit.

The external power supply requirements (Type-C) are:

Minimum Voltage: 5 VDC, Recommended Minimum Current: 3000 mA

Maximum Voltage: 15VDC, Maximum current: 5000 mA

Table 2-12. Recommended External Power Supply

| DigiKeyPart No. | Manufacturer | Manufacturer Part No. |

|-----------------|--------------|-----------------------|

| 1939-1794-ND    | GlobTek,Inc. | TR9CZ3000USBCG2R6BF2  |

| Q1251-ND        | Qualtek      | QADC-65-20-08CB       |

#### Note

Because SK-AM62 SIP implements USB PD for power, the device is able to negotiate to the highest Voltage/Current combination supported by both the Device and Power Adapter. If the power supply exceeds the maximum voltage and the current requirements listed above are acceptable, then the power adapter is compliant with the USB-C PD specification.

### 2.19.2 Power Input

Both Type-C Connectors (VBUS and CC lines) are connected to a Dual PD controller Mfr Part# TPS65988. TheTPS65988 is a stand-alone USB Type-C and Power Delivery (PD) controller providing cable plug and orientation detection for two USB Type-C Connectors. Upon cable detection, the TPS65988 communicates on the CC wire using the USB PD protocol. When cable detection and USB PD negotiation are complete, the TPS65988 enables the appropriate power path. The two internal power paths of TPS65988 are configured as sink paths for the two Type-C ports and an external FET path is provided for Type-C CONN 2 to source 5 V when acting as DFP. The external FET path is controlled by GPIO17/PP EXT2 of the PD controller.

TPS65988 PD controller can provide an output of 3 A (15 V max) through CC negotiation. The VBUS pins from both the Type C connectors are connected to the VBUS pins of the PD controller. The output of the PD is VMAIN, which is given to on board Buck-Boost and Buck regulators to generate fixed 5 V and 3.3 V supply for the SK EVM board.

Hardware www.ti.com

Figure 2-22. PD Controller

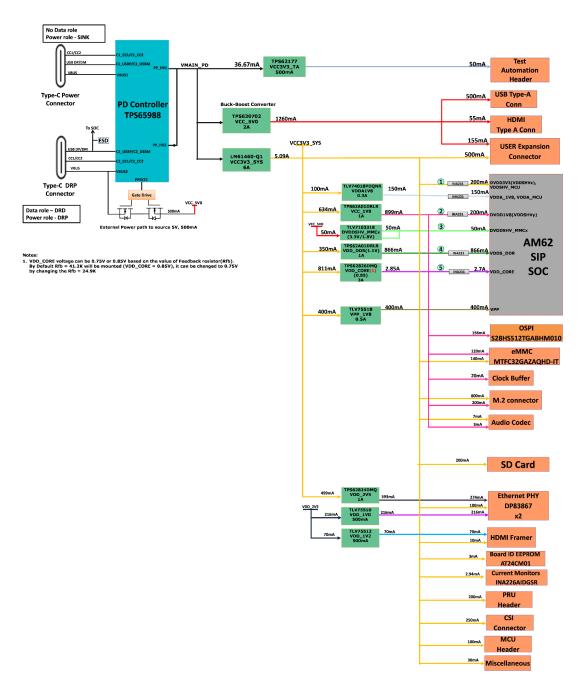

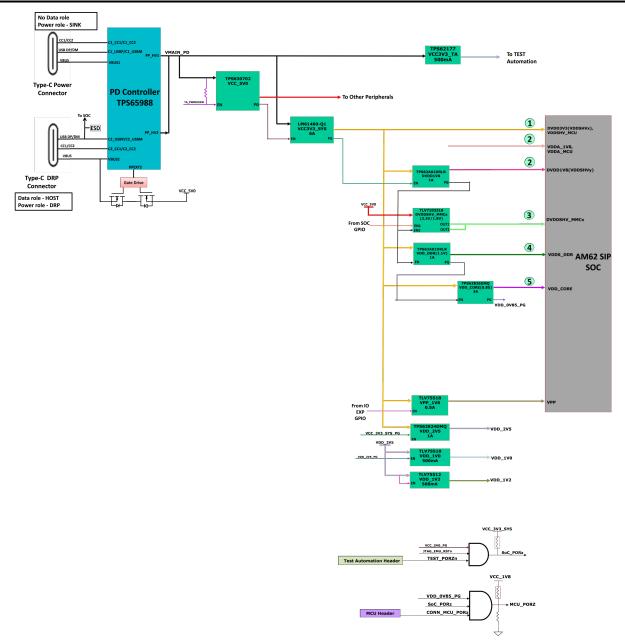

The following sections describe the power distribution network topology that supplies the SKEVM board, supporting components and reference voltages.

The AM62x SIP SK EVM board includes a power solution based on discrete power supply components. The initial stage of the power supply are VBUS voltage from either of the two USB Type C connectors J11 and J13. USB Type-C Dual PD controller of Mfr. Part# TPS65988DHRSHR is used for negotiation of the required power to the system.

Buck-Boost controller TPS630702RNMR and Buck converter LM61460-Q1 are used for the generation of 5 V and 3.3V respectively and the input to the regulators is the PD output. These 3.3 V and 5 V are the primary voltages for the AM62x SIP SK EVM Board power resources.

The 3.3 V supply generated from the Buck regulator LM61460-Q1 is the input supply to the various SoC regulators and LDOs. The 5 V supply generated from the Buck Boost regulator TPS630702RNMR is used for powering the on board peripherals.

Discrete regulators and LDOs used on board are:

- TPS62824DMQR To generate VDD 2V5 rail for Ethernet PHYs

- TLV75510PDQNR To generate VDD 1V0 for Ethernet PHYs

- TLV75512PDQNR To generate VDD 1V2 for HDMI Transmitter

- TLV74018PDQNR To generate 1.8 V Analog supply for SoC

- TPS62A01DRLR To generate 1.8V IO supply for SoC and for Peripherals namely OSPI, eMMC, Audio codec, M.2 Connector and Clock Buffer

- TLV7103318QDSERQ1 To generate VDDSHV5\_MMC1(SD interface) supply for SoC

- TPS62A01DRLR To generate DDR Power for SoC

- TPS62826DMQR To generate Core supply for SoC

Dedicated regulators are also provided on the board for:

- TPS62177 Regulator Powering the always on circuits of Test Automation Section

- TLV75518LDO e-Fuse programming of SoC

- TPS79601LDO XDS110 On board emulator

- TPS73533LDO FT4232 UART to USB Bridge

Additionally, GPIO from the test automation header is also connected to the TPS630702RNMR Enable to control ON/OFF of the SK EVM via the test automation board. The test automation board only disables the VCC\_5V0 output of TPS630702RNMR from which all other power supplies are derived. SoC has different IO groups. Each IO group is powered by specific power supplies as given in the next section.

INSTRUMENTS Hardware www.ti.com

### 2.19.3 Power Supply

AM62x SIP SK EVM utilizes an array of DC-DC converters to supply the various memories, clocks, SoC and other components on the board with the necessary voltage and the power required.

The figure below shows the various discrete regulators and LDOs used to generate power rails and the current consumption of each peripheral on AM62x SIP SK EVM board.

Figure 2-23. Power Architecture

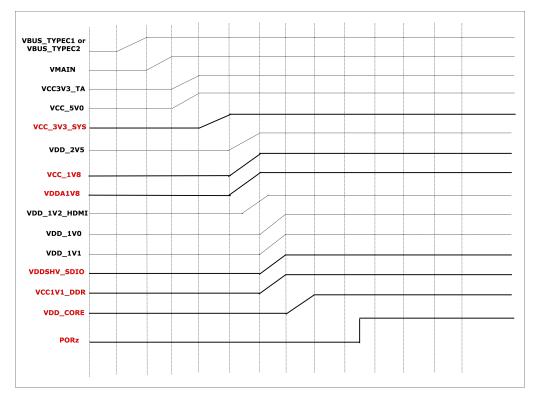

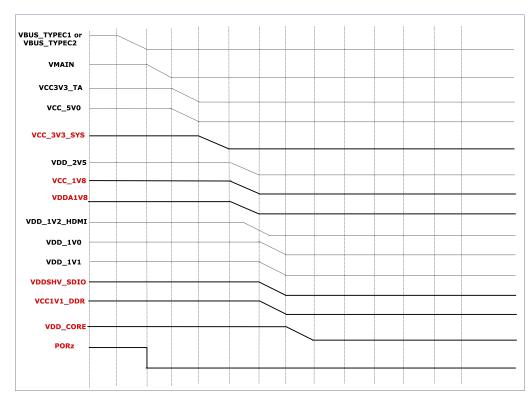

### 2.19.4 Power Sequencing

The figure below shows the Power Up and Power Down sequence of all the AM62x SIP SK EVM Power supplies. AM62x SIP SoC Power rails are named in red.

Figure 2-24. Power Up Sequence

Figure 2-25. Power Down Sequence

Hardware INSTRUMENTS

www.ti.com

Figure 2-26. Power Supply Sequencing

#### 2.19.5 AM62x SIP SoC Power

The Core voltage of the AM62x SIP can be 0.75 V or 0.85 V based on the Rfb (R150) Resistor value and on the power optimization requirement. By Default Rfb = 41.2K is mounted (VDD\_CORE = 0.85 V), and can be changed to 0.75 V by changing the Rfb to 24.9K. Current monitors are provided on all the SoC Power rails.

The SoC has different IO groups. Each IO group is powered by specific power supplies as shown in below table.

Table 2-13. SoC Power Supply

| SI.No | Power Supply     | SoCSupply Rails                    | IO Power Group | Voltage |

|-------|------------------|------------------------------------|----------------|---------|

| 1     | VDD_CORE         | VDDA_CORE_USB                      |                | 0.85    |

|       |                  | VDDA_CORE_CSI                      |                |         |

|       |                  | VDD_CANUART                        | CANUART        |         |

|       |                  | VDD_CORE                           | CORE           |         |

|       |                  | VDDR_CORE                          | CORE           |         |

| 2     | VDDA_1V8         | VDDA_1V8_CSIRX.                    | CSI            | 1.8     |

|       |                  | VDDA_1V8_USB                       | USB            |         |

|       |                  | VDDA_1V8_MCU                       |                |         |

|       |                  | VDDA_1V8_OLDI                      | OLDI           |         |

|       |                  | VDDA_1V8_OSCO                      | OSCO           |         |

|       |                  | VDDS_MEM_1P8                       | DDR            |         |

|       |                  | VDDA_PLL0, VDDA_PLL1<br>&VDDA_PLL2 |                |         |

| 3     | VDD_DDR          | VDDS_DDR                           | DDR0           | 1.1     |

|       |                  | VDDS_DDR_MEM                       |                |         |

| 5     | VPP_1V8          | VPP_1V8                            |                | 1.8     |

| 6     | SoC_VDDSHV5_SDIO | VDDSHV5                            | MMC1           |         |

| 7     | SoC_DVDD1V8      | VDDSHV0                            | General        | 1.8     |

|       |                  | VDDSHV1                            | OSPI           |         |

|       |                  | VDDSHV4                            | MMC0           |         |

|       |                  | VDDSHV6                            | MMC2           |         |

|       |                  | VMON_1P8_SOC                       |                |         |

| 8     | SoC_DVDD3V3      | VDDSHV0                            | General        | 3.3     |

|       |                  | VDDSHV2                            | RGMII          |         |

|       |                  | VDDSHV3                            | GPMC           |         |

|       |                  | VDDSHV_MCU                         | MCU General    |         |

|       |                  | VMON_3P3_SOC                       |                |         |

|       |                  | VDDA_3P3_USB                       | USB            |         |

### 2.19.6 Current Monitoring

INA231 power monitor devices are used to monitor current and voltage of various power rails of AM62x SIP processor. The INA231 interfaces to the AM62x SIP through I2C interface (SoC\_I2C1). Four terminal, high precision shunt resistors are provided to measure load current.

Table 2-14. INA I2C Device Address

| Source      | Supply Net  | Device Address | Value of the Shunt Connected to the Supply Rail |

|-------------|-------------|----------------|-------------------------------------------------|

| VCC_CORE    | VDD_CORE    | 0x40           | 1mΩ± 1%                                         |

| VCC_3V3_SYS | SoC_DVDD3V3 | 0x4C           | 10mΩ± 1%                                        |

| VCC_1V8     | SoC_DVDD1V8 | 0x45           | 10mΩ± 1%                                        |

| VDDA1V8     | VDDA_1V8    | 0x4D           | 10mΩ± 1%                                        |

| VCC1V1_DDR  | VDD_DDR     | 0x47           | 10mΩ± 1%                                        |

Hardware www.ti.com

### 2.20 EVM User Setup/Configuration

### 2.20.1 EVM DIP Switches

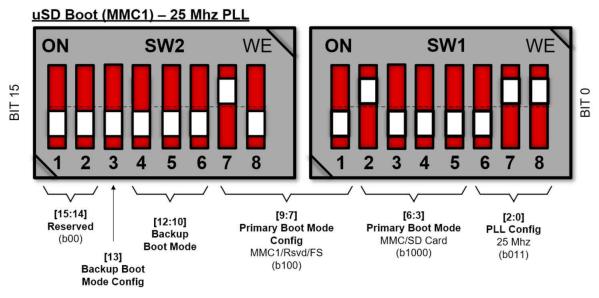

AM62x SIP SK EVM has two 8 - position DIP Switch to set the SoC Boot mode and related parameters.

#### 2.20.2 Boot Modes

The boot mode for the AM62x SIP SK EVM board is defined by two banks of switches SW1 and SW2 or by the I2C buffer connected to the Test automation connector. This allows for AM62x SIP SoC Boot mode control by either the user (DIP Switch Control) or by the Test Automation connector.

All the bits of switch (SW1 and SW2) have weak pull-down resistor and a strong pull up resistor as shown in below picture. Note that OFF setting provides a low logic level ('0') and an ON setting provides a high logic level ('1').

Note: Actual Board Silkscreen May Appear Inverted in this Orientation. Follow Physical Switch Text

Figure 2-27. Boot Mode Switch Configuration for SD Boot

The boot mode pins of the SoC have associated alternate functions during normal operation. Hence isolation is provided using Buffer IC's to cater for alternate pin functionality. The output of the buffer is connected to the boot mode pins on the AM62x SIP and the output is enabled when the boot mode is needed during a reset cycle.

The input to the buffer is connected to the DIP switch circuit and to the output of an I2C buffer set by the test automation circuit. If the test automation circuit is going to control the bootmode, then all the switches are manually set to the OFF position. The boot mode buffer is powered by an always ON power supply to make sure that the boot mode remains present even if the SoC power is cycled.

Switch SW1 and SW2 bits [15:0] are used to set the SoC Boot mode.

The switch map to the boot mode functions is provided in the tables below.

Table 2-15. Boot Mode Pin Mapping

|          |          |                                |        |        |       |                    |                    |      |         | ,        |      |      |       |            |      |

|----------|----------|--------------------------------|--------|--------|-------|--------------------|--------------------|------|---------|----------|------|------|-------|------------|------|

| Bit15    | Bit14    | Bit13                          | Bit12  | Bit11  | Bit10 | Bit9               | Bit8               | Bit7 | Bit6    | Bit5     | Bit4 | Bit3 | Bit2  | Bit1       | Bit0 |

| Reserved | Reserved | Backup boot mode configuration | Backup | boot m | ode   | Primary<br>configu | / boot m<br>ration | ode  | Primary | / boot m | ode  |      | PLLCo | nfiguratio | on   |

The table below gives details of PLL reference clock selection.

#### Note

BOOT-MODE[0:2] – Denote system clock frequency for PLL configuration. By default, this bits are set for 25 MHz.

Table 2-16. PLL Reference Clock Selection BOOTMODE[2:0]

| Bit 2 | Bit 1 | Bit 0 | PLL REF CLK (MHz) |

|-------|-------|-------|-------------------|

| OFF   | OFF   | OFF   | RSVD              |

| OFF   | OFF   | ON    | RSVD              |

| OFF   | ON    | OFF   | 24                |

| OFF   | ON    | ON    | 25                |

| ON    | OFF   | OFF   | 26                |

| ON    | OFF   | ON    | RSVD              |

| ON    | ON    | OFF   | RSVD              |

| ON    | ON    | ON    | RSVD              |

The table below provides primary boot device selection details.

### Note

BOOT-MODE[3:6] – This provides primary boot mode configuration to select the requested boot mode after POR, that is, the peripheral/memory to boot from.

Table 2-17. Boot Device Selection BOOTMODE[6:3]

| Table 2 11: Boot Bevies edication Boot Mobile 10:0] |       |       |       |                                 |  |  |

|-----------------------------------------------------|-------|-------|-------|---------------------------------|--|--|

| Bit 6                                               | Bit 5 | Bit 4 | Bit 3 | Primary Boot Device<br>Selected |  |  |

| OFF                                                 | OFF   | OFF   | OFF   | Serial NAND                     |  |  |

| OFF                                                 | OFF   | OFF   | ON    | OSPI                            |  |  |

| OFF                                                 | OFF   | ON    | OFF   | QSPI                            |  |  |

| OFF                                                 | OFF   | ON    | ON    | SPI                             |  |  |

| OFF                                                 | ON    | OFF   | OFF   | Ethernet RGMII1                 |  |  |

| OFF                                                 | ON    | OFF   | ON    | Ethernet RMII1                  |  |  |

| OFF                                                 | ON    | ON    | OFF   | I2C                             |  |  |

| OFF                                                 | ON    | ON    | ON    | UART                            |  |  |

| ON                                                  | OFF   | OFF   | OFF   | MMC/SD card                     |  |  |

| ON                                                  | OFF   | OFF   | ON    | eMMC                            |  |  |

| ON                                                  | OFF   | ON    | OFF   | USB0                            |  |  |

| ON                                                  | OFF   | ON    | ON    | GPMC NAND                       |  |  |

| ON                                                  | ON    | OFF   | OFF   | GPMC NOR                        |  |  |

| ON                                                  | ON    | OFF   | ON    | Rsvd                            |  |  |

| ON                                                  | ON    | ON    | OFF   | xSPI                            |  |  |

| ON                                                  | ON    | ON    | ON    | Noboot/Dev Boot                 |  |  |

|                                                     |       |       |       |                                 |  |  |

The below table provides backup boot mode selection details.

#### Note