# DRV10866 Lock Detection Functionality

### Rick Duncan

### **ABSTRACT**

This document is provided as a supplement to the DRV10866 data sheet. It details how the DRV10866 can falsely detect a locked rotor and the recommended workaround procedures.

|   |                      | Contents                                                                                                               |   |

|---|----------------------|------------------------------------------------------------------------------------------------------------------------|---|

| 1 |                      | duction                                                                                                                |   |

| 2 | False Lock Detection |                                                                                                                        | 2 |

|   | 2.1                  | Description of Circuit                                                                                                 | 2 |

|   | 2.2                  | Target Motor Speed is Fixed Inside the False Detection Range of 101.6 Hz ±10% at V <sub>cc</sub> 5 V Room Temperature  | 3 |

|   | 2.3                  | Target Motor Speed is Fixed Outside the False Detection Range of 101.6 Hz ±10% at V <sub>cc</sub> 5 V Room Temperature | 3 |

|   | 2.4                  | Target Motor Speed is Variable with FG Inside the False Detect Window                                                  | 3 |

| 3 | Conc                 | lusion                                                                                                                 | 3 |

|   |                      | List of Figures                                                                                                        |   |

| 1 | Timir                | ng of Internal Sampling Clock Versus FG Output                                                                         | 2 |

### **Trademarks**

All trademarks are the property of their respective owners.

Introduction www.ti.com

#### 1 Introduction

The DRV10866 is an integrated device providing the benefits of low cost, low size, and ease of use. Under certain conditions, it has been determined that the lock detection mechanism can detect a locked rotor condition that is not real. If a locked rotor condition is incorrectly detected, the DRV10866 will stop driving the motor, wait for some time, and then re-start.

This false lock condition occurs when a number of conditions are met. The information in Section 2 describes the condition in which the lock is incorrectly detected and recommended workaround procedures.

### 2 False Lock Detection

### 2.1 Description of Circuit

The lock detection circuit inside the DRV10866 monitors the FG signal to determine if the signal is static. If the FG signal is sampled as a static value for approximately 305 clocks of an internal sampling clock, the internal logic signals that the rotor is locked. When this condition occurs, the DRV10866 is reset and after approximately 5 seconds is restarted.

The internal sampling clock reference is set to approximately 101.6 Hz, with a variance of 10% at  $V_{\rm CC}$  5 V room temperature.

It has been observed that some devices falsely detect lock if the FG signal matches this internal sampling clock. An example is when the FG signal is within 0.16% of the sampling clock. When this condition occurs, the 305 samples will occur in either the high side or the low side of the FG signal.

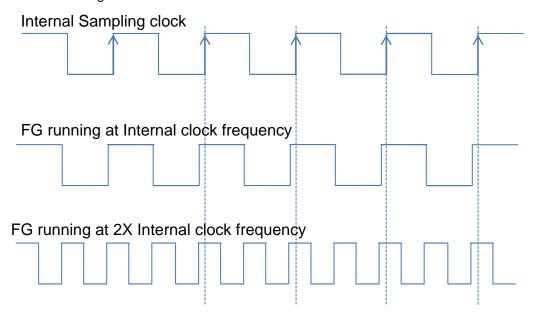

Figure 1 shows the internal sampling clock sampling a logical high on the FG signal for 5 consecutive samples. If this is continued through 305 samples, the internal lock detection signals that the rotor is locked.

The relationship of the variation of FG and the internal sampling clock are inversely proportional.

(1)

As FG increases by a power of 2, the variation allowed decreases by the same power of 2. This means that it becomes less likely for a false lock to be detected as the motor speed increases.

As seen in Figure 1, the sampling of FG at multiples of the internal sampling clock can also result in false lock conditions. As the FG frequency increases by even multiples of the sample clock, the allowable variation of the FG signal decreases. For example, if FG is twice the internal sampling clock the allowed variation of the FG signal reduces to 0.08%.

Figure 1. Timing of Internal Sampling Clock Versus FG Output

www.ti.com False Lock Detection

The false lock condition depends on several conditions. The motor speed can vary as the temperature of the device varies. The voltage of the DRV10866 can vary from board to board or system to system. The internal sampling clock can vary due to process variations.

If the false lock is detected, the recommended workaround procedures are listed below. These workarounds depend on the application. In some applications, the target speed is fixed. In other applications, the target speed may vary from zero to the maximum motor speed.

## 2.2 Target Motor Speed is Fixed Inside the False Detection Range of 101.6 Hz $\pm$ 10% at $V_{cc}$ 5 V Room Temperature

Use FGS input to change the FG frequency such that it will be outside of the window. The FG signal can either be increased or decreased by a multiple of 2 on power up by changing the FGS input.

# 2.3 Target Motor Speed is Fixed Outside the False Detection Range of 101.6 Hz $\pm 10\%$ at $V_{cc}$ 5 V Room Temperature

No action is required.

### 2.4 Target Motor Speed is Variable with FG Inside the False Detect Window

There are three possible actions if the lock detection occurs falsely. All actions change the speed of the motor:

- If using the PWM input to adjust the motor speed, raise or lower the PWM input duty cycle by 1%. This will move the FG signal away from the internal sampling clock frequency.

- If using V<sub>CC</sub> to adjust the motor speed, raise or lower V<sub>CC</sub> by 10 mV. This will move the FG signal away from the internal sampling clock frequency.

- Modulate the PWM input between 2 duty cycles 1% to 2% apart. Do this every 1 to 1.5 seconds to

prevent the FG frequency matching the internal sampling frequency. The result is an average speed of

the two PWM duty cycles.

#### 3 Conclusion

The lock detect circuitry of the DRV10866 device can improperly report a rotor locked condition when several events align. The alignment of these events can be avoided by using the workarounds described above.

Revision History www.ti.com

### **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cł | Changes from Original (September 2013) to A Revision                                                               |   |  |  |

|----|--------------------------------------------------------------------------------------------------------------------|---|--|--|

| •  | Changed the second paragraph of Section 2.1                                                                        | 2 |  |  |

| •  | Changed From: 101.6Hz +/-30% To: 101.6 Hz $\pm$ 10 at $V_{cc}$ 5 V Room Temperature in Section 2.2 and Section 2.3 | 3 |  |  |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated