# Programmable Yn Clock Phase Shift With SN74SSQEA32882 DDR3 Register

Christian Schmoeller and Siva RaghuRam

CDC - Clock Distribution Circuits

#### **ABSTRACT**

This application report describes how to shift the Yn clock position on TI's DDR3 register SN74SSQEA32882 (V4.2) by using extended CMR commands. This Yn clock position shift can be used for the analysis of post register margin at the DRAMs. Note that this application report does not apply to SN74SSQE32882 (V3.1).

## 1 CMR Commands

SSTE32882-compliant DDR3 registers have internal control bits (also called Control Mode registers) to configure certain device features.

If the device is operated in Dual Chip Select Mode (QCSEN#=HIGH), then the control bits are accessed by the simultaneous assertion of both DCS0# and DCS1# LOW.

If Quad Chip Select Mode is enabled (QCSEN#=LOW), then the control bits are accessed by the simultaneous LOW assertion of both DCS0# and DCS1# or DCS2# and DCS3# or all four DCS[n:0].

SSTE32882-compliant DDR3 registers allocate decoding for up to 16 words of control bits, RC0 through RC15. Selection of each word of control bits is presented on inputs DA0 through DA2 and DBA2. Data to be written into the configuration registers need to be presented on DA3, DA4, DBA0, and DBA1.

For more details on CMR commands and how to use them, see the SSTE32882 JEDEC Specification or TI application report SCAA102.

### 2 Extended CMR Commands

Extended CMR command to the register are not standardized by JEDEC; they only apply to TI DDR3 Registers. To access an extended CMR, the device has to be put into extended CMR mode by setting RC7 bit DA2 to 1.

The purpose of the extended CMRs is mainly for TI internal testing. Different device versions may have different mappings for extended CMRs.

## 3 Yn Clock Phase Shift Function of SN74SSQEA32882 (V4.2)

TI's DDR3 register SN74SSQEA32882 (V4.2) allows manual adjustment of the Yn edge position within the Command/Address (C/A) data eye. Note that this feature is not supported in TI register SN74SSQE32882 (V3.1).

The Yn clock edge phase can be modified with the following steps:

- 1. Enable Extended CMR range in RC7.

- 2. Disable C/A tracking of Yn in RC23.

- 3. Enable manual phase adjustment in RC17.

- 4. Write manual phase adjust control word (PA<19:0>, see Table 1). This requires programming of RC18-RC22.

- 5. Switch back to standard CMR range in RC7 (if standard CMR programming is required)

Table 1. Simplified Phase Adjust Control Word Lookup Table<sup>(1)</sup>

| Phase<br>Adjustment<br>in Degrees | Phase Adjust Control Word<br>PA<0:19> |     |     |     |        |  |  |

|-----------------------------------|---------------------------------------|-----|-----|-----|--------|--|--|

|                                   | <0>                                   | <1> | <2> | <3> | <4:19> |  |  |

| 0°                                | 0                                     | 0   | 0   | 0   | 0x0000 |  |  |

| 22.5°                             | 1                                     | 0   | 0   | 0   | 0xFFFF |  |  |

| 45°                               | 1                                     | 1   | 0   | 0   | 0x0000 |  |  |

| 67.5°                             | 0                                     | 1   | 0   | 0   | 0xFFFF |  |  |

| 90°                               | 0                                     | 1   | 1   | 0   | 0x0000 |  |  |

| 112.5°                            | 1                                     | 1   | 1   | 0   | 0xFFFF |  |  |

| 135°                              | 1                                     | 1   | 1   | 1   | 0x0000 |  |  |

| 157.5°                            | 0                                     | 1   | 1   | 1   | 0xFFFF |  |  |

| 180°                              | 0                                     | 1   | 0   | 1   | 0x0000 |  |  |

| 202.5°                            | 1                                     | 1   | 0   | 1   | 0xFFFF |  |  |

| 225°                              | 1                                     | 0   | 0   | 1   | 0x0000 |  |  |

| 247.5°                            | 0                                     | 0   | 0   | 1   | 0xFFFF |  |  |

| 270°                              | 0                                     | 0   | 1   | 1   | 0x0000 |  |  |

| 292.5°                            | 1                                     | 0   | 1   | 1   | 0xFFFF |  |  |

| 315°                              | 1                                     | 0   | 1   | 0   | 0x0000 |  |  |

| 337.5°                            | 0                                     | 0   | 1   | 0   | 0xFFFF |  |  |

<sup>(1)</sup> More detailed lookup table available, if required.

## 3.1 CMR Sequence for Adjusting the Yn Phase

Table 2. CMR Sequence for Changing Yn Clock Phase

| CMR7  | Enable Extend                     | Hod CMP        |           |                |        |        |        |       |

|-------|-----------------------------------|----------------|-----------|----------------|--------|--------|--------|-------|

|       |                                   |                |           |                |        |        |        |       |

| DBA2  | DA2                               | DA1            | DA0       |                | DBA1   | DBA0   | DA4    | DA3   |

| 0     | 1                                 | 1              | 1         |                | 0      | 0      | 0      | 1     |

|       |                                   |                |           | it 8 clock cyc | les    |        |        |       |

| CMR23 | Disabled C/A                      | Tracking of Yr | 1         |                |        |        | 1      |       |

| DBA2  | DA2                               | DA1            | DA0       |                | DBA1   | DBA0   | DA4    | DA3   |

| 1     | 0                                 | 0              | 1         |                | 0      | 0      | 1      | 0     |

|       |                                   |                | Wai       | it 8 clock cyc | les    |        |        |       |

| CMR17 | Enable Manua                      | al Phase Adjus | st        |                |        |        |        |       |

| DBA2  | DA2                               | DA1            | DA0       |                | DBA1   | DBA0   | DA4    | DA3   |

| 0     | 0                                 | 0              | 1         |                | 1      | 0      | 0      | 0     |

|       |                                   |                | Wai       | it 8 clock cyc | les    |        |        |       |

| CMR18 | <3:0> (Manual Phase Adjust Value) |                |           |                |        |        |        |       |

| DBA2  | DA2                               | DA1            | DA0       |                | DBA1   | DBA0   | DA4    | DA3   |

| 0     | 0                                 | 1              | 0         |                | PA<3>  | PA<2>  | PA<1>  | PA<0> |

|       | 1                                 |                | Wai       | it 8 clock cyc | les    | 1      | II.    |       |

| CMR19 | <7:4> (Manual Phase Adjust Value) |                |           |                |        |        |        |       |

| DBA2  | DA2                               | DA1            | DA0       |                | DBA1   | DBA0   | DA4    | DA3   |

| 0     | 0                                 | 1              | 1         |                | PA<7>  | PA<6>  | PA<5>  | PA<4> |

|       |                                   |                | Wai       | it 8 clock cyc | les    |        |        |       |

| CMR20 | <11:8> (Manu                      | al Phase Adju  | st Value) |                |        |        |        |       |

| DBA2  | DA2                               | DA1            | DA0       |                | DBA1   | DBA0   | DA4    | DA3   |

| 0     | 1                                 | 0              | 0         |                | PA<11> | PA<10> | PA<9>  | PA<8> |

|       |                                   |                | Wai       | it 8 clock cyc | les    |        |        |       |

| CMR21 | <15:12> (Man                      | ual Phase Ad   |           |                |        |        |        |       |

| DBA2  | DA2                               | DA1            | DA0       |                | DBA1   | DBA0   | DA4    | DA3   |

| 0     | 1                                 | 0              | 1         |                | PA<15> | PA<14> | PA<13> | PA<12 |

|       |                                   |                | Wai       | it 8 clock cyc | les    |        |        |       |

| CMR22 | <19:16> (Man                      | ual Phase Ad   |           | ,-             |        |        |        |       |

| DBA2  | DA2                               | DA1            | DA0       |                | DBA1   | DBA0   | DA4    | DA3   |

| 1     | 0                                 | 0              | 1         |                | PA<19> | PA<18> | PA<17> | PA<16 |

|       |                                   |                |           | it 8 clock cyc |        |        | 1      |       |

| CMR7  | Switch back to                    | Standard CN    |           |                |        |        |        |       |

| DBA2  | DA2                               | DA1            | DA0       |                | DBA1   | DBA0   | DA4    | DA3   |

| 0     | 1                                 | 1              | 1         | -              | 0      | 0      | 0      | 0     |

References www.ti.com

## 3.2 Example Phase Adjustments of Yn Clock

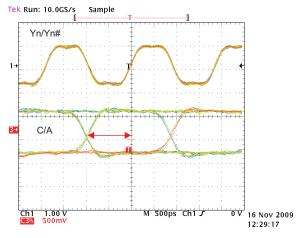

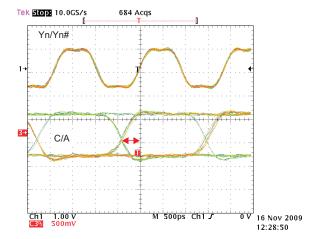

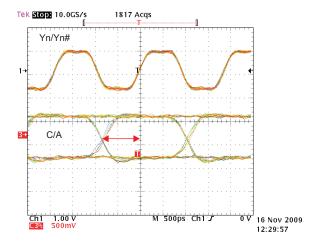

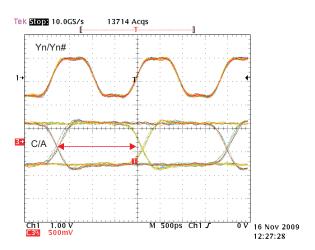

The following scope shots are examples of how the Yn clock phase can be changed within the C/A data eye.

Figure 1. Yn Clock Default Phase Setting (Center of C/A eye)

Figure 2. Yn Clock With Phase Adjust Value 0°

Figure 3. Yn Clock With Phase Adjust Value 90°

Figure 4. Yn Clock With Phase Adjust Value 270°

## 4 References

- 1. SN74SSQE32882, 28-Bit to 56-Bit Registered Buffer WIth Address Parity Test One Pair to Four Pair Differential Clock PLL Driver data sheet (SCAS857)

- 2. SN74SSQEA32882, 28-Bit to 56-Bit Registered Buffer WIth Address Parity Test One Pair to Four Pair Differential Clock PLL Driver data sheet (SCAS879)

- 3. CMR Programming for DDR3 Registers application report (SCAA102)

- 4. SSTE32882 JEDEC Specification

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                 |                                   |

|-----------------------------|------------------------|------------------------------|-----------------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio                        | www.ti.com/audio                  |

| Data Converters             | dataconverter.ti.com   | Automotive                   | www.ti.com/automotive             |

| DLP® Products               | www.dlp.com            | Communications and Telecom   | www.ti.com/communications         |

| DSP                         | <u>dsp.ti.com</u>      | Computers and<br>Peripherals | www.ti.com/computers              |

| Clocks and Timers           | www.ti.com/clocks      | Consumer Electronics         | www.ti.com/consumer-apps          |

| Interface                   | interface.ti.com       | Energy                       | www.ti.com/energy                 |

| Logic                       | logic.ti.com           | Industrial                   | www.ti.com/industrial             |

| Power Mgmt                  | power.ti.com           | Medical                      | www.ti.com/medical                |

| Microcontrollers            | microcontroller.ti.com | Security                     | www.ti.com/security               |

| RFID                        | www.ti-rfid.com        | Space, Avionics & Defense    | www.ti.com/space-avionics-defense |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video and Imaging            | www.ti.com/video                  |

|                             |                        | Wireless                     | www.ti.com/wireless-apps          |