LMK03806 SNAS522K - SEPTEMBER 2011 - REVISED DECEMBER 2023

# LMK03806 Ultra Low Jitter Clock Generator With 14 Programmable Outputs

### 1 Features

- High performance, ultra low jitter clock generator

- Low jitter:

- < 50-fs jitter (1.875 MHz 20 MHz) at 312.5-</li> MHz output frequency

- < 150-fs jitter (12 kHz 20 MHz) at 312.5-MHz</li> output frequency

- Generates multiple clocks from a low-cost crystal or external clock

- 14 outputs with programmable output format (LVDS, LVPECL, CMOS)

- Up to 8 unique output frequencies.

- Industrial temperature range: -40°C to 85°C

- Tunable VCO frequency: 2.37 GHz 2.6 GHz

- Programmable dividers to generate multiple clocks from a low-cost crystal.

- 3.15-V to 3.45-V operation

# 2 Applications

- Ultra high-speed serial interfaces in SONET/SDH

- Multi-gigabit Ethernet and Fiber Channel line cards

- Base Band Units (BBUs) for RAN applications

- GPON OLT/ONU, high-speed serial interface such as PCIe, XAUI, SATA, SAS

- Clocking ADC, and DACs

- Clocking DSP, microprocessors, and FPGAs

# 3 Description

The LMK03806 device is a high-performance, ultra low-jitter, multi-rate clock generator capable of synthesizing 8 different frequencies on 14 outputs at frequencies of up to 2.6 GHz. Each output clock is programmable in LVDS, LVPECL or LVCMOS format. The LMK03806 integrates a high-performance integer-N PLL, low-noise VCO, and programmable output dividers to generate multiple reference clocks for SONET, Ethernet, Fiber Channel, XAUI, Backplane, PCIe, SATA, and Network Processors from a low-cost crystal.

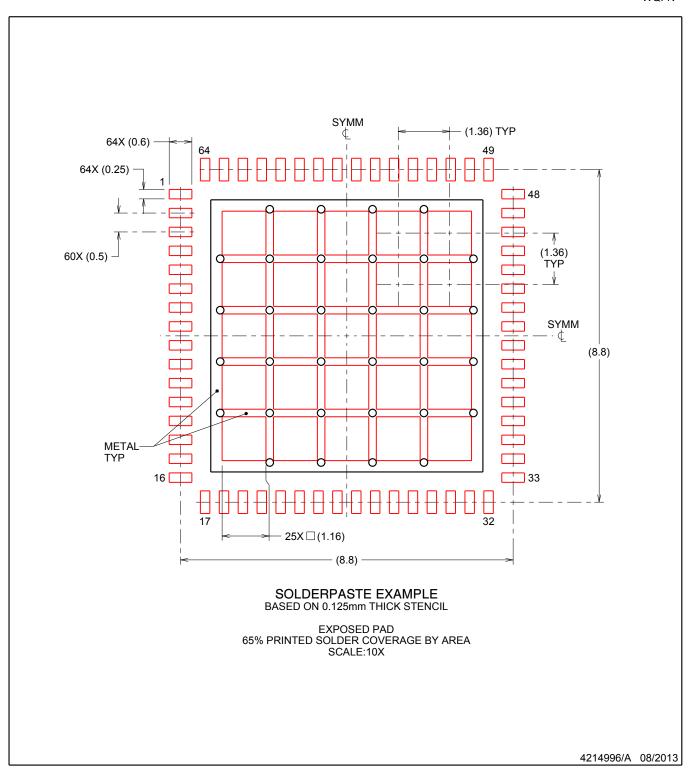

### **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE(2)   |

|-------------|------------------------|-------------------|

| LMK03806    | WQFN (64)              | 9.00 mm × 9.00 mm |

- For all available packages, see Section 12. (1)

- (2) The package size (length × width) is a nominal value and includes pins, where applicable.

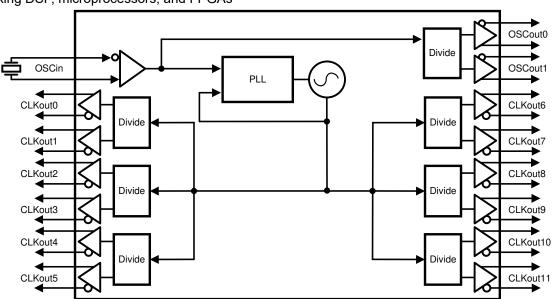

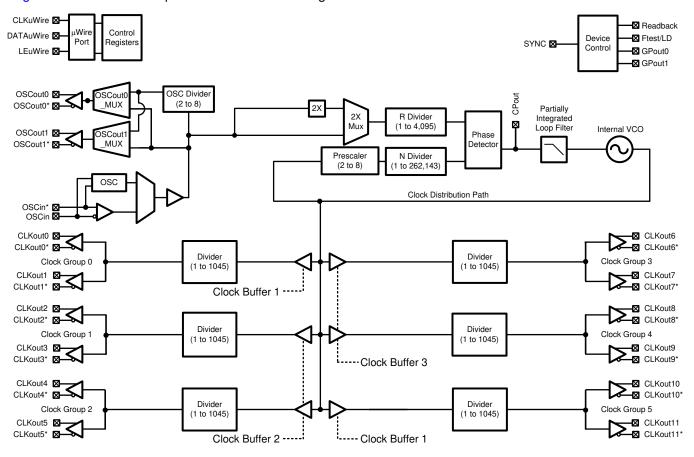

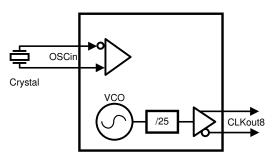

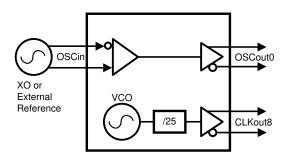

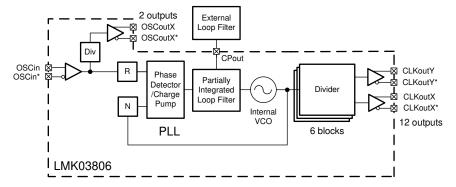

**Functional Block Diagram**

# **Table of Contents**

| 1 Features                                          | 9.1 Device Support41                                  |

|-----------------------------------------------------|-------------------------------------------------------|

| 2 Applications1                                     | 9.2 Documentation Support41                           |

| 3 Description1                                      | 9.3 Receiving Notification of Documentation Updates41 |

| 4 Pin Configuration and Functions3                  | 9.4 Support Resources41                               |

| 5 Specifications5                                   | 9.5 Trademarks41                                      |

| 5.1 Absolute Maximum Ratings5                       | 9.6 Electrostatic Discharge Caution41                 |

| 5.2 ESD Ratings5                                    | 9.7 Glossary41                                        |

| 5.3 Recommended Operating Conditions5               | 10 Register Maps42                                    |

| 5.4 Thermal Information6                            | 10.1 Default Device Register Settings After Power     |

| 5.5 Electrical Characteristics6                     | On Reset43                                            |

| 5.6 Timing Requirements14                           | 10.2 Register R0 TO R545                              |

| 5.7 Typical Characteristics                         | 10.3 Registers R6 TO R847                             |

| 6 Parameter Measurement Information16               | 10.4 REGISTER R948                                    |

| 6.1 Differential Voltage Measurement Terminology 16 | 10.5 REGISTER R1048                                   |

| 7 Detailed Description17                            | 10.6 REGISTER R1150                                   |

| 7.1 Overview                                        | 10.7 REGISTER R1251                                   |

| 7.2 Functional Block Diagrams17                     | 10.8 REGISTER R1352                                   |

| 7.3 Features Description19                          | 10.9 REGISTER 1452                                    |

| 7.4 Device Functional Modes21                       | 10.10 REGISTER 1653                                   |

| 7.5 Programming22                                   | 10.11 REGISTER 2453                                   |

| 8 Application and Implementation24                  | 10.12 REGISTER 2656                                   |

| 8.1 Application Information                         | 10.13 REGISTER 2857                                   |

| 8.2 Typical Application30                           | 10.14 REGISTER 2957                                   |

| 8.3 System Examples36                               | 10.15 REGISTER 3058                                   |

| 8.4 Best Design Practices37                         | 10.16 REGISTER 3159                                   |

| 8.5 Power Supply Recommendations37                  | 11 Revision History 60                                |

| 8.6 Layout38                                        | 12 Mechanical, Packaging, and Orderable               |

| 9 Device and Documentation Support41                | Information60                                         |

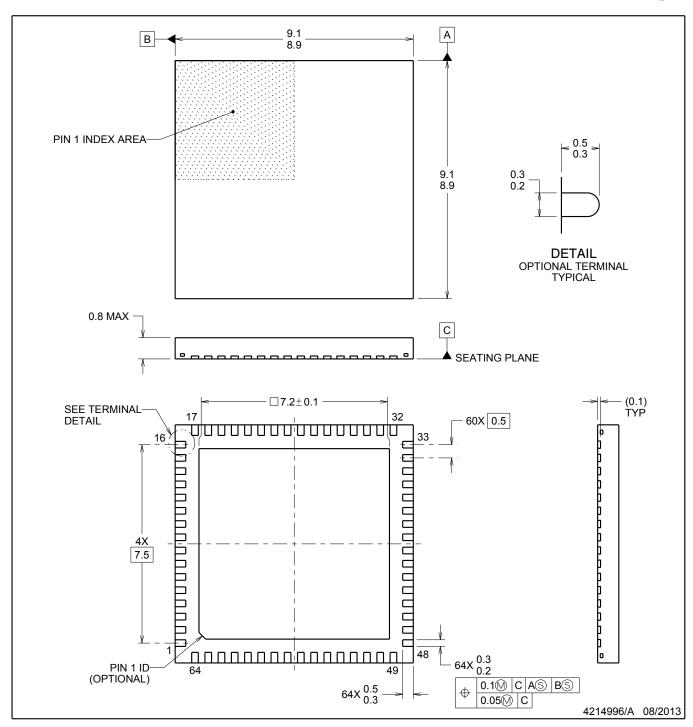

# 4 Pin Configuration and Functions

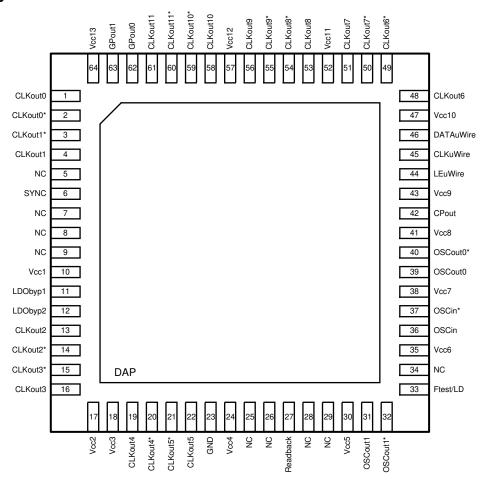

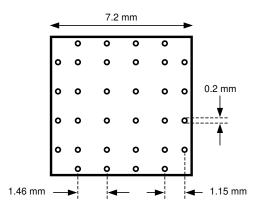

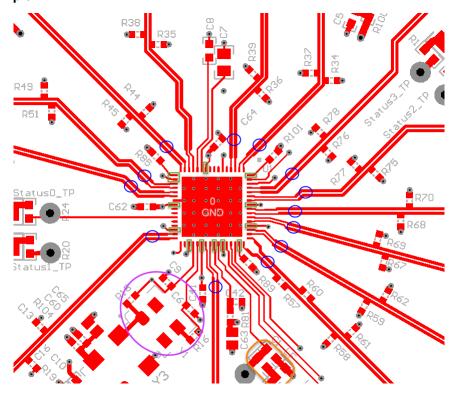

Figure 4-1. NKD Package 64-Pin WQFN Top View

Table 4-1. Pin Functions

| PIN                    | PIN    |     | TYPE         | DESCRIPTION                      |  |

|------------------------|--------|-----|--------------|----------------------------------|--|

| NAME                   | NO.    | I/O | IIFE         | DESCRIPTION                      |  |

| CLKout0, CLKout0*      | 1, 2   | 0   | Programmable | Clock output 0 (clock group 0).  |  |

| CLKout1*, CLKout1      | 3, 4   | 0   | Programmable | Clock output 1 (clock group 0).  |  |

| CLKout2, CLKout2*      | 13, 14 | 0   | Programmable | Clock output 2 (clock group 1).  |  |

| CLKout3*, CLKout3      | 15, 16 | 0   | Programmable | Clock output 3 (clock group 1).  |  |

| CLKout4, CLKout4*      | 19, 20 | 0   | Programmable | Clock output 4 (clock group 2).  |  |

| CLKout5*, CLKout5      | 21, 22 | 0   | Programmable | Clock output 5 (clock group 2).  |  |

| CLKout6, CLKout6*      | 48, 49 | 0   | Programmable | Clock output 6 (clock group 3).  |  |

| CLKout7*, CLKout7      | 50, 51 | 0   | Programmable | Clock output 7 (clock group 3).  |  |

| CLKout8, CLKout8*      | 53, 54 | 0   | Programmable | Clock output 8 (clock group 4).  |  |

| CLKout9*, CLKout9      | 55, 56 | 0   | Programmable | Clock output 9 (clock group 4).  |  |

| CLKout10,<br>CLKout10* | 58, 59 | 0   | Programmable | Clock output 10 (clock group 5). |  |

| CLKout11*,<br>CLKout11 | 60, 61 | 0   | Programmable | Clock output 11 (clock group 5). |  |

| CLKuWire               | 45     | I   | CMOS         | MICROWIRE Clock Input.           |  |

| CPout                  | 42     | 0   | ANLG         | Charge pump output.              |  |

Copyright © 2023 Texas Instruments Incorporated

# **Table 4-1. Pin Functions (continued)**

| PIN               | N                                |     | e 4-1. Pin Functions |                                                                                                                                                                            |

|-------------------|----------------------------------|-----|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | NO.                              | I/O | TYPE                 | DESCRIPTION                                                                                                                                                                |

| DAP               | DAP                              | _   | GND                  | DIE ATTACH PAD, connect to GND.                                                                                                                                            |

| DATAuWire         | 46                               | ı   | CMOS                 | MICROWIRE Data Input.                                                                                                                                                      |

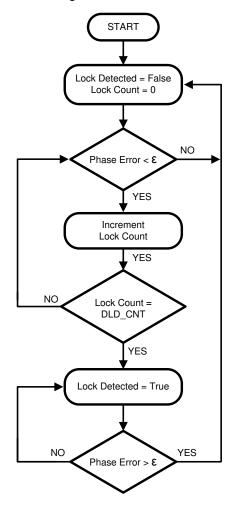

| Ftest/LD          | 33                               | 0   | Programmable         | Multiplexed Lock Detect and Test output pin.                                                                                                                               |

| GND               | 23                               | _   | PWR                  | Ground                                                                                                                                                                     |

| GPout0, GPout1    | 62, 63                           | 0   | CMOS                 | These pins can be programmed for general purpose output.                                                                                                                   |

| LDObyp1           | 11                               | _   | ANLG                 | LDO Bypass, bypassed to ground with 10 μF capacitor.                                                                                                                       |

| LDObyp2           | 12                               | _   | ANLG                 | LDO Bypass, bypassed to ground with a 0.1 μF capacitor.                                                                                                                    |

| LEuWire           | 44                               | I   | CMOS                 | MICROWIRE Latch Enable Input.                                                                                                                                              |

| NC                | 5, 7, 8, 9, 25, 26,<br>28,29, 34 | _   | Do Not Connect       | These pins must be left floating. Do NOT ground.                                                                                                                           |

| OSCout1, OSCout1* | 31, 32                           | 0   | LVPECL               | Buffered output 1 of OSCin port.                                                                                                                                           |

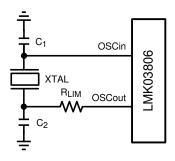

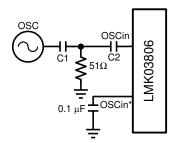

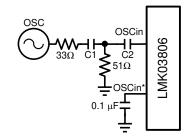

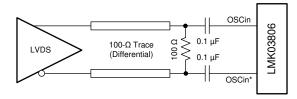

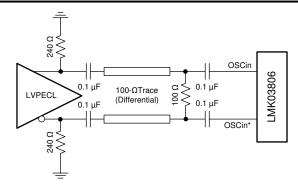

| OSCin, OSCin*     | 36, 37                           | I   | ANLG                 | Reference input to PLL. Reference input may be:  A Crystal for use with the internal crystal oscillator circuit.  A XO, TCXO, or other external clock. Must be AC Coupled. |

| OSCout0, OSCout0* | 39, 40                           | 0   | Programmable         | Buffered output 0 of OSCin port.                                                                                                                                           |

| Readback          | 27                               | 0   | CMOS                 | Pin that can be used to readback register information.                                                                                                                     |

| SYNC              | 6                                | I   | CMOS                 | Clock synchronization input.                                                                                                                                               |

| Vcc1              | 10                               | _   | PWR                  | Power supply for VCO LDO.                                                                                                                                                  |

| Vcc2              | 17                               | _   | PWR                  | Power supply for clock group 1: CLKout2 and CLKout3.                                                                                                                       |

| Vcc3              | 18                               | _   | PWR                  | Power supply for clock group 2: CLKout4 and CLKout5.                                                                                                                       |

| Vcc4              | 24                               | _   | PWR                  | Power supply for digital.                                                                                                                                                  |

| Vcc5              | 30                               | _   | PWR                  | Power supply for clock inputs.                                                                                                                                             |

| Vcc6              | 35                               | _   | PWR                  | Power supply. No bypassing required on this pin.                                                                                                                           |

| Vcc7              | 38                               | _   | PWR                  | Power supply for OSCin port.                                                                                                                                               |

| Vcc8              | 41                               | _   | PWR                  | Power supply for PLL charge pump.                                                                                                                                          |

| Vcc9              | 43                               | _   | PWR                  | Power supply for PLL.                                                                                                                                                      |

| Vcc10             | 47                               | _   | PWR                  | Power supply for clock group 3: CLKout6 and CLKout7.                                                                                                                       |

| Vcc11             | 52                               | _   | PWR                  | Power supply for clock group 4: CLKout8 and CLKout9.                                                                                                                       |

| Vcc12             | 57                               | _   | PWR                  | Power supply for clock group 5: CLKout10 and CLKout11.                                                                                                                     |

| Vcc13             | 64                               | _   | PWR                  | Power supply for clock group 0: CLKout0 and CLKout1.                                                                                                                       |

# **5 Specifications**

# 5.1 Absolute Maximum Ratings

See (1) (3).

|                  |                                           | MIN        | MAX                   | UNIT |

|------------------|-------------------------------------------|------------|-----------------------|------|

| V <sub>CC</sub>  | Supply voltage (2)                        | -0.3       | 3.6                   | V    |

| V <sub>IN</sub>  | Input voltage                             | -0.3       | V <sub>CC</sub> + 0.3 | V    |

| TL               | Lead temperature (solder 4 seconds)       |            | 260                   | °C   |

| TJ               | Junction temperature                      |            | 150                   | °C   |

| I <sub>IN</sub>  | Differential input current (OSCin/OSCin*) | <b>-</b> 5 | 5                     | mA   |

| MSL              | Moisture sensitivity level                |            | 3                     |      |

| T <sub>stg</sub> | Storage temperature                       | -65        | 150                   | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) Never to exceed 3.6 V.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

# 5.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±750  | V    |

|                    |                         | Machine model (MM)                                                             | ±150  |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2000 V may actually have higher performance.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±750 V may actually have higher performance.

## 5.3 Recommended Operating Conditions

Copyright © 2023 Texas Instruments Incorporated

|                 |                      |                         | MIN  | NOM | MAX  | UNIT |

|-----------------|----------------------|-------------------------|------|-----|------|------|

| T <sub>A</sub>  | Ambient temperature  | V <sub>CC</sub> = 3.3 V | -40  | 25  | 85   | °C   |

| TJ              | Junction temperature | V <sub>CC</sub> = 3.3 V |      |     | 125  | °C   |

| V <sub>CC</sub> | Supply voltage       |                         | 3.15 | 3.3 | 3.45 | V    |

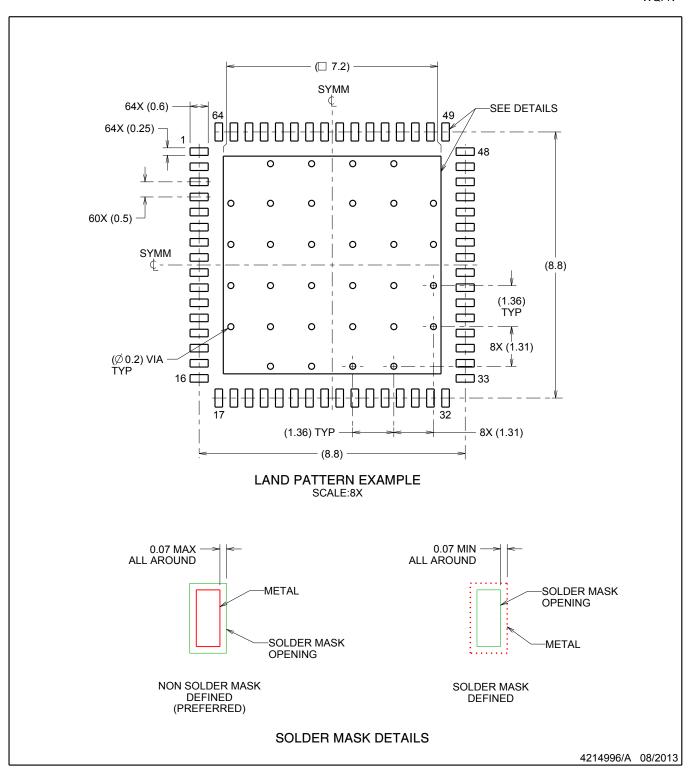

## **5.4 Thermal Information**

|                        |                                                                            | LMK03806   |      |

|------------------------|----------------------------------------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                                              | NKD (WQFN) | UNIT |

|                        |                                                                            | 64 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance on 4-layer JEDEC PCB <sup>(2)</sup> | 25.2       | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance <sup>(3)</sup>                   | 6.9        | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance                                       | 4.0        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter                                 | 0.1        | °C/W |

| $\Psi_{JB}$            | Junction-to-board characterization parameter                               | 4.0        | °C/W |

| $R_{\theta JC(bot)}$   | Junction-to-case (bottom) thermal resistance                               | 0.8        | °C/W |

- (1) For more information about traditional and new thermal metrics, see the Semiconductors and IC Package Thermal Metrics application report (SPRA953).

- Specification assumes 32 thermal vias connect the die attach pad to the embedded copper plane on the 4-layer JEDEC PCB. These vias play a key role in improving the thermal performance of the WQFN. Note that the JEDEC PCB is a standard thermal measurement PCB and does not represent best performance a PCB can achieve. TI recommends that the maximum number of vias be used in the board layout. R <sub>0.JA</sub> is unique for each PCB.

- (3) Case is defined as the DAP (die attach pad)

# 5.5 Electrical Characteristics

$3.15~V \le V_{CC} \le 3.45~V, -40^{\circ}C \le T_{A} \le 85^{\circ}C$ , Junction Temperature  $T_{J} \le 125^{\circ}C$ . Typical values represent most likely parametric norms at  $V_{CC} = 3.3~V, T_{A} = 25^{\circ}C$ , at *Recommended Operating Conditions* at the time of product characterization and are not ensured. (3)

|                           | PARAMETER                                                      | TEST CONDITIONS                                                                  | MIN  | TYP | MAX      | UNIT |

|---------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------|------|-----|----------|------|

| CURRENT CC                | DNSUMPTION                                                     |                                                                                  |      |     | <u>'</u> |      |

| I <sub>CC_PD</sub>        | Powerdown supply current                                       | No DC path to ground on OSCout1/1*(1)                                            |      | 1   |          | mA   |

| I <sub>CC_CLKS</sub>      | Supply current with all clocks enabled <sup>(2)</sup>          | CLKoutX_Y_DIV = 16,<br>CLKoutX_TYPE = 1 (LVDS),<br>PLL locked                    |      | 445 |          | mA   |

| EXTERNAL C                | LOCK (OSCin) SPECIFICATIONS                                    |                                                                                  |      |     |          |      |

| f <sub>OSCin</sub>        | PLL reference Input <sup>(4)</sup>                             |                                                                                  | 1    |     | 500      | MHz  |

| SLEW <sub>OSCin</sub>     | PLL reference clock minimum slew rate on OSCin <sup>(9)</sup>  | 20% to 80%                                                                       | 0.15 | 0.5 |          | V/ns |

| $V_{OSCin}$               | Input voltage for OSCin or OSCin*(9)                           | AC coupled; Single-ended (Unused pin AC coupled to GND)                          | 0.2  |     | 2.4      | Vpp  |

| V <sub>ID</sub> OSCin     | Differential college                                           | AC coupled, see Figure 6-1                                                       | 0.2  |     | 1.55     | V    |

| V <sub>SS</sub> OSCin     | Differential voltage swing                                     |                                                                                  | 0.4  |     | 3.1      | Vpp  |

| V <sub>OSCin-offset</sub> | DC offset voltage between OSCin/<br>OSCin*<br>OSCinX* - OSCinX | Each pin AC coupled                                                              |      | 20  |          | mV   |

| f <sub>doubler_max</sub>  | Doubler input frequency <sup>(9)</sup>                         | EN_PLL_REF_2X = 1;<br>OSCin Duty Cycle 40% to 60%                                |      |     | 155      | MHz  |

| CRYSTAL OS                | CILLATOR MODE SPECIFICATIONS                                   |                                                                                  | -    |     | <u>.</u> |      |

| f                         | Crystal frequency range <sup>(9)</sup>                         | $R_{ESR} \le 40 \Omega$<br>$C_L \le 20 \text{ pF}$                               | 16   |     | 20.5     | MHz  |

| f <sub>XTAL</sub>         | Crystal frequency range (%)                                    | $R_{ESR} \le 80 \Omega$<br>$C_L \le 22 pF$                                       | 6    |     | 16       | MHz  |

| P <sub>XTAL</sub>         | Crystal power dissipation                                      | Vectron VXB1 crystal, 20.48 MHz, $R_{ESR} \le 40 \Omega$ $C_L \le 20 \text{ pF}$ |      | 120 |          | μW   |

| C <sub>IN</sub>           | Input capacitance of the OSCin port                            | -40°C to +85°C                                                                   |      | 6   |          | pF   |

| RMS JITTER I              | PERFORMANCE                                                    |                                                                                  |      |     |          |      |

www.ti.com

$3.15~V \le V_{CC} \le 3.45~V, -40^{\circ}C \le T_{A} \le 85^{\circ}C$ , Junction Temperature  $T_{J} \le 125^{\circ}C$ . Typical values represent most likely parametric norms at  $V_{CC} = 3.3~V, T_{A} = 25^{\circ}C$ , at *Recommended Operating Conditions* at the time of product characterization and are not ensured. (3)

|                                               | PARAMETER                                    | TEST CONDITIONS         | MIN TYP MAX | UNIT |

|-----------------------------------------------|----------------------------------------------|-------------------------|-------------|------|

|                                               | Integration bandwidth                        | 156.25 MHz, LVDS/LVPECL | 81          | fs   |

|                                               | 10 kHz to 1 MHz                              | 312.5 MHz, LVDS/LVPECL  | 85          | fs   |

|                                               |                                              | 100 MHz, LVDS           | 139         | fs   |

|                                               |                                              | 100 MHz, LVPECL         | 117         | fs   |

|                                               |                                              | 106.25 MHz, LVDS        | 145         | fs   |

| XO mode <sup>(14)</sup> (15) (16)             |                                              | 106.25 MHz, LVPECL      | 126         | fs   |

|                                               | Integration bandwidth 12 kHz to 20 MHz       | 156.25 MHz, LVDS        | 111         | fs   |

|                                               | TE KI IE to EO WII IE                        | 156.25 MHz, LVPECL      | 100         | fs   |

|                                               |                                              | 312.5 MHz, LVDS         | 108         | fs   |

|                                               |                                              | 312.5 MHz, LVPECL       | 95          | fs   |

|                                               |                                              | 622.08 MHz, LVDS/LVPECL | 141         | fs   |

|                                               | Integration bandwidth                        | 106.25 MHz, LVDS        | 78          | fs   |

|                                               | 637 kHz to 10 MHz                            | 106.25 MHz, LVPECL      | 60          | fs   |

|                                               | Integration bandwidth<br>1.875 MHz to 20 MHz | 156.25 MHz, LVDS        | 70          | fs   |

|                                               |                                              | 156.25 MHz, LVPECL      | 57          | fs   |

|                                               |                                              | 312.5 MHz, LVDS         | 57          | fs   |

|                                               |                                              | 312.5 MHz, LVPECL       | 43          | fs   |

|                                               | Integration bandwidth                        | 156.25 MHz, LVDS/LVPECL | 190         | fs   |

|                                               | 10 kHz to 1 MHz                              | 312.5 MHz, LVDS/LVPECL  | 200         | fs   |

|                                               |                                              | 100 MHz, LVDS           | 235         | fs   |

|                                               |                                              | 100 MHz, LVPECL         | 210         | fs   |

|                                               |                                              | 106.25 MHz, LVDS        | 280         | fs   |

|                                               |                                              | 106.25 MHz, LVPECL      | 250         | fs   |

|                                               | Integration bandwidth 12 kHz to 20 MHz       | 156.25 MHz, LVDS        | 200         | fs   |

|                                               | TE IN IE to EU IVII IE                       | 156.25 MHz, LVPECL      | 195         | fs   |

| Crystal mode iitter <sup>(10)</sup> (11) (12) |                                              | 312.5 MHz, LVDS         | 220         | fs   |

| jittor                                        |                                              | 312.5 MHz, LVPECL       | 190         | fs   |

|                                               |                                              | 622.08 MHz, LVDS/LVPECL | 255         | fs   |

|                                               | Integration bandwidth                        | 106.25 MHz, LVDS        | 90          | fs   |

|                                               | 637 kHz to 10 MHz                            | 106.25 MHz, LVPECL      | 65          | fs   |

|                                               |                                              | 156.25 MHz, LVDS        | 75          | fs   |

|                                               | Integration bandwidth                        | 156.25 MHz, LVPECL      | 65          | fs   |

|                                               | 1.875 MHz to 20 MHz                          | 312.5 MHz, LVDS         | 60          | fs   |

|                                               |                                              | 312.5 MHz, LVPECL       | 45          | fs   |

$3.15 \text{ V} \le \text{V}_{CC} \le 3.45 \text{ V}, -40 ^{\circ}\text{C} \le \text{T}_{A} \le 85 ^{\circ}\text{C}$ , Junction Temperature  $\text{T}_{J} \le 125 ^{\circ}\text{C}$ . Typical values represent most likely parametric norms at  $\text{V}_{CC} = 3.3 \text{ V}, \text{T}_{A} = 25 ^{\circ}\text{C}$ , at *Recommended Operating Conditions* at the time of product characterization and are not ensured. (3)

| ,                   | PARAMETER                                | TEST CONDITIONS | MIN | TYP N | IAX | UNIT   |

|---------------------|------------------------------------------|-----------------|-----|-------|-----|--------|

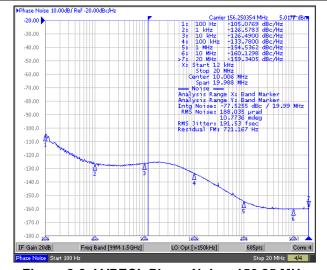

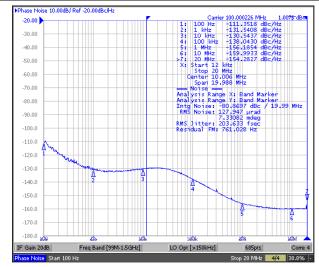

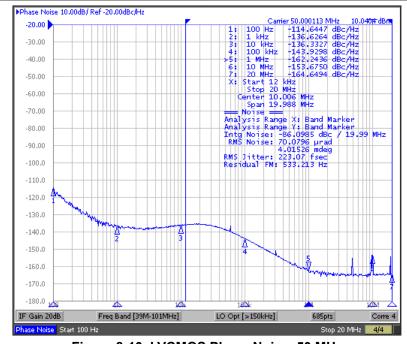

| PHASE NOISE F       | PERFORMANCE                              |                 |     |       |     |        |

|                     |                                          | 10 kHz          | -   | -142  |     | dBc/Hz |

| NO mode phase noise |                                          | 100 kHz         | -   | -143  |     | dBc/Hz |

|                     |                                          | 1 MHz           | -   | –157  |     | dBc/Hz |

|                     | 100 MHz (LVDS/LVPECL) <sup>(14)</sup>    | 10 MHz (LVDS)   | -   | -159  |     | dBc/Hz |

|                     |                                          | 20 MHz (LVDS)   | -   | -160  |     | dBc/Hz |

|                     |                                          | 10 MHz (LVPECL) | -   | -160  |     | dBc/Hz |

|                     |                                          | 20 MHz (LVPECL) | -   | -161  |     | dBc/Hz |

|                     |                                          | 10 kHz          | -   | -141  |     | dBc/Hz |

|                     |                                          | 100 kHz         | -   | -140  |     | dBc/Hz |

|                     |                                          | 1 MHz           | -   | -156  |     | dBc/Hz |

|                     | 106.25 MHz (LVDS/LVPECL) <sup>(15)</sup> | 10 MHz (LVDS)   | -   | -159  |     | dBc/Hz |

|                     |                                          | 20 MHz (LVDS)   | -   | -160  |     | dBc/Hz |

|                     |                                          | 10 MHz (LVPECL) | -   | -162  |     | dBc/Hz |

|                     |                                          | 20 MHz (LVPECL) | -   | -163  |     | dBc/Hz |

|                     | 156.25 MHz (LVDS/LVPECL) <sup>(14)</sup> | 10 kHz          | -   | –139  |     | dBc/Hz |

|                     |                                          | 100 kHz         | -   | -140  |     | dBc/Hz |

|                     |                                          | 1 MHz           | -   | –153  |     | dBc/Hz |

|                     |                                          | 10 MHz (LVDS)   | -   | –159  |     | dBc/Hz |

|                     |                                          | 20 MHz (LVDS)   | -   | –159  |     | dBc/Hz |

|                     |                                          | 10 MHz (LVPECL) | -   | -160  |     | dBc/Hz |

|                     |                                          | 20 MHz (LVPECL) | -   | -160  |     | dBc/Hz |

|                     |                                          | 10 kHz          | -   | -132  |     | dBc/Hz |

|                     |                                          | 100 kHz         | -   | –133  |     | dBc/Hz |

|                     |                                          | 1 MHz           | -   | –148  |     | dBc/Hz |

|                     | 312.5 MHz (LVDS/LVPECL) <sup>(14)</sup>  | 10 MHz (LVDS)   | -   | -154  |     | dBc/Hz |

|                     |                                          | 20 MHz (LVDS)   | -   | –155  |     | dBc/Hz |

|                     |                                          | 10 MHz (LVPECL) | -   | –157  |     | dBc/Hz |

|                     |                                          | 20 MHz (LVPECL) | -   | –158  |     | dBc/Hz |

|                     |                                          | 10 kHz          | -   | -123  |     | dBc/Hz |

|                     |                                          | 100 kHz         | -   | -121  |     | dBc/Hz |

|                     |                                          | 1 MHz           | -   | -143  |     | dBc/Hz |

|                     | 622.08 MHz (LVDS/LVPECL) <sup>(16)</sup> | 10 MHz (LVDS)   | -   | -154  |     | dBc/Hz |

|                     |                                          | 20 MHz (LVDS)   | -   | -154  |     | dBc/Hz |

|                     |                                          | 10 MHz (LVPECL) | -   | –157  |     | dBc/Hz |

|                     |                                          | 20 MHz (LVPECL) | -   | –158  |     | dBc/Hz |

$3.15~V \le V_{CC} \le 3.45~V, -40^{\circ}C \le T_{A} \le 85^{\circ}C$ , Junction Temperature  $T_{J} \le 125^{\circ}C$ . Typical values represent most likely parametric norms at  $V_{CC} = 3.3~V, T_{A} = 25^{\circ}C$ , at *Recommended Operating Conditions* at the time of product characterization and are not ensured. (3)

|                          | PARAMETER                                | TEST CONDITIONS | MIN TYP MAX | UNIT   |

|--------------------------|------------------------------------------|-----------------|-------------|--------|

|                          |                                          | 10 kHz          | -129        | dBc/Hz |

| Crystal mode phase noise |                                          | 100 kHz         | -137        | dBc/Hz |

|                          |                                          | 1 MHz           | -156        | dBc/Hz |

|                          | 100 MHz (LVDS/LVPECL) <sup>(10)</sup>    | 10 MHz (LVDS)   | -158        | dBc/Hz |

|                          |                                          | 20 MHz (LVDS)   | -159        | dBc/Hz |

|                          |                                          | 10 MHz (LVPECL) | -160        | dBc/Hz |

|                          |                                          | 20 MHz (LVPECL) | -161        | dBc/Hz |

|                          |                                          | 10 kHz          | -124        | dBc/Hz |

|                          |                                          | 100 kHz         | -137        | dBc/Hz |

|                          |                                          | 1 MHz           | -156        | dBc/Hz |

|                          | 106.25 MHz (LVDS/LVPECL) <sup>(11)</sup> | 10 MHz (LVDS)   | -158        | dBc/Hz |

|                          |                                          | 20 MHz (LVDS)   | -159        | dBc/Hz |

|                          |                                          | 10 MHz (LVPECL) | -160        | dBc/Hz |

|                          |                                          | 20 MHz (LVPECL) | -161        | dBc/Hz |

|                          | 156.25 MHz (LVDS/LVPECL) <sup>(10)</sup> | 10 kHz          | -125        | dBc/Hz |

|                          |                                          | 100 kHz         | -132        | dBc/Hz |

|                          |                                          | 1 MHz           | -153        | dBc/Hz |

| •                        |                                          | 10 MHz (LVDS)   | -158        | dBc/Hz |

| pridee rielee            |                                          | 20 MHz (LVDS)   | -159        | dBc/Hz |

|                          |                                          | 10 MHz (LVPECL) | -160        | dBc/Hz |

|                          |                                          | 20 MHz (LVPECL) | -160        | dBc/Hz |

|                          |                                          | 10 kHz          | -119        | dBc/Hz |

|                          |                                          | 100 kHz         | -126        | dBc/Hz |

|                          |                                          | 1 MHz           | -147        | dBc/Hz |

|                          | 312.5 MHz (LVDS/LVPECL) <sup>(10)</sup>  | 10 MHz (LVDS)   | -153        | dBc/Hz |

|                          |                                          | 20 MHz (LVDS)   | -154        | dBc/Hz |

|                          |                                          | 10 MHz (LVPECL) | -156        | dBc/Hz |

|                          |                                          | 20 MHz (LVPECL) | -157        | dBc/Hz |

|                          |                                          | 10 kHz          | -110        | dBc/Hz |

|                          |                                          | 100 kHz         | -120        | dBc/Hz |

|                          |                                          | 1 MHz           | -140        | dBc/Hz |

|                          | 622.08 MHz (LVDS/LVPECL) <sup>(12)</sup> | 10 MHz (LVDS)   | -153        | dBc/Hz |

|                          |                                          | 20 MHz (LVDS)   | -153        | dBc/Hz |

|                          |                                          | 10 MHz (LVPECL) | -154        | dBc/Hz |

|                          |                                          | 20 MHz (LVPECL) | -154        | dBc/Hz |

$3.15~V \le V_{CC} \le 3.45~V, -40^{\circ}C \le T_{A} \le 85^{\circ}C$ , Junction Temperature  $T_{J} \le 125^{\circ}C$ . Typical values represent most likely parametric norms at  $V_{CC} = 3.3~V, T_{A} = 25^{\circ}C$ , at *Recommended Operating Conditions* at the time of product characterization and are not ensured. (3)

|                           | PARAMETER                                                                                                                                                                                                        | TEST CONDITIONS                                                                                               | MIN TYP | MAX  | UNIT   |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------|------|--------|

| PLL PHASE DE              | TECTOR AND CHARGE PUMP SPECIFI                                                                                                                                                                                   | CATIONS                                                                                                       |         |      |        |

| f <sub>PD</sub>           | Phase detector frequency                                                                                                                                                                                         |                                                                                                               |         | 155  | MHz    |

|                           |                                                                                                                                                                                                                  | V <sub>CPout</sub> =V <sub>CC</sub> /2, PLL_CP_GAIN = 0                                                       | 100     |      | μA     |

|                           | 5                                                                                                                                                                                                                | V <sub>CPout</sub> =V <sub>CC</sub> /2, PLL_CP_GAIN = 1                                                       | 400     |      | μA     |

| I <sub>CPout</sub> SOURCE | PLL charge pump source current                                                                                                                                                                                   | V <sub>CPout</sub> =V <sub>CC</sub> /2, PLL_CP_GAIN = 2                                                       | 1600    |      | μA     |

|                           |                                                                                                                                                                                                                  | V <sub>CPout</sub> =V <sub>CC</sub> /2, PLL_CP_GAIN = 3                                                       | 3200    |      | μA     |

|                           |                                                                                                                                                                                                                  | V <sub>CPout</sub> =V <sub>CC</sub> /2, PLL_CP_GAIN = 0                                                       | -100    |      | μA     |

|                           | 5                                                                                                                                                                                                                | V <sub>CPout</sub> =V <sub>CC</sub> /2, PLL_CP_GAIN = 1                                                       | -400    |      | μA     |

| I <sub>CPout</sub> SINK   | PLL charge pump sink current                                                                                                                                                                                     | V <sub>CPout</sub> =V <sub>CC</sub> /2, PLL_CP_GAIN = 2                                                       | -1600   |      | μA     |

|                           |                                                                                                                                                                                                                  | V <sub>CPout</sub> =V <sub>CC</sub> /2, PLL_CP_GAIN = 3                                                       | -3200   |      | μA     |

| I <sub>CPout</sub> %MIS   | Charge pump sink/source mismatch                                                                                                                                                                                 | V <sub>CPout</sub> =V <sub>CC</sub> /2, T <sub>A</sub> = 25°C                                                 | 3%      | 10%  |        |

| $I_{CPout}V_{TUNE}$       | Magnitude of charge pump current vs. charge pump voltage variation                                                                                                                                               | 0.5 V < V <sub>CPout</sub> < V <sub>CC</sub> - 0.5 V<br>T <sub>A</sub> = 25°C                                 | 4%      |      |        |

| I <sub>CPout</sub> %TEMP  | Charge pump current vs. temperature variation                                                                                                                                                                    |                                                                                                               | 4%      |      |        |

| I <sub>CPout</sub> TRI    | Charge pump leakage                                                                                                                                                                                              | 0.5 V < V <sub>CPout</sub> < V <sub>CC</sub> - 0.5 V                                                          |         | 10   | nA     |

|                           | PLL 1/f noise at 10 kHz offset <sup>(5)</sup> .  Normalized to  1-GHz output frequency                                                                                                                           | PLL_CP_GAIN = 400 µA                                                                                          | -118    |      | dBc/Hz |

| PN10kHz                   |                                                                                                                                                                                                                  | PLL_CP_GAIN = 3200 μA                                                                                         | -121    |      | dBc/Hz |

| PN1Hz                     | Normalized phase noise contribution <sup>(6)</sup>                                                                                                                                                               | PLL_CP_GAIN = 400 µA                                                                                          | -222.5  |      | dBc/Hz |

| 1 111112                  |                                                                                                                                                                                                                  | PLL_CP_GAIN = 3200 µA                                                                                         | -227    |      | dBc/Hz |

|                           | PLL phase noise                                                                                                                                                                                                  | 1-kHz Offset                                                                                                  | -93     |      | dBc/Hz |

| L(f)                      | (Assumes a very wide bandwidth, noiseless crystal, 2500-MHz output                                                                                                                                               | 10 kHz                                                                                                        | -103    |      | dBc/Hz |

| L(I)                      | frequency, and 25-MHz phase detector                                                                                                                                                                             | 100-kHz Offset                                                                                                | -116    |      | dBc/Hz |

|                           | frequency)                                                                                                                                                                                                       | 1-MHz Offset                                                                                                  | -116    |      | dBc/Hz |

| INTERNAL VCC              | SPECIFICATIONS                                                                                                                                                                                                   |                                                                                                               |         |      |        |

| f <sub>VCO</sub>          | VCO tuning range                                                                                                                                                                                                 |                                                                                                               | 2370    | 2600 | MHz    |

|                           | Fine tuning sensitivity                                                                                                                                                                                          | f <sub>VCO</sub> at low end                                                                                   | 16      |      |        |

| K <sub>vco</sub>          | (The range displayed in the typical column indicates the lower sensitivity is typical at the lower end of the tuning range, and the higher tuning sensitivity is typical at the higher end of the tuning range). | f <sub>VCO</sub> at high end                                                                                  | 21      |      | MHz/V  |

| ΔT <sub>CL</sub>          | Allowable temperature drift for continuous lock <sup>(7)</sup> (9)                                                                                                                                               | After programming R30 for lock, no changes to output configuration are permitted to guarantee continuous lock |         | 125  | °C     |

|                           | Phase noise                                                                                                                                                                                                      | 10-kHz Offset                                                                                                 | -87     |      | dBc/Hz |

| L(f)                      | (Assumes a very narrow loop                                                                                                                                                                                      | 100-kHz Offset                                                                                                | -112    |      | dBc/Hz |

|                           | bandwidth)                                                                                                                                                                                                       | 1-MHz Offset                                                                                                  | -133    |      | dBc/Hz |

www.ti.com

$3.15~V \le V_{CC} \le 3.45~V, -40^{\circ}C \le T_{A} \le 85^{\circ}C$ , Junction Temperature  $T_{J} \le 125^{\circ}C$ . Typical values represent most likely parametric norms at  $V_{CC} = 3.3~V, T_{A} = 25^{\circ}C$ , at *Recommended Operating Conditions* at the time of product characterization and are not ensured. (3)

| PARAMETER                          |                                                                                                 | TEST CONDITIONS                                                                                                                                                                            | MIN            | TYP  | MAX   | UNIT |

|------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|-------|------|

|                                    |                                                                                                 | LVDS-to-LVDS, T = 25°C, $f_{CLK}$ = 800 MHz, $R_L$ = 100 $\Omega$ AC coupled                                                                                                               |                | 30   |       | ps   |

| T <sub>SKEW</sub>                  | Maximum CLKoutX to CLKoutY <sup>(8)</sup> (9)                                                   | LVPECL-to-LVPECL, $T = 25^{\circ}\text{C}, \\ f_{\text{CLK}} = 800 \text{ MHz}, R_{\text{L}} = 100 \Omega \\ \text{emitter resistors} = \\ 240 \Omega \text{ to GND} \\ \text{AC coupled}$ |                | 30   |       | ps   |

|                                    | Maximum skew between any two LVCMOS outputs, same CLKout or different CLKout <sup>(8)</sup> (9) | R <sub>L</sub> = 50 Ω, C <sub>L</sub> = 5 pF,<br>T = 25°C, F <sub>CLK</sub> = 100 MHz. <sup>(8)</sup>                                                                                      |                | 100  |       | ps   |

| Mixed <sub>SKEW</sub>              | LVDS or LVPECL to LVCMOS                                                                        | Same device, T = 25°C,<br>250 MHz                                                                                                                                                          |                | 750  |       | ps   |

| LVDS CLOCK                         | OUTPUTS (CLKoutX), CLKoutX_TYPE =                                                               | 1                                                                                                                                                                                          |                |      |       |      |

| f <sub>CLKout</sub>                | Operating frequency <sup>(9) (13)</sup>                                                         | R <sub>L</sub> = 100 Ω                                                                                                                                                                     |                |      | 1300  | MHz  |

| V <sub>OD</sub>                    | Differential output voltageFigure 6-2                                                           |                                                                                                                                                                                            | 250            | 400  | 450   | mV   |

| V <sub>SS</sub>                    | Differential output voltagerigure 0-2                                                           |                                                                                                                                                                                            | 500            | 800  | 900   | mVpp |

| $\Delta V_{OD}$                    | Change in magnitude of V <sub>OD</sub> for complementary output states                          | T = 25°C, DC measurement<br>AC-coupled to receiver input                                                                                                                                   | -50            |      | 50    | mV   |

| V <sub>OS</sub>                    | Output offset voltage                                                                           | R = 100- $\Omega$ differential termination                                                                                                                                                 | 1.125          | 1.25 | 1.375 | V    |

| ΔV <sub>OS</sub>                   | Change in V <sub>OS</sub> for complementary output states                                       |                                                                                                                                                                                            |                |      | 35    | mV   |

| т /т                               | Output rise time                                                                                | 20% to 80%, R <sub>L</sub> = 100 Ω                                                                                                                                                         |                | 200  |       | ps   |

| T <sub>R</sub> / T <sub>F</sub>    | Output fall time                                                                                | 80% to 20%, R <sub>L</sub> = 100 Ω                                                                                                                                                         |                | 200  |       | ps   |

| I <sub>SA</sub><br>I <sub>SB</sub> | Output short circuit current - single-ended                                                     | Single-ended output shorted to GND, T = 25°C                                                                                                                                               | shorted to -24 |      | 24    | mA   |

|                                    |                                                                                                 | Complimentary outputs tied together, T = 25°C                                                                                                                                              | -12            |      | 12    | mA   |

| LVPECL CLO                         | CK OUTPUTS (CLKoutX)                                                                            |                                                                                                                                                                                            |                |      |       |      |

| f <sub>CLKout</sub>                | Operating frequency <sup>(9)</sup> (13)                                                         |                                                                                                                                                                                            |                |      | 1300  | MHz  |

|                                    | 20% to 80% output rise                                                                          | $R_L$ = 100 Ω, emitter resistors =                                                                                                                                                         |                |      |       |      |

| T <sub>R</sub> / T <sub>F</sub>    | 80% to 20% output fall time                                                                     | 240 Ω to GND<br>CLKoutX_TYPE = 4 or 5<br>(1600 or 2000 mVpp)                                                                                                                               |                | 150  |       | ps   |

$3.15~V \le V_{CC} \le 3.45~V, -40^{\circ}C \le T_{A} \le 85^{\circ}C$ , Junction Temperature  $T_{J} \le 125^{\circ}C$ . Typical values represent most likely parametric norms at  $V_{CC} = 3.3~V, T_{A} = 25^{\circ}C$ , at Recommended Operating Conditions at the time of product characterization and are not ensured. (3)

|                     | PARAMETER                          | TEST CONDITIONS                                            | MIN                    | TYP                    | MAX                                   | UNIT |

|---------------------|------------------------------------|------------------------------------------------------------|------------------------|------------------------|---------------------------------------|------|

| 700-mVpp L\         | PECL CLOCK OUTPUTS (CLKoutX),      | CLKoutX_TYPE = 2                                           |                        |                        | '                                     |      |

| V <sub>OH</sub>     | Output high voltage                |                                                            |                        | V <sub>CC</sub> – 1.03 |                                       | V    |

| V <sub>OL</sub>     | Output low voltage                 | T = 25°C, DC measurement                                   |                        | V <sub>CC</sub> – 1.41 |                                       | V    |

| V <sub>OD</sub>     | Outrot with a Figure 6.0           | Termination = 50 $\Omega$ to $V_{CC}$ – 1.4 V              | 305                    | 380                    | 440                                   | mV   |

| V <sub>SS</sub>     | Output voltageFigure 6-2           |                                                            | 610                    | 760                    | 880                                   | mVpp |

| 1200-mVpp I         | LVPECL CLOCK OUTPUTS (CLKoutX)     | ), CLKoutX_TYPE = 3                                        |                        |                        | · · · · · · · · · · · · · · · · · · · |      |

| V <sub>OH</sub>     | Output high voltage                |                                                            | V <sub>CC</sub> - 1.07 |                        |                                       | V    |

| V <sub>OL</sub>     | Output low voltage                 | T = 25°C, DC measurement                                   |                        | V <sub>CC</sub> - 1.69 |                                       | V    |

| V <sub>OD</sub>     | Outrot welter a Figure 6.2         | Termination = 50 $\Omega$ to $V_{CC}$ – 1.7 V              | 545                    | 625                    | 705                                   | mV   |

| V <sub>SS</sub>     | Output voltageFigure 6-2           |                                                            | 1090                   | 1250                   | 1410                                  | mVpp |

| 1600-mVpp I         | LVPECL CLOCK OUTPUTS (CLKoutX      | ), CLKoutX_TYPE = 4                                        |                        |                        | '                                     |      |

| V <sub>OH</sub>     | Output high voltage                |                                                            |                        | V <sub>CC</sub> – 1.10 |                                       | V    |

| V <sub>OL</sub>     | Output low voltage                 | T = 25°C, DC Measurement                                   |                        | V <sub>CC</sub> – 1.97 |                                       | V    |

| V <sub>OD</sub>     | Output voltage Figure 6.2          | Termination = 50 $\Omega$ to $V_{CC} - 2 V$                | 660                    | 870                    | 965                                   | mV   |

| V <sub>SS</sub>     | Output voltageFigure 6-2           |                                                            | 1320                   | 1740                   | 1930                                  | mVpp |

| 2000-mVpp I         | LVPECL (2VPECL) CLOCK OUTPUTS      | (CLKoutX), CLKoutX_TYPE = 5                                |                        |                        | '                                     |      |

| V <sub>OH</sub>     | Output high voltage                |                                                            |                        | V <sub>CC</sub> – 1.13 |                                       | V    |

| V <sub>OL</sub>     | Output low voltage                 | T = 25°C, DC Measurement<br>Termination = 50 $\Omega$ to   |                        | V <sub>CC</sub> - 2.20 |                                       | V    |

| V <sub>OD</sub>     | Output voltageFigure 6-2           | V <sub>CC</sub> – 2.3 V                                    | 800                    | 1070                   | 1200                                  | mV   |

| V <sub>SS</sub>     | Output voltagerigure 6-2           |                                                            | 1600                   | 2140                   | 2400                                  | mVpp |

| LVCMOS CL           | OCK OUTPUTS (CLKoutX)              |                                                            |                        |                        | '                                     |      |

| f <sub>CLKout</sub> | Operating frequency <sup>(9)</sup> | 5-pF Load                                                  |                        |                        | 250                                   | MHz  |

| V <sub>OH</sub>     | Output high voltage                | 1-mA Load                                                  | V <sub>CC</sub> - 0.1  |                        |                                       | V    |

| V <sub>OL</sub>     | Output low voltage                 | 1-mA Load                                                  |                        |                        | 0.1                                   | V    |

| I <sub>OH</sub>     | Output high current (Source)       | V <sub>CC</sub> = 3.3 V, V <sub>O</sub> = 1.65 V           |                        | 28                     |                                       | mA   |

| I <sub>OL</sub>     | Output low current (Sink)          | V <sub>CC</sub> = 3.3 V, V <sub>O</sub> = 1.65 V           |                        | 28                     |                                       | mA   |

| DUTY <sub>CLK</sub> | Output duty cycle <sup>(9)</sup>   | $V_{CC}/2$ to $V_{CC}/2$ , $F_{CLK}$ = 100 MHz, $T$ = 25°C | 45                     | 50                     | 55                                    | %    |

| T <sub>R</sub>      | Output rise time                   | 20% to 80%, $R_L$ = 50 Ω, $CL$ = 5 pF                      |                        | 400                    |                                       | ps   |

| T <sub>F</sub>      | Output fall time                   | 80% to 20%, $R_L$ = 50 $\Omega$ , $CL$ = 5 pF              |                        | 400                    |                                       | ps   |

| DIGITAL OU          | TPUTS (Ftest/LD, Readback, GPoutX) | )                                                          | 1                      |                        | I.                                    |      |

| V <sub>OH</sub>     | High-level output voltage          | I <sub>OH</sub> = -500 μA                                  | V <sub>CC</sub> - 0.4  |                        |                                       | V    |

| V <sub>OL</sub>     | Low-level output voltage           | Ι <sub>ΟL</sub> = 500 μΑ                                   |                        |                        | 0.4                                   | V    |

#### www.ti.com

3.15 V  $\leq$  V<sub>CC</sub>  $\leq$  3.45 V,  $-40^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  85°C, Junction Temperature T<sub>J</sub>  $\leq$  125°C.

Typical values represent most likely parametric norms at  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , at Recommended Operating Conditions at the time of product characterization and are not ensured. (3)

|                 | PARAMETER                           | TEST CONDITIONS                   | MIN | TYP MAX         | UNIT |

|-----------------|-------------------------------------|-----------------------------------|-----|-----------------|------|

| DIGITAL II      | NPUTS (SYNC)                        | ·                                 |     |                 |      |

| V <sub>IH</sub> | High-level input voltage            |                                   | 1.6 | V <sub>CC</sub> | V    |

| V <sub>IL</sub> | Low-level input voltage             |                                   |     | 0.4             | V    |

| DIGITAL II      | NPUTS (CLKuWire, DATAuWire, LEuWire | )                                 |     |                 |      |

| V <sub>IH</sub> | High-level input voltage            |                                   | 1.6 | V <sub>CC</sub> | V    |

| V <sub>IL</sub> | Low-level input voltage             |                                   |     | 0.4             | V    |

| I <sub>IH</sub> | High-level input current            | V <sub>IH</sub> = V <sub>CC</sub> | 5   | 25              | μA   |

| I <sub>IL</sub> | Low-level input current             | V <sub>IL</sub> = 0               | -5  | 5               | μA   |

- If emitter resistors are placed on the OSCout1/1\* pins, there will be a DC current to ground which will cause powerdown Icc to

- Load conditions for output clocks: LVDS: 100 Ω differential. See Current Consumption and Power Dissipation Calculations for Icc for specific part configuration and how to calculate Icc for a specific design.

- In order to meet the jitter performance listed in the subsequent sections of this data sheet, the minimum recommended slew rate for all input clocks is 0.5 V/ns. This is especially true for single-ended clocks. Phase noise performance will begin to degrade as the clock input slew rate is reduced. However, the device will function at slew rates down to the minimum listed. When compared to single-ended clocks, differential clocks (LVDS, LVPECL) will be less susceptible to degradation in phase noise performance at lower slew rates due to their common mode noise rejection. However, it is also recommended to use the highest possible slew rate for differential clocks to achieve optimal phase noise performance at the device outputs.

- Foscin maximum frequency guaranteed by characterization. Production tested at 200 MHz.

- A specification in modeling PLL in-band phase noise is the 1/f flicker noise, LPLL flicker(f), which is dominant close to the carrier. Flicker noise has a 10 dB/decade slope. PN10kHz is normalized to a 10 kHz offset and a 1 GHz carrier frequency. PN10kHz = L<sub>PLL flicker</sub>(10 kHz) - 20log(Fout / 1 GHz), where L<sub>PLL</sub> flicker(f) is the single side band phase noise of only the flicker noise's contribution to total noise, L(f). To measure L<sub>PLL\_flicker</sub>(f) it is important to be on the 10 dB/decade slope close to the carrier. A high compare frequency and a clean crystal are important to isolating this noise source from the total phase noise, L(f). L<sub>PLL\_flicker</sub>(f) can be masked by the reference oscillator performance if a low power or noisy source is used. The total PLL in-band phase noise performance is the sum of L<sub>PLL flicker</sub>(f) and L<sub>PLL flat</sub>(f).

- A specification modeling PLL in-band phase noise. The normalized phase noise contribution of the PLL, L<sub>PLL</sub> flat(f), is defined as: PN1HZ=L<sub>PLL</sub> flat(f) - 20log(N) - 10log(f<sub>PD</sub>). L<sub>PLL</sub> flat(f) is the single side band phase noise measured at an offset frequency, f, in a 1 Hz bandwidth and f<sub>PD</sub> is the phase detector frequency of the synthesizer. L<sub>PLL\_flat</sub>(f) contributes to the total noise, L(f).

- Maximum Allowable Temperature Drift for Continuous Lock is how far the temperature can drift in either direction from the value it was at the time that the R30 register was last programmed, and still have the part stay in lock. The action of programming the R30 register, even to the same value, activates a frequency calibration routine. This implies the part will work over the entire frequency range, but if the temperature drifts more than the maximum allowable drift for continuous lock, then it will be necessary to reload the R30 register to ensure it stays in lock. Regardless of what temperature the part was initially programmed at, the temperature can never drift outside the frequency range of -40°C to 85°C without violating specifications.

- Equal loading and identical clock output configuration on each clock output is required for specification to be valid.

- Guaranteed by characterization.

Copyright © 2023 Texas Instruments Incorporated

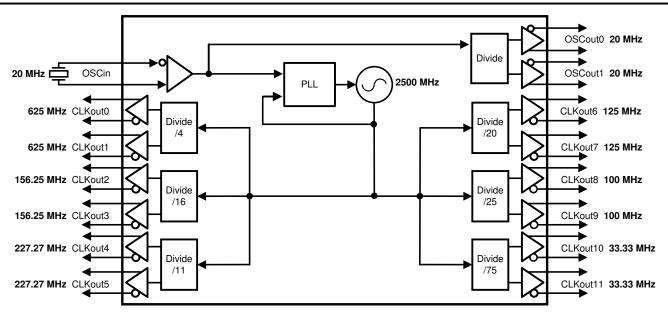

- (10) Jitter and phase noise data for 100 MHz, 156.25, and 312.5 MHz collected using an ECS crystal, part number ECS-200-20-30B-DU. Loop filter values are C1 = 220 pF, C2 = 18 nF, R2 = 820 Ω, C3 = 10 pF, R3 = 200 Ω, C4 = 10 pF, R4 = 200 Ω. Charge pump current = 3.2 mA. LVPECL emitter resistors,  $R_e$  = 240  $\Omega$ . Reference doubler disabled. VCO frequency = 2500 MHz using a phase detector frequency = 20 MHz the loop bandwidth = 62 kHz and phase margin = 76°.

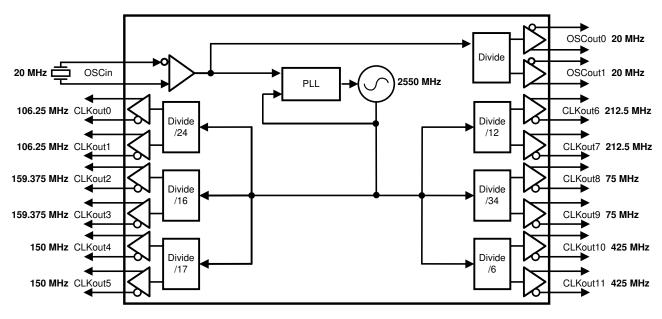

- (11) Jitter and phase noise data for 106.25 MHz collected using an ECS crystal, part number ECS-200-20-30B-DU. Loop filter values are C1 = 220 pF, C2 = 18 nF, R2 = 820  $\Omega$ , C3 = 10 pF, R3 = 200  $\Omega$ , C4 = 10 pF, R4 = 200  $\Omega$ . Charge pump current = 3.2 mA, LVPECL emitter resistors,  $R_e = 240 \Omega$ . Reference doubler disabled. VCO frequency = 2550 MHz using a phase detector frequency = 10 MHz the loop bandwidth = 32 kHz and phase margin = 69°.

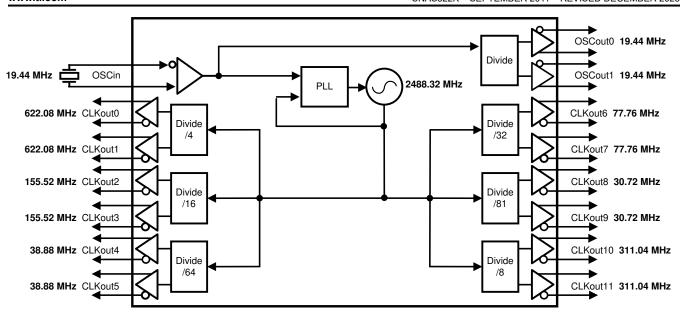

- (12) Jitter and phase noise data for 622.08 MHz collected using a Vectron crystal, part number VXB1-1137-15M360. Loop filter values are C1 = 100 pF, C2 = 120 nF, R2 = 470  $\Omega$ , C3 = 10 pF, R3 = 200  $\Omega$ , C4 = 10 pF, R4 = 200  $\Omega$ . Charge pump current = 3.2 mA. LVPECL emitter resistors,  $R_e = 240 \Omega$ . Reference doubler enabled. VCO frequency = 2488.32 MHz using a phase detector frequency = 30.72 MHz the loop bandwidth = 54 kHz and phase margin = 86°.

- (13) Refer to typical performance charts for output operation performance at higher frequencies than the minimum maximum output frequency.

- Jitter and phase noise data for 100 MHz, 156.25, and 312.5 MHz collected using a Wenzel crystal oscillator, part number 501-04623G. Loop filter values are C1 = 39 pF, C2 = 3.3 nF, R2 = 680 Ω, C3 = 10 pF, R3 = 200 Ω, C4 = 10 pF, R4 = 200 Ω. Charge pump current = 3.2 mA. LVPECL emitter resistors,  $R_e$  = 240  $\Omega$ . Reference doubler disabled. VCO frequency = 2500 MHz using a phase detector frequency = 100 MHz the loop bandwidth = 80 kHz and phase margin = 60°.

- (15) Jitter and phase noise data for 106.25 MHz collected using a Wenzel crystal oscillator, part number 501–04623G. Loop filter values are C1 = 39pF, C2 = 3.3 nF, R2 = 820Ω, C3 = 10 pF, R3 = 200 Ω, C4 = 10 pF, R4 = 200 Ω. Charge pump current = 3.2 mA. LVPECL emitter resistors,  $R_e = 240 \Omega$ . Reference doubler disabled. VCO frequency = 2550 MHz using a phase detector frequency = 10 MHz the loop bandwidth = 80 kHz and phase margin = 60°.

(16) Jitter and phase noise data for 622.08 MHz collected using a Crystec oscillator, part number CVHD-950. Loop filter values are C1 = 39 pF, C2 = 3.3 nF, R2 = 680  $\Omega$ , C3 = 10 pF, R3 = 200  $\Omega$ , C4 = 10 pF, R4 = 200  $\Omega$ . Charge pump current = 3.2 mA. LVPECL emitter resistors,  $R_e = 240$   $\Omega$ . Reference doubler enabled. VCO frequency = 2488.32 MHz using a phase detector frequency = 30.72 MHz the loop bandwidth = 80 kHz and phase margin =  $60^\circ$ .

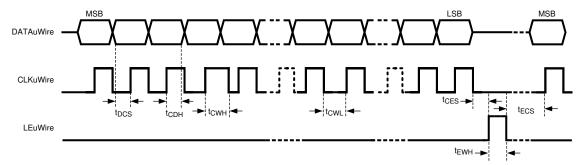

# 5.6 Timing Requirements

See *Programming* for additional information

|                  |                                |                | MIN | NOM N | ΙΑΧ | UNIT |

|------------------|--------------------------------|----------------|-----|-------|-----|------|

| T <sub>ECS</sub> | LE to clock set-up time        | See Figure 5-1 | 25  |       |     | ns   |

| T <sub>DCS</sub> | Data to clock set-up time      | See Figure 5-1 | 25  |       |     | ns   |

| T <sub>CDH</sub> | Clock to data hold time        | See Figure 5-1 | 8   |       |     | ns   |

| T <sub>CWH</sub> | Clock pulse width high         | See Figure 5-1 | 25  |       |     | ns   |

| T <sub>CWL</sub> | Clock pulse width low          | See Figure 5-1 | 25  |       |     | ns   |

| T <sub>CES</sub> | Clock to LE set-up time        | See Figure 5-1 | 25  |       |     | ns   |

| T <sub>EWH</sub> | LE pulse width                 | See Figure 5-1 | 25  |       |     | ns   |

| T <sub>CR</sub>  | Falling clock to readback time | See READBACK   | 25  |       |     | ns   |

Figure 5-1. MICROWIRE Timing Diagram

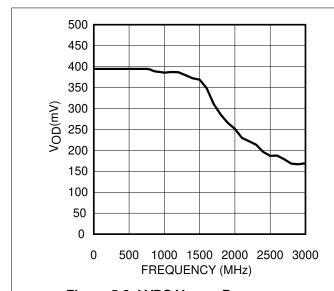

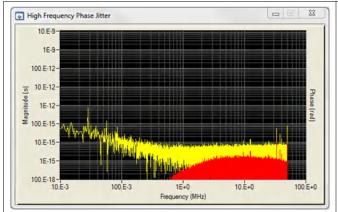

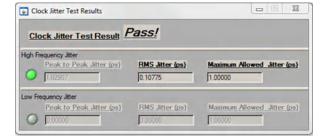

# **5.7 Typical Characteristics**

# **Clock Output AC Characteristics**

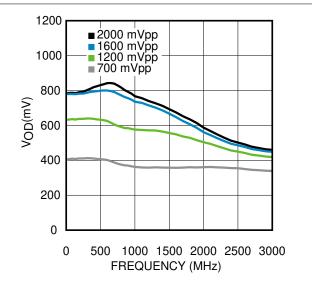

Figure 5-2. LVDS  $V_{\rm OD}$  vs Frequency

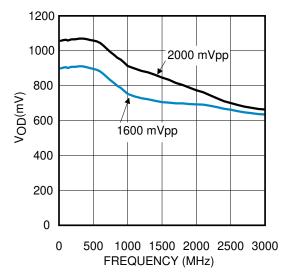

Figure 5-3. LVPECL With 240- $\Omega$  Emitter Resistors  $V_{OD}$  vs Frequency

Figure 5-4. LVPECL With 120- $\Omega$  Emitter Resistors  $V_{OD}$  vs Frequency

# **6 Parameter Measurement Information**

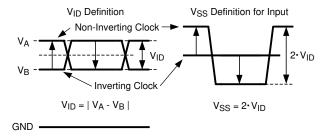

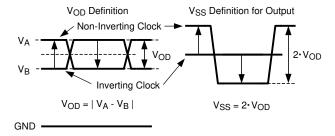

# 6.1 Differential Voltage Measurement Terminology

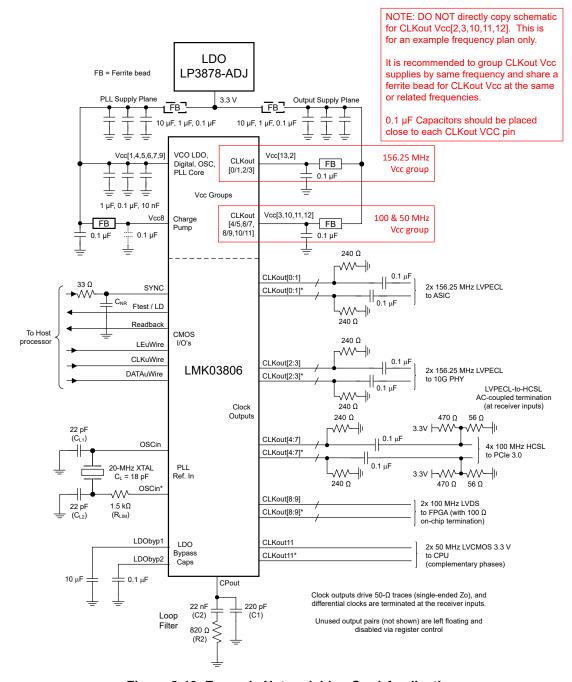

The differential voltage of a differential signal can be described by two different definitions causing confusion when reading data sheets or communicating with other engineers. This section will address the measurement and description of a differential signal so that the reader will be able to understand and discern between the two different definitions when used.