**ADS52J65** SBAS948A - DECEMBER 2018-REVISED JUNE 2020

## ADS52J65 8-Channel, 16-Bit, 125-MSPS, 70-mW/Ch ADC With JESD204B Interface

#### **Features**

- 16-Bit Resolution, Idle SNR: 80 dBFS

- 70 mW/Ch at 125 MSPS, 4-CH per Lane

- 45 mW/Ch at 62.5 MSPS, 8-CH per Lane

- Full-Scale Input: 2 VPP

- Full-Scale SNR: 78 dBFS at f<sub>in</sub> = 10 MHz

- Full-Scale SFDR: -85 dBc at f<sub>in</sub> = 10 MHz

- Analog Input -3 dB Bandwidth = 250 MHz

- Maximum Input Signal Frequency for 2 VPP Input = 130 MHz

- Fast and Consistent Overload Recovery

- **Advanced Digital Features**

- Automatic DC Offset Correction

- Digital Average

- Digital I/Q Demodulator

- Fractional Decimation Filter M = 1 to 63 With Increments of 0.25

- Data Output Rate Reduction After Decimation

- 64 mW/Ch at 80 MSPS and Decimation = 2

- On-Chip RAM With 32 Preset Profiles

- JESD204B Subclass 0, 1, and 2

- 2, 4, or 8 Channels per JESD Lane

- 10-Gbps JESD Interface

- Supports lane rate up to 12.8 Gbps for short trace length (< 5 Inch)

- 64-Pin Non-Magnetic 9 x 9-mm Package

## **Applications**

- Medical Imaging: Ultrasound, MRI

- High Frequency Ultrasound

- Non-Destructive Tests (NDT)

- Radar, Lidar, and Spectroscopy

- Digital Oscillscopes and Data Acquistion

- Flow cytometry, flow cytometer, Hematology analyzer

## 3 Description

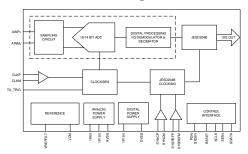

The 8-channel, 16-bit ADS52J65 analog-to-digital converter (ADC) uses CMOS process and innovative circuit techniques. It is designed to operate at low power and give very high signal-to-noise ratio (SNR) performance with a 2-Vpp full-scale input. The device gives 80-dBFS idle SNR and 78-dBFS full-scale SNR at 5 MHz. The large input bandwidth of 250 MHz makes the device suitable for a wide range of applications, such as high frequency medical ultrasound, magnetic resonance imaging, multichannel data acquisition, flow cytometry, flow cytometer, and hematology analyzer. The ADC integrates an internal reference trimmed to match across devices.

ADS52J65 has advanced digital features, including a digital I/Q demodulator with fractional decimation filter. The ADC data from each channel is encoded using an 8B to 10B format and is sent as a SerDes data stream using current-mode logic (CML) output buffers, as per the JESD204B standard. The ADC data from all eight channels can be output over a single CML buffer (1-lane SerDes) with the data rate limited to a maximum of 12.8 Gbps. Using SerDes outputs reduces the number of interface lines. This, together with the low-power design, enables eight channels to be packaged in a 9-mm × 9-mm VQFN allowing high system integration densities. ADS52J65 also supports modes where all ADC data is sent over four CML buffers (4-Lane SerDes), reducing the SerDes data rate per lane for low-cost FPGAs.

The ADS52J65 is available in a non-magnetic VQFN package that does not create any magnetic artifact. The device is specified over -40°C to +85°C.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |

|-------------|-----------|-------------------|--|--|

| ADS52J65    | VQFN (64) | 9.00 mm × 9.00 mm |  |  |

(1) See the orderable addendum at the end of the data sheet.

#### Block Diagram

# 4 Revision History

| Cr | nanges from Original (December 2018) to Revision A                                                       | Page                                   |

|----|----------------------------------------------------------------------------------------------------------|----------------------------------------|

| •  | Added Application: Flow cytometry, flow cytometer, Hematology analyze:                                   |                                        |

| •  | Added text to the first paragraph of the Description: flow cytometry, flow cytometer, hematology analyze | ······································ |

Product Folder Links: ADS52J65

## 5 Device and Documentation Support

#### 5.1 Related Documentation

For related documentation see the following:

- JESD204B Overview

- Clocking High-Speed Data Converters

- ADS52J90 10-Bit, 12-Bit, 14-Bit, Multichannel, Low-Power, High-Speed ADC with LVDS, JESD Outputs

- ADS5263 Quad Channel 16-Bit, 100-MSPS High-SNR ADC

- AFE5818 16-Channel, Ultrasound, Analog Front-End with 140-mW/Channel Power, 0.75-nV/√Hz Noise, 14-Bit, 65-MSPS or 12-Bit, 80-MSPS ADC, and Passive CW Mixer

- ISO724x High-Speed, Quad-Channel Digital Isolators

- LMK0482x Ultra Low-Noise JESD204B Compliant Clock Jitter Cleaner with Dual Loop PLLs

- SN74AUP1T04 LOW POWER, 1.8/2.5/3.3-V INPUT, 3.3-V CMOS OUTPUT, SINGLE INVERTER GATE

- THS413x High-Speed, Low-Noise, Fully-Differential I/O Amplifiers

#### 5.2 Trademarks

All trademarks are the property of their respective owners.

### 5.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 5.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 6 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Product Folder Links: ADS52J65

## PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

| ADS52J65IRGCR    | ACTIVE     | VQFN         | RGC                | 64   | 2000           | RoHS & Green | SN                            | Level-3-260C-168 HR | -40 to 85    | ADS52J65             | Samples |

| ADS52J65IRGCT    | ACTIVE     | VQFN         | RGC                | 64   | 250            | RoHS & Green | SN                            | Level-3-260C-168 HR | -40 to 85    | ADS52J65             | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Dec-2023

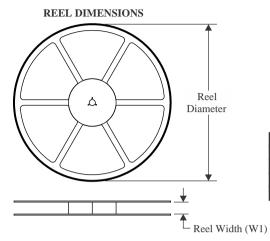

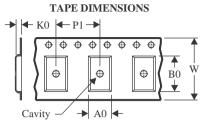

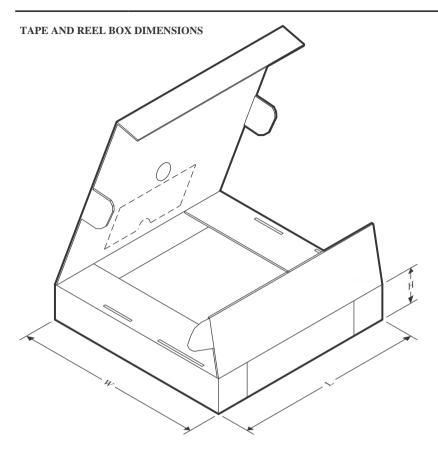

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

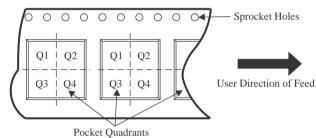

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ADS52J65IRGCR | VQFN            | RGC                | 64 | 2000 | 330.0                    | 16.4                     | 9.3        | 9.3        | 1.5        | 12.0       | 16.0      | Q2               |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Dec-2023

### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| ADS52J65IRGCR | VQFN         | RGC             | 64   | 2000 | 350.0       | 350.0      | 43.0        |  |

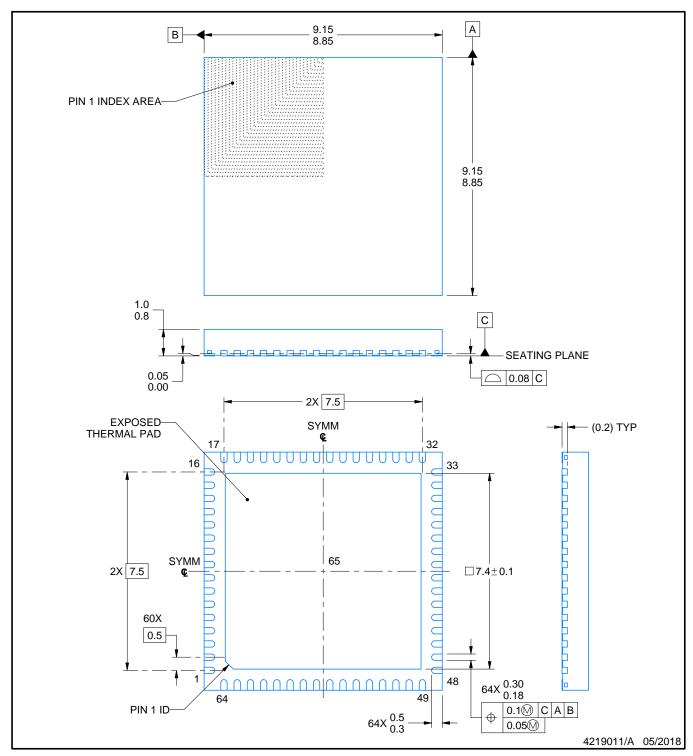

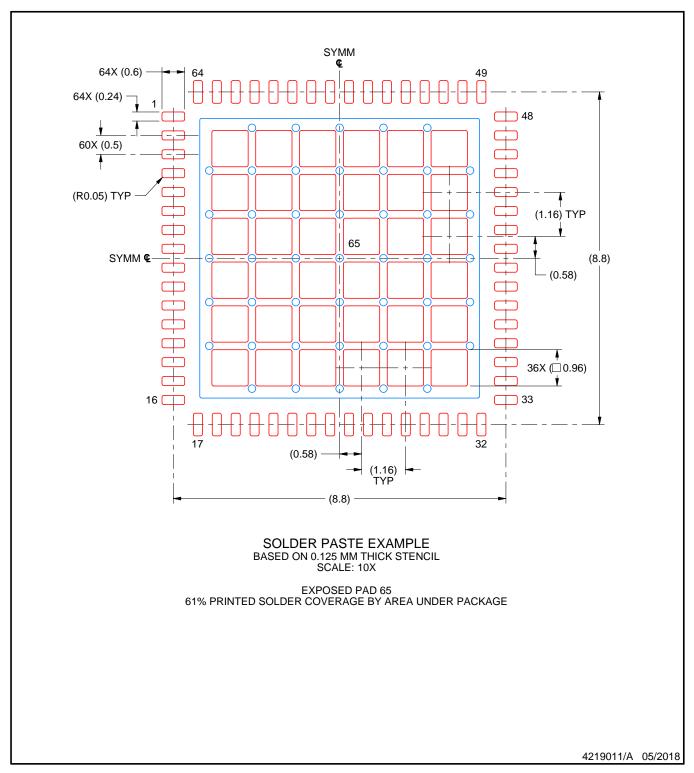

9 x 9, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4224597/A

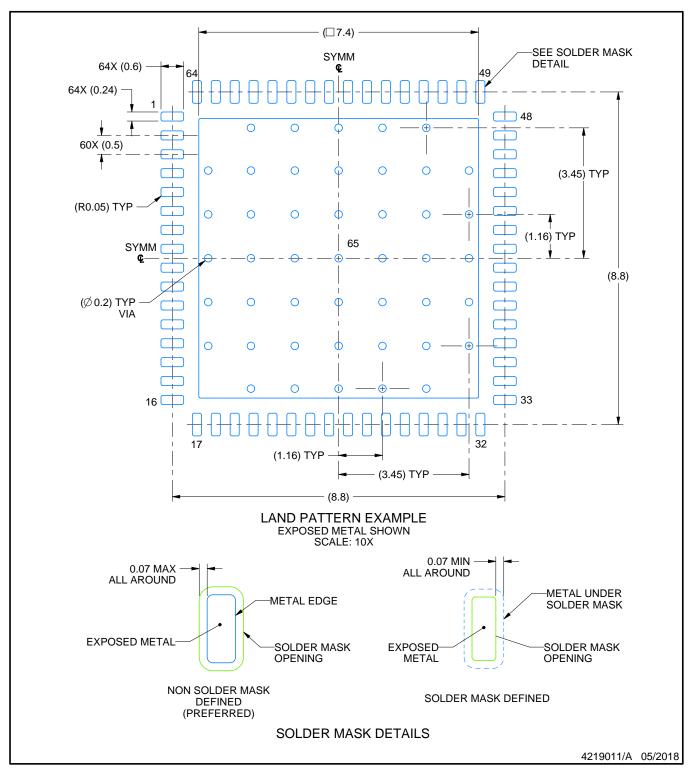

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated