# LP3996 Dual Linear Regulator with 300 mA and 150 mA Outputs and Power-On-Reset

Check for Samples: LP3996

#### **FEATURES**

- 2 LDO Outputs with Independent Enable

- 1.5% Accuracy at Room Temperature, 3% Over

- **Power-On-Reset Function with Adjustable**

- **Thermal Shutdown Protection**

- **Stable with Ceramic Capacitors**

#### **KEY SPECIFICATIONS**

- Input Voltage Range 2.0V to 6.0V

- Low Dropout Voltage 210 mV at 300 mA

- Ultra-Low I<sub>O</sub> (Enabled) 35 μA

- Virtually Zero I<sub>Q</sub> (Disabled) <10 nA

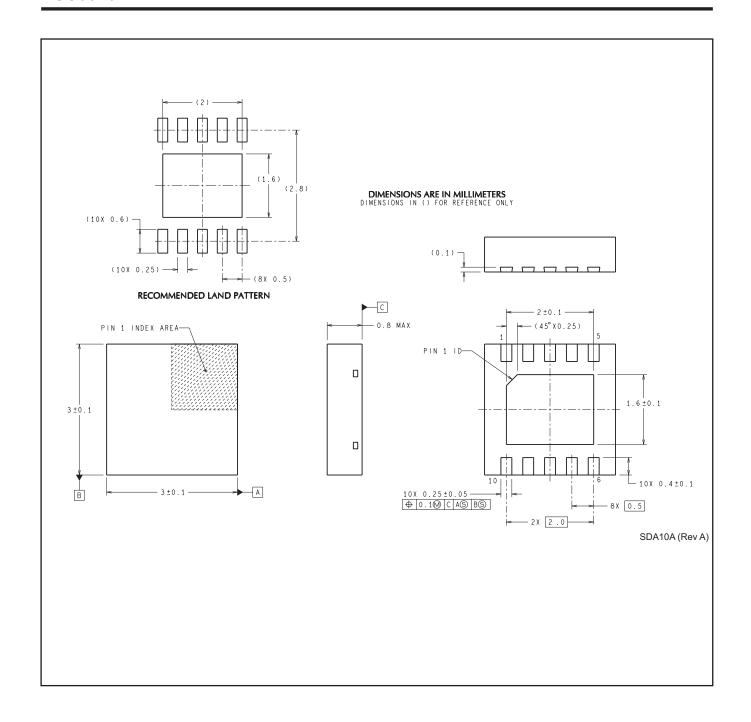

- Package Available in Lead-Free Option 10-pin 3 mm x 3 mm

#### **APPLICATIONS**

- **Cellular Handsets**

- **PDAs**

- Wireless Network Adaptors

#### DESCRIPTION

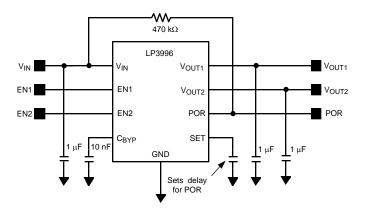

The LP3996 is a dual low dropout regulator with power-on-reset circuit. The first regulator can source 150 mA, while the second is capable of sourcing 300 mA and has a power-on-reset function included.

The LP3996 provides 1.5% accuracy requiring an ultra low guiescent current of 35 µA. Separate enable pins allow each output of the LP3996 to be shut down, drawing virtually zero current.

The LP3996 is designed to be stable with small footprint ceramic capacitors down to 1 µF. An external capacitor may be used to set the POR delay time as required.

The LP3996 is available in fixed output voltages and comes in a 10-pin, 3 mm x 3 mm package.

## **Typical Application Circuit**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

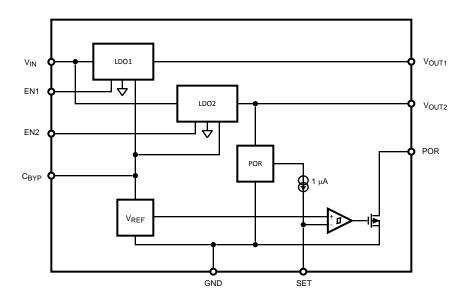

# **Functional Block Diagram**

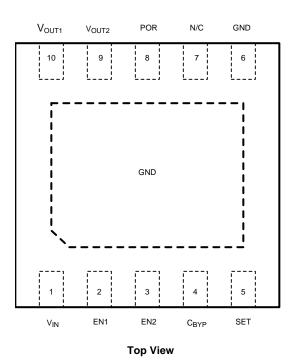

## **Pin Functions**

| Pin No | Symbol            | Name and Function                                                                                                                                                        |

|--------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | V <sub>IN</sub>   | Voltage Supply Input. Connect a 1 µF capacitor between this pin and GND.                                                                                                 |

| 2      | EN1               | Enable Input to Regulator 1. Active high input. High = On. Low = OFF.                                                                                                    |

| 3      | EN2               | Enable Input to Regulator 2. Active high input.  High = On. Low = OFF.                                                                                                   |

| 4      | C <sub>BYP</sub>  | Internal Voltage Reference Bypass. Connect a 10nF capacitor from this pin to GND to reduce output noise and improve line transient and PSRR.  This pin may be left open. |

| 5      | SET               | Set Delay Input. Connect a capacitor between this pin and GND to set the POR delay time. If left open, there will be no delay.                                           |

| 6      | GND               | Common Ground pin. Connect externally to exposed pad.                                                                                                                    |

| 7      | N/C               | No Connection. Do not connect to any other pin.                                                                                                                          |

| 8      | POR               | Power-On Reset Output. Open drain output. Active low indicates under-voltage output on Regulator 2. A pull-up resistor is required for correct operation.                |

| 9      | V <sub>OUT2</sub> | Output of Regulator 2. 300 mA maximum current output. Connect a 1 $\mu$ F capacitor between this pin and GND.                                                            |

| 10     | V <sub>OUT1</sub> | Output of Regulator 1. 150 mA maximum current output. Connect a 1 µF capacitor between this pin and GND.                                                                 |

| Pad    | GND               | Common Ground. Connect to Pin 6.                                                                                                                                         |

# **Connection Diagram**

Figure 1. WSON-10 Package See Package Number DSC0010A

Table 1. Additional Device Information (1)

| VOUT1/VOUT2 (V) | ORDER NUMBER         |

|-----------------|----------------------|

| 0.8/3.3         | LP3996SD/X-0833/NOPB |

| 1.0/1.8         | LP3996SD/X-1018/NOPB |

| 1.5/2.5         | LP3996SD/X-1525/NOPB |

| 1.8/3.3         | LP3996SD/X-1833/NOPB |

| 2.5/3.3         | LP3996SD/X-2533/NOPB |

| 2.8/2.8         | LP3996SD/X-2828/NOPB |

| 3.0/3.0         | LP3996SD/X-3030/NOPB |

| 3.0/3.3         | LP3996SD/X-3033/NOPB |

| 3.3/0.8         | LP3996SD/X-3308/NOPB |

| 3.3/3.3         | LP3996SD/X-3333/NOPB |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### ABSOLUTE MAXIMUM RATINGS(1)(2)

| Input Voltage to GND                                      |                   | -0.3V to 6.5V                                     |  |  |

|-----------------------------------------------------------|-------------------|---------------------------------------------------|--|--|

| V <sub>OUT1</sub> , V <sub>OUT2</sub> EN1 and EN2 Voltage | to GND            | -0.3V to (V <sub>IN</sub> + 0.3V) with 6.5V (max) |  |  |

| POR to GND                                                | -0.3V to 6.5V     |                                                   |  |  |

| Junction Temperature (T <sub>J-MAX</sub> )                | 150°C             |                                                   |  |  |

| Lead/Pad Temp <sup>(3)</sup>                              | 235°C             |                                                   |  |  |

| Storage Temperature                                       | age Temperature   |                                                   |  |  |

| Continuous Power Dissipation Intern                       | nally Limited (4) | ,                                                 |  |  |

| FOR Dation (5)                                            | Human Body Model  | 2.0kV                                             |  |  |

| ESD Rating <sup>(5)</sup>                                 | Machine Model     | 200V                                              |  |  |

- (1) All Voltages are with respect to the potential at the GND pin.

- (2) Absolute Maximum Ratings are limits beyond which damage can occur. Recommended Operating Conditions are conditions under which operation of the device is ensured. Recommended Operating Conditions do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

- (3) For detailed soldering specifications and information, please refer to Texas Instruments Application Note AN-1187, Leadless Leadframe Package.

- (4) Internal thermal shutdown circuitry protects the device from permanent damage.

- (5) The human body model is 100 pF discharged through a 1.5 kΩ resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin.

## RECOMMENDED OPERATING CONDITIONS(1)(2)

| Input Voltage                                           | 2.0V to 6.0V                                |

|---------------------------------------------------------|---------------------------------------------|

| EN1, EN2, POR Voltage                                   | 0 to (V <sub>IN</sub> + 0.3V) to 6.0V (max) |

| Junction Temperature                                    | -40°C to 125°C                              |

| Ambient Temperature T <sub>A</sub> Range <sup>(3)</sup> | -40°C to 85°C                               |

- (1) Absolute Maximum Ratings are limits beyond which damage can occur. Recommended Operating Conditions are conditions under which operation of the device is ensured. Recommended Operating Conditions do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

- (2) All Voltages are with respect to the potential at the GND pin.

- (3) The maximum ambient temperature (T<sub>A(max)</sub>) is dependant on the maximum operating junction temperature (T<sub>J(max-op)</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D(max)</sub>), and the junction to ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A(max)</sub> = T<sub>J(max-op)</sub> (θ<sub>JA</sub> × P<sub>D(max)</sub>).

# THERMAL PROPERTIES(1)

| Junction-To-Ambient Thermal Resistance <sup>(2)</sup> |        |

|-------------------------------------------------------|--------|

| θ <sub>JA</sub> WSON-10 Package                       | 55°C/W |

- (1) Absolute Maximum Ratings are limits beyond which damage can occur. Recommended Operating Conditions are conditions under which operation of the device is ensured. Recommended Operating Conditions do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

- (2) Junction-to-ambient thermal resistance is dependent on the application and board layout. In applications where high maximum power dissipation is possible; special care must be paid to thermal dissipation issues in board design.

# **ELECTRICAL CHARACTERISTICS**(1)(2)

Unless otherwise noted,  $V_{EN}$  = 950 mV,  $V_{IN}$  =  $V_{OUT}$  + 1.0V, or 2.0V, whichever is higher, where  $V_{OUT}$  is the higher of  $V_{OUT1}$  and  $V_{OUT2}$ .  $C_{IN}$  = 1  $\mu$ F,  $I_{OUT}$  = 1 mA,  $C_{OUT1}$  =  $C_{OUT2}$  = 1.0  $\mu$ F.

Typical values and limits appearing in normal type apply for T<sub>A</sub> = 25°C. Limits appearing in **boldface** type apply over the full junction temperature range for operation, -40 to +125°C.

| SYMBOL V <sub>IN</sub> | PARAMETER                |                                            | TYP                                                                | LIN  | LINUTO               |                    |       |

|------------------------|--------------------------|--------------------------------------------|--------------------------------------------------------------------|------|----------------------|--------------------|-------|

|                        | PARAMETER                |                                            | CONDITIONS  See <sup>(3)</sup>                                     |      |                      | MAX                | UNITS |

| V <sub>IN</sub>        | Input Voltage            | See <sup>(3)</sup>                         |                                                                    |      |                      | 6                  | V     |

| ΔV <sub>OUT</sub>      | Output Voltage Tolerance | I <sub>OUT</sub> = 1mA                     | 1.5V < V <sub>OUT</sub> ≤ 3.3V                                     |      | -2.5<br><b>-3.75</b> |                    |       |

|                        |                          |                                            | V <sub>OUT</sub> ≤ 1.5V                                            |      | -2.75<br><b>-4</b>   | +2.75<br><b>+4</b> | %     |

|                        | Line Regulation Error    | $V_{IN} = (V_{OUT(NC)})$                   | <sub>OM)</sub> + 1.0V) to 6.0V                                     | 0.03 |                      | 0.3                | %/V   |

|                        | Load Regulation Error    | I <sub>OUT</sub> = 1 mA to<br>(LDO 1)      | 150 mA                                                             | 85   |                      | 155                |       |

|                        |                          | $I_{OUT} = 1 \text{ mA to}$ (LDO 2)        | 26                                                                 |      | 85                   | μV/mA              |       |

| $V_{DO}$               | Dropout Voltage (4)      |                                            | I <sub>OUT</sub> = 1 mA to 150 mA<br>(LDO 1)                       |      |                      | 220                | >/    |

|                        |                          | I <sub>OUT</sub> = 1 mA to<br>(LDO 2)      | 210                                                                |      | 550                  | mV                 |       |

| IQ                     | Quiescent Current        |                                            | LDO 1 ON, LDO 2 ON<br>I <sub>OUT1</sub> = I <sub>OUT2</sub> = 0 mA |      |                      | 100                |       |

|                        |                          | LDO 1 ON, LD<br>I <sub>OUT1</sub> = 150 m. | 45                                                                 |      | 110                  | 4                  |       |

|                        |                          |                                            | LDO 1 OFF, LDO 2 ON<br>I <sub>OUT2</sub> = 300 mA                  |      |                      | 110                | μΑ    |

|                        |                          | LDO 1 ON, LD<br>I <sub>OUT1</sub> = 150 m  | OO 2 ON<br>A, I <sub>OUT2</sub> = 300 mA                           | 70   |                      | 170                |       |

|                        |                          | V <sub>EN1</sub> = V <sub>EN2</sub> =      | 0.4V                                                               | 0.5  |                      | 10                 | nA    |

All Voltages are with respect to the potential at the GND pin.

Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not ensured, but do represent the most likely

$V_{\text{IN(MIN)}} = V_{\text{OUT(NOM)}}$  +0.5V, or 2.0V, whichever is higher. Dropout voltage is voltage difference between input and output at which the output voltage drops to 100 mV below its nominal value. This parameter only for output voltages above 2.0V

# **ELECTRICAL CHARACTERISTICS**(1)(2) (continued)

Unless otherwise noted,  $V_{EN}$  = 950 mV,  $V_{IN}$  =  $V_{OUT}$  + 1.0V, or 2.0V, whichever is higher, where  $V_{OUT}$  is the higher of  $V_{OUT1}$  and  $V_{OUT2}$ .  $C_{IN}$  = 1  $\mu$ F,  $I_{OUT}$  = 1 mA,  $C_{OUT1}$  =  $C_{OUT2}$  = 1.0  $\mu$ F.

Typical values and limits appearing in normal type apply for  $T_A = 25^{\circ}C$ . Limits appearing in **boldface** type apply over the full junction temperature range for operation, -40 to  $+125^{\circ}C$ .

| SYMBOL                | PARAMETER                                                   | CO                                                                       | TYP                                           | LIMIT |      | UNITS |                   |

|-----------------------|-------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------|-------|------|-------|-------------------|

| STWIBOL               | FARAMETER                                                   |                                                                          | NDITIONS                                      | 115   | MIN  | MAX   | UNITS             |

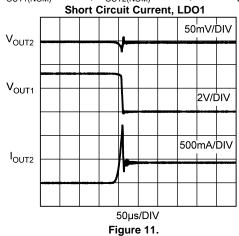

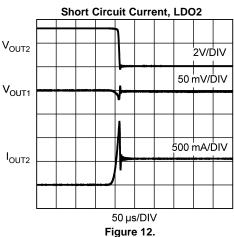

| I <sub>SC</sub>       | Short Circuit Current Limit                                 | LDO 1                                                                    |                                               | 420   |      | 750   | mA                |

|                       |                                                             | LDO 2                                                                    |                                               | 550   |      | 840   | ША                |

| l <sub>OUT</sub>      | Maximum Output Current                                      | LDO 1                                                                    |                                               |       | 150  |       | m ^               |

|                       |                                                             | LDO 2                                                                    |                                               |       | 300  |       | mA                |

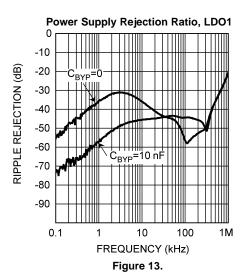

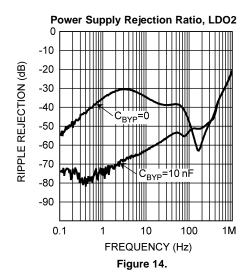

| PSRR                  | Power Supply Rejection Ratio (5)                            | f = 1kHz, I <sub>OUT</sub> =                                             | LDO1                                          | 58    |      |       |                   |

|                       |                                                             | 1mA to 150 mA $C_{BYP} = 10 \text{ nF}$                                  | LDO2                                          | 70    |      |       |                   |

|                       |                                                             | $f = 20 \text{ kHz}, I_{OUT}$                                            | LDO1                                          | 45    |      |       | dB                |

|                       |                                                             | = 1mA to 150<br>mA<br>C <sub>BYP</sub> = 10 nF                           | LDO2                                          | 60    |      |       |                   |

| e <sub>n</sub>        | Output noise Voltage <sup>(5)</sup>                         | BW = 10 Hz to                                                            | V <sub>OUT</sub> = 0.8V                       | 36    |      |       |                   |

|                       | , ,                                                         | 100kHz<br>$C_{BYP} = 10 nF$                                              | V <sub>OUT</sub> = 3.3V                       | 75    |      |       | μV <sub>RMS</sub> |

| T <sub>SHUTDOWN</sub> | Thermal Shutdown                                            | Temperature                                                              |                                               | 160   |      |       | 00                |

|                       |                                                             | Hysteresis                                                               |                                               | 20    |      |       | °C                |

| Enable Cont           | rol Characteristics                                         |                                                                          |                                               |       |      |       |                   |

| I <sub>EN</sub>       | Input Current at V <sub>EN1</sub> or V <sub>EN2</sub>       | V <sub>EN</sub> = 0.0V                                                   | 0.005                                         |       | 0.1  |       |                   |

|                       |                                                             | V <sub>EN</sub> = 6V                                                     | 2                                             |       | 5    | μA    |                   |

| V <sub>IL</sub>       | Low Input Threshold at $V_{\text{EN1}}$ or $V_{\text{EN2}}$ |                                                                          |                                               |       |      | 0.4   | ٧                 |

| V <sub>IH</sub>       | High Input Threshold at $V_{EN1}$ or $V_{EN2}$              |                                                                          |                                               |       | 0.95 |       | V                 |

| POR Output            | Characteristics                                             |                                                                          |                                               | II.   | I.   | I.    | Ш                 |

| V <sub>TH</sub>       | Low Threshold % 0f V <sub>OUT2 (NOM)</sub>                  | Flag ON                                                                  |                                               | 88    |      | 0/    |                   |

|                       | High Threshold % 0f V <sub>OUT2 (NOM)</sub>                 | Flag OFF                                                                 |                                               |       |      | 96    | %                 |

| I <sub>POR</sub>      | Leakage Current                                             | Flag OFF, V <sub>POR</sub>                                               | = 6.5V                                        | 30    |      |       | nA                |

| V <sub>OL</sub>       | Flag Output Low Voltage                                     | I <sub>SINK</sub> = 250 μA                                               |                                               | 20    |      |       | mV                |

| Timing Char           | acteristics                                                 |                                                                          |                                               |       |      |       |                   |

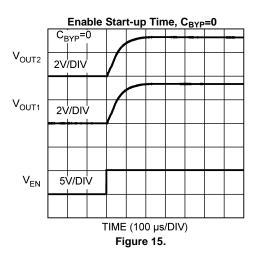

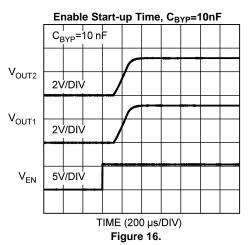

| T <sub>ON</sub>       | Turn On Time <sup>(5)</sup>                                 | To 95% Level<br>C <sub>BYP</sub> = 10 nF                                 |                                               | 300   |      |       | μs                |

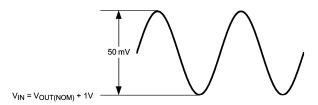

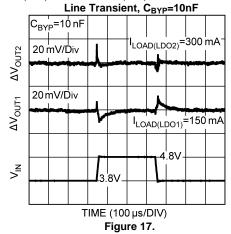

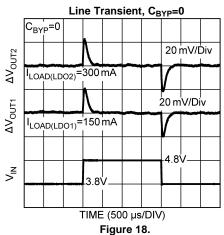

| Transient<br>Response | Line Transient Response  δV <sub>OUT</sub>   <sup>(5)</sup> | $T_{rise} = T_{fall} = 10 \mu$<br>$\delta V_{IN} = 1 V C_{BYP} = 10 \mu$ | 20                                            |       |      |       |                   |

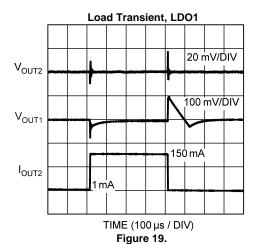

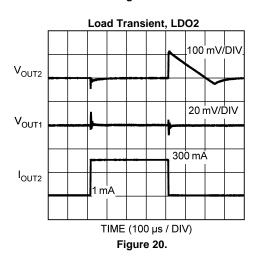

| ·                     | Load Transient Response  δV <sub>OUT</sub>   <sup>(5)</sup> | T <sub>rise</sub> = T <sub>fall</sub> = 1<br>µs                          | LDO 1<br>I <sub>OUT</sub> = 1 mA to 150<br>mA | 175   |      |       | mV<br>(pk - pk)   |

|                       |                                                             |                                                                          | LDO 2<br>I <sub>OUT</sub> = 1 mA to 300<br>mA | 150   |      |       |                   |

| SET Input Cl          | haracteristics                                              |                                                                          |                                               |       |      |       |                   |

| I <sub>SET</sub>      | SET Pin Current Source                                      | V <sub>SET</sub> = 0V                                                    |                                               | 1.3   |      |       | μΑ                |

| V <sub>TH(SET)</sub>  | SET Pin Threshold Voltage                                   | POR = High                                                               |                                               | 1.25  |      |       | V                 |

<sup>(5)</sup> This electrical specification is specified by design.

Submit Documentation Feedback

Copyright © 2006–2013, Texas Instruments Incorporated

# **OUTPUT CAPACITOR, RECOMMENDED SPECIFICATIONS**

| SYMBOL           | PARAMETER          | CONDITIONS                 | NOM | LIN | UNITS |       |

|------------------|--------------------|----------------------------|-----|-----|-------|-------|

| STIVIBOL         | FARAMETER          | CONDITIONS                 | NOW | MIN | MAX   | UNITS |

| C <sub>OUT</sub> | Output Capacitance | Capacitance <sup>(1)</sup> | 1.0 | 0.7 |       | μF    |

|                  |                    | ESR                        |     | 5   | 500   | mΩ    |

The Capacitor tolerance should be 30% or better over temperature. The full operating conditions for the application should be considered when selecting a suitable capacitor to ensure that the minimum value of capacitance is always met. Recommended capacitor is X7R. However, depending on the application, X5R, Y5V and Z5U can also be used. (See Capacitor sections in **APPLICATION HINTS.)**

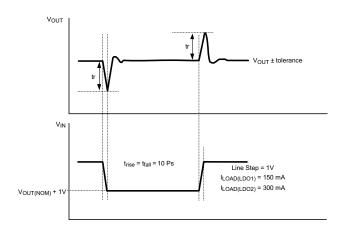

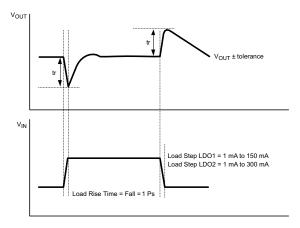

#### **Transient Test Conditions**

Figure 2. PSRR Input Signal

Figure 3. Line Transient Input Test Signal

Figure 4. Load Transient Input Signal

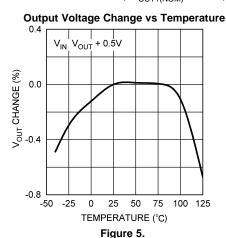

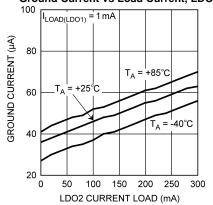

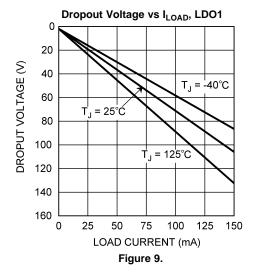

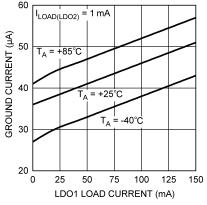

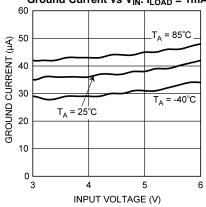

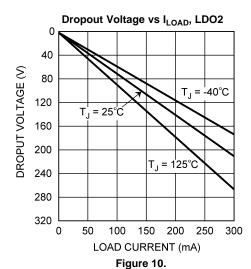

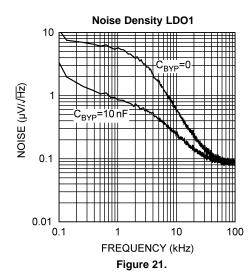

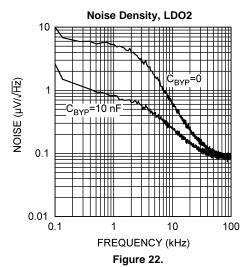

#### TYPICAL PERFORMANCE CHARACTERISTICS

Unless otherwise specified,  $C_{IN}$  = 1.0  $\mu$ F Ceramic,  $C_{OUT1}$  =  $C_{OUT2}$  = 1.0  $\mu$ F Ceramic,  $C_{BYP}$  = 10 nF,  $V_{IN}$  =  $V_{OUT2(NOM)}$  + 1.0V,  $T_{A}$  = 25°C,  $V_{OUT1(NOM)}$  = 3.3V,  $V_{OUT2(NOM)}$  = 3.3V, Enable pins are tied to  $V_{IN}$ .

Figure 7.

## **Ground Current vs Load Current, LDO1**

Figure 6.

# Ground Current vs $V_{IN}$ . $I_{LOAD} = 1mA$

Figure 8.

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

Unless otherwise specified,  $C_{IN}$  = 1.0  $\mu$ F Ceramic,  $C_{OUT1}$  =  $C_{OUT2}$  = 1.0  $\mu$ F Ceramic,  $C_{BYP}$  = 10 nF,  $V_{IN}$  =  $V_{OUT2(NOM)}$  + 1.0V,  $T_{A}$  = 25°C,  $V_{OUT1(NOM)}$  = 3.3V,  $V_{OUT2(NOM)}$  = 3.3V, Enable pins are tied to  $V_{IN}$ .

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Unless otherwise specified,  $C_{IN}$  = 1.0  $\mu$ F Ceramic,  $C_{OUT1}$  =  $C_{OUT2}$  = 1.0  $\mu$ F Ceramic,  $C_{BYP}$  = 10 nF,  $V_{IN}$  =  $V_{OUT2(NOM)}$  + 1.0V,  $T_{A}$  = 25°C,  $V_{OUT1(NOM)}$  = 3.3V,  $V_{OUT2(NOM)}$  = 3.3V, Enable pins are tied to  $V_{IN}$ .

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

Unless otherwise specified,  $C_{IN}$  = 1.0  $\mu$ F Ceramic,  $C_{OUT1}$  =  $C_{OUT2}$  = 1.0  $\mu$ F Ceramic,  $C_{BYP}$  = 10 nF,  $V_{IN}$  =  $V_{OUT2(NOM)}$  + 1.0V,  $T_{A}$  = 25°C,  $V_{OUT1(NOM)}$  = 3.3V,  $V_{OUT2(NOM)}$  = 3.3V, Enable pins are tied to  $V_{IN}$ .

Copyright © 2006–2013, Texas Instruments Incorporated

#### **APPLICATION HINTS**

### **Operation Description**

The LP3996 is a low quiescent current, power management IC, designed specifically for portable applications requiring minimum board space and smallest components. The LP3996 contains two independently selectable LDOs. The first is capable of sourcing 150 mA at outputs between 0.8V and 3.3V. The second can source 300 mA at an output voltage of 0.8V to 3.3V. In addition, LDO2 contains power good flag circuit, which monitors the output voltage and indicates when it is within 8% of its nominal value. The flag will also act as a power-on-reset signal and, by adding an external capacitor; a delay may be programmed for the POR output.

#### **Input Capacitor**

An input capacitor is required for stability. It is recommended that a 1.0 µF capacitor be connected between the LP3996 input pin and ground (this capacitance value may be increased without limit).

This capacitor must be located a distance of not more than 1 cm from the input pin and returned to a clean analogue ground. Any good quality ceramic, tantalum, or film capacitor may be used at the input.

**Important:** Tantalum capacitors can suffer catastrophic failures due to surge current when connected to a low-impedance source of power (like a battery or a very large capacitor). If a tantalum capacitor is used at the input, it must be ensured by the manufacturer to have a surge current rating sufficient for the application.

There are no requirements for the ESR (Equivalent Series Resistance) on the input capacitor, but tolerance and temperature coefficient must be considered when selecting the capacitor to ensure the capacitance will remain approximately 1.0 µF over the entire operating temperature range.

### **Output Capacitor**

The LP3996 is designed specifically to work with very small ceramic output capacitors. A 1.0  $\mu$ F ceramic capacitor (temperature types Z5U, Y5V or X7R) with ESR between 5 m $\Omega$  to 500 m $\Omega$ , is suitable in the LP3996 application circuit.

For this device the output capacitor should be connected between the V<sub>OUT</sub> pin and ground.

It is also possible to use tantalum or film capacitors at the device output,  $C_{OUT}$  (or  $V_{OUT}$ ), but these are not as attractive for reasons of size and cost (see Capacitor Characteristics).

The output capacitor must meet the requirement for the minimum value of capacitance and also have an ESR value that is within the range 5 m $\Omega$  to 500 m $\Omega$  for stability.

#### **No-Load Stability**

The LP3996 will remain stable and in regulation with no external load. This is an important consideration in some circuits, for example CMOS RAM keep-alive applications.

#### **Capacitor Characteristics**

The LP3996 is designed to work with ceramic capacitors on the output to take advantage of the benefits they offer. For capacitance values in the range of 0.47  $\mu$ F to 4.7  $\mu$ F, ceramic capacitors are the smallest, least expensive and have the lowest ESR values, thus making them best for eliminating high frequency noise. The ESR of a typical 1.0  $\mu$ F ceramic capacitor is in the range of 20 m $\Omega$  to 40 m $\Omega$ , which easily meets the ESR requirement for stability for the LP3996.

For both input and output capacitors, careful interpretation of the capacitor specification is required to ensure correct device operation. The capacitor value can change greatly, depending on the operating conditions and capacitor type.

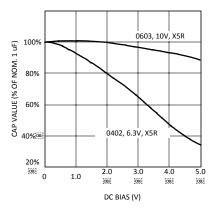

In particular, the output capacitor selection should take account of all the capacitor parameters, to ensure that the specification is met within the application. The capacitance can vary with DC bias conditions as well as temperature and frequency of operation. Capacitor values will also show some decrease over time due to aging. The capacitor parameters are also dependant on the particular case size, with smaller sizes giving poorer performance figures in general. As an example, Figure 26 shows a typical graph comparing different capacitor case sizes in a Capacitance vs. DC Bias plot. As shown in the graph, increasing the DC Bias condition can result in the capacitance value falling below the minimum value given in the recommended capacitor specifications table (0.7  $\mu$ F in this case). Note that the graph shows the capacitance out of spec for the 0402 case size capacitor at higher bias voltages. It is therefore recommended that the capacitor manufacturers' specifications for the nominal value capacitor are consulted for all conditions, as some capacitor sizes (that is, 0402) may not be suitable in the actual application.

Figure 26. Graph Showing a Typical Variation in Capacitance vs DC Bias

The ceramic capacitor's capacitance can vary with temperature. The capacitor type X7R, which operates over a temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C, will only vary the capacitance to within  $\pm 15^{\circ}$ C. The capacitor type X5R has a similar tolerance over a reduced temperature range of  $-55^{\circ}$ C to  $+85^{\circ}$ C. Many large value ceramic capacitors, larger than  $1\mu$ F are manufactured with Z5U or Y5V temperature characteristics. Their capacitance can drop by more than 50% as the temperature varies from 25°C to 85°C. Therefore X7R is recommended over Z5U and Y5V in applications where the ambient temperature will change significantly above or below 25°C.

Tantalum capacitors are less desirable than ceramic for use as output capacitors because they are more expensive when comparing equivalent capacitance and voltage ratings in the 0.47 µF to 4.7 µF range.

Another important consideration is that tantalum capacitors have higher ESR values than equivalent size ceramics. This means that while it may be possible to find a tantalum capacitor with an ESR value within the stable range, it would have to be larger in capacitance (which means bigger and more costly) than a ceramic capacitor with the same ESR value. It should also be noted that the ESR of a typical tantalum will increase about 2:1 as the temperature goes from 25°C down to -40°C, so some guard band must be allowed.

#### **Enable Control**

The LP3996 features active high enable pins for each regulator, EN1 and EN2, which turns the corresponding LDO off when pulled low. The device outputs are enabled when the enable lines are set to high. When not enabled the regulator output is off and the device typically consumes 2nA.

If the application does not require the Enable switching feature, one or both enable pins should be tied to  $V_{IN}$  to keep the regulator output permanently on.

To ensure proper operation, the signal source used to drive the enable inputs must be able to swing above and below the specified turn-on / off voltage thresholds listed in the Electrical Characteristics section under  $V_{IL}$  and  $V_{IH}$ .

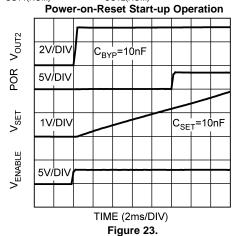

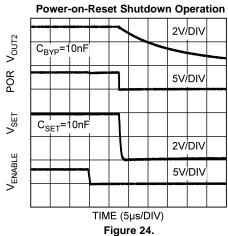

#### **Power-On-Reset**

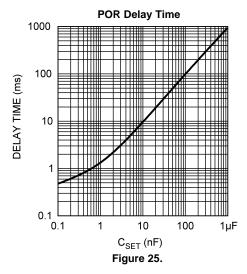

The POR pin is an open-drain output which will be set to Low whenever the output of LDO2 falls out of regulation to approximately 90% of its nominal value. An external pull-up resistor, connected to  $V_{\text{OUT}}$  or  $V_{\text{IN}}$ , is required on this pin. During start-up, or whenever a fault condition is removed, the POR flag will return to the High state after the output reaches approximately 96% of its nominal value. By connecting a capacitor from the SET pin to GND, a delay to the rising condition of the POR flag may be introduced. The delayed signal may then be used as a Power-on -Reset for a microprocessor within the user's application.

The duration of the delay is determined by the time to charge the delay capacitor to a threshold voltage of 1.25V at 1.2  $\mu$ A from the SET pin as in the formula below.

$$t_{DELAY} = \frac{V_{TH(SET)} \times C_{SET}}{I_{SET}}$$

(1)

A 0.1 µF capacitor will introduce a delay of approximately 100 ms.

## **Bypass Capacitor**

The internal voltage reference circuit of the LP3996 is connected to the  $C_{BYP}$  pin via a high value internal resistor. An external capacitor, connected to this pin, forms a low-pass filter which reduces the noise level on both outputs of the device. There is also some improvement in PSSR and line transient performance. Internal circuitry ensures rapid charging of the  $C_{BYP}$  capacitor during start-up. A 10 nF, high quality ceramic capacitor with either NPO or COG dielectric is recommended due to their low leakage characteristics and low noise performance.

#### Safe Area of Operation

Due consideration should be given to operating conditions to avoid excessive thermal dissipation of the LP3996 or triggering its thermal shutdown circuit. When both outputs are enabled, the total power dissipation will be  $P_{D(LDO2)} + P_{D(LDO2)}$  Where  $P_D = (V_{IN} - V_{OUT}) \times I_{OUT}$  for each LDO.

In general, device options which have a large difference in output voltage will dissipate more power when both outputs are enabled, due to the input voltage required for the higher output voltage LDO. In such cases, especially at elevated ambient temperature, it may not be possible to operate both outputs at maximum current at the same time.

# **REVISION HISTORY**

| Changes from Revision B (March 2013) to Revision C  | Page |

|-----------------------------------------------------|------|

| Changed layout of National Data Sheet to TI format; | 14   |

| Changes from Revision C (March 2013) to Revision D  | Page |

| Added Additional Device Table back to datasheet     |      |

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|--------------|

|                       | . ,    | .,            |                 |                       | . ,  | (4)                           | (5)                        |              |              |

| LP3996SD-0833/NOPB    | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | L167B        |

| LP3996SD-0833/NOPB.A  | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | L167B        |

| LP3996SD-1525/NOPB    | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | L168B        |

| LP3996SD-1525/NOPB.A  | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | L168B        |

| LP3996SD-1833/NOPB    | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -            | L228B        |

| LP3996SD-1833/NOPB.A  | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | L228B        |

| LP3996SD-2533/NOPB    | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -            | L229B        |

| LP3996SD-2533/NOPB.A  | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | L229B        |

| LP3996SD-3030/NOPB    | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | L172B        |

| LP3996SD-3030/NOPB.A  | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | L172B        |

| LP3996SD-3033/NOPB    | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | L170B        |

| LP3996SD-3033/NOPB.A  | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | L170B        |

| LP3996SD-3333/NOPB    | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | L173B        |

| LP3996SD-3333/NOPB.A  | Active | Production    | WSON (DSC)   10 | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | L173B        |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 11-Nov-2025

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF LP3996:

Automotive: LP3996-Q1

NOTE: Qualified Version Definitions:

Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

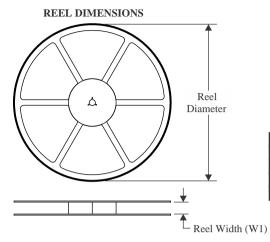

## TAPE AND REEL INFORMATION

NSTRUMENTS

# TAPE DIMENSIONS + K0 - P1 - B0 W Cavity - A0 -

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

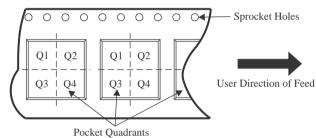

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device             | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LP3996SD-0833/NOPB | WSON            | DSC                | 10 | 1000 | 177.8                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LP3996SD-1525/NOPB | WSON            | DSC                | 10 | 1000 | 177.8                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LP3996SD-1833/NOPB | WSON            | DSC                | 10 | 1000 | 177.8                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LP3996SD-2533/NOPB | WSON            | DSC                | 10 | 1000 | 177.8                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LP3996SD-3030/NOPB | WSON            | DSC                | 10 | 1000 | 177.8                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LP3996SD-3033/NOPB | WSON            | DSC                | 10 | 1000 | 177.8                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

| LP3996SD-3333/NOPB | WSON            | DSC                | 10 | 1000 | 177.8                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q1               |

www.ti.com 1-Aug-2025

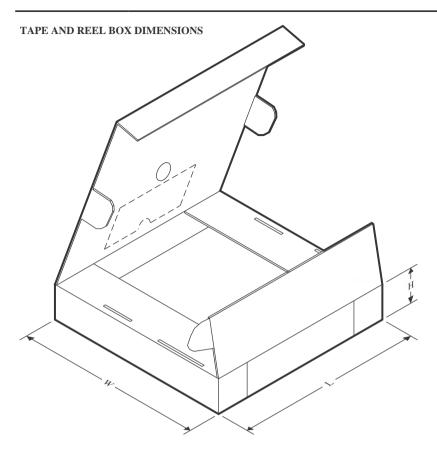

## \*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LP3996SD-0833/NOPB | WSON         | DSC             | 10   | 1000 | 208.0       | 191.0      | 35.0        |

| LP3996SD-1525/NOPB | WSON         | DSC             | 10   | 1000 | 208.0       | 191.0      | 35.0        |

| LP3996SD-1833/NOPB | WSON         | DSC             | 10   | 1000 | 208.0       | 191.0      | 35.0        |

| LP3996SD-2533/NOPB | WSON         | DSC             | 10   | 1000 | 208.0       | 191.0      | 35.0        |

| LP3996SD-3030/NOPB | WSON         | DSC             | 10   | 1000 | 208.0       | 191.0      | 35.0        |

| LP3996SD-3033/NOPB | WSON         | DSC             | 10   | 1000 | 208.0       | 191.0      | 35.0        |

| LP3996SD-3333/NOPB | WSON         | DSC             | 10   | 1000 | 208.0       | 191.0      | 35.0        |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025