LMX2592 SNAS646G - DECEMBER 2015 - REVISED AUGUST 2022

# LMX2592 High Performance, Wideband PLLatinum™ RF Synthesizer With Integrated **VCO**

#### 1 Features

- Output Frequency Range from 20 to 9800 MHz

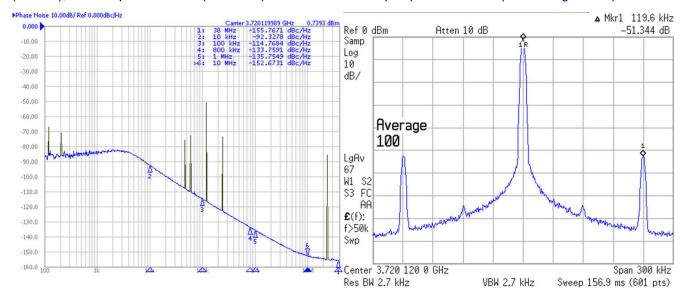

- Industry Leading Phase Noise Performance

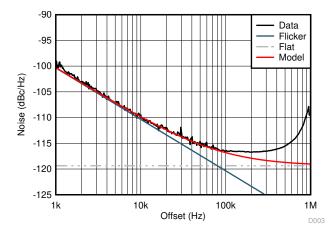

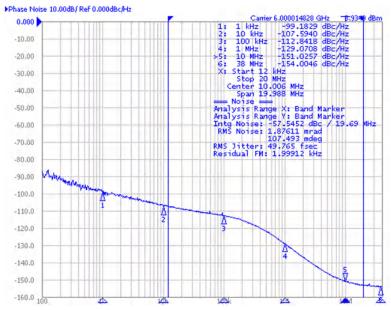

- VCO Phase Noise: –134.5 dBc/Hz at 1-MHz Offset for 6-GHz Output

- Normalized PLL Noise Floor: –231 dBc/Hz

- Normalized PLL Flicker Noise: –126 dBc/Hz

- 49-fs RMS Jitter (12 kHz to 20 MHz) for 6 GHz Output

- Input Clock Frequency Up to 1400 MHz

- Phase Detector Frequency Up to 200 MHz, and Up to 400 MHz in Integer-N Mode

- Supports Fractional-N and Integer-N Modes

- **Dual Differential Outputs**

- Innovative Solution to Reduce Spurs

- Programmable Phase Adjustment

- Programmable Charge Pump Current

- Programmable Output Power Level

- SPI or uWire (4-Wire Serial Interface)

- Single Power Supply Operation: 3.3 V

# 2 Applications

- Test and Measurement Equipment

- Defense and RADAR

- Microwave Backhaul

- High-Performance Clock Source for High-Speed **Data Converters**

- Satellite Communications

# 3 Description

The LMX2592 device is a low-noise, wideband RF PLL with integrated VCO that supports a frequency range from 20 MHz to 9.8 GHz. The device supports both fractional-N and integer-N modes, with a 32-bit fractional divider allowing fine frequency selection. Integrated noise of 49 fs for 6-GHz output makes it an ideal low-noise source. Combining best-in-class PLL and integrated VCO noise with integrated LDOs, this device removes the need for multiple discrete devices in high performance systems.

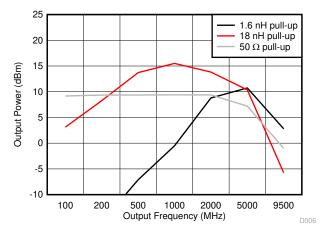

The device accepts input frequencies up to 1.4 GHz, which combined with frequency dividers and programmable low noise multiplier allows flexible frequency planning. The additional programmable low-noise multiplier lets users mitigate the impact of integer boundary spurs. In Fractional-N mode, the device can adjust the output phase by a 32-bit resolution. For applications that need fast frequency changes, the device supports a fast calibration option which takes less than 25 µs.

This performance is achieved by using single 3.3-V supply. It supports 2 flexible differential outputs that can be configured as single-ended outputs as well. Users can choose to program one output from the VCO (or doubler) and the second from the channel divider. When not being used, each output can be muted separately.

#### Package Information (1)

| PART NUMBER                | DESCRIPTION | BODY SIZE (NOM)   |

|----------------------------|-------------|-------------------|

| LMX2592RHAT<br>LMX2592RHAR | VQFN (40)   | 6.00 mm × 6.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

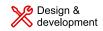

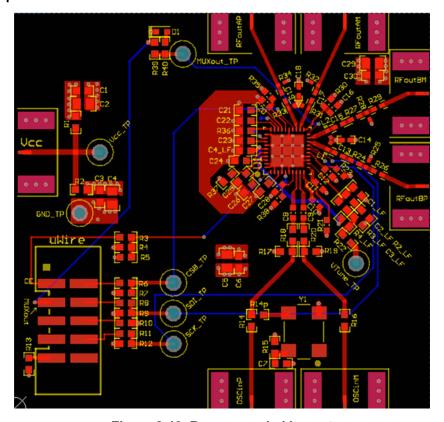

Simplified Schematic

# **Table of Contents**

| 1 Features1                           | 7.5 Programming                                     | 18 |

|---------------------------------------|-----------------------------------------------------|----|

| 2 Applications 1                      | 7.6 Register Maps                                   | 19 |

| 3 Description1                        | 8 Application and Implementation                    | 30 |

| 4 Revision History2                   | 8.1 Application Information                         |    |

| 5 Pin Configuration and Functions4    | 8.2 Typical Application                             | 37 |

| 6 Specifications6                     | 8.3 Power Supply Recommendations                    |    |

| 6.1 Absolute Maximum Ratings6         | 8.4 Layout                                          | 39 |

| 6.2 ESD Ratings6                      | 9 Device and Documentation Support                  |    |

| 6.3 Recommended Operating Conditions6 | 9.1 Device Support                                  | 40 |

| 6.4 Thermal Information6              | 9.2 Documentation Support                           | 40 |

| 6.5 Electrical Characteristics7       | 9.3 Receiving Notification of Documentation Updates | 40 |

| 6.6 Timing Requirements8              | 9.4 Support Resources                               | 40 |

| 6.7 Typical Characteristics10         | 9.5 Trademarks                                      | 40 |

| 7 Detailed Description13              | 9.6 Electrostatic Discharge Caution                 | 40 |

| 7.1 Overview13                        | 9.7 Glossary                                        | 40 |

| 7.2 Functional Block Diagram13        | 10 Mechanical, Packaging, and Orderable             |    |

| 7.3 Functional Description13          | Information                                         | 40 |

| 7.4 Device Functional Modes17         |                                                     |    |

|                                       |                                                     |    |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | nanges from Revision F (October 2017) to Revision G (August 2022)                              | Page           |

|---|------------------------------------------------------------------------------------------------|----------------|

| • | Changed package description from WQFN to VQFN                                                  | 1              |

| • | Added a new requirement to Vtune pin description                                               |                |

| • | Added HD2 and HD3 information to the Electrical Characteristics table                          | <mark>7</mark> |

| • | Removed sentence: The CLK signal should not be high when LE transitions to low                 |                |

| • | Changed the Channel Divider requirement                                                        |                |

| • | Added a new register field, VTUNE_ADJ, in register R30                                         |                |

| • | Changed the position of register field, PFD_CTL, in register R13                               |                |

| • | Added read only register R68, R69 and R70                                                      |                |

| • | Added additional requirement for register CP_ICOARSE in Table 7-16                             |                |

| • | Added additional information for register MUXOUT_HDRV in Table 7-44                            |                |

| • | Added a new register field, VTUNE_ADJ, in Table 7-25                                           |                |

| • | Changed the register R0 FCAL_LPFD_ADJ configurable values                                      |                |

| • | Changed the register R13 PFD_CTL position                                                      |                |

| • | Added the R68, R69 and R70 register field descriptions                                         |                |

| • | Added External Loop Filter section                                                             |                |

| • | Moved the Power Supply Recommendations and Layout sections to the Application and Implement    |                |

|   | section                                                                                        |                |

| C | hanges from Revision E (July 2017) to Revision F (October 2017)                                | Page           |

| • | Switched the RFoutBP and RFoutBM pins in the pinout diagram                                    | 4              |

| • | Changed register 7 and the register descriptions of 4, 20 and 46                               |                |

| C | hanges from Revision D (February 2017) to Revision E (July 2017)                               | Page           |

| • | Changed Channel Divider Setting as a Function of the Desired Output Frequency table            | 16             |

| C | hanges from Revision C (October 2016) to Revision D (January 2017)                             | Page           |

| • | Removed < 25-µs Fast Calibration Mode bullet from Features                                     |                |

| • | Changed the high level input voltage minimum value of from: 1.8 to: 1.4                        |                |

| • | Changed text from: the rising edge of the LE signal to: the rising edge of the last CLK signal |                |

|   |                                                                                                |                |

#### www.ti.com

| Changed text from: the shift registers to an actual counter to: the shift registers to a regis |                  |

|------------------------------------------------------------------------------------------------|------------------|

| Added content to the Voltage Controlled Oscillator section                                     |                  |

| Changed Channel Divider Setting as a Function of the Desired Output Frequency table            |                  |

| Changed register 0, 22, and 64 descriptions                                                    | 19               |

| hanges from Revision B (July 2016) to Revision C (September 2016)                              | Page             |

| Updated data sheet text to the latest documentation and translations standards                 | 1                |

| Changed pin 30 name from: Rext to: NC                                                          | 4                |

| Changed CDM value from: ±1250 V to: ±750 V                                                     | 6                |

| Changed parameter name from: Maximum reference input frequency to: reference input             |                  |

| Removed the charge pump current TYP range '0 to 12' and split range into MIN (0) and           | MAX (12) columns |

| 7                                                                                              | _                |

| Moved all typical values in the <i>Timing Requirements</i> table to minimum column             |                  |

| Changed output frequency units from: MHz to: Hz in graphic                                     |                  |

| Changed high input value from: 700 to: 200                                                     |                  |

| Changed high input value from: 1400 to: 400                                                    | 14               |

| Changed minimum output frequency step from: Fpd / PLL_DEN to: Fpd × PLL_N_PRE / divider value] |                  |

| Changed text from: output dividers to: channel dividers                                        |                  |

| Changed output frequency from: 3600 to: 3550                                                   |                  |

| Changed VCO frequency from: 7200 to: 7100                                                      |                  |

| Changed Phase shift (degrees) from: 360 × MASH_SEED / PLL_N_DEN / [Channel divi                |                  |

| MASH_SEED x PLL_N_PRE / PLL_N_DEN / [Channel divider value]"                                   |                  |

| Changed register 7, 8, 19, 23, 32, 33, 34, 46, and 64 descriptions                             |                  |

| Added registers 20, 22, 25, 59, and 61                                                         |                  |

| Changed register descriptions from: Program to default to: Program to Register Map def         |                  |

| Updated content in the <i>Decreasing Lock Time</i> section                                     |                  |

| Changed typical application image                                                              |                  |

| Changed charge pump value from: 4.8 to: 20                                                     |                  |

| Changed R2 value from: 0.068 to: 68                                                            |                  |

| Changes 132 Value from 0.000 to 00                                                             |                  |

| hanges from Revision A (December 2015) to Revision B (July 2016)                               |                  |

| Added VCO Calibration Time to Electrical Characteristics                                       |                  |

| Added registers 2, 4, and 62 to Register Table                                                 |                  |

| Changed register 38 in Register Table                                                          | 19               |

| Added R2 Register Field Descriptions                                                           |                  |

| Added R4 Register Field Descriptions                                                           |                  |

| Added R62 Register Field Descriptions                                                          | 20               |

| hanges from Revision * (December 2015) to Revision A (December 2015)                           | Page             |

| Changed device status from product preview to production data, and released full data s        | sheet1           |

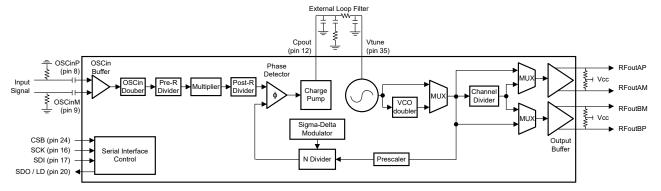

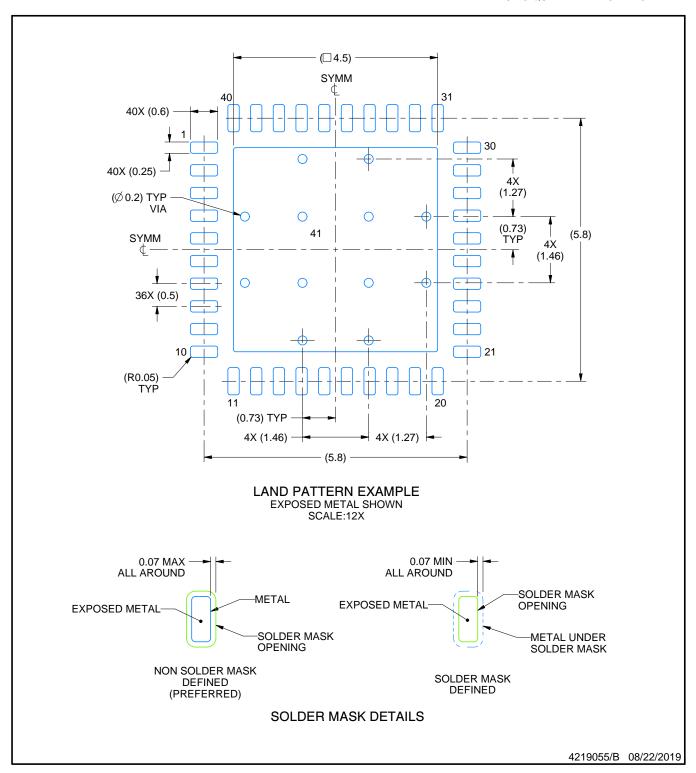

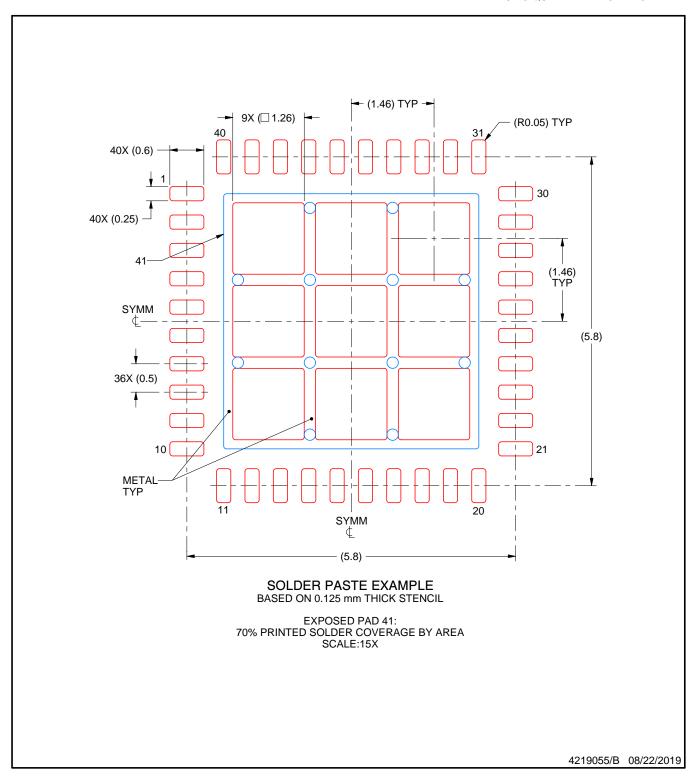

# **5 Pin Configuration and Functions**

Figure 5-1. RHA Package 40-Pin VQFN Top View

**Table 5-1. Pin Functions**

|         | PIN                                    | TVDE   | PERCENTION                                                                                                                                                                   |

|---------|----------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO.                                    | TYPE   | DESCRIPTION                                                                                                                                                                  |

| CE      | 1                                      | Input  | Chip Enable input. Active high powers on the device.                                                                                                                         |

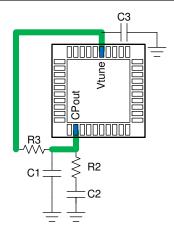

| CPout   | 12                                     | Output | Charge pump output. Recommend connecting C1 of loop filter close to pin.                                                                                                     |

| CSB     | 24                                     | Input  | SPI chip select bar or uWire latch enable (abbreviated as LE in Figure 6-1). High impedance CMOS input. 1.8 to 3.3-V logic.                                                  |

| DAP     | GND                                    | Ground | RFout ground.                                                                                                                                                                |

| GND     | 2, 4, 6, 13, 14, 25,<br>31, 34, 39, 40 | Ground | VCO ground.                                                                                                                                                                  |

| MUXout  | 20                                     | Output | Programmable with register MUXOUT_SEL to be readback SDO or lock detect indicator (active high).                                                                             |

| NC      | 5, 28, 30, 32                          | _      | Not connected.                                                                                                                                                               |

| OSCinP  | 8                                      | Input  | Differential reference input clock (+). High input impedance. Requires connecting series capacitor (0.1-µF recommended).                                                     |

| OSCinM  | 9                                      | Input  | Differential reference input clock (–). High input impedance. Requires connecting series capacitor (0.1-µF recommended).                                                     |

| RFoutAM | 22                                     | Output | Differential output A (–). This output requires a pullup component for proper biasing. A $50-\Omega$ resistor or inductor may be used. Place as close to output as possible. |

| RFoutAP | 23                                     | Output | Differential output A (+). This output requires a pullup component for proper biasing. A $50-\Omega$ resistor or inductor may be used. Place as close to output as possible. |

| RFoutBP | 19                                     | Output | Differential output B (+). This output requires a pullup component for proper biasing. A 50-Ω resistor or inductor may be used. Place as close to output as possible.        |

| RFoutBM | 18                                     | Output | Differential output B (–). This output requires a pullup component for proper biasing. A $50-\Omega$ resistor or inductor may be used. Place as close to output as possible. |

| SCK     | 16                                     | Input  | SPI or uWire clock (abbreviated as CLK in Figure 6-1). High impedance CMOS input. 1.8 to 3.3-V logic.                                                                        |

| SDI     | 17                                     | Input  | SPI or uWire data (abbreviated as DATA in Figure 6-1). High impedance CMOS input. 1.8 to 3.3-V logic.                                                                        |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

**Table 5-1. Pin Functions (continued)**

| PIN                  |     | TVDE   | DESCRIPTION                                                                                                                     |  |  |  |

|----------------------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                 | NO. | TYPE   | DESCRIPTION                                                                                                                     |  |  |  |

| VbiasVARAC           | 33  | Bypass | VCO varactor internal voltage, access for bypass. Requires connecting 10-μF capacitor to VCO ground.                            |  |  |  |

| VbiasVCO             | 3   | Bypass | VCO bias internal voltage, access for bypass. Requires connecting 10-μF capacitor to VCO ground. Place close to pin.            |  |  |  |

| VbiasVCO2            | 27  | Bypass | VCO bias internal voltage, access for bypass. Requires connecting 1-μF capacitor to VCO ground.                                 |  |  |  |

| V <sub>CC</sub> BUF  | 21  | Supply | Output buffer supply. Requires connecting 0.1-µF capacitor to RFout ground.                                                     |  |  |  |

| V <sub>CC</sub> CP   | 11  | Supply | Charge pump supply. Recommend connecting 0.1-µF capacitor to charge pump ground.                                                |  |  |  |

| V <sub>CC</sub> DIG  | 7   | Supply | Digital supply. Recommend connecting 0.1-µF capacitor to digital ground.                                                        |  |  |  |

| V <sub>CC</sub> MASH | 15  | Supply | Digital supply. Recommend connecting 0.1-μF and 10-μF capacitor to digital ground.                                              |  |  |  |

| V <sub>CC</sub> VCO  | 37  | Supply | VCO supply. Recommend connecting 0.1-μF and 10-μF capacitor to ground.                                                          |  |  |  |

| V <sub>CC</sub> VCO2 | 26  | Supply | VCO supply. Recommend connecting 0.1-μF and 10-μF capacitor to VCO ground.                                                      |  |  |  |

| VrefVCO              | 36  | Bypass | VCO supply internal voltage, access for bypass. Requires connecting 10-μF capacitor to ground.                                  |  |  |  |

| VrefVCO2             | 29  | Bypass | VCO supply internal voltage, access for bypass. Requires connecting 10-μF capacitor to VCO ground.                              |  |  |  |

| VregIN               | 10  | Bypass | Input reference path internal voltage, access for bypass. Requires connecting 1-μF capacitor to ground. Place close to pin.     |  |  |  |

| VregVCO              | 38  | Bypass | VCO supply internal voltage, access for bypass. Requires connecting 1-μF capacitor to ground.                                   |  |  |  |

| Vtune                | 35  | Input  | VCO tuning voltage input. This signal should be kept away from noise sources. Connect a 3.3-nF or more capacitor to VCO ground. |  |  |  |

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                    |                                                       | MIN                                  | MAX                         | UNIT |

|--------------------|-------------------------------------------------------|--------------------------------------|-----------------------------|------|

| V <sub>CC</sub>    | Power supply voltage                                  | -0.3                                 | 3.6                         | V    |

| V <sub>IN</sub>    | Input voltage to pins other than V <sub>CC</sub> pins | -0.3                                 | $V_{CC} + 0.3$              | V    |

| V <sub>OSCin</sub> | Voltage on OSCin (pin 8 and pin 9)                    | ≤1.8 with V <sub>CC</sub><br>Applied | ≤1 with V <sub>CC</sub> = 0 | Vpp  |

| TL                 | Lead temperature (solder 4 s)                         |                                      | 260                         | °C   |

| TJ                 | Junction temperature                                  | -40                                  | 150                         | °C   |

| T <sub>stg</sub>   | Storage temperature                                   | -65                                  | 150                         | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±750  | V    |

|                    |                         | Machine model (MM) ESD stress voltage                                          | ±250  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2500 V may actually have higher performance.

#### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                 |                      | MIN  | NOM | MAX  | UNIT |

|-----------------|----------------------|------|-----|------|------|

| V <sub>CC</sub> | Power supply voltage | 3.15 |     | 3.45 | V    |

| T <sub>A</sub>  | Ambient temperature  | -40  |     | 85   | °C   |

| TJ              | Junction temperature |      |     | 125  | °C   |

### 6.4 Thermal Information

|                               |                                              | LMX2592    |      |  |

|-------------------------------|----------------------------------------------|------------|------|--|

| THERMAL METRIC <sup>(1)</sup> |                                              | RHA (VQFN) | UNIT |  |

|                               |                                              | 40 PINS    |      |  |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 30.5       | °C/W |  |

| R <sub>0JC(top)</sub>         | Junction-to-case (top) thermal resistance    | 15.3       | °C/W |  |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 5.4        | °C/W |  |

| ΨЈТ                           | Junction-to-top characterization parameter   | 0.2        | °C/W |  |

| ΨЈВ                           | Junction-to-board characterization parameter | 5.3        | °C/W |  |

| R <sub>0</sub> JC(bot)        | Junction-to-case (bottom) thermal resistance | 0.9        | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: LMX2592

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±1250 V may actually have higher performance.

# **6.5 Electrical Characteristics**

$3.15~V \le V_{CC} \le 3.45~V, -40^{\circ}C \le T_{A} \le 85^{\circ}C.$  Typical values are at  $V_{CC} = 3.3~V, 25^{\circ}C$  (unless otherwise noted)

|                         | PARAMETER                                                             | Т                                    | EST CONDITIONS                            | MIN  | TYP    | MAX  | UNIT      |

|-------------------------|-----------------------------------------------------------------------|--------------------------------------|-------------------------------------------|------|--------|------|-----------|

| POWER SUI               | PPLY                                                                  |                                      |                                           |      |        |      |           |

| V <sub>CC</sub>         | Supply voltage                                                        |                                      |                                           |      | 3.3    |      | V         |

| I <sub>cc</sub>         | Supply current                                                        | Single 6-GH                          | z, 0-dBm output <sup>(1)</sup>            |      | 250    |      | mA        |

| I <sub>PD</sub>         | Powerdown current                                                     |                                      |                                           |      | 3.7    |      | mA        |

| OUTPUT CH               | IARACTERISTICS                                                        |                                      |                                           |      |        |      |           |

| F <sub>out</sub>        | Output frequency                                                      |                                      |                                           | 20   |        | 9800 | MHz       |

| P <sub>out</sub>        | Typical high output power                                             | Output = 3 G<br>ended <sup>(2)</sup> | GHz, 50-Ω pullup, single-                 |      | 8      |      | dBm       |

| Tcal                    | VCO calibration time                                                  | Reference in desired outp            | put = 100 MHz, 7-GHz<br>ut <sup>(8)</sup> |      | 590    | 800  | μs        |

| INPUT SIGN              | IAL PATH                                                              |                                      |                                           |      |        | '    |           |

| REFin                   | Reference input frequency                                             |                                      |                                           | 5    |        | 1400 | MHz       |

| REFv                    | Reference input voltage                                               | AC-coupled,                          | differential <sup>(3)</sup>               | 0.2  |        | 2    | Vppd      |

| MULin                   | Input signal path multiplier input frequency                          |                                      |                                           | 40   |        | 70   | MHz       |

| MULout                  | Input signal path multiplier output frequency                         |                                      |                                           | 180  |        | 250  | MHz       |

| PHASE DET               | ECTOR AND CHARGE PUMP                                                 |                                      |                                           |      |        | 1    |           |

| DDE                     | Discount data at a few many                                           |                                      |                                           | 5    |        | 200  | MHz       |

| PDF                     | Phase detector frequency                                              | Extended rai                         | nge mode <sup>(4)</sup>                   | 0.25 |        | 400  | MHz       |

| CPI                     | Charge pump current                                                   | Programmak                           | ole                                       | 0    |        | 12   | mA        |

| PLL PHASE               | NOISE                                                                 |                                      |                                           |      | ,      | '    |           |

| PLL_flicker_Nor         | Normalized PLL Flicker Noise <sup>(5)</sup>                           |                                      |                                           |      | -126   |      | dBc/Hz    |

| PLL_FOM                 | Normalized PLL Noise Floor (PLL Figure of Merit) <sup>(5)</sup>       |                                      |                                           |      | -231   |      | dBc/Hz    |

| VCO                     |                                                                       |                                      |                                           |      |        |      |           |

| ΔT <sub>CL</sub>        | Allowable temperature drift <sup>(6)</sup>                            | VCO not bei                          | ng recalibrated                           |      |        | 125  | °C        |

|                         |                                                                       | 100 kHz                              |                                           |      | -118.8 |      |           |

|                         | Output = 3 GHz                                                        | 1 MHz                                |                                           |      | -140.3 |      |           |

|                         | Output = 3 GHz                                                        | 10 MHz                               |                                           |      | -155.1 |      |           |

|                         |                                                                       | 100 MHz                              |                                           |      | -156.3 |      |           |

|                         |                                                                       | 100 kHz                              |                                           |      | -112.6 |      |           |

| DNI                     | Outrot - C OH-                                                        | 1 MHz                                |                                           |      | -134.2 |      | المال مال |

| PN <sub>open loop</sub> | Output = 6 GHz                                                        | 10 MHz                               |                                           |      | -152.6 |      | dBc/H     |

|                         |                                                                       | 100 MHz                              |                                           |      | -156.2 |      |           |

|                         |                                                                       | 100 kHz                              |                                           |      | -108.2 |      |           |

|                         | Output = 0.9 CHz                                                      | 1 MHz                                |                                           |      | -129.1 |      |           |

|                         | Output = 9.8 GHz                                                      | 10 MHz                               |                                           |      | -140.5 |      | 1         |

|                         |                                                                       | 100 MHz                              |                                           |      | -141.1 |      |           |

| HARMONIC                | DISTORTION <sup>(7)</sup>                                             |                                      |                                           |      |        |      |           |

| HD_fund                 | Harmonic Distortion fundamental feed-<br>through with doubler enabled | 8 GHz,<br>VCO<br>doubler<br>enabled  | Fundamental (4 GHz)                       |      | -26    |      |           |

# $3.15~\textrm{V} \leq \textrm{V}_{\textrm{CC}} \leq 3.45~\textrm{V}, -40^{\circ}\textrm{C} \leq \textrm{T}_{\textrm{A}} \leq 85^{\circ}\textrm{C}.$

Typical values are at V<sub>CC</sub> = 3.3 V, 25°C (unless otherwise noted)

|                 | PARAMETER                                    | TEST CONDITIONS                                                                      | MIN | TYP                   | MAX             | UNIT |  |  |

|-----------------|----------------------------------------------|--------------------------------------------------------------------------------------|-----|-----------------------|-----------------|------|--|--|

| HD2             | 2nd Order Harmonic Distortion <sup>(9)</sup> | Testing output A, output at 5 GHz, output                                            | -27 |                       |                 | dBc  |  |  |

| HD3             | 3rd Order Harmonic Distortion <sup>(9)</sup> | power level at 8.5-dBm, single-ended output, other end terminated with 50 $\Omega$ . |     | -25                   |                 | dBc  |  |  |

| DIGITAL IN      | DIGITAL INTERFACE                            |                                                                                      |     |                       |                 |      |  |  |

| V <sub>IH</sub> | High level input voltage                     |                                                                                      | 1.4 |                       | V <sub>CC</sub> | V    |  |  |

| V <sub>IL</sub> | Low level input voltage                      |                                                                                      | 0   |                       | 0.4             | V    |  |  |

| I <sub>IH</sub> | High level input current                     |                                                                                      | -25 |                       | 25              | μΑ   |  |  |

| I <sub>IL</sub> | Low level input current                      |                                                                                      | -25 |                       | 25              | μΑ   |  |  |

| V <sub>OH</sub> | High level output voltage                    | Load/Source Current of –350 μA                                                       |     | V <sub>CC</sub> – 0.4 |                 | V    |  |  |

| V <sub>OL</sub> | Low level output voltage                     | Load/Sink Current of 500 μA                                                          |     | 0.4                   |                 | V    |  |  |

| SPIW            | Highest SPI write speed                      |                                                                                      |     | 75                    |                 | MHz  |  |  |

| SPIR            | SPI read speed                               |                                                                                      |     | 50                    |                 | MHz  |  |  |

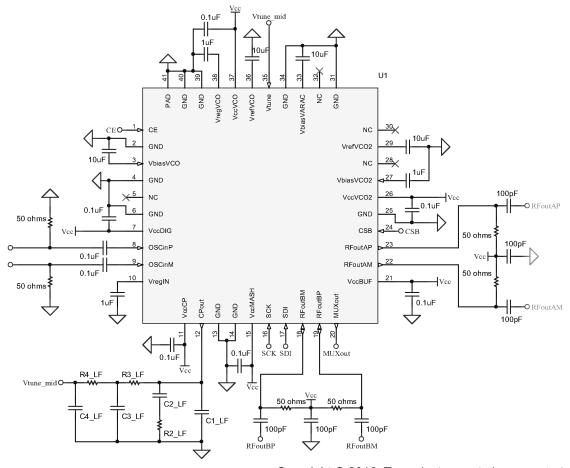

- (1) For typical total current consumption of 250 mA: 100-MHz input frequency, OSCin doubler bypassed, pre-R divider bypassed, multiplier bypassed, post-R divider bypassed, 100-MHz phase detector frequency, 0.468-mA charge pump current, channel divider off, one output on, 6GHz output frequency, 50-Ω output pullup, 0-dBm output power (differential). See the *Application and Implementation* section for more information.

- (2) For a typical high output power for a single-ended output, with 50-Ω pullup on both M and P side, register OUTx\_POW = 63. Un-used side terminated with 50-Ω load.

- (3) There is internal voltage biasing so the OSCinM and OSCinP pins must always be AC-coupled (capacitor in series). Vppd is differential peak-to-peak voltage swing. If there is a differential signal (two are negative polarity of each other), the total swing is one subtracted by the other, each should be 0.1 to 1-Vppd. If there is a single-ended signal, it can have 0.2 to 2 Vppd. See the *Application and Implementation* section for more information.

- (4) To use phase detector frequencies lower than 5-MHz set register FCAL\_LPFD\_ADJ = 3. To use phase detector frequencies higher than 200 MHz, you must be in integer mode, set register PFD\_CTL = 3 (to use single PFD mode), set FCAL\_HPFD\_ADJ = 3. For more information, see the *Detailed Description* section.

- (5) The PLL noise contribution is measured using a clean reference and a wide loop bandwidth and is composed into flicker and flat components. PLL\_flat = PLL\_FOM + 20 × log(Fvco/Fpd) + 10 × log(Fpd / 1Hz). PLL\_flicker (offset) = PLL\_flicker\_Norm + 20 × log(Fvco / 1GHz) 10 × log(offset / 10kHz). Once these two components are found, the total PLL noise can be calculated as PLL\_Noise = 10 × log(10PLL\_Flat / 10 + 10PLL\_flicker / 10).

- (6) Not tested in production. Ensured by characterization. Allowable temperature drift refers to programming the device at an initial temperature and allowing this temperature to drift without reprogramming the device, and still have the device stay in lock. This change could be up or down in temperature and the specification does not apply to temperatures that go outside the recommended operating temperatures of the device.

- (7) Not tested in production. Typical numbers from characterization with output settings: 50-Ω pullup, OUTA\_POW = 15, channel divider off.

- (8) The is the calibration time from the time of FCAL\_EN = 1 is triggered to the calibration algorithm completing and output at 7 GHz. A reference input signal of 100 MHz is used and register CAL\_CLK\_DIV = 0 for state machine clock to be 100 MHz. Faster calibration times can be achieve through changes of other register settings. See the *Application and Implementation* section for more information. This parameter is ensured by bench.

- (9) This parameter is verified by characterization on evaluation board, not tested in production.

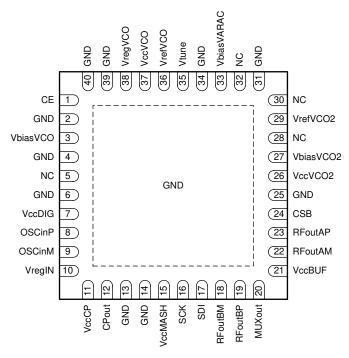

#### 6.6 Timing Requirements

$3.15 \text{ V} \le \text{V}_{CC} \le 3.45 \text{ V}$ ,  $-40 ^{\circ}\text{C} \le \text{T}_{A} \le 85 ^{\circ}\text{C}$ , except as specified. Typical values are at  $\text{V}_{CC} = 3.3 \text{ V}$ ,  $\text{T}_{A} = 25 ^{\circ}\text{C}$

|        |                            |                | MIN | TYP | MAX | UNIT |

|--------|----------------------------|----------------|-----|-----|-----|------|

| MICROV | VIRE TIMING                |                |     |     |     |      |

| tES    | Clock to enable low time   |                | 5   |     |     | ns   |

| tCS    | Data to clock setup time   |                | 2   |     |     | ns   |

| tCH    | Data to clock hold time    |                | 2   |     |     | ns   |

| tCWH   | Clock pulse width high     | See Figure 6-1 | 5   |     |     | ns   |

| tCWL   | Clock pulse width low      |                | 5   |     |     | ns   |

| tCES   | Enable to clock setup time |                | 5   |     |     | ns   |

| tEWH   | Enable pulse width high    |                | 2   |     |     | ns   |

Product Folder Links: 1 MX2592

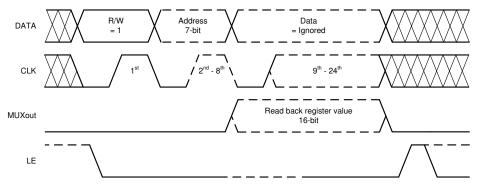

Figure 6-1. Serial Data Input Timing Diagram

There are several considerations for programming:

- A slew rate of at least 30 V/µs is recommended for the CLK, DATA, LE

- The DATA is clocked into a shift register on each rising edge of the CLK signal. On the rising edge of the last CLK signal, the data is sent from the shift registers to a register bank

- · The LE pin may be held high after programming and clock pulses are ignored

- When CLK and DATA lines are shared between devices, TI recommends diving down the voltage to the CLK, DATA, and LE pins closer to the minimum voltage. This provides better noise immunity

- If the CLK and DATA lines are toggled while the VCO is in lock, as is sometimes the case when these lines are shared with other parts, the phase noise may be degraded during the time of this programming

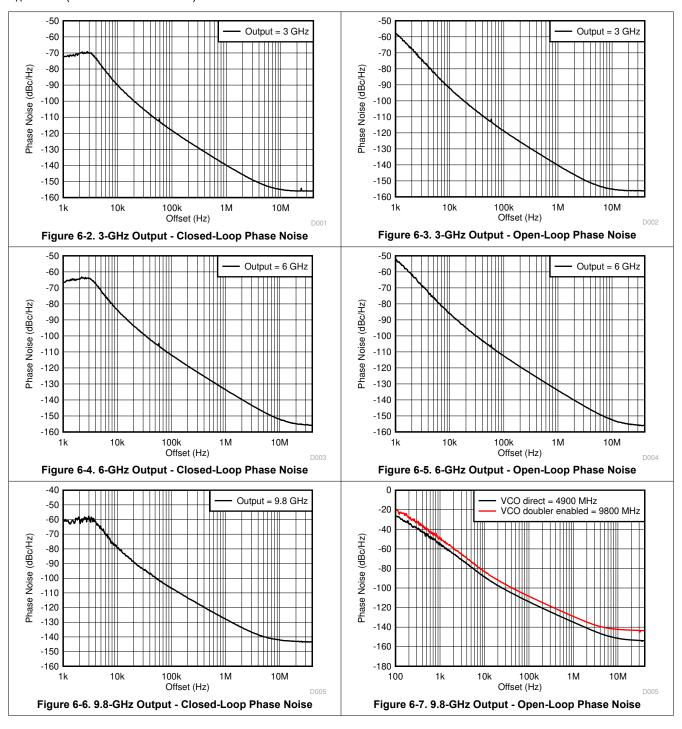

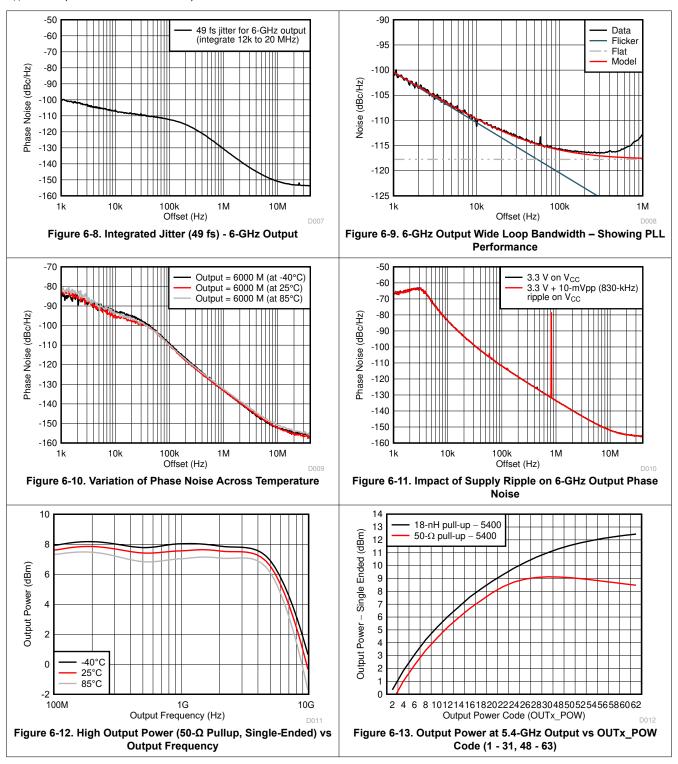

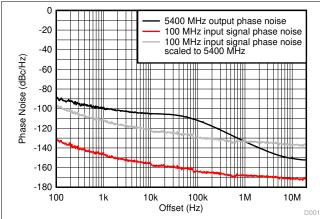

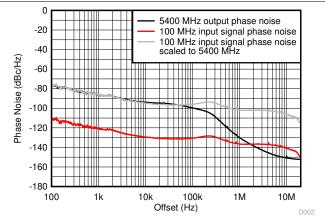

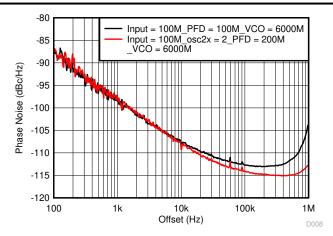

# **6.7 Typical Characteristics**

T<sub>A</sub> = 25°C (unless otherwise noted)

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 6.7 Typical Characteristics (continued)

T<sub>A</sub> = 25°C (unless otherwise noted)

# **6.7 Typical Characteristics (continued)**

T<sub>A</sub> = 25°C (unless otherwise noted)

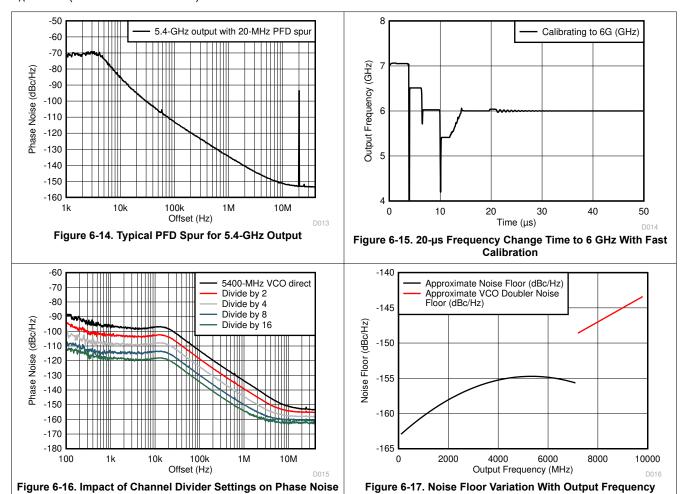

# 7 Detailed Description

#### 7.1 Overview

The LMX2592 is a high performance wideband synthesizer (PLL with integrated VCO). The output frequency range is from 20 MHz to 9.5 GHz. The VCO core covers an octave from 3.55 to 7.1 GHz. The output channel divider covers the frequency range from 20 MHz to the low bound of the VCO core. The VCO-doubler covers the frequency range from the upper bound of the VCO to 9800MHz.

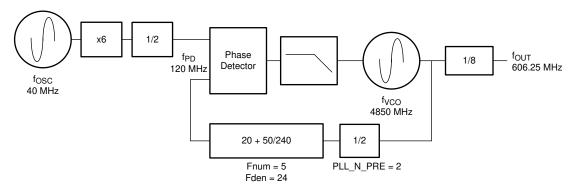

The input signal frequency has a wide range from 5 to 1400 MHz. Following the input, there is an programmable OSCin doubler, a pre-R divider (previous to multiplier), a multiplier, and then a post-R divider (after multiplier) for flexible frequency planning between the input (OSCin) and the phase detector.

The phase detector (PFD) can take frequencies from 5 to 200 MHz, but also has extended modes down to 0.25 MHz and up to 400 MHz. The phase-lock loop (PLL) contains a Sigma-Delta modulator (1st to 4th order) for fractional N-divider values. The fractional denominator is programmable to 32-bit long, allowing a very fine resolution of frequency step. There is a phase adjust feature that allows shifting of the output phase in relation to the input (OSCin) by a fraction of the size of the fractional denominator.

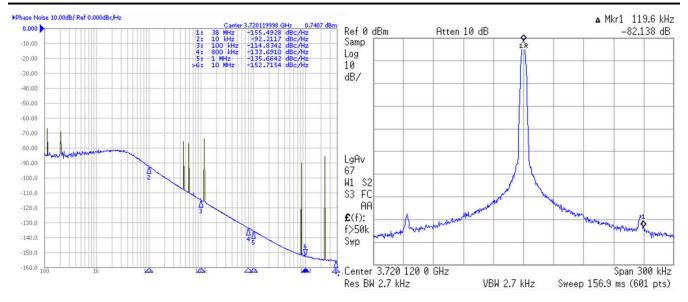

The output power is programmable and can be designed for high power at a specific frequency by the pullup component at the output pin.

The digital logic is a standard 4-wire SPI or uWire interface and is 1.8-V and 3.3-V compatible.

### 7.2 Functional Block Diagram

#### 7.3 Functional Description

#### 7.3.1 Input Signal

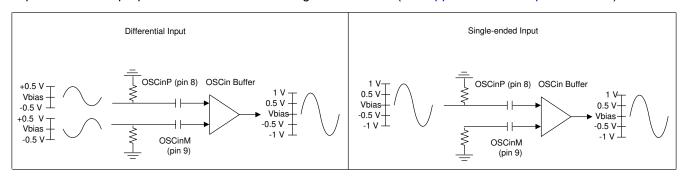

An input signal is required for the PLL to lock. The input signal is also used for the VCO calibration, so a proper signal needs to be applied before the start of programming. The input signal goes to the OSCinP and OSCinM pins of the device (there is internal biasing which requires AC-coupling caps in series before the pin). This is a differential buffer so the total swing is the OSCinM signal subtracted by the OSCinP signal. Both differential signals and single-ended signal can be used. Below is an example of the max signal level in each mode. It is important to have proper termination and matching on both sides (see *Application and Implementation*).

Figure 7-1. Differential vs. Single-Ended Mode

#### 7.3.2 Input Signal Path

The input signal path contains the components between the input (OSCin) buffer and the phase detector. The best PLL noise floor is achieved with a 200-MHz input signal for the highest dual-phase detector frequency. To address a wide range of applications, the input signal path contains the below components for flexible configuration before the phase detector. Each component can be bypassed. See Table 7-1 for usage boundaries if engaging a component.

- OSCin doubler: This is low noise frequency doubler which can be used to multiply input frequencies by two. The doubler uses both the rising and falling edge of the input signal so the input signal must have 50% duty cycle if enabling the doubler. The best PLL noise floor is achieved with 200-MHz PFD, thus the doubler is useful if, for example, a very low-noise, 100-MHz input signal is available instead.

- Pre-R divider: This is a frequency divider capable of very high frequency inputs. Use this to divide any input frequency up to 1400-MHz, and then the post-R divider if lower frequencies are needed.

- Multiplier: This is a programmable, low noise multiplier. In combination with the Pre-R and Post-R dividers, the multiplier offers the flexibility to set a PFD away from frequencies that may create critical integer boundary spurs with the VCO and output frequencies. See the *Application and Implementation* section for an example. The user should not use the doubler while using the low noise programmable multiplier.

- Post-R divider: Use this divider to divide down to frequencies below 5 MHz in extended PFD mode.

| Table 7 1. Boundaries for input 1 day components |           |            |           |            |  |  |  |  |  |  |

|--------------------------------------------------|-----------|------------|-----------|------------|--|--|--|--|--|--|

|                                                  | IN        | PUT        | OU.       | ГРИТ       |  |  |  |  |  |  |

|                                                  | LOW (MHz) | HIGH (MHz) | LOW (MHz) | HIGH (MHz) |  |  |  |  |  |  |

| Input signal                                     | 5         | 1400       |           |            |  |  |  |  |  |  |

| OSCin doubler                                    | 5         | 200        | 10        | 400        |  |  |  |  |  |  |

| Pre-R divider                                    | 10        | 1400       | 5         | 700        |  |  |  |  |  |  |

| Multiplier                                       | 40        | 70         | 180       | 250        |  |  |  |  |  |  |

| Post-R divider                                   | 5         | 250        | 0.25      | 125        |  |  |  |  |  |  |

| PFD                                              | 0.25      | 400        |           |            |  |  |  |  |  |  |

|                                                  |           |            |           |            |  |  |  |  |  |  |

Table 7-1. Boundaries for Input Path Components

#### 7.3.3 PLL Phase Detector and Charge Pump

The PLL phase detector, also known as phase frequency detector (PFD), compares the outputs of the post-R divider and N divider and generates a correction current with the charge pump corresponding to the phase error until the two signals are aligned in phase (the PLL is locked). The charge pump output goes through external components (loop filter) which turns the correction current pulses into a DC voltage applied to the tuning voltage (Vtune) of the VCO. The charge pump gain level is programmable and allow to modify the loop bandwidth of the PLL.

The default architecture is a dual-loop PFD which can operate between 5 to 200 MHz. To use it in extended range mode the PFD has to be configured differently:

- Extended low phase detector frequency mode: For frequencies between 250 kHz and 5 MHz, low PFD mode can be activated (FCAL\_LPFD\_ADJ = 3). PLL\_N\_PRE also needs to be set to 4.

- Extended high phase detector frequency mode: For frequencies between 200 and 400 MHz, high PFD mode can be activated (FCAL\_HPFD\_ADJ = 3). The PFD also has to be set to single-loop PFD mode (PFD\_CTL = 3). This mode only works if using integer-N, and PLL noise floor will be about 6-dB higher than in dual-loop PFD mode.

# 7.3.4 N Divider and Fractional Circuitry

The N divider (12 bits) includes a multi-stage noise shaping (MASH) sigma-delta modulator with programmable order from 1st to 4th order, which performs fractional compensation and can achieve any fractional denominator from 1 to  $(2^{32} - 1)$ . Using programmable registers, PLL\_N is the integer portion and PLL\_NUM / PLL\_DEN is the fractional portion, thus the total N divider value is determined by PLL\_N + PLL\_NUM / PLL\_DEN. This allows the output frequency to be a fractional multiplication of the phase detector frequency. The higher the denominator the finer the resolution step of the output. There is a N divider prescaler (PLL\_N\_PRE) between the VCO and

the N divider which performs a division of 2 or 4. 2 is selected typically for higher performance in fractional mode and 4 may be desirable for lower power operation and when N is approaching max value.

Fvco = Fpd × PLL N PRE × (PLL N + PLL NUM / PLL DEN)

Minimum output frequency step = Fpd × PLL\_N\_PRE / PLL\_DEN / [Channel divider value]

Typically, higher modulator order pushes the noise out in frequency and may be filtered out with the PLL. However, several tradeoff needs to be made. Table 7-2 shows the suggested minimum N value while in fractional mode as a function of the sigma-delta modulator order. It also describe the recommended register setting for the PFD delay (register PFD\_DLY\_SEL).

Table 7-2. MASH Order and N Divider

|                                             | INTEGER-N | 1st ORDER | 2nd ORDER | 3rd ORDER | 4th ORDER |

|---------------------------------------------|-----------|-----------|-----------|-----------|-----------|

| Minimum N divider (low bound)               | 9         | 11        | 16        | 18        | 30        |

| PFD delay recommended setting (PFD_DLY_SEL) | 1         | 1         | 2         | 2         | 8         |

#### 7.3.5 Voltage Controlled Oscillator

The voltage controlled oscillator (VCO) is fully integrated. The frequency range of the VCO is from 3.55 to 7.1 GHz so it covers one octave. Channel dividers allow the generation of all other lower frequencies. The VCO-doubler allow the generation of all other higher frequencies. The output frequency of the VCO is inverse proportional to the DC voltage present at the tuning voltage point on pin Vtune. The tuning range is 0 V to 2.5 V. 0 V generates the maximum frequency and 2.5 V generates the minimum frequency. This VCO requires a calibration procedure for each frequency selected to lock on. Each VCO calibration will force the tuning voltage to mid value and calibrate the VCO circuit. Any frequency setting in fast calibration occurs in the range of Vtune pin 0 V to 2.5 V. The VCO is designed to remained locked over the entire temperature range the device can support. Table 7-3 shows the VCO gain as a function of frequency.

Table 7-3. Typical kVCO

| VCO FREQUENCY (MHz) | kVCO (MHz/V) |

|---------------------|--------------|

| 3700                | 28           |

| 4200                | 30           |

| 4700                | 33           |

| 5200                | 36           |

| 5700                | 41           |

| 6200                | 47           |

| 6800                | 51           |

#### 7.3.6 VCO Calibration

The VCO calibration is responsible of setting the VCO circuit to the target frequency. The frequency calibration routine is activated any time that the R0 register is programmed with the FCAL\_EN = 1. A valid input (OSCin) signal to the device must present before the VCO calibration begins. To see how to reduce the calibration time, refer to the *Application and Implementation* section.

# 7.3.7 VCO Doubler

To go above the VCO upper bound, the VCO-doubler must be used (VCO\_2X\_EN=1). The doubling block can be enabled while the VCO is between 3.55 GHz (lowest VCO frequency) and 4.9 GHz. When VCO doubler is enabled, the N divider prescalar is automatically forced to divide by 4.

Copyright © 2022 Texas Instruments Incorporated

#### 7.3.8 Channel Divider

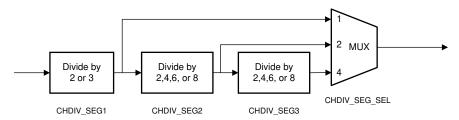

Figure 7-2. Channel Divider Diagram

To go below the VCO lower bound, the channel divider must be used. The channel divider consists of three programmable dividers controlled by the registers CHDIV SEG1, CHDIV SEG2, CHDIV SEG3. The Multiplexer (programmed with register CHDIV SEG SEL) selects which divider is included in the path. The minimum division is 2 while the maximum division is 192. Un-used dividers can be powered down to save current consumption. The entire channel divider can be powered down with register CHDIV EN = 0 or selectively setting registers CHDIV SEG1 EN = 0, CHDIV SEG2 EN = 0, CHDIV SEG3 EN = 0. Unused buffers may also be powered down with registers CHDIV DISTA EN and CHDIV DIST EN. There are restrictions on the maximum VCO frequency when channel divider is engaged.

Table 7-4. Channel Divider vs VCO Frequency

| OUTPUT FRE | QUENCY (MHz) | 1    | CHDIV SEGMEN | Т    | TOTAL    | VCO FREQU | JENCY (MHz) |

|------------|--------------|------|--------------|------|----------|-----------|-------------|

| MIN        | MAX          | SEG1 | SEG2         | SEG3 | DIVISION | MIN       | MAX         |

| 1775       | 3550         | 2    | 1            | 1    | 2        | 3550      | 7100        |

| 1184       | 2200         | 3    | 1            | 1    | 3        | 3552      | 6600        |

| 888        | 1184         | 2    | 2            | 1    | 4        | 3552      | 4736        |

| 592        | 888          | 3    | 2            | 1    | 6        | 3552      | 5328        |

| 444        | 592          | 2    | 4            | 1    | 8        | 3552      | 4736        |

| 296        | 444          | 2    | 6            | 1    | 12       | 3552      | 5328        |

| 222        | 296          | 2    | 8            | 1    | 16       | 3552      | 4736        |

| 148        | 222          | 3    | 8            | 1    | 24       | 3552      | 5328        |

| 111        | 148          | 2    | 8            | 2    | 32       | 3552      | 4736        |

| 99         | 111          | 3    | 6            | 2    | 36       | 3564      | 3996        |

| 74         | 99           | 3    | 8            | 2    | 48       | 3552      | 4752        |

| 56         | 74           | 2    | 8            | 4    | 64       | 3584      | 4736        |

| 37         | 56           | 2    | 8            | 6    | 96       | 3552      | 5376        |

| 28         | 37           | 2    | 8            | 8    | 128      | 3584      | 4736        |

| 20         | 28           | 3    | 8            | 8    | 192      | 3840      | 5376        |

Product Folder Links: LMX2592

#### 7.3.9 Output Distribution

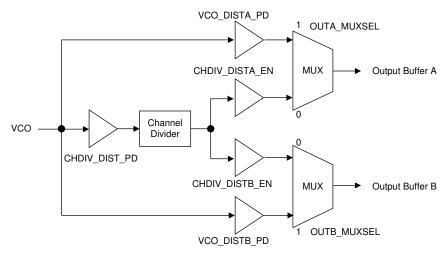

Figure 7-3. Output Distribution Diagram

For each output A or B, there is a mux which select the VCO output directly or the channel divider output. Before these selection MUX there are several buffers in the distribution path which can be configured depending on the route selected. By disabling unused buffers, unwanted signals can be isolated and unneeded current consumption can be eliminated.

#### 7.3.10 Output Buffer

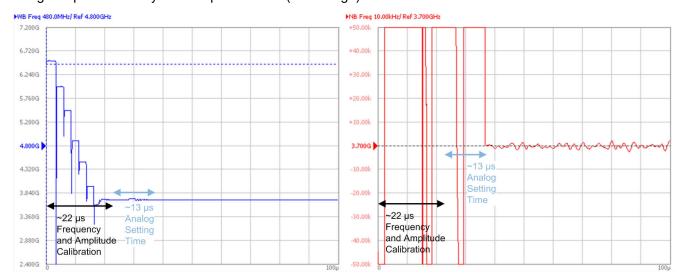

Each output buffer (A and B) have programmable gain with register OUTA\_POW and OUTB\_POW. The RF output buffer configuration is open-collector and requires an external pullup from RFout pin to  $V_{CC}$ . There are two pullup options that can be used with either resistor or inductor. Refer to the *Application and Implementation* section for design considerations.

- 1. Resistor pullup: placing a  $50-\Omega$  resistor pullup matches the output impedance to  $50-\Omega$ . However, maximum output power is limited. Output buffer current settings should be set to a value before output power is saturated (output power increases less for every step increase in output current value).

- 2. Inductor pullup: placing an inductor pullup creates a resonance at the frequency of interest. This offers higher output power for the same current and higher maximum output power. However, the output impedance is higher and additional matching may be required..

### 7.3.11 Phase Adjust

In fractional mode, the phase relationship between the output and the input can be changed with very fine resolution. Every time MASH\_SEED register is written, it will trigger a phase shift of the amount described in Equation 1. The seed value should be less then the fractional-N denominator register PLL\_N\_DEN. The actual phase shift can be obtained with the following equation:

### 7.4 Device Functional Modes

### 7.4.1 Power Down

Power up and down can be achieved using the CE pin (logic HIGH or LOW voltage) or the POWERDOWN register bit (0 or 1). When the device comes out of the powered-down state, either by pulling back CE pin HIGH (if it was powered down by CE pin) or by resuming the POWERDOWN bit to 0 (if it was powered down by register write), it is required that register R0 be programmed again to re-calibrate the device.

#### 7.4.2 Lock Detect

The MUXout pin can be configured to output a signal that gives an indication for the PLL being locked. If lock detect is enabled (LD\_EN = 1) and the MUXout pin is configured as lock detect output (MUXOUT\_SEL = 1),

Copyright © 2022 Texas Instruments Incorporated

when the device is locked, the MUXout pin output is a logic HIGH voltage, and when the device is unlocked, MUXout output is a logic LOW voltage.

#### 7.4.3 Register Readback

The MUXout pin can be programmed (MUXOUT\_SEL = 0) to use register readback serial data output. Timing requirements for MUXout to CLK follow the same specifications as Data to CLK in *Timing Requirements*. To read back a certain register value, use the following steps:

- 1. Set the R/W bit to 1; the data field contents are ignored.

- 2. Program this register to the device, readback serial data will be output starting at the 9th clock.

Figure 7-4. Register Readback Timing Diagram

#### 7.5 Programming

The programming using 24-bit shift registers. The shift register consists of a R/W bit (MSB), followed by a 7-bit address field and a 16-bit data field. For the R/W (bit 23), 1 is read and 0 is write. The address field ADDRESS (bits 22:16) is used to decode the internal register address. The remaining 16 bits form the data field DATA (bits 15:0). While CSB is low, serial data is clocked into the shift register upon the rising edge of clock (data is programmed MSB first). When CSB goes high, data is transferred from the data field into the selected register bank.

#### 7.5.1 Recommended Initial Power on Programming Sequence

When the device is first powered up, the device needs to be initialized and the ordering of this programming is very important. After this sequence is completed, the device should be running and locked to the proper frequency.

- 1. Apply power to the device and ensure the V<sub>CC</sub> pins are at the proper levels

- 2. Ensure that a valid reference is applied to the OSCin pin

- 3. Soft reset the device (write R0[1] = 1)

- 4. Program the remaining registers

- 5. Frequency calibrate (write R0[3] = 1)

#### 7.5.2 Recommended Sequence for Changing Frequencies

The recommended sequence for changing frequencies is as follows:

- 1. Set the new N divider value (write R38[12:1])

- 2. Set the new PLL numerator (R45 and R44) and denominator (R41 and R40)

- 3. Frequency calibrate (write R0[3] = 1)

# 7.6 Register Maps

# 7.6.1 LMX2592 Register Map – Default Values

|     |         |    |    |      |      |      |    |    |    |                                   | Fig                  | ure 7   | -5. R      | legis                       | ter Ta               | ble                       |                       |      |               |                 |          |                    |                           |                   |

|-----|---------|----|----|------|------|------|----|----|----|-----------------------------------|----------------------|---------|------------|-----------------------------|----------------------|---------------------------|-----------------------|------|---------------|-----------------|----------|--------------------|---------------------------|-------------------|

| REG | 23      | 22 | 21 | 20   | 19   | 18   | 17 | 16 | 15 | 14                                | 13                   | 12      | 11         | 10                          | 9                    | 8                         | 7                     | 6    | 5             | 4               | 3        | 2                  | 1                         | 0                 |

|     | R/<br>W |    |    | ADDF | RESS | 6:0] |    |    |    |                                   |                      |         |            |                             |                      | DAT                       | A [15:0]              |      |               |                 |          |                    |                           |                   |

| 0   | R/<br>W | 0  | 0  | 0    | 0    | 0    | 0  | 0  | 0  | 0                                 | LD_EN                | 0       | 0          | 0                           | 1                    |                           | _HPFD<br>ADJ          |      | _LPFD_<br>ADJ | ACA<br>L_E<br>N | FCAL_EN  | MUXO<br>UT_S<br>EL | RES<br>ET                 | POWE<br>RDOW<br>N |

| 1   | R/<br>W | 0  | 0  | 0    | 0    | 0    | 0  | 1  | 0  | 0                                 | 0                    | 0       | 1          | 0                           | 0                    | 0                         | 0                     | 0    | 0             | 0               | 1        | CA                 | L_CLK                     | _DIV              |

| 2   | R/<br>W | 0  | 0  | 0    | 0    | 0    | 1  | 0  | 0  | 0                                 | 0                    | 0       | 0          | 1                           | 0                    | 1                         | 0                     | 0    | 0             | 0               | 0        | 0                  | 0                         | 0                 |

| 4   | R/<br>W | 0  | 0  | 0    | 0    | 1    | 0  | 0  |    |                                   | ,                    | ACAL_CN | иР_DLY     | ,                           |                      |                           | 0                     | 1    | 0             | 0               | 0        | 0                  | 1                         | 1                 |

| 7   | R/<br>W | 0  | 0  | 0    | 0    | 1    | 1  | 1  | 0  | 0                                 | 1                    | 0       | 1          | 0                           | 0                    | 0                         | 1                     | 0    | 1             | 1               | 0        | 0                  | 1                         | 0                 |

| 8   | R/<br>W | 0  | 0  | 0    | 1    | 0    | 0  | 0  | 0  | 0                                 | VCO_ID<br>AC_OV<br>R | 1       | 0          | VCO_<br>CAPC<br>TRL_<br>OVR | 0                    | 0                         | 1                     | 0    | 0             | 0               | 0        | 1                  | 0                         | 0                 |

| 9   | R/<br>W | 0  | 0  | 0    | 1    | 0    | 0  | 1  | 0  | 0                                 | 0                    | 0       | OSC<br>_2X | 0                           | REF_E<br>N           | 1                         | 0                     | 0    | 0             | 0               | 0        | 0                  | 1                         | 0                 |

| 10  | R/<br>W | 0  | 0  | 0    | 1    | 0    | 1  | 0  | 0  | 0                                 | 0                    | 1       |            | l                           | MULT                 |                           |                       | 1    | 0             | 1               | 1        | 0                  | 0                         | 0                 |

| 11  | R/<br>W | 0  | 0  | 0    | 1    | 0    | 1  | 1  | 0  | 0                                 | 0                    | 0       |            |                             |                      | PLI                       | _R                    |      |               |                 | 1        | 0                  | 0                         | 0                 |

| 12  | R/<br>W | 0  | 0  | 0    | 1    | 1    | 0  | 0  | 0  | 1                                 | 1                    | 1       |            |                             |                      |                           |                       | PLI  | _R_PRE        |                 |          |                    |                           |                   |

| 13  | R/<br>W | 0  | 0  | 0    | 1    | 1    | 0  | 1  | 0  | CP_E<br>N                         | 0                    | 0       | 0          | 0                           | 0                    | 0                         | 0                     | 0    | 0             | 0               | 0        | 0                  | PF                        | D_CTL             |

| 14  | R/<br>W | 0  | 0  | 0    | 1    | 1    | 1  | 0  | 0  | 0                                 | 0                    | 0       |            |                             | CP_IDN               |                           |                       |      |               | CP_I            | UP       |                    | CP_I                      | COARSE            |

| 19  | R/<br>W | 0  | 0  | 1    | 0    | 0    | 1  | 1  | 0  | 0                                 | 0                    | 0       |            |                             |                      |                           | VCO_ID                | AC   |               |                 |          | 1                  | 0                         | 1                 |

| 20  | R/<br>W | 0  | 0  | 1    | 0    | 1    | 0  | 0  | 0  | 0                                 | 0                    | 0       | 0          | 0                           | 0                    |                           |                       |      | ACAL_         | _vco_           | IDAC_STR | Г                  |                           |                   |

| 22  | R/<br>W | 0  | 0  | 1    | 0    | 1    | 1  | 0  | 0  | 0                                 | 1                    | 0       | 0          | 0                           | 1                    | 1                         |                       |      |               | VCO_            | _CAPCTRL |                    |                           |                   |

| 23  | R/<br>W | 0  | 0  | 1    | 0    | 1    | 1  | 1  | 1  | FCAL<br>_VC<br>O_S<br>EL_S<br>TRT | V                    | CO_SEL  |            | VCO_<br>SEL_<br>FORC<br>E   | 0                    | 0                         | 0                     | 1    | 0             | 0               | 0        | 0                  | 1                         | 0                 |

| 24  | R/<br>W | 0  | 0  | 1    | 1    | 0    | 0  | 0  | 0  | 0                                 | 0                    | 0       | 0          | 1                           | 0                    | 1                         | 0                     | 0    | 0             | 0               | 1        | 0                  | 0                         | 1                 |

| 25  | R/<br>W | 0  | 0  | 1    | 1    | 0    | 0  | 1  | 0  | 0                                 | 0                    | 0       | 0          | 0                           | 0                    | 0                         | 0                     | 0    | 0             | 0               | 0        | 0                  | 0                         | 0                 |

| 28  | R/<br>W | 0  | 0  | 1    | 1    | 1    | 0  | 0  | 0  | 0                                 | 1                    | 0       | 1          | 0                           | 0                    | 1                         | 0                     | 0    | 1             | 0               | 0        | 1                  | 0                         | 0                 |

| 29  | R/<br>W | 0  | 0  | 1    | 1    | 1    | 0  | 1  | 0  | 0                                 | 0                    | 0       | 0          | 0                           | 0                    | 0                         | 1                     | 0    | 0             | 0               | 0        | 1                  | 0                         | 0                 |

| 30  | R/<br>W | 0  | 0  | 1    | 1    | 1    | 1  | 0  | 0  | 0                                 | 0                    | 0       | 0          | MASH<br>_DITH<br>ER         | 0                    | 0                         | VTUNE                 | _ADJ | 1             | 1               | 0        | 1                  | 0                         | VCO_2<br>X_EN     |

| 31  | R/<br>W | 0  | 0  | 1    | 1    | 1    | 1  | 1  | 0  | 0                                 | 0                    | 0       | 0          | VCO_<br>DIST<br>B_PD        | VCO_D<br>ISTA_P<br>D | 0                         | CHDIV<br>_DIST<br>_PD | 0    | 0             | 0               | 0        | 0                  | 0                         | 1                 |

| 32  | R/<br>W | 0  | 1  | 0    | 0    | 0    | 0  | 0  | 0  | 0                                 | 1                    | 0       | 0          | 0                           | 0                    | 1                         | 0                     | 0    | 0             | 0               | 1        | 0                  | 1                         | 0                 |

| 33  | R/<br>W | 0  | 1  | 0    | 0    | 0    | 0  | 1  | 0  | 0                                 | 1                    | 0       | 1          | 0                           | 1                    | 0                         | 0                     | 0    | 0             | 0               | 1        | 0                  | 1                         | 0                 |

| 34  | R/<br>W | 0  | 1  | 0    | 0    | 0    | 1  | 0  | 1  | 1                                 | 0                    | 0       | 0          | 0                           | 1                    | 1                         | 1                     | 1    | CHDIV<br>_EN  | 0               | 1        | 0                  | 1                         | 0                 |

| 35  | R/<br>W | 0  | 1  | 0    | 0    | 0    | 1  | 1  | 0  | 0                                 | 0                    |         | CHDIV      | /_SEG2                      |                      | CHD<br>IV_S<br>EG3<br>_EN | CHDIV<br>_SEG<br>2_EN | 0    | 0             | 1               | 1        | CHDIV<br>_SEG<br>1 | CHD<br>IV_S<br>EG1<br>_EN | 1                 |

Figure 7-5. Register Table (continued)

|     |         |    |    |      |      |       |    |    |                                            | гıу                                                       | ure 7- | o. Re                                         | giste                      | i iai                      | ole (C | Ontil | nueu        | <u>)                                    </u> |                     |     |       |        |       |             |

|-----|---------|----|----|------|------|-------|----|----|--------------------------------------------|-----------------------------------------------------------|--------|-----------------------------------------------|----------------------------|----------------------------|--------|-------|-------------|----------------------------------------------|---------------------|-----|-------|--------|-------|-------------|

| REG | 23      | 22 | 21 | 20   | 19   | 18    | 17 | 16 | 15                                         | 14                                                        | 13     | 12                                            | 11                         | 10                         | 9      | 8     | 7           | 6                                            | 5                   | 4   | 3     | 2      | 1     | 0           |

|     | R/<br>W |    |    | ADDF | RESS | [6:0] |    |    |                                            |                                                           |        |                                               |                            |                            |        | DAT   | A [15:0]    |                                              |                     |     |       |        |       |             |

| 36  | R/<br>W | 0  | 1  | 0    | 0    | 1     | 0  | 0  | 0                                          | 0                                                         | 0      | 0                                             | CHDI<br>V_DI<br>STB_<br>EN | CHDI<br>V_DIS<br>TA_E<br>N | 0      | 0     | 0           | СН                                           | DIV_SEG_            | SEL |       | CHDIV_ | SEG3  |             |

| 37  | R/<br>W | 0  | 1  | 0    | 0    | 1     | 0  | 1  | 0                                          | 1                                                         | 0      | 0   PLL_N   0   0   0   0   0   0   0   0   0 |                            |                            | 0      | 0     |             |                                              |                     |     |       |        |       |             |

| 38  | R/<br>W | 0  | 1  | 0    | 0    | 1     | 1  | 0  | 0                                          | 0 0 PLL_N 0                                               |        |                                               |                            |                            |        |       |             |                                              |                     |     |       |        |       |             |

| 39  | R/<br>W | 0  | 1  | 0    | 0    | 1     | 1  | 1  | 1                                          | 0                                                         |        |                                               | PFD_                       | DLY                        |        |       | 0           | 0                                            | 0                   | 0   | 0     | 1      | 0     | 0           |

| 40  | R/<br>W | 0  | 1  | 0    | 1    | 0     | 0  | 0  |                                            |                                                           |        |                                               |                            |                            |        | PLL_D | EN[31:16    | 5]                                           |                     |     |       |        | •     | 1           |

| 41  | R/<br>W | 0  | 1  | 0    | 1    | 0     | 0  | 1  |                                            |                                                           |        |                                               |                            |                            |        | PLL_C | DEN[15:0    | ]                                            |                     |     |       |        |       |             |

| 42  | R/<br>W | 0  | 1  | 0    | 1    | 0     | 1  | 0  |                                            |                                                           |        |                                               |                            |                            | М      | ASH_S | SEED[31:    | 16]                                          |                     |     |       |        |       |             |

| 43  | R/<br>W | 0  | 1  | 0    | 1    | 0     | 1  | 1  |                                            | MASH_SEED[15:0]                                           |        |                                               |                            |                            |        |       |             |                                              |                     |     |       |        |       |             |

| 44  | R/<br>W | 0  | 1  | 0    | 1    | 1     | 0  | 0  |                                            | PLL_NUM[31:16]                                            |        |                                               |                            |                            |        |       |             |                                              |                     |     |       |        |       |             |

| 45  | R/<br>W | 0  | 1  | 0    | 1    | 1     | 0  | 1  |                                            |                                                           |        |                                               |                            |                            |        | PLL_N | IUM[15:0    | ]                                            |                     |     |       |        |       |             |