# TPS7H1111-SP および TPS7H1111-SEP 1.5A、超低ノイズ、高 PSRR の耐放射線低ドロップアウト (LDO) リニア・レギュレータ

## 1 特長

- 吸収線量 (TID) 特性評価済み

- 放射線耐性保証 (RHA): 100krad(Si) または 50krad(Si)

- シングル・イベント効果 (SEE) 特性評価済み

- シングル・イベント・ラッチアップ (SEL)、シングル・イベント・バーンアウト (SEB)、シングル・イベント・ゲート・ラップチャ (SEGR) の、最大線エネルギー付与 (LET) = 75 MeV-cm<sup>2</sup>/mg に対する耐性

- シングル・イベント機能割り込み (SEFI) およびシングル・イベント過渡 (SET) の最大 LET = 75MeV-cm<sup>2</sup>/mg に対する耐性

- 超低ノイズ (10Hz~100kHz):

- 1.71 $\mu$ V<sub>RMS</sub> (代表値)

- 高い電源電圧変動除去比 (PSRR) (代表値):

- 1kHz 時 109dB

- 100kHz 時 71dB

- 1MHz 時 66dB

- 0.85V~7V の入力電圧範囲

- 2.2V~14V のバイアス電源による消費電力の最小化

- 出力電圧を最小 0.4V まで調整可能

- 最大 1.5A の出力電流

- ラインおよび負荷に対する優れた出力精度:

- 全温度範囲で -1.3%~+1.2%

- 25°C で -0.7%~+0.9%

- 低ドロップアウト: 215mV (代表値)、1.5A 時

- プログラマブル・ソフト・スタート制御 (SS\_SET)

- オープン・ドレインのパワー・グッド (PG) インジケータ

- 構成可能なパワー・グッド・スレッショルド (FB\_PG)

- 外部補償の STAB ピンを使用した露出制御ループ

- 構成可能な動作による内部電流制限

- 電流共有により最大 2.9A の動作を実現

- 軍事用温度範囲 (-55°C~125°C)

## 2 アプリケーション

- 衛星用電源システム (EPS)

- 高速かつ高精度の回路向けの電源

- データ・コンバータ: ADC と DAC (A/D コンバータと D/A コンバータ)

- VCO (電圧制御発振器)

- PLL (フェーズ・ロック・ループ)

- SerDes (シリアルライザ / デシリアルライザ)

- 画像センサ

- FPGA (フィールド・プログラマブル・ゲート・アレイ) と DSP (デジタル信号プロセッサ) 向けの高精度電源

- スペースに制約のある領域向けの放射線強化された超クリーンなアナログ電源

## 3 概要

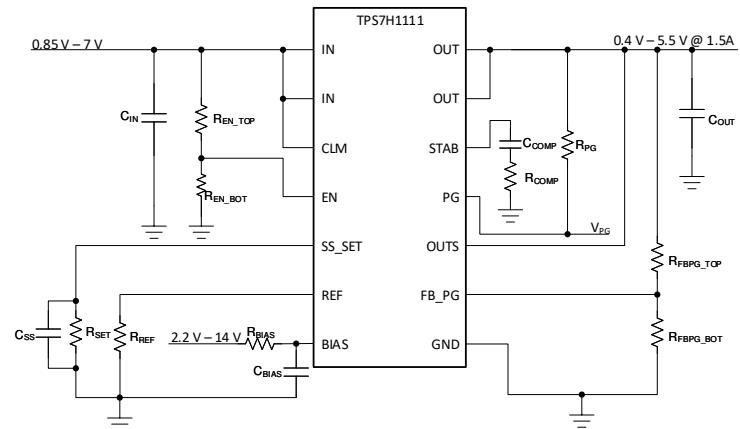

TPS7H1111 は超低ノイズ、高 PSRR、低ドロップアウトのリニア・レギュレータ (LDO) で、宇宙環境の無線周波数 (RF) デバイスへの電力供給用に最適化されています。2.2V~14V のバイアス電源で、0.85V~7V の入力範囲にわたって最大 1.5A の電流を供給できます。

高性能なこのデバイスは、電源で発生する位相ノイズとクロックのジッタを制限できるため、高性能 ADC、DAC、VCO、PLL、SerDes、および衛星内の他の RF 部品への電力供給に最適です。低電圧動作を必要とするデジタル負荷 (FPGA や DSP など) では、非常に優れた精度と過渡性能により、最適なシステム性能が実現します。

QML バリエント 5962R21203 では、SMD (Standard Microcircuit Drawing) を利用できます。-SEP バリエント V62/23602 では、VID (Vendor Item Drawing) を利用できます。

## 製品情報

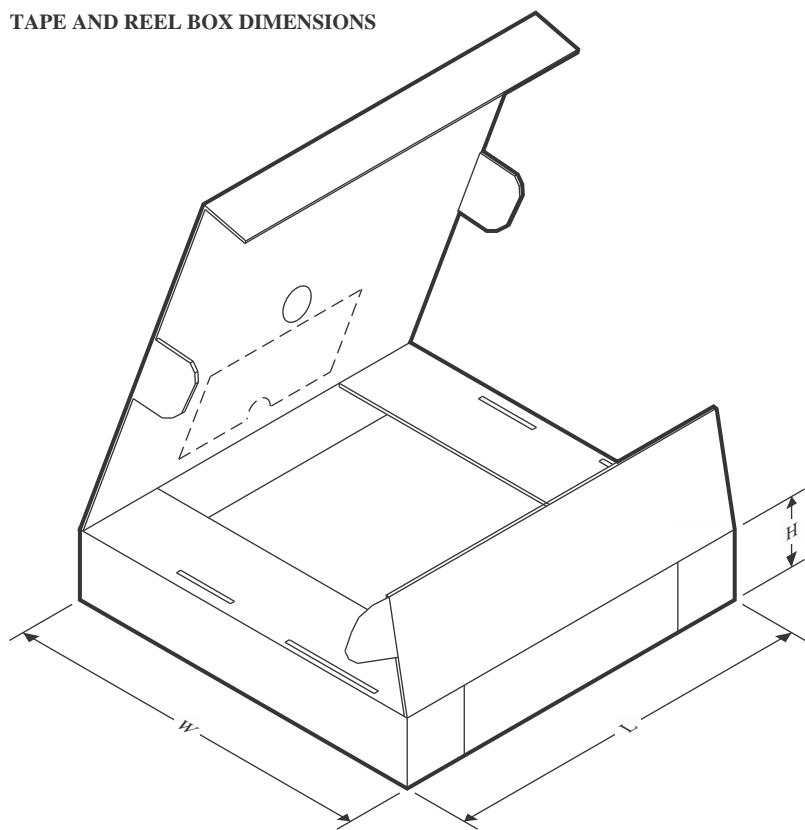

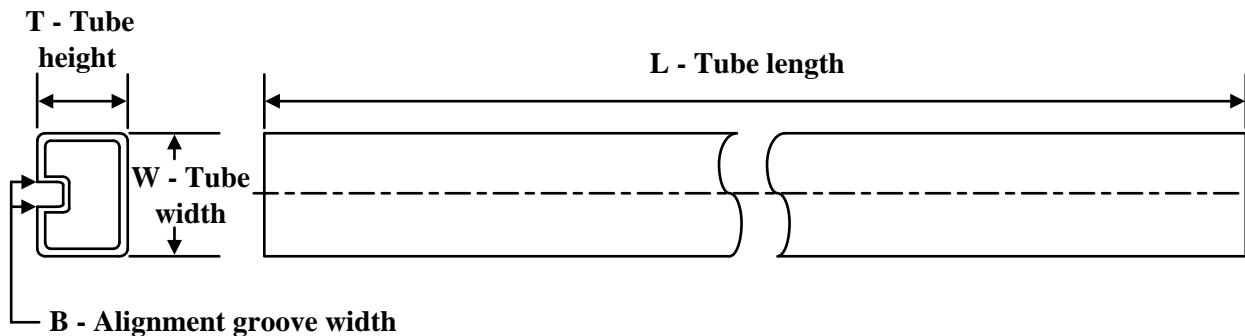

| 部品番号 (1)          | グレード         | パッケージ (2)                                      |

|-------------------|--------------|------------------------------------------------|

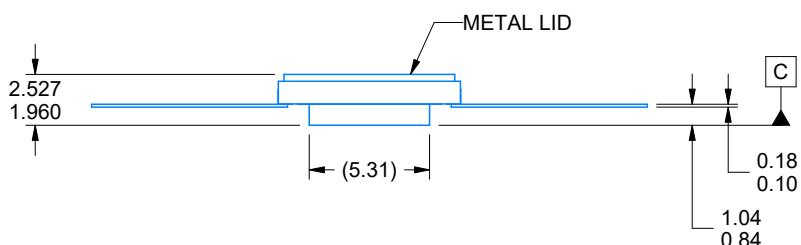

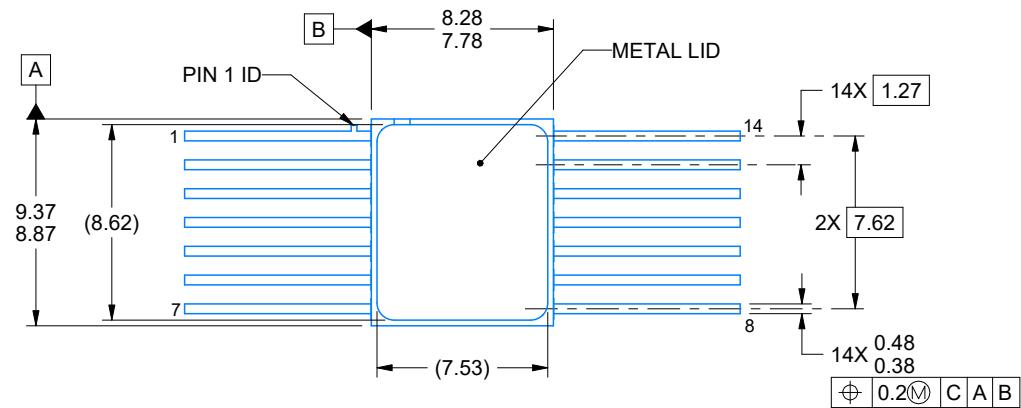

| 5962R2120301VXC   | QMLV-RHA     | 14 ピン セラミック<br>8.03mm × 9.12mm<br>質量 = 1.23g   |

| TPS7H1111HBL/EM   | エンジニアリングサンプル |                                                |

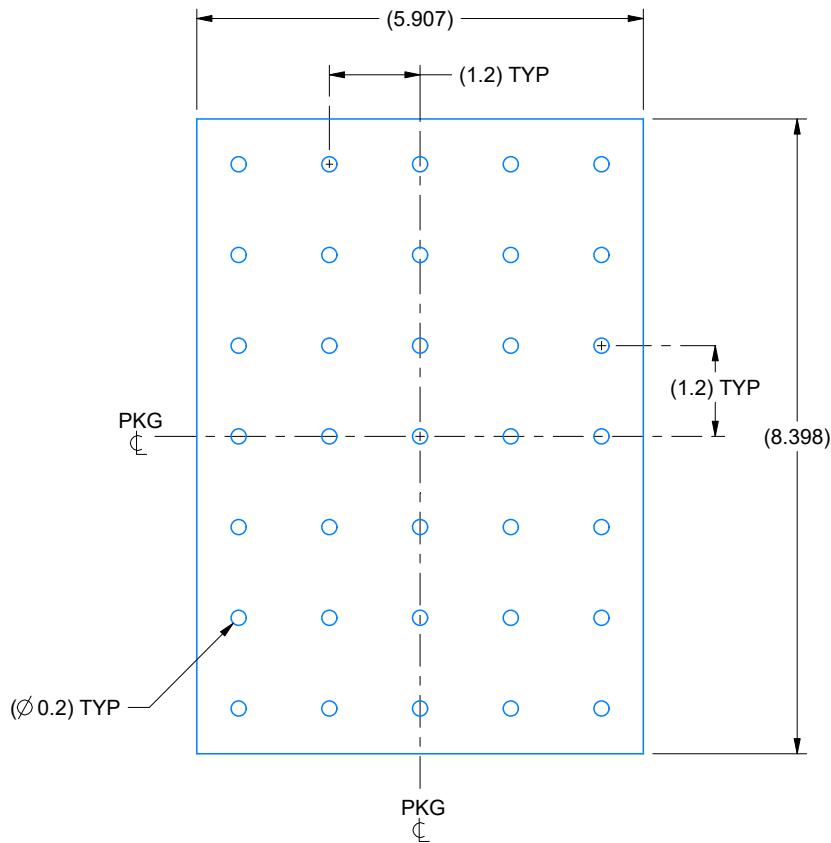

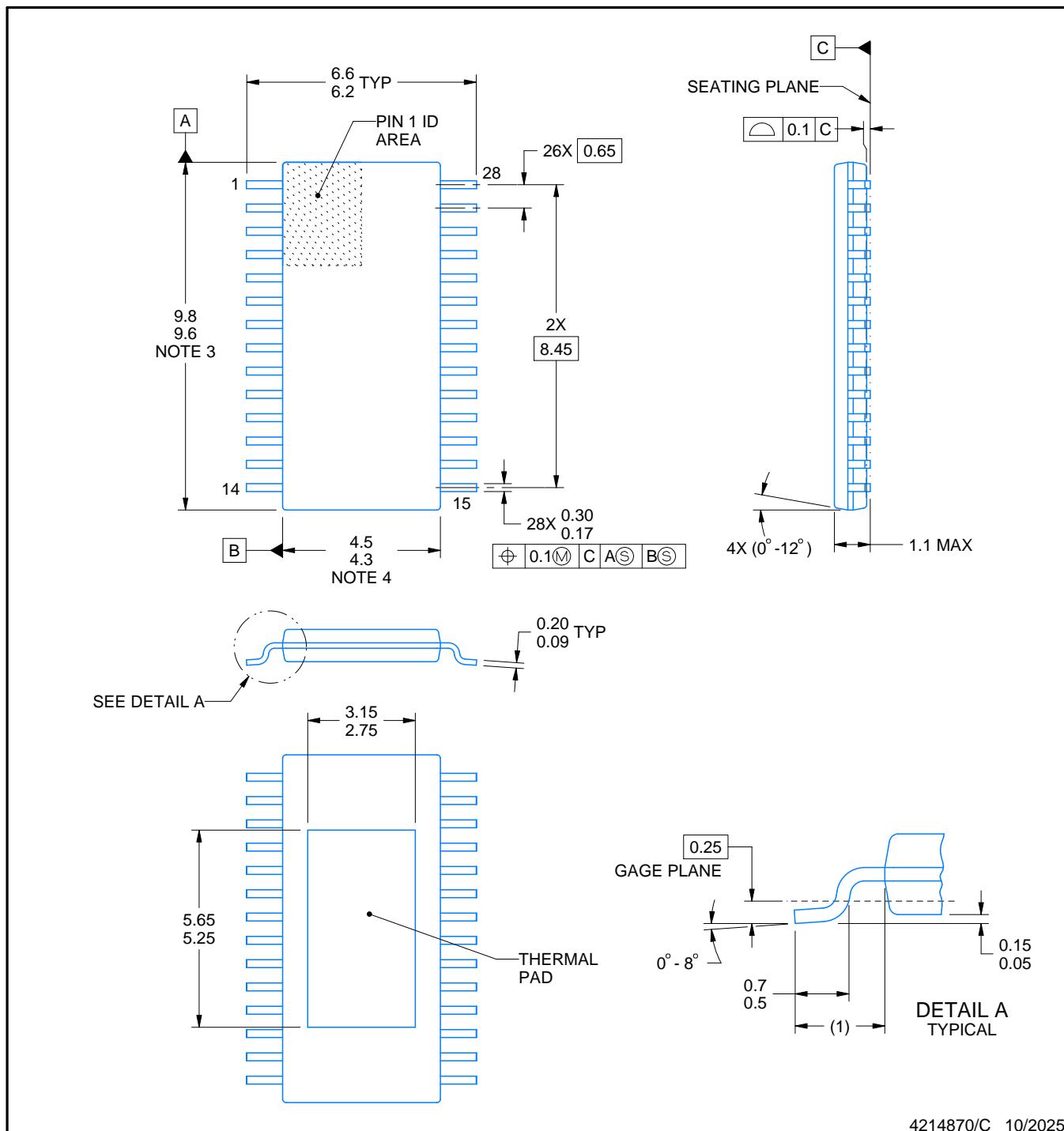

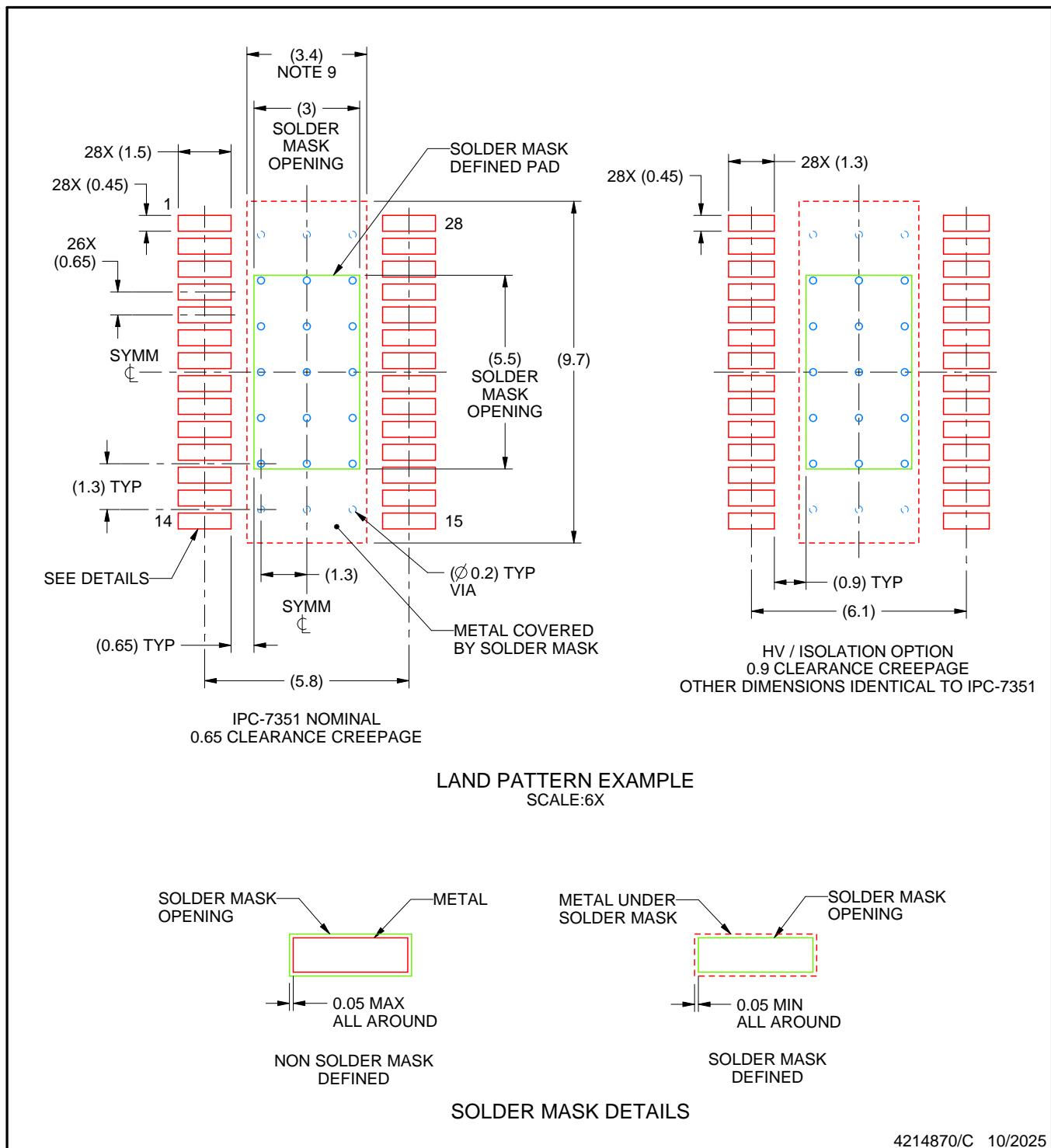

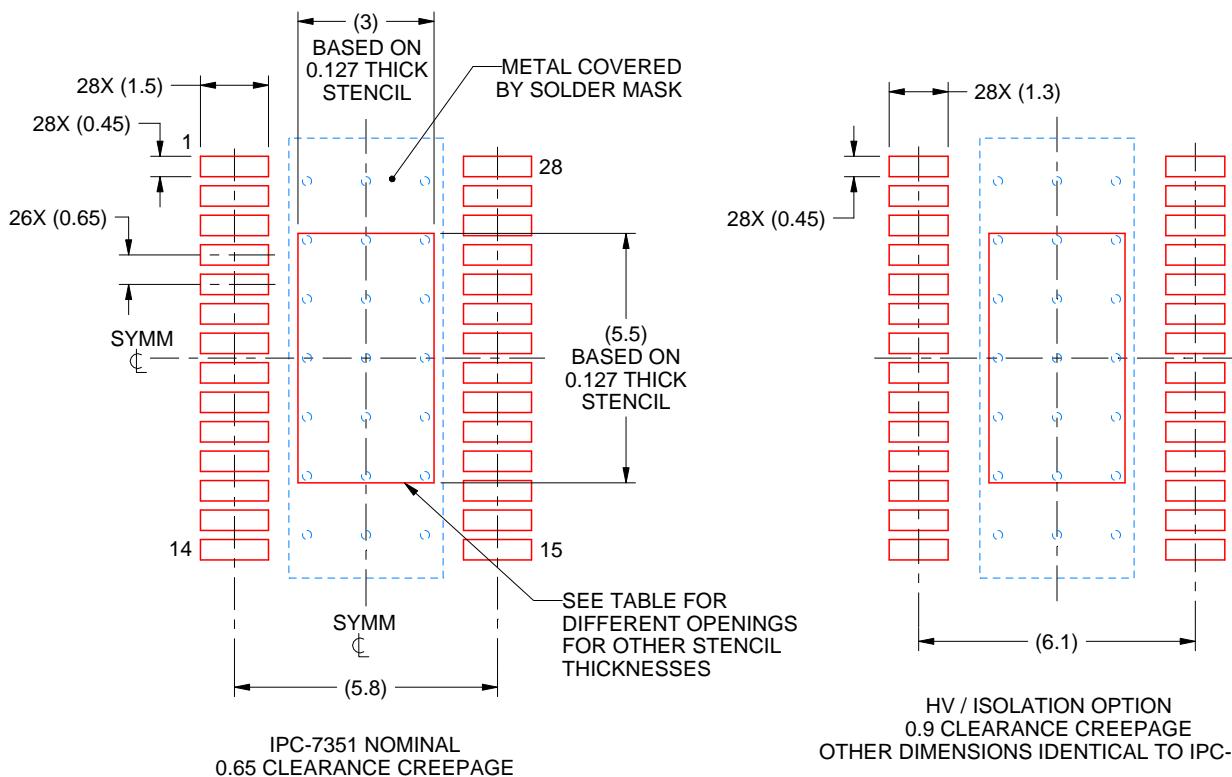

| 5962R2120302PYE   | QMLP-RHA     | 28 ピン プラスチック<br>4.40mm × 9.70mm<br>質量 = 198 mg |

| TPS7H1111MPWPTSEP | SEP          |                                                |

(1) 詳細は、[デバイスオプション表](#)をご覧ください。

(2) 寸法と質量の値は公称値です。

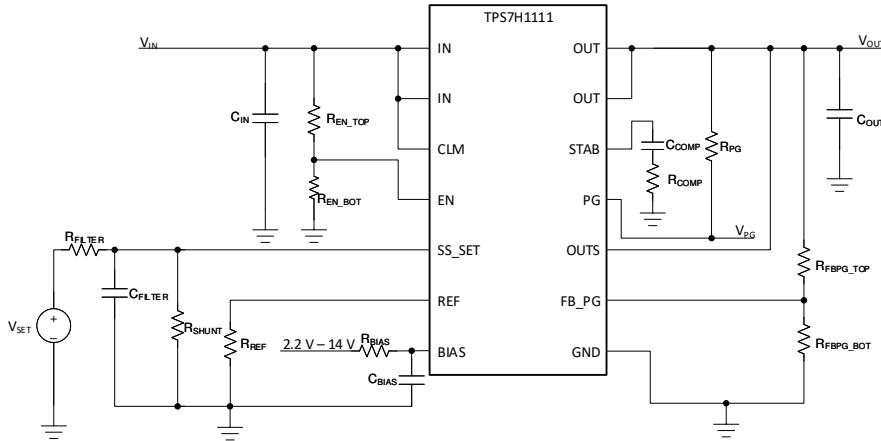

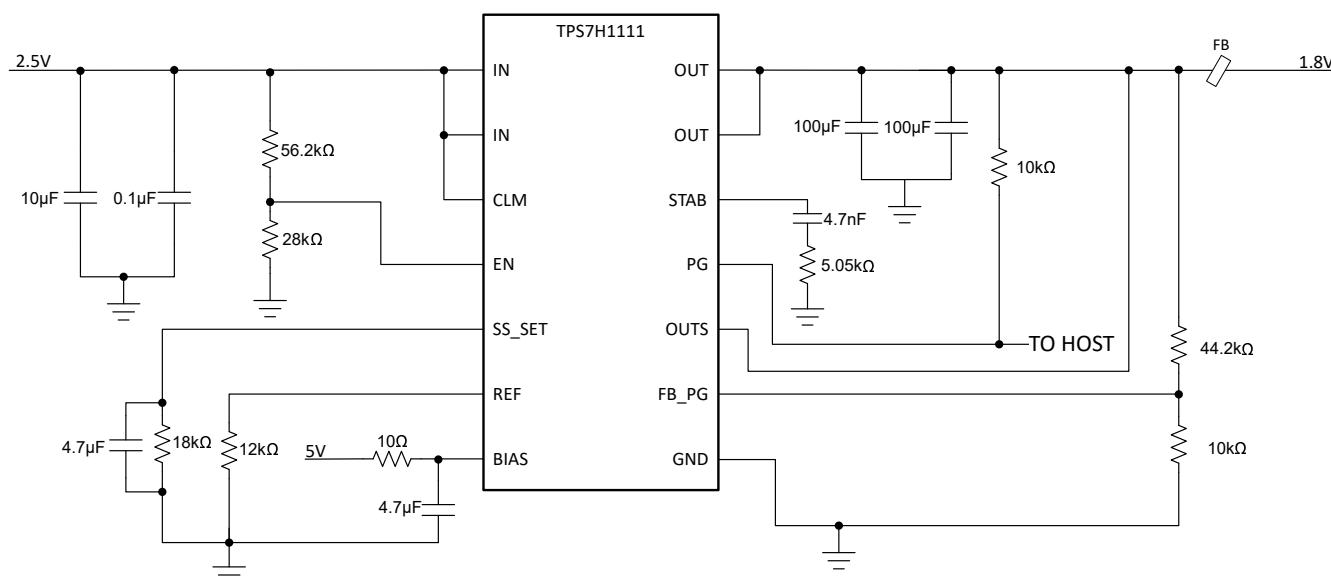

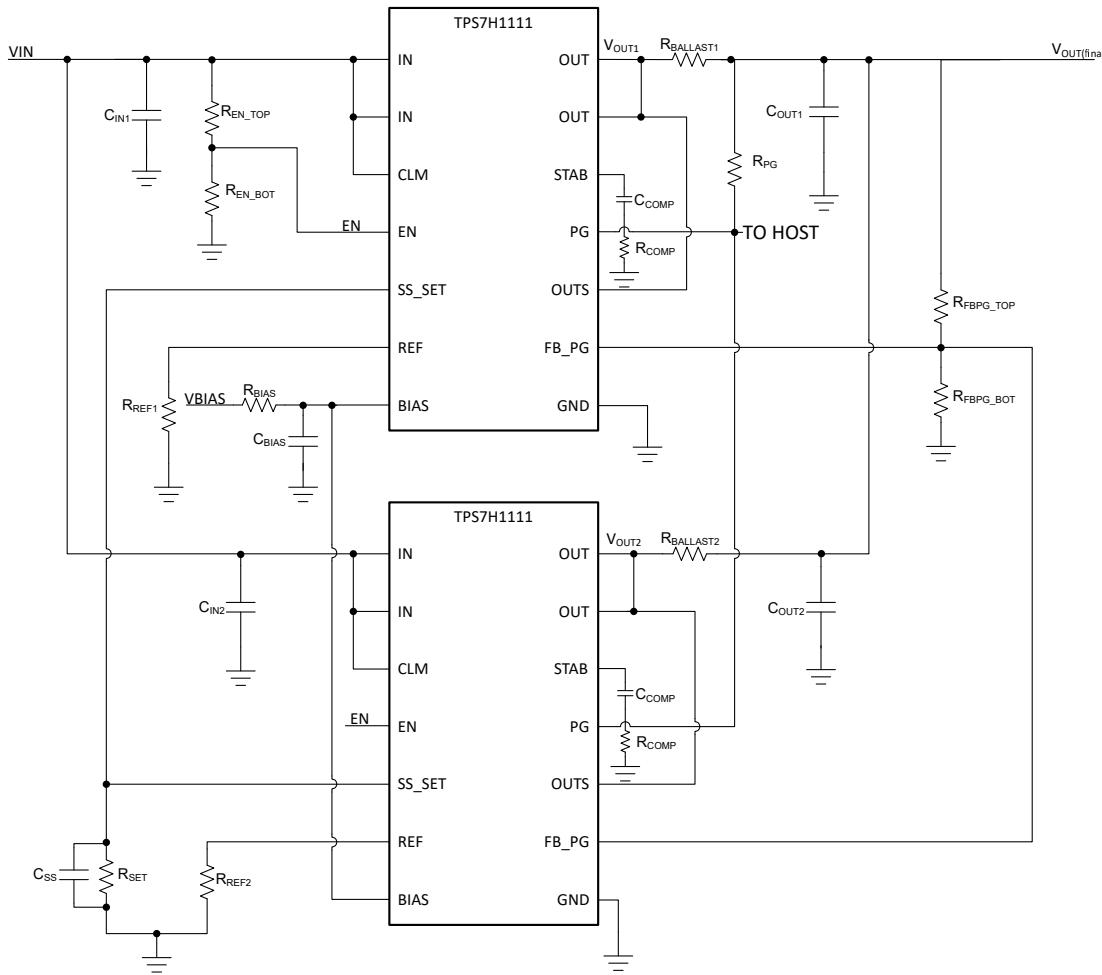

代表的なアプリケーション回路

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|               |    |                         |    |

|---------------|----|-------------------------|----|

| 1 特長          | 1  | 8.4 デバイスの機能モード          | 40 |

| 2 アプリケーション    | 1  | 9 アプリケーションと実装           | 41 |

| 3 概要          | 1  | 9.1 アプリケーション情報          | 41 |

| 4 デバイスのオプション表 | 3  | 9.2 代表的なアプリケーション        | 41 |

| 5 ピン構成および機能   | 4  | 9.3 テストしたコンデンサ          | 48 |

| 6 仕様          | 6  | 9.4 TID の影響             | 48 |

| 6.1 絶対最大定格    | 6  | 9.5 電源に関する推奨事項          | 50 |

| 6.2 ESD 定格    | 6  | 9.6 レイアウト               | 51 |

| 6.3 推奨動作条件    | 7  | 10 デバイスおよびドキュメントのサポート   | 53 |

| 6.4 熱に関する情報   | 7  | 10.1 ドキュメントのサポート        | 53 |

| 6.5 電気的特性     | 8  | 10.2 ドキュメントの更新通知を受け取る方法 | 53 |

| 6.6 品質適合検査    | 11 | 10.3 サポート・リソース          | 53 |

| 6.7 代表的特性     | 12 | 10.4 商標                 | 53 |

| 7 パラメータ測定情報   | 25 | 10.5 静電気放電に関する注意事項      | 53 |

| 8 詳細説明        | 26 | 10.6 用語集                | 53 |

| 8.1 概要        | 26 | 11 改訂履歴                 | 53 |

| 8.2 機能ブロック図   | 26 | 12 メカニカル、パッケージ、および注文情報  | 55 |

| 8.3 機能説明      | 27 |                         |    |

## 4 デバイスのオプション表

| ジェネリック型番      | 放射線定格 <sup>(1)</sup>                                             | グレード <sup>(2)</sup>    | パッケージ                                        | 発注用製品型番           |

|---------------|------------------------------------------------------------------|------------------------|----------------------------------------------|-------------------|

| TPS7H1111-SP  | 100krad(Si) RLAT の TID、<br>75MeV-cm <sup>2</sup> /mg まで DSEE フリー | QMLV-RHA               | 14 ピン CFP HBL                                | 5962R2120301VXC   |

|               |                                                                  | QMLP-RHA               | 28 ピン HTSSOP PWP                             | 5962R2120302PYE   |

|               |                                                                  | なし                     | エンジニアリング モデル <sup>(3)</sup><br>14 ピン CFP HBL | TPS7H1111HBL/EM   |

| TPS7H1111-SEP | 50krad(Si) RLAT の TID、<br>43MeV-cm <sup>2</sup> /mg まで DSEE フリー  | 宇宙向けに強化されたプラスチック       | 28 ピン HTSSOP PWP                             | TPS7H1111MPWPTSEP |

| SN0014HBL     | 該当なし                                                             | メカニカル「ダミー」パッケージ (ダイなし) | 14 ピン CFP HBL                                | SN0014HBL         |

- (1) TID は総電離線量、DSEE は破壊的シングル イベント効果です。詳細については、関連する TID レポートおよび各製品の SEE レポートを参照してください。

- (2) 部品のグレードについて詳細は、[SLYB235](#) をご覧ください。

- (3) これらのユニットは、技術的な評価のみを目的としています。非準拠のフローで処理されています (バーンインがない、25°Cでのテストしか行わないなど)。これらのユニットは、認定、量産、放射線テスト、航空での使用には適していません。部品は、温度または動作寿命全体にわたる性能を保証されていません。

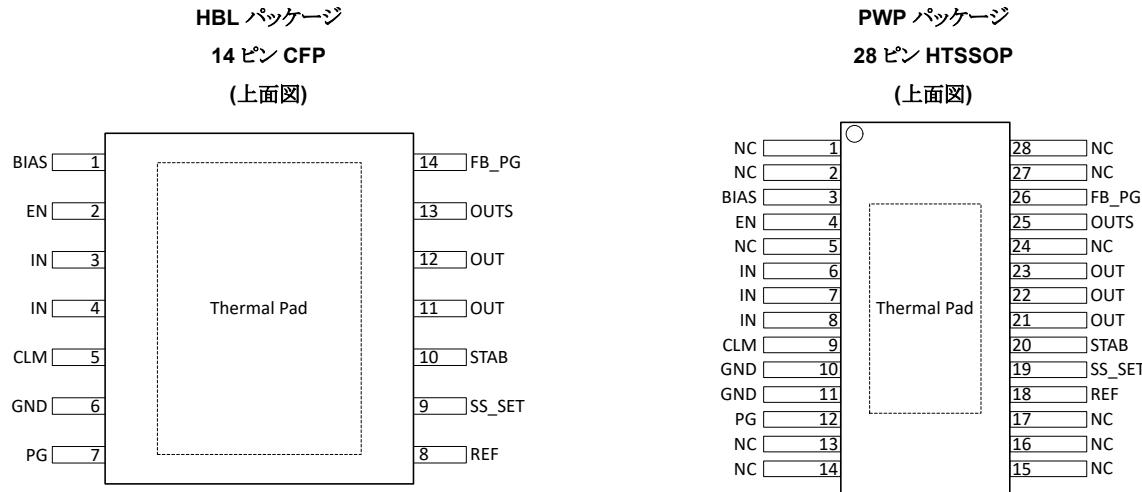

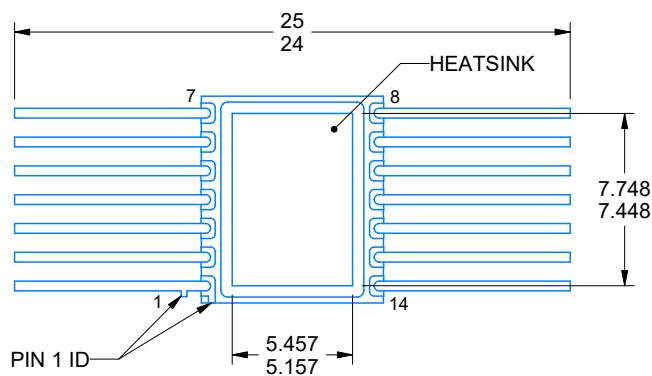

## 5 ピン構成および機能

表 5-1. ピンの機能

| 名称     | ピン          |             | I/O <sup>(1)</sup> | 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|-------------|-------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | HBL (14) 番号 | PWP (28) 番号 |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BIAS   | 1           | 3           | I                  | バイアス電源。最大出力電流をサポートするには、ヘッドルーム電圧が 1.6V 未満 ( $V_{headroom} = V_{IN} - V_{OUT} < 1.6V$ ) の場合、別のバイアス電源が必要です。最大出力電流をサポートするには、個別のバイアス電源を $V_{OUT}$ より 1.6V 以上高い電圧に設定します。12V バイアス電源でこれらの条件が満たされます (通常は 5V 電源でも十分です)。 $V_{BIAS}$ と $V_{IN}$ の間にシーケンシング要件はありません。 $V_{BIAS}$ のノイズを制限するため、 $V_{BIAS}$ が非常にクリーンな電源でない場合は、RC フィルタ (通常は $10\Omega$ および $4.7\mu F$ ) を推奨します。個別のバイアス電源を使用しない場合は、BIAS を $V_{IN}$ に接続します ( $V_{IN}$ レールを RC フィルタを介して BIAS ピンに接続することも推奨します)。 |

| EN     | 2           | 4           | I                  | イネーブル。このピンを High に駆動するとデバイスがイネーブルになり、Low に駆動するとデバイスがディセーブルになります。イネーブル機能が不要な場合は、このピンを IN に接続します。このピンをフローティングにしないでください。                                                                                                                                                                                                                                                                                                                                     |

| IN     | 3, 4        | 6, 7, 8     | I                  | 入力電力。このピンの近くに入力コンデンサ (公称 $10\mu F$ ) を配置することを推奨します。                                                                                                                                                                                                                                                                                                                                                                                                       |

| CLM    | 5           | 9           | I                  | 電流制限モード。ブリックウォール電流制限モードの場合は、CLM を $V_{IN}$ に接続します (電流制限に達すると、障害が解消されるまで、 $V_{OUT}$ がレギュレートされて一定の出力電流が維持されます)。ターンオフ電流制限モードの場合は、CLM を GND に接続します (電流制限に達すると、EN がトグルされるまで、 $V_{OUT}$ のレギュレーションが停止します)。デバイスがイネーブルのときにこのピンの値を変更しないでください。また、このピンはフローティングにしないでください。                                                                                                                                                                                              |

| GND    | 6           | 10, 11      | —                  | グランド。                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PG     | 7           | 12          | O                  | パワー グッド インジケータ。これはオーブン ドレイン ピンです。プルアップ抵抗を使用して、このピンを $V_{OUT}$ または必要なロジック レベルにプルアップします。PG を使用しない場合はグランドにプルダウンすることをお勧めしますが、フローティングのままでもかまいません。                                                                                                                                                                                                                                                                                                              |

| REF    | 8           | 18          | I/O                | リファレンス ピン。REF は公称 $1.2V$ を出力します。REF と GND の間に $12.0k\Omega$ の高精度外付け抵抗を配置して、内部 $100\mu A$ 電流源を設定します。                                                                                                                                                                                                                                                                                                                                                       |

| SS_SET | 9           | 19          | I/O                | ソフト スタートおよび電圧設定ピン。外付けコンデンサ (公称 $4.7\mu F$ セラミック) を使用して、スタートアップ時の出力電圧のランプ レートを遅くし、内部デバイス ノイズをフィルタリングします。コンデンサの値が $4.7\mu F$ 未満の場合、出力ノイズはわずかに大きくなります。適切なソフト スタート時間を実現するため、内部高速スタート回路があります。また、SS_SET と GND の間の抵抗によって出力電圧が設定されます。公称動作中はこのピンに $100\mu A$ が outputされ、SS_SET と GND の間の抵抗によって出力電圧が設定されます。                                                                                                                                                         |

**表 5-1. ピンの機能 (続き)**

| ピン       |                                         |             | I/O <sup>(1)</sup> | 概要                                                                                                                                                                                                                                                                                                        |

|----------|-----------------------------------------|-------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | HBL (14) 番号                             | PWP (28) 番号 |                    |                                                                                                                                                                                                                                                                                                           |

| STAB     | 10                                      | 20          | I/O                | 安定性ピン。これは、内部 OTA (オペレーションナルトランスコンダクタンス) 誤差アンプからの出力で、制御ループの測定または最適化に役立ちます。直列接続した $4.7nF$ のコンデンサ ( $C_{COMP}$ ) と $5k\Omega$ の抵抗 ( $R_{COMP}$ ) を使用して、デバイスを補償します。各種の補償オプションについては、 <a href="#">セクション 8.3.8.2</a> を参照してください。 $V_{BIAS}$ または $7.5V$ の低いほうに耐えることができる C0G (NP0) タイプのコンデンサ (25V 定格のコンデンサ) を推奨します。 |

| OUT      | 11, 12                                  | 21, 22, 23  | O                  | 出力電源ピン。レギュレートされた出力電圧です。 $220\mu F$ のタンタルまたはタンタル ポリマー コンデンサを 1 つ、あるいは 2 つの $100\mu F$ タンタルまたはタンタル ポリマー コンデンサを使用することをお勧めします。詳細については、 <a href="#">セクション 8.3.8.1</a> を参照してください。                                                                                                                               |

| OUTS     | 13                                      | 25          | I                  | 出力検出センスピン。このピンを使用して、レギュレーションの出力電圧を検知します。OUTS を必要なレギュレーション点 (リモート センス) で OUT ピンに接続します。                                                                                                                                                                                                                     |

| FB_PG    | 14                                      | 26          | I                  | フィードバック ピンとパワー グッド ピン。 <b>FB_PG</b> ピンで、構成可能なパワー グッド スレッショルドを設定します。これは、出力電圧を分圧抵抗を介してこのピンに供給することで実現されます (標準スレッショルドは $300mV$ )。スレッショルドに達すると、PG がアサートされます。また、このピンのスレッショルドに達すると、スタートアップが終了し、内部高速スタート回路がディセーブルされます。このピンを OUT に直接接続すると、高速スタート動作は停止し、 $V_{OUT}$ が $300mV$ (標準値) に達したときにすぐに PG がアサートされます。         |

| NC       | 1, 2, 5, 13, 14, 15, 16, 17, 24, 27, 28 |             | —                  | 接続なし。このピンは内部接続されていません。電荷の蓄積を防ぐため、これらのピンを GND に接続することを推奨しますが、これらのピンはオープンのままにすることも、GND と $V_{BIAS}$ の範囲の任意の電圧に接続することもできます。                                                                                                                                                                                  |

| サーマル パッド |                                         |             | —                  | セラミック パッケージのサーマル パッドは、導電性のバスを経由してダイの裏面、および GND ピンに内部接続されています。効果的な放熱のため、この金属サーマル パッドは大きなグランド プレーンに接続することを推奨します。プラスチック パッケージのサーマル パッドは、導電性のバスを経由してダイの裏面に接続されており、グランドには内部接続されていません。効果的な放熱のため、および適切な動作のためにダイの裏面を GND に接続するため、サーマル パッドは大きなグランド プレーンに接続します。                                                     |

| 金属製ふた    | ふた                                      | 該当なし        | —                  | このふたは、シール リングを介してサーマル パッドと GND に内部接続されています。                                                                                                                                                                                                                                                               |

(1) I = 入力、O = 出力、I/O = 入力または出力、— = その他

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|       |                          |  | 最小値    | 最大値  | 単位 |

|-------|--------------------------|--|--------|------|----|

| 入力電圧  | IN                       |  | -0.3   | 7.5  | V  |

|       | BIAS                     |  | -0.3   | 16   |    |

|       | EN, PG, FB_PG, OUTS, CLM |  | -0.3   | 7.5  |    |

| 出力電圧  | OUT                      |  | -0.3   | 7.5  | V  |

|       | SS_SET, REF, STAB        |  | -0.3   | 7.5  |    |

| 入力電流  | PG                       |  | -0.001 | 0.01 | A  |

| 出力電流  | OUT                      |  | -2     | 2.25 | A  |

| 接合部温度 | T <sub>J</sub>           |  | -55    | 150  | °C |

| 保管温度  | T <sub>stg</sub>         |  | -65    | 150  | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの恒久的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|                    |       |                                                                  | 値     | 単位 |

|--------------------|-------|------------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | ±2000 | V  |

|                    |       | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | ±1000 |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

## 6.3 推奨動作条件

動作温度範囲全体、 $T_J = -55^{\circ}\text{C} \sim 125^{\circ}\text{C}$  (特に記述のない限り)

|                         |                       | 最小値             | 公称値                             | 最大値   | 単位                 |

|-------------------------|-----------------------|-----------------|---------------------------------|-------|--------------------|

| 入力電圧                    | IN                    | 0.85            |                                 | 7     | V                  |

|                         | BIAS <sup>(1)</sup>   | $V_{\text{IN}}$ | $V_{\text{OUT}} + 1.6\text{V}$  |       |                    |

|                         |                       | 2.2             |                                 | 14    |                    |

|                         | PG                    | 0               |                                 | 7     |                    |

|                         | EN                    | 0               |                                 | 7     |                    |

|                         | FB_PG                 | 0               |                                 | 6     |                    |

| 出力電圧                    | CLM                   | 0               | $V_{\text{IN}}$                 |       | V                  |

|                         | OUT <sup>(2)</sup>    |                 | $V_{\text{IN}} - V_{\text{DO}}$ |       |                    |

|                         |                       | 0.4             |                                 | 5.5   |                    |

|                         | SS_SET <sup>(2)</sup> |                 | $V_{\text{IN}} - V_{\text{DO}}$ |       |                    |

| 入力電流                    | PG                    | 0               |                                 | 0.002 | A                  |

| 出力電流                    | OUT                   | 0               |                                 | 1.5   | A                  |

| 出力パルク容量 <sup>(3)</sup>  | $C_{\text{OUT}}$      | 132             | 200                             | 308   | $\mu\text{F}$      |

|                         | ESR                   | 7               |                                 | 40    | $\text{m}\Omega$   |

|                         | ESL                   | 0.8             |                                 | 2.4   | nH                 |

| リファレンス構成                | $R_{\text{REF}}$      | 11              | 12                              | 13    | $\text{k}\Omega$   |

| EN トグル時間 <sup>(4)</sup> | $t_{\text{EN\_LOW}}$  | 20              |                                 |       | $\mu\text{s}$      |

| 接合部温度                   | $T_J$                 | -55             |                                 | 125   | $^{\circ}\text{C}$ |

- (1) BIAS には、 $V_{\text{IN}}$  と  $2.2\text{V}$  の 2 つの最小値があります。BIAS は、これら 2 つの値のうち大きい方以上に設定する必要があります。BIAS の最大値は常に  $14\text{V}$  です。最大性能を得るには、 $V_{\text{BIAS}} \geq V_{\text{OUT}} + 1.6\text{V}$  を設定します。詳細については、「[バイアス電源](#)」を参照してください。

- (2) OUT と SS\_SET には、 $(V_{\text{IN}} - V_{\text{DO}})$  と  $5.5\text{V}$  の 2 つの最大値があります。OUT と SS\_SET は、これら 2 つの値のうち小さい方以下に設定する必要があります。OUT および SS\_SET の最小値は常に  $0.4\text{V}$  です。

- (3) これらは、パルク容量のデフォルトで許容される出力容量値、等価直列抵抗 (ESR) 値、等価直列インダクタンス (ESL) 値です。STAB ピンを使用した外部補償で制御ループを変更するなど、他の値も許容される場合があります。これらの要件を満たすために、通常はタンタルまたはタンタルポリマー コンデンサが使用されます。セラミック デカップリング コンデンサを追加する必要はありませんが、負荷ポイント付近に ESL の小さい  $0.1\mu\text{F}$  セラミック コンデンサを 1 つ使用することもできます。TPS7H1111 LDO は広い帯域幅にわたって高 PSRR と低ノイズを実現するため、追加の大型セラミック コンデンサは必要ありません。そのため、TPS7H1111 は、大型のセラミック コンデンサをサポートするようには設計されていません。詳細については、「[出力容量](#)」セクションを参照してください。

- (4)  $t_{\text{EN\_LOW}}$  は、デバイスがリセットを検出するために、EN ピンを再び High に駆動する前に、EN ピンを Low に駆動する必要がある時間です。これは通常、ターンオフ電流制限モードを終了しようとする場合にのみ適用されます。

## 6.4 热に関する情報

| 热評価基準 <sup>(1)</sup>        |                     | TPS7H1111-SP | TPS7H1111-SEP | TPS7H1111-SP | 単位                   |

|-----------------------------|---------------------|--------------|---------------|--------------|----------------------|

|                             |                     | CFP HBL      | PWP (HTSSOP)  | PWP (HTSSOP) |                      |

|                             |                     | 14 ピン        | 28 ピン         | 28 ピン        |                      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗        | 25.1         | 24.7          | 24.4         | $^{\circ}\text{C/W}$ |

| $R_{\theta JC(\text{top})}$ | 接合部からケース (上面) への熱抵抗 | 6.3          | 15.6          | 15.8         | $^{\circ}\text{C/W}$ |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗        | 9.3          | 6.6           | 6.4          | $^{\circ}\text{C/W}$ |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ    | 1.4          | 0.2           | 0.2          | $^{\circ}\text{C/W}$ |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ    | 9.1          | 6.6           | 6.4          | $^{\circ}\text{C/W}$ |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース (底面) への熱抵抗 | 0.5          | 1.0           | 0.7          | $^{\circ}\text{C/W}$ |

- (1) 従来および最新の熱評価基準の詳細については、『[半導体および IC パッケージの熱評価基準](#)』アプリケーション レポートを参照してください。

## 6.5 電気的特性

$0.85V \leq V_{IN} \leq 7V$ ,  $V_{BIAS} \geq V_{OUT} + 1.6V$  ( $V_{IN} \leq V_{BIAS} \leq 14V$  &  $V_{BIAS} \geq 2.2V$ ),  $V_{OUT}$  (ターゲット)  $\leq V_{IN} - 1.6V$ ,  $I_{OUT} = 1mA$ ,  $C_{OUT} = 220\mu F$ <sup>(1)</sup>,  $R_{REF} = 12.0k\Omega$ , 動作温度範囲全体 ( $T_A = -55^{\circ}C \sim 125^{\circ}C$ ), 特に記述のない限り, 標準値は  $T_A = 25^{\circ}C$ での値 (QML RHA および SEP デバイスにサブグループ番号が存在する場合の  $T_A = 25^{\circ}C$ での RLAT を含む)<sup>(2)</sup>

| パラメータ            |                                            | テスト条件                                                                                                      | サブグループ <sup>(3)</sup>                      | 最小値     | 標準値   | 最大値   | 単位      |

|------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------|-------|-------|---------|

| <b>電源と電流</b>     |                                            |                                                                                                            |                                            |         |       |       |         |

| $V_{DO}$         | $V_{BIAS} \geq V_{OUT} + 1.6V$ でのドロップアウト電圧 | $0.85V \leq V_{IN} \leq 7V$ , $V_{OUT} = 98.5\% \times V_{OUT(NOM)}$                                       | $I_{OUT} = 0.1A$                           | 1, 2, 3 | 17    | 40    | mV      |

|                  |                                            |                                                                                                            | $I_{OUT} = 0.5A$                           | 1, 2, 3 | 75    | 150   |         |

|                  |                                            |                                                                                                            | $I_{OUT} = 1A$                             | 1, 2, 3 | 110   | 280   |         |

|                  |                                            |                                                                                                            | $I_{OUT} = 1.5A$                           | 1, 2, 3 | 215   | 430   |         |

| $V_{DO}$         | $V_{BIAS} = V_{IN}$ でのドロップアウト電圧            | $2.2V \leq V_{IN} \leq 7V$ , $V_{OUT} = 98.5\% \times V_{OUT(NOM)}$                                        | $I_{OUT} = 0.1A$                           | 1, 2, 3 | 785   | 1100  | mV      |

|                  |                                            |                                                                                                            | $I_{OUT} = 0.5A$                           | 1, 2, 3 | 908   | 1150  |         |

|                  |                                            |                                                                                                            | $I_{OUT} = 1A$                             | 1, 2, 3 | 1063  | 1250  |         |

|                  |                                            |                                                                                                            | $I_{OUT} = 1.5A$                           | 1, 2, 3 | 1168  | 1400  |         |

| $I_{LIM}$        | 出力電流制限                                     | $2.5V \leq V_{IN} \leq 7V$ , $V_{OUT} = 0.5V$ , $V_{CLM} = V_{IN}$                                         | $T_A = -55^{\circ}C$                       | 3       | 1.8   | 1.95  | 2.1     |

|                  |                                            |                                                                                                            | $T_A = 25^{\circ}C$                        | 1       | 1.75  | 1.85  | 2       |

|                  |                                            |                                                                                                            | $T_A = 125^{\circ}C$                       | 2       | 1.7   | 1.8   | 1.95    |

| $I_{CLM(LKG)}$   | CLM の入力リーキ電流                               | $V_{CLM} = 7V$                                                                                             | 1, 2, 3                                    |         | 5     | 150   | nA      |

| $I_{Q\_IN}$      | 静止時電流                                      | $V_{EN} = 7V$ , $I_{OUT} = 0A$                                                                             | 1, 2, 3                                    |         | 19    | 27    | mA      |

| $I_{Q\_BIAS}$    | 出力負荷なしでのバイアス電流                             | $V_{EN} = 7V$ , $I_{OUT} = 0A$                                                                             | 1, 2, 3                                    |         | 16    | 25    |         |

| $I_{IN\_GND}$    | 全出力負荷での $I_{IN} - I_{OUT}$                 | $V_{EN} = 7V$ , $I_{OUT} = 1.5A$                                                                           | 1, 2, 3                                    |         | 20    | 27    | mA      |

| $I_{BIAS}$       | 全出力負荷でのバイアス電流                              | $V_{EN} = 7V$ , $I_{OUT} = 1.5A$                                                                           | 1, 2, 3                                    |         | 17    | 25    |         |

| $I_{SHDN}$       | シャットダウン電流                                  | $V_{EN} = 0V$ , $I_{OUT} = 0A$ , $V_{OUT} = 0V$                                                            | 1, 2, 3                                    |         | 20    | 350   | $\mu A$ |

| $I_{SHDN\_BIAS}$ | シャットダウンバイアス電流                              | $V_{EN} = 0V$ , $I_{OUT} = 0A$ , $V_{OUT} = 0V$                                                            | 1, 2, 3                                    |         | 550   | 1000  |         |

| <b>精度</b>        |                                            |                                                                                                            |                                            |         |       |       |         |

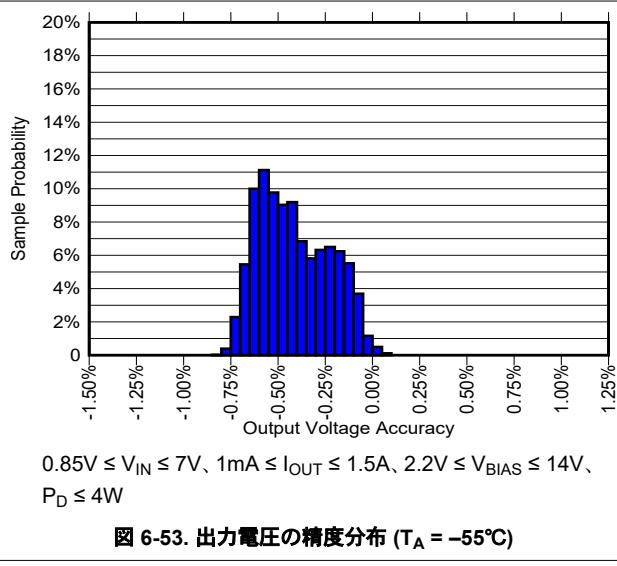

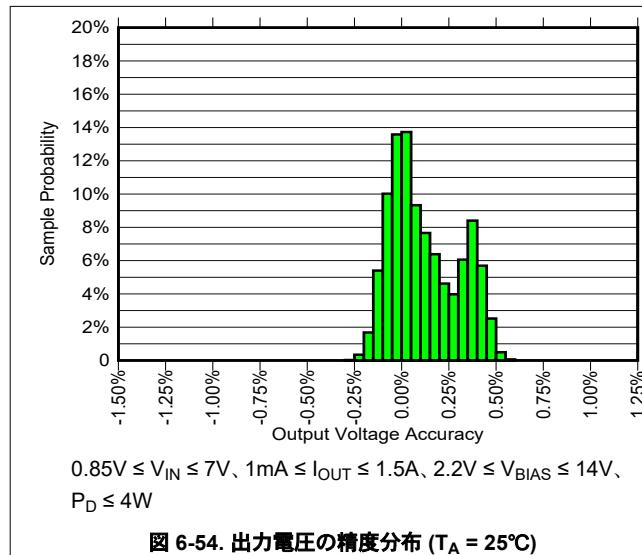

| $V_{ACC}$        | 出力電圧精度                                     | $1mA \leq I_{OUT} \leq 1.5A$ , $2.2V \leq V_{BIAS} \leq 14V$ <sup>(4)</sup> , $P_D \leq 4W$ <sup>(5)</sup> | $-55^{\circ}C \leq T_A \leq 125^{\circ}C$  | 1, 2, 3 | -1.3% | 1.2%  | mV      |

|                  |                                            |                                                                                                            | $T_A = -55^{\circ}C$                       | 3       | -1.3% | 0.5%  |         |

|                  |                                            |                                                                                                            | $T_A = 25^{\circ}C$                        | 1       | -0.7% | 0.9%  |         |

|                  |                                            |                                                                                                            | $T_A = 25^{\circ}C$ , TID 後 <sup>(6)</sup> | 1       | -0.7% | 1.1%  |         |

|                  |                                            |                                                                                                            | $T_A = 125^{\circ}C$                       | 2       | -0.7% | 1.2%  |         |

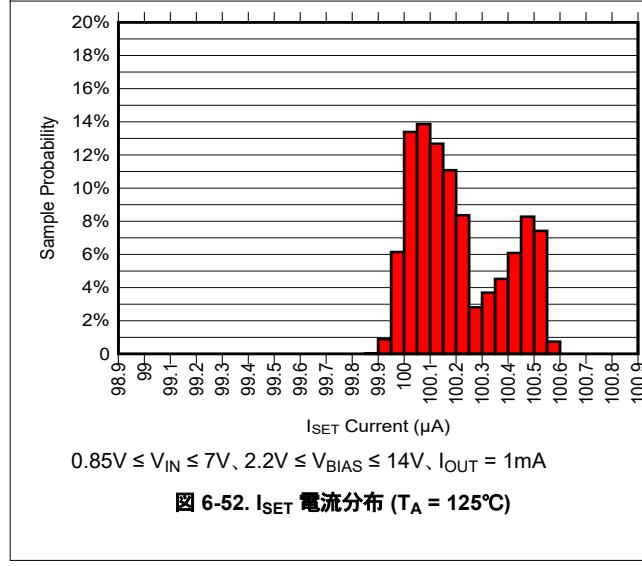

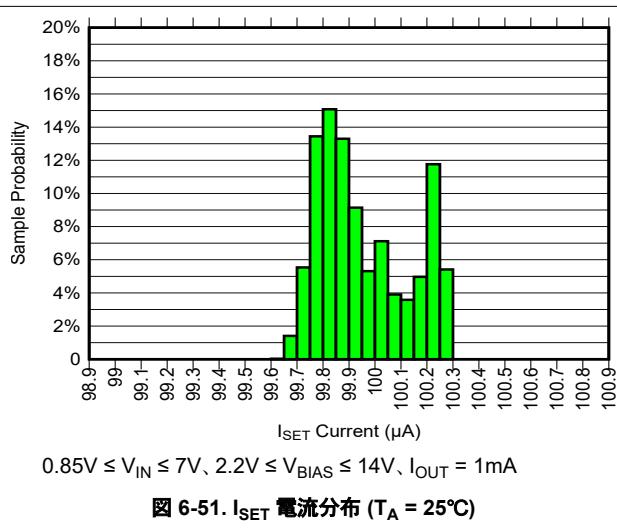

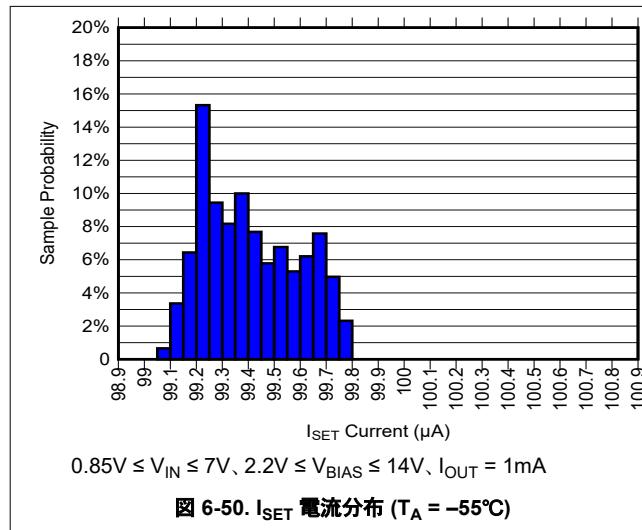

| $I_{SET}$        | $V_{OUT}$ を設定する SS_SET ピンの電流               | $-55^{\circ}C \leq T_A \leq 125^{\circ}C$                                                                  | 1, 2, 3                                    | 98.8    | 99.9  | 101   | $\mu A$ |

|                  |                                            | $T_A = -55^{\circ}C$                                                                                       | 3                                          | 98.8    | 99.4  | 100.3 |         |

|                  |                                            | $T_A = 25^{\circ}C$                                                                                        | 1                                          | 99.0    | 100   | 100.9 |         |

|                  |                                            | $T_A = 125^{\circ}C$                                                                                       | 2                                          | 99.2    | 100.2 | 101   |         |

| $V_{OS}$         | 出力オフセット電圧 ( $V_{OUT} - V_{SS\_SET}$ )      | $-55^{\circ}C \leq T_A \leq 125^{\circ}C$                                                                  | 1, 2, 3                                    | -2      | 0.78  | mV    |         |

|                  |                                            | $T_A = -55^{\circ}C$                                                                                       | 3                                          | -1.33   | -0.2  | 0.78  |         |

|                  |                                            | $T_A = 25^{\circ}C$                                                                                        | 1                                          | -1.45   | -0.25 | 0.76  |         |

|                  |                                            | $T_A = 25^{\circ}C$ , TID 後 <sup>(6)</sup>                                                                 | 1                                          | -1.45   |       | 1.5   |         |

|                  |                                            | $T_A = 125^{\circ}C$                                                                                       | 2                                          | -2      | -0.5  | 0.7   |         |

## 6.5 電気的特性 (続き)

$0.85V \leq V_{IN} \leq 7V$ 、 $V_{BIAS} \geq V_{OUT} + 1.6V$  ( $V_{IN} \leq V_{BIAS} \leq 14V$  &  $V_{BIAS} \geq 2.2V$ )、 $V_{OUT}$  (ターゲット)  $\leq V_{IN} - 1.6V$ 、 $I_{OUT} = 1mA$ 、 $C_{OUT} = 220\mu F$ <sup>(1)</sup>、 $R_{REF} = 12.0k\Omega$ 、動作温度範囲全体 ( $T_A = -55^{\circ}C \sim 125^{\circ}C$ )、特に記述のない限り、標準値は  $T_A = 25^{\circ}C$  での値 (QML RHA および SEP デバイスにサブグループ番号が存在する場合の  $T_A = 25^{\circ}C$  での RLAT を含む)<sup>(2)</sup>

| パラメータ                           |                                                        | テスト条件                                                                                                                 | サブグループ <sup>(3)</sup>                              | 最小値    | 標準値       | 最大値       | 単位                  |

|---------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------|-----------|-----------|---------------------|

| $V_{OUT,tempco}$                | $V_{OUT}$ 温度係数                                         | $T_A = -55^{\circ}C \sim 125^{\circ}C$                                                                                |                                                    | 0.004% |           |           | $V_{OUT}/^{\circ}C$ |

|                                 |                                                        | $T_A = -55^{\circ}C \sim -40^{\circ}C$                                                                                |                                                    | 0.011% |           |           |                     |

|                                 |                                                        | $T_A = -40^{\circ}C \sim 0^{\circ}C$                                                                                  |                                                    | 0.007% |           |           |                     |

|                                 |                                                        | $T_A = 0^{\circ}C \sim 25^{\circ}C$                                                                                   |                                                    | 0.005% |           |           |                     |

|                                 |                                                        | $T_A = 25^{\circ}C \sim 85^{\circ}C$                                                                                  |                                                    | 0.003% |           |           |                     |

|                                 |                                                        | $T_A = 85^{\circ}C \sim 125^{\circ}C$                                                                                 |                                                    | 0.001% |           |           |                     |

| $V_{REF}$                       | リファレンス電圧、セラミック パッケージ                                   |                                                                                                                       | 1, 2, 3                                            | 1.191  | 1.206     | 1.220     | V                   |

| $V_{REF}$                       | リファレンス電圧、プラスチック パッケージ                                  |                                                                                                                       | 1, 2, 3                                            | 1.190  | 1.206     | 1.221     |                     |

| $\Delta V_{OUT}/\Delta V_{IN}$  | ライン レギュレーション、図 7-1 を参照                                 | $0.85V \leq V_{IN} \leq 7V$ 、 $I_{OUT} = 1mA$ 、 $V_{BIAS} = 5V$ 、 $V_{OUT} = 0.4V$                                    | 1, 2, 3                                            | 3      | 200       | $\mu V/V$ |                     |

| $\Delta V_{OUT}/\Delta I_{OUT}$ | 負荷レギュレーション、図 7-2 を参照                                   | $1mA \leq I_{OUT} \leq 1.5A$ 、 $V_{BIAS} = 5V$ 、 $V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$                                   | 1, 2, 3                                            | 500    | 1000      | $\mu V/A$ |                     |

|                                 | カレント シェア誤差のパーセンテージ                                     | $R_{ballast} = 5m\Omega$ 、 $T_A = 25^{\circ}C$                                                                        | $I_{OUT(TOTAL)} = 1.2A$<br>$I_{OUT(TOTAL)} = 2.9A$ |        | $\pm 1\%$ |           |                     |

| $I_{OUTS(LKG)}$                 | OUTS のリーク電流                                            |                                                                                                                       | 1, 2, 3                                            | 20     | 200       | nA        |                     |

| イネーブル                           |                                                        |                                                                                                                       |                                                    |        |           |           |                     |

| $V_{EN(rising)}$                | イネーブル立ち上がりスレッショルド (ターンオン)                              |                                                                                                                       | 1, 2, 3                                            | 0.58   | 0.60      | 0.62      | V                   |

| $V_{EN(falling)}$               | イネーブル立ち下がりスレッショルド (ターンオフ)                              |                                                                                                                       | 1, 2, 3                                            | 0.48   | 0.50      | 0.52      |                     |

| $t_{EN(delay)}$                 | EN 伝搬遅延                                                | EN High から $V_{OUT} = 10mV$ まで                                                                                        | 9, 10, 11                                          | 90     | 500       | $\mu s$   |                     |

| $I_{EN(LKG)}$                   | イネーブル入力リーク電流                                           | $V_{EN} = 7V$                                                                                                         | 1, 2, 3                                            | 3      | 150       | nA        |                     |

| $T_{SD(enter)}$                 | サーマル シャットダウン開始                                         |                                                                                                                       |                                                    |        | 160       |           | $^{\circ}C$         |

| $T_{SD(exit)}$                  | サーマル シャットダウン終了                                         |                                                                                                                       |                                                    |        | 130       |           |                     |

| パワーグッド                          |                                                        |                                                                                                                       |                                                    |        |           |           |                     |

| $V_{FB\_PG(rising)}$            | パワーグッドの立ち上がりスレッショルド                                    |                                                                                                                       | 1, 2, 3                                            | 290    | 306       | 313       | mV                  |

| $V_{FB\_PG(HYS)}$               | パワーグッドのヒステリシス                                          |                                                                                                                       | 1, 2, 3                                            | 7      | 14        | 19        |                     |

| $I_{FB\_PG(LKG)}$               | FB_PG の入力リーク電流                                         | $V_{FB\_PG} = 6V$                                                                                                     | 1, 2, 3                                            | 9      | 150       | nA        |                     |

| $V_{PG(OL)}$                    | パワーグッド出力 Low                                           | $I_{PG(SINK)} = 2mA$                                                                                                  | 1, 2, 3                                            | 113    | 200       | mV        |                     |

| $V_{IN(MIN\_PG)}$               | 有効な PG の最小 $V_{IN}$ または $V_{BIAS}$ ( $V_{PG} < 0.5V$ ) | $I_{PG(sink)} = 0.6mA$                                                                                                | 1, 2, 3                                            | 0.6    | 0.8       | V         |                     |

| $I_{PG(LKG)}$                   | パワーグッドのリーク電流                                           | $V_{PG} = 7V$ 、 $V_{FB\_PG} > V_{FB\_PG(rising threshold)}$                                                           | 1, 2, 3                                            | 0.1    | 2         | $\mu A$   |                     |

| ソフトスタート                         |                                                        |                                                                                                                       |                                                    |        |           |           |                     |

| $I_{SS\_SET(start)}$            | スタートアップ時の SS_SET ピンの電流                                 |                                                                                                                       | 1, 2, 3                                            | 1.68   | 2.1       | 2.52      | mA                  |

| $t_{ss}$                        | ソフトスタート時間                                              | $V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $I_{OUT} = 1A$ 、 $R_{FB\_PG(top)} = 44.2k\Omega$ 、 $R_{FB\_PG(bot)} = 10k\Omega$ | $C_{ss} = 2.2\mu F$                                |        | 1.7       |           | ms                  |

|                                 |                                                        |                                                                                                                       | $C_{ss} = 4.7\mu F$                                |        | 3.7       |           |                     |

|                                 |                                                        |                                                                                                                       | $C_{ss} = 10\mu F$                                 |        | 7.8       |           |                     |

## 6.5 電気的特性 (続き)

$0.85V \leq V_{IN} \leq 7V$ 、 $V_{BIAS} \geq V_{OUT} + 1.6V$  ( $V_{IN} \leq V_{BIAS} \leq 14V$  &  $V_{BIAS} \geq 2.2V$ )、 $V_{OUT}$  (ターゲット)  $\leq V_{IN} - 1.6V$ 、 $I_{OUT} = 1mA$ 、 $C_{OUT} = 220\mu F$ <sup>(1)</sup>、 $R_{REF} = 12.0k\Omega$ 、動作温度範囲全体 ( $T_A = -55^{\circ}C$ ~ $125^{\circ}C$ )、特に記述のない限り、標準値は  $T_A = 25^{\circ}C$  での値 (QML RHA および SEP デバイスにサブグループ番号が存在する場合の  $T_A = 25^{\circ}C$  での RLAT を含む)<sup>(2)</sup>

| パラメータ                |                                    | テスト条件                                                                                                                                       | サブグループ <sup>(3)</sup> | 最小値 | 標準値  | 最大値 | 単位             |

|----------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|------|-----|----------------|

| <b>ノイズおよび PSRR</b>   |                                    |                                                                                                                                             |                       |     |      |     |                |

| PSRR                 | 電源除去比                              | $V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{SS} = 4.7\mu F$ 、 $C_{BIAS} = 4.7\mu F$ 、 $R_{BIAS} = 10\Omega$ | $f_{ripple} = 100Hz$  |     | 109  |     | dB             |

|                      |                                    |                                                                                                                                             | $f_{ripple} = 1kHz$   |     | 109  |     |                |

|                      |                                    |                                                                                                                                             | $f_{ripple} = 10kHz$  |     | 90   |     |                |

|                      |                                    |                                                                                                                                             | $f_{ripple} = 100kHz$ |     | 71   |     |                |

|                      |                                    |                                                                                                                                             | $f_{ripple} = 1MHz$   |     | 66   |     |                |

|                      |                                    |                                                                                                                                             | $f_{ripple} = 10MHz$  |     | 30   |     |                |

| PSRR <sub>BIAS</sub> | 電源除去比、 $V_{BIAS}$ から $V_{OUT}$     | $V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{SS} = 4.7\mu F$ 、 $C_{BIAS} = 4.7\mu F$ 、 $R_{BIAS} = 10\Omega$ | $f_{ripple} = 100Hz$  |     | 102  |     | dB             |

|                      |                                    |                                                                                                                                             | $f_{ripple} = 1kHz$   |     | 105  |     |                |

|                      |                                    |                                                                                                                                             | $f_{ripple} = 10kHz$  |     | 87   |     |                |

|                      |                                    |                                                                                                                                             | $f_{ripple} = 100kHz$ |     | 97   |     |                |

|                      |                                    |                                                                                                                                             | $f_{ripple} = 1MHz$   |     | 118  |     |                |

|                      |                                    |                                                                                                                                             | $f_{ripple} = 10MHz$  |     | 68   |     |                |

| V <sub>N</sub>       | 出力ノイズ RMS 電圧<br>(10Hz~100kHz の帯域幅) | $V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$                                                                       | $C_{SS} = 2.2\mu F$   |     | 1.73 |     | $\mu V_{RMS}$  |

|                      |                                    |                                                                                                                                             | $C_{SS} = 4.7\mu F$   |     | 1.71 |     |                |

|                      |                                    |                                                                                                                                             | $C_{SS} = 10\mu F$    |     | 1.69 |     |                |

| e <sub>N</sub>       | 出力ノイズ電圧密度                          | $V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{SS} = 4.7\mu F$                                                 | $f = 10Hz$            |     | 97   |     | $nV/\sqrt{Hz}$ |

|                      |                                    |                                                                                                                                             | $f = 100Hz$           |     | 11.2 |     |                |

|                      |                                    |                                                                                                                                             | $f = 1kHz$            |     | 5.4  |     |                |

|                      |                                    |                                                                                                                                             | $f = 10kHz$           |     | 5.6  |     |                |

|                      |                                    |                                                                                                                                             | $f = 100kHz$          |     | 4.9  |     |                |

|                      |                                    |                                                                                                                                             | $f = 1MHz$            |     | 1.6  |     |                |

|                      |                                    |                                                                                                                                             | $f = 10MHz$           |     | 1.7  |     |                |

| <b>安定性</b>           |                                    |                                                                                                                                             |                       |     |      |     |                |

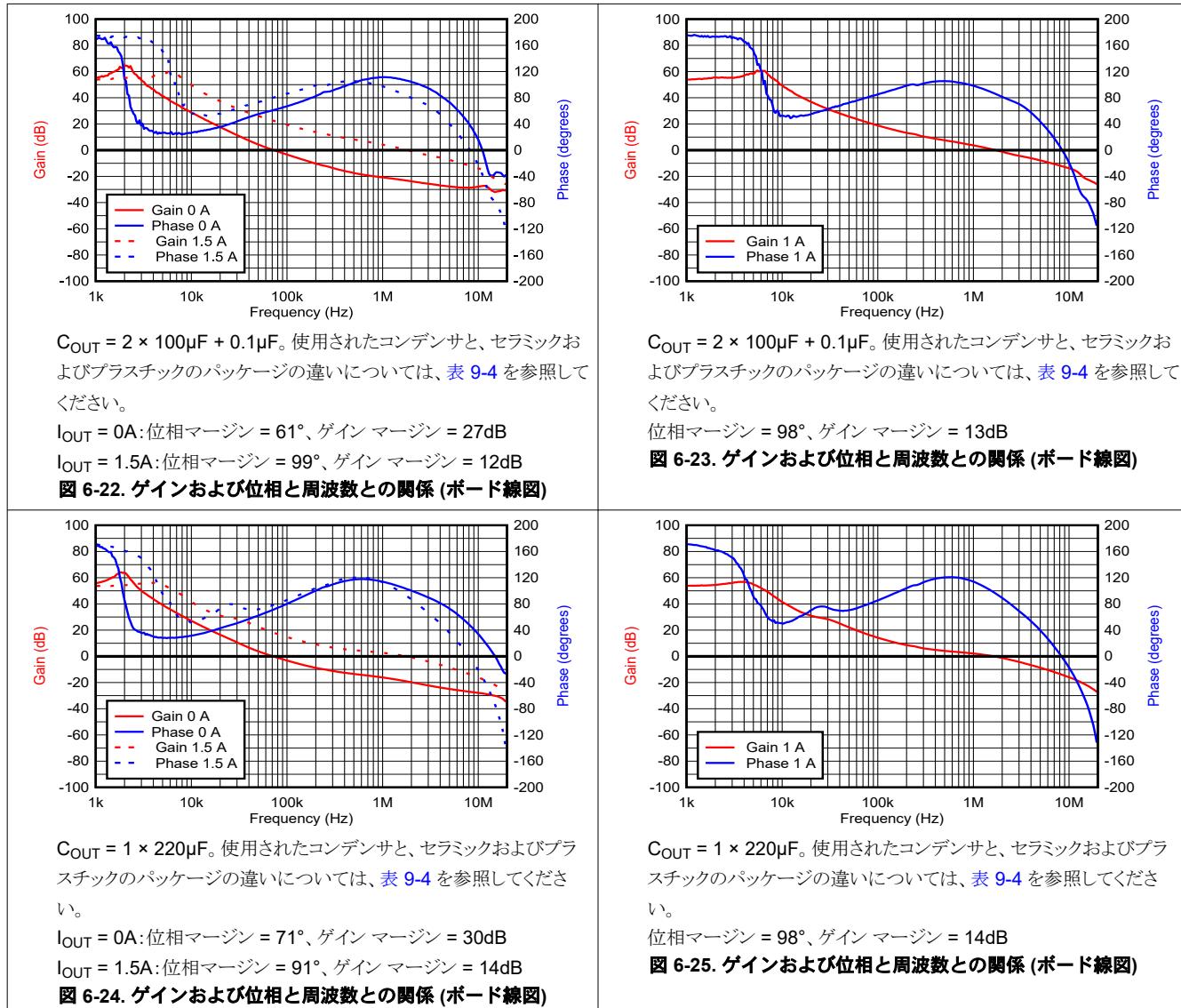

| PM                   | 位相マージン                             | $V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $I_{OUT} = 1.0A$ 、<br>$C_{OUT} = 2 \times 100\mu F$ <sup>(7)</sup>                                     |                       |     | 98°  |     |                |

| GM                   | ゲインマージン                            |                                                                                                                                             |                       |     | 19   |     | dB             |

(1) 1つの  $220\mu F$  タンタルコンデンサを使用

(2) QML RHA デバイスの詳細については [5962R21203 SMD](#) を、SEP デバイスの詳細については [V62/23602 VID](#) を参照してください。

(3) サブグループは、デバイスの QML バージョンにのみ適用できます。サブグループの定義については、[セクション 6.6](#) を参照してください。

(4) また、 $V_{BIAS} \geq V_{IN}$  および  $V_{BIAS} \geq V_{OUT} + 1.6V$  です。

(5)  $P_D$  は内部消費電力です。 $P_D$  が  $4W$  を超えると、(テストの制限による) 局所的な過熱を避けるため、電流が低下します。

(6) QMLV および QMLP 部品の場合は  $TID = 100krad(Si)$ 、SEP 部品の場合は  $TID = 50krad(Si)$  です。

(7) 詳細については、[セクション 9.3](#) を参照してください。

## 6.6 品質適合検査

MIL-STD-883、方法 5005 - グループ A

| サブグループ | 説明         | 温度 (°C) |

|--------|------------|---------|

| 1      | 静的テスト      | 25      |

| 2      | 静的テスト      | 125     |

| 3      | 静的テスト      | -55     |

| 4      | 動的テスト      | 25      |

| 5      | 動的テスト      | 125     |

| 6      | 動的テスト      | -55     |

| 7      | 機能テスト      | 25      |

| 8A     | 機能テスト      | 125     |

| 8B     | 機能テスト      | -55     |

| 9      | スイッチング テスト | 25      |

| 10     | スイッチング テスト | 125     |

| 11     | スイッチング テスト | -55     |

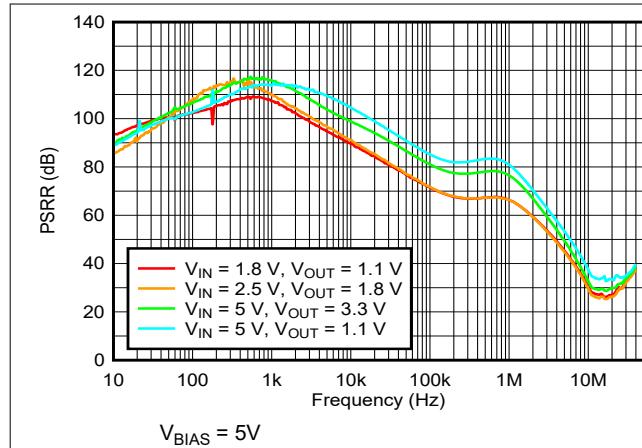

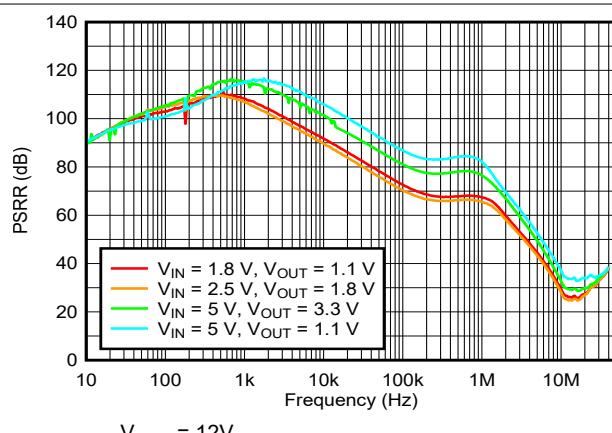

## 6.7 代表的特性

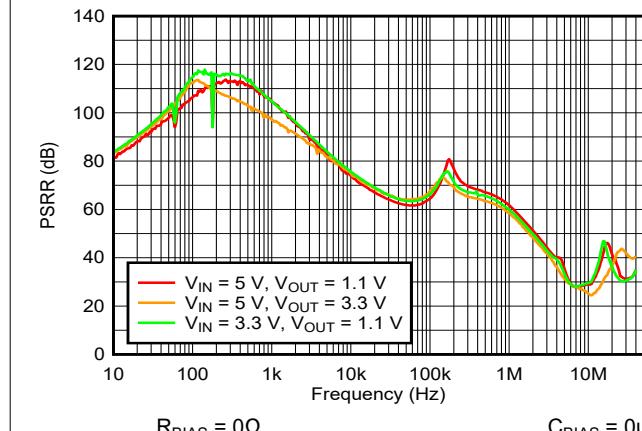

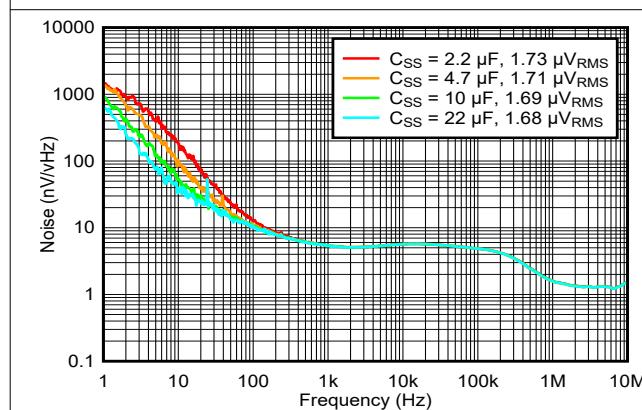

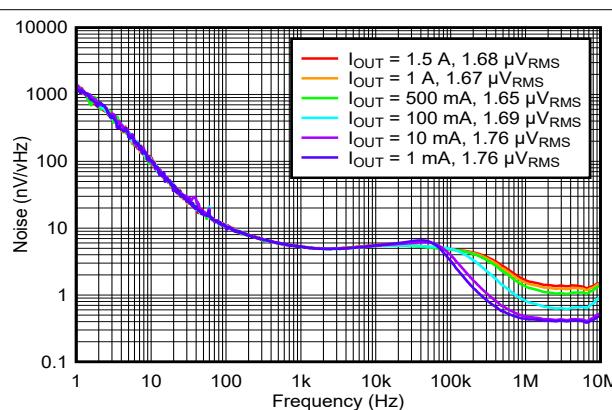

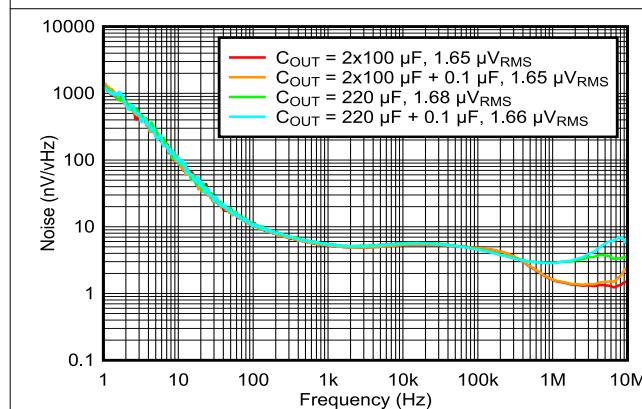

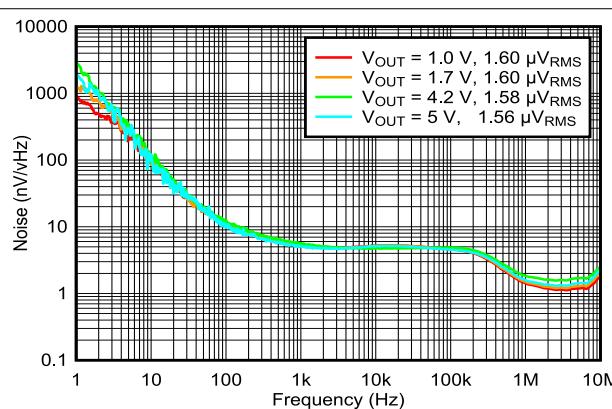

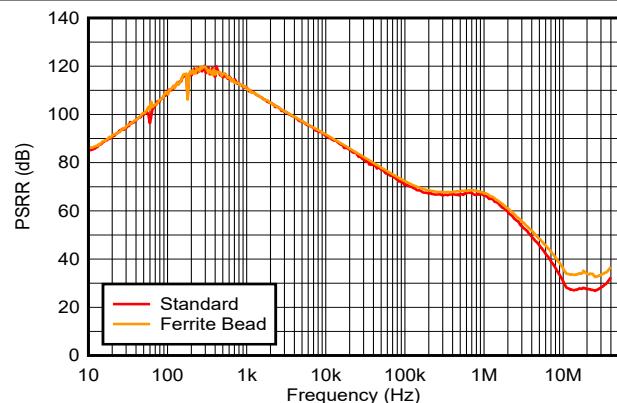

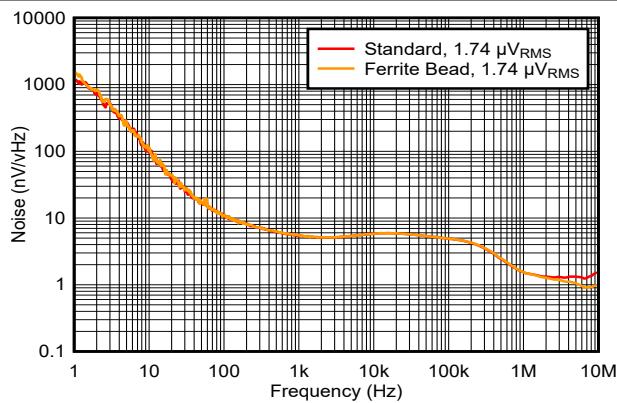

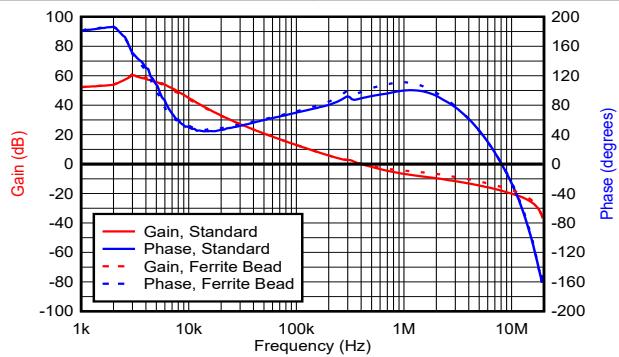

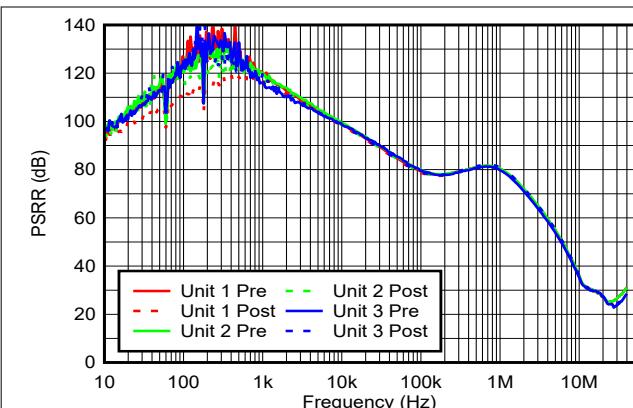

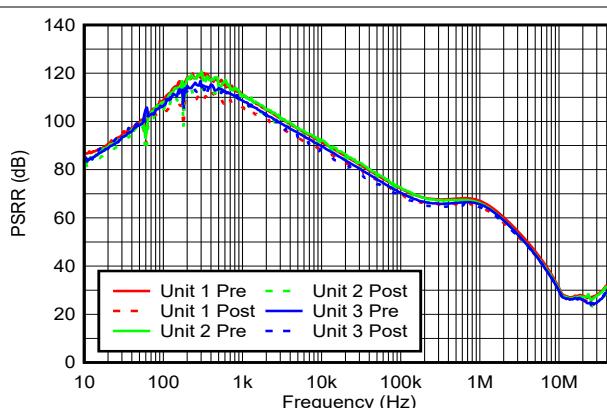

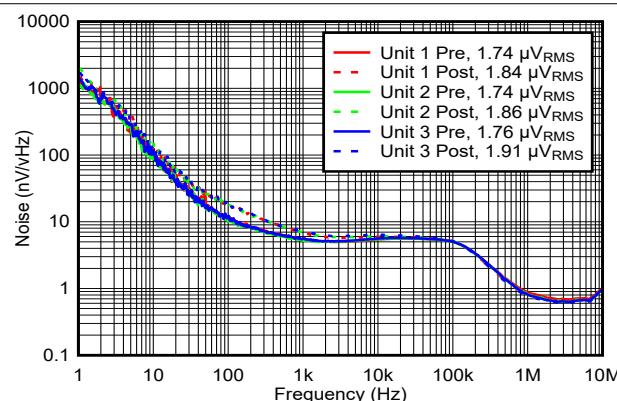

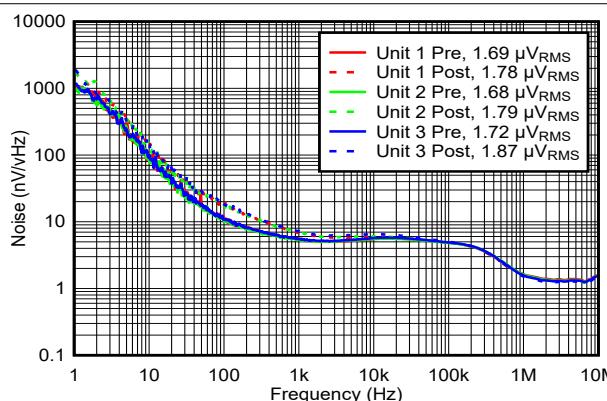

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{OUT} = 2 \times 100\mu F$ 、 $C_{SS} = 4.7\mu F$ 、 $R_{REF} = 12.0k\Omega$ 、 $R_{BIAS} = 10\Omega$ 、 $C_{BIAS} = 4.7\mu F$ 、 $T_A = 25^\circ C$ 、特に記述のない限り、積分ノイズは 10Hz～100kHz の帯域幅で報告。

図 6-1. PSRR と周波数との関係 (一般的な構成)

図 6-2. PSRR と周波数との関係 (一般的な構成)

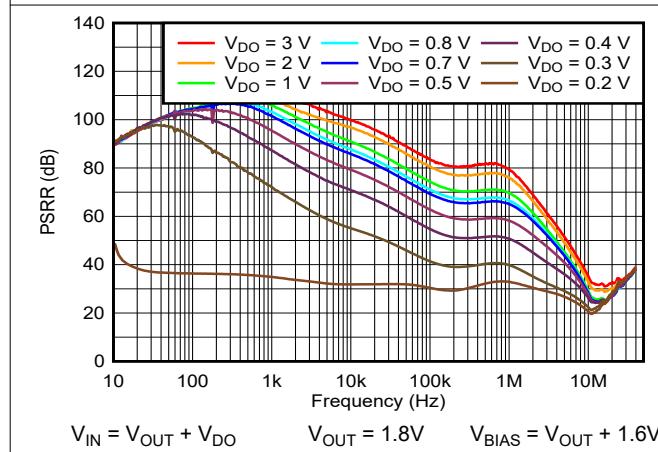

図 6-3. さまざまなドロップアウト電圧における PSRR と周波数との関係

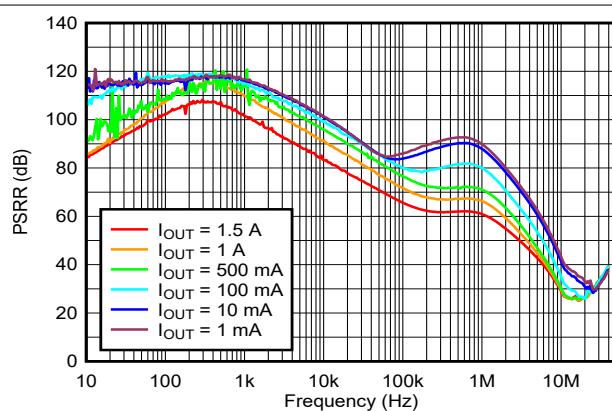

図 6-4. さまざまな出力電流における PSRR と周波数との関係

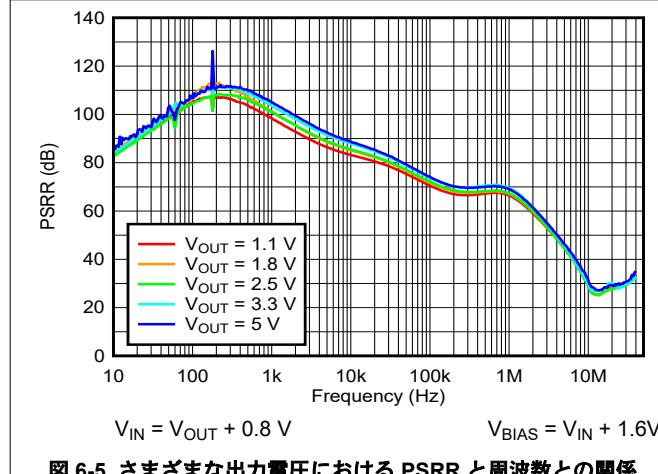

図 6-5. さまざまな出力電圧における PSRR と周波数との関係

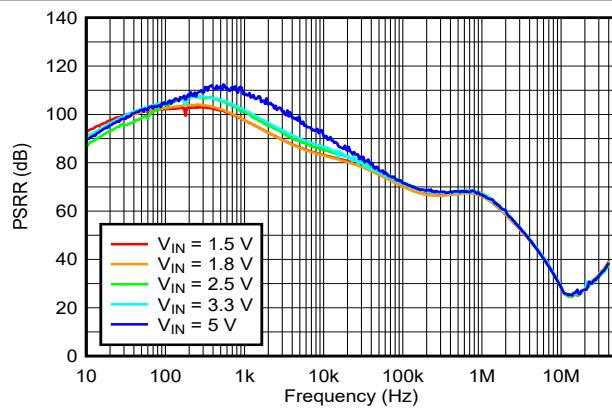

図 6-6. さまざまな入力電圧における PSRR と周波数との関係

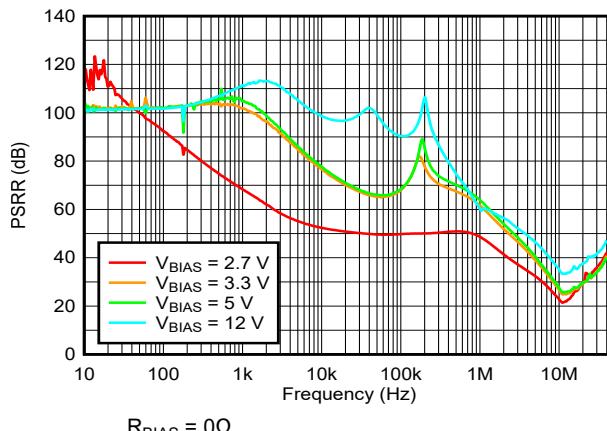

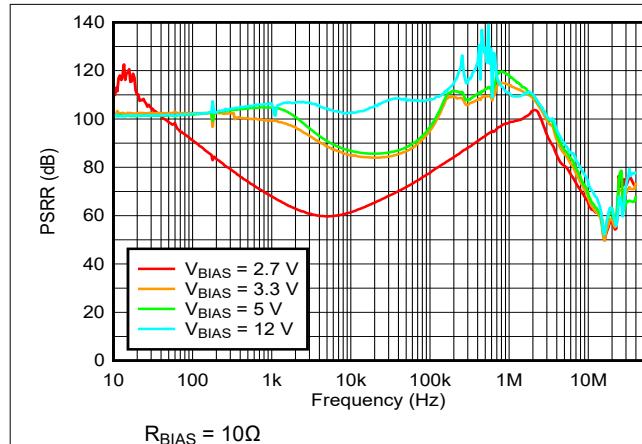

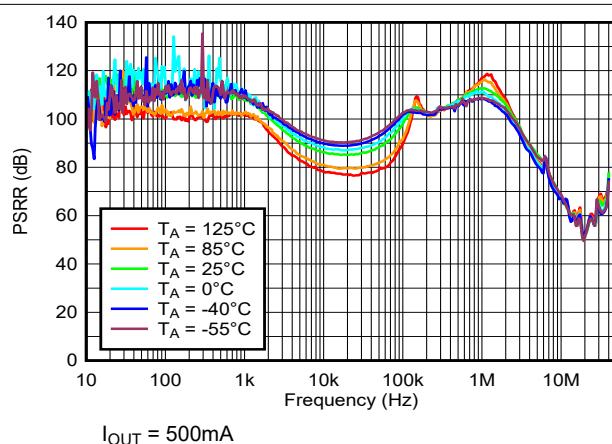

## 6.7 代表的特性 (続き)

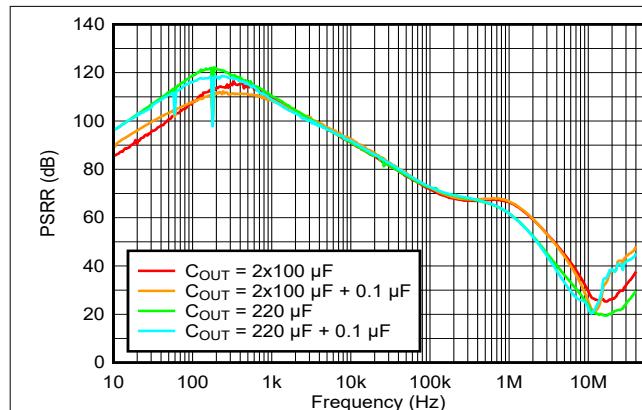

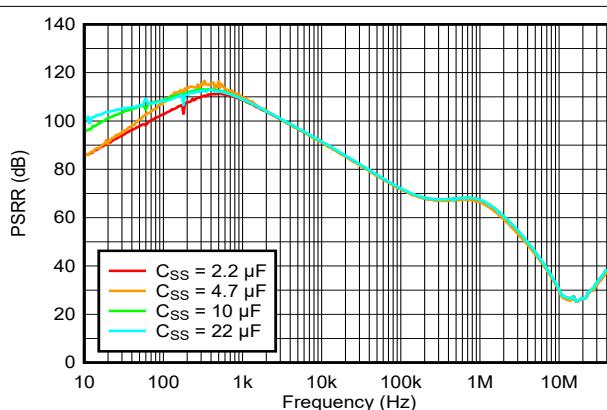

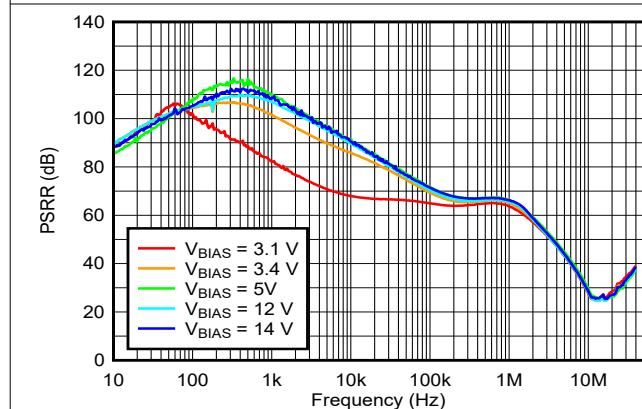

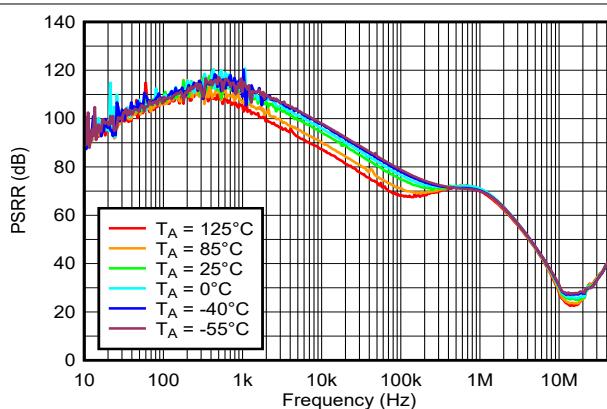

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{OUT} = 2 \times 100\mu F$ 、 $C_{SS} = 4.7\mu F$ 、 $R_{REF} = 12.0k\Omega$ 、 $R_{BIAS} = 10\Omega$ 、 $C_{BIAS} = 4.7\mu F$ 、 $T_A = 25^\circ C$ 、特に記述のない限り、積分ノイズは 10Hz～100kHz の帯域幅で報告。

使用されたコンデンサの型番については表 9-4 を参照。

図 6-7. さまざまな出力容量における PSRR と周波数との関係

図 6-8. さまざまなソフトスタート容量における PSRR と周波数との関係

図 6-9. さまざまなバイアス電源における PSRR と周波数との関係

$I_{OUT} = 500mA$

図 6-10. 動作温度範囲における PSRR と周波数の関係

$R_{BIAS} = 0\Omega$

$C_{BIAS} = 0\mu F$

図 6-11.  $V_{IN} = V_{BIAS}$  における PSRR と周波数との関係

図 6-12. さまざまなバイアス電圧における  $PSRR_{BIAS}$  と周波数との関係 (RC なし)

## 6.7 代表的特性 (続き)

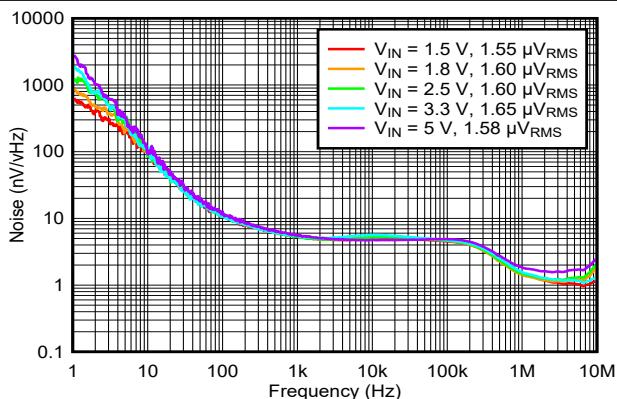

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{OUT} = 2 \times 100\mu F$ 、 $C_{SS} = 4.7\mu F$ 、 $R_{REF} = 12.0k\Omega$ 、 $R_{BIAS} = 10\Omega$ 、 $C_{BIAS} = 4.7\mu F$ 、 $T_A = 25^\circ C$ 、特に記述のない限り、積分ノイズは 10Hz～100kHz の帯域幅で報告。

図 6-13. さまざまなバイアス電圧における PSRR<sub>BIAS</sub> と周波数との関係 (RC あり)

図 6-14. 動作温度範囲における PSRR<sub>BIAS</sub> と周波数の関係

図 6-15. さまざまな C<sub>SS</sub> における出力ノイズと周波数との関係 (ノイズスペクトル密度)

図 6-16. さまざまな出力電流における出力ノイズと周波数との関係 (ノイズスペクトル密度)

使用されたコンデンサの型番については表 9-4 を参照。

図 6-17. さまざまな出力コンデンサにおける出力ノイズと周波数との関係 (ノイズスペクトル密度)

図 6-18. さまざまな出力電圧における出力ノイズと周波数との関係 (ノイズスペクトル密度)

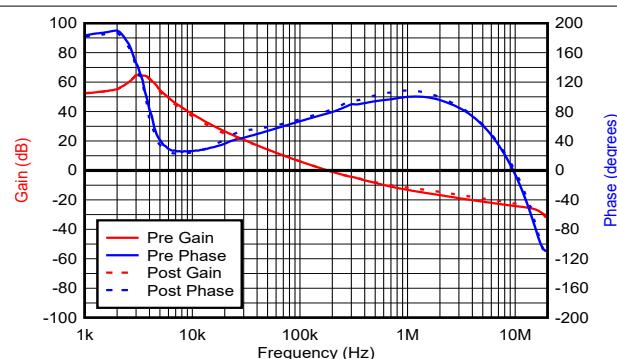

## 6.7 代表的特性 (続き)

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{OUT} = 2 \times 100\mu F$ 、 $C_{SS} = 4.7\mu F$ 、 $R_{REF} = 12.0k\Omega$ 、 $R_{BIAS} = 10\Omega$ 、 $C_{BIAS} = 4.7\mu F$ 、 $T_A = 25^\circ C$ 、特に記述のない限り、積分ノイズは 10Hz～100kHz の帯域幅で報告。

$$V_{OUT} = V_{IN} - 0.8V$$

図 6-19. さまざまな入力電圧における出力ノイズと周波数との関係 (ノイズスペクトル密度)

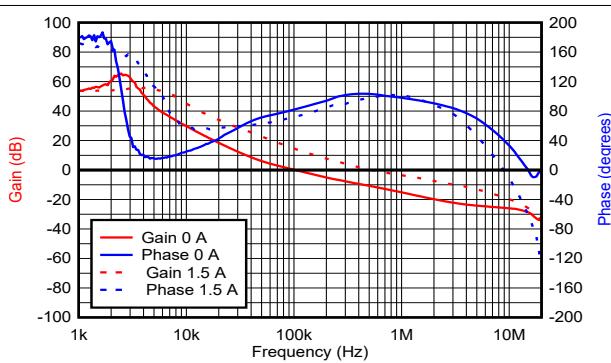

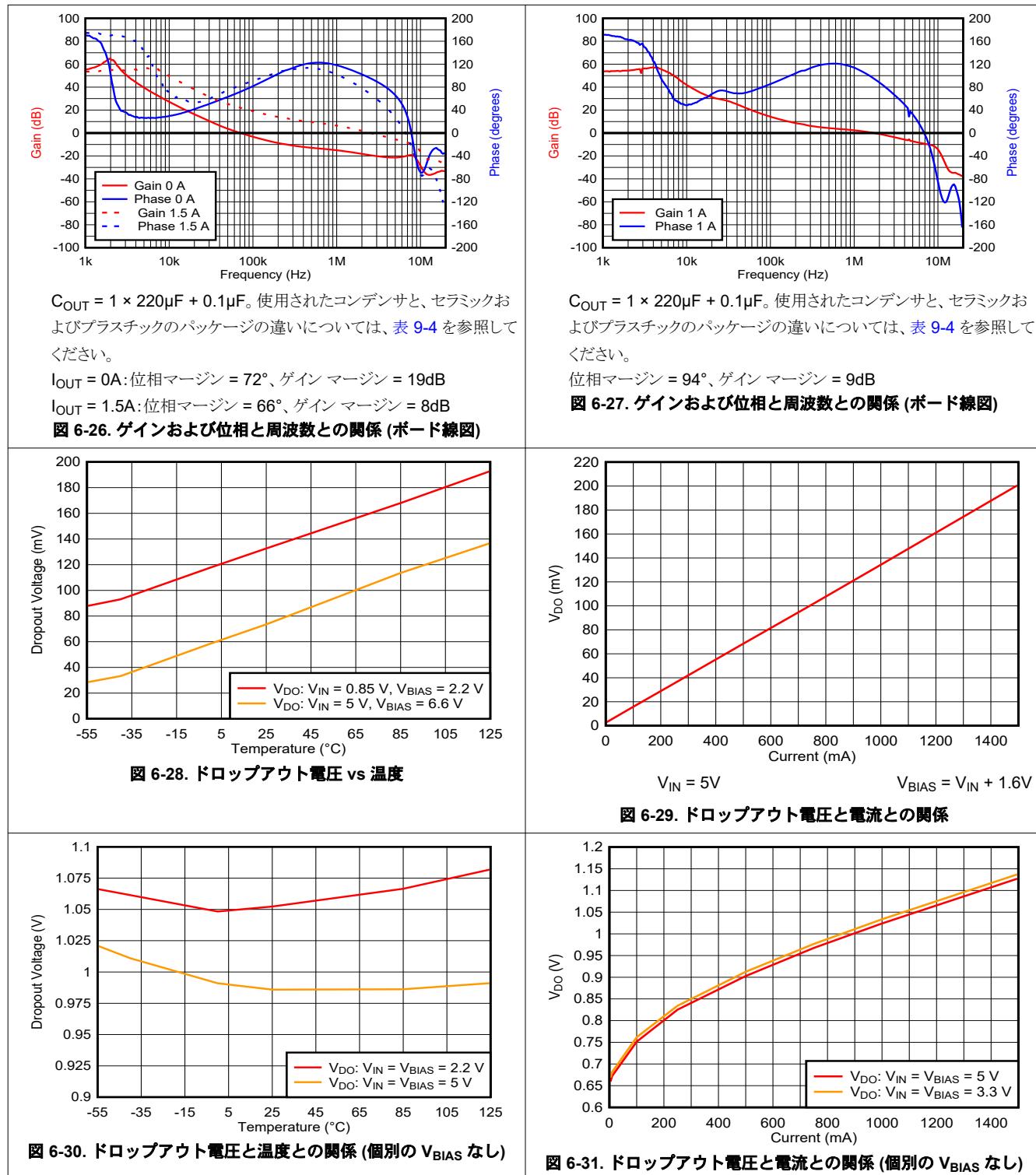

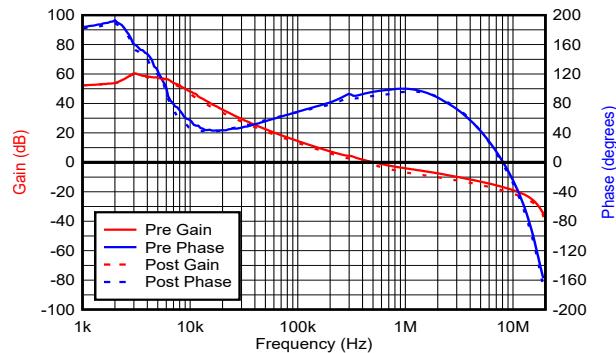

$C_{OUT} = 2 \times 100\mu F$ 。使用されたコンデンサと、セラミックおよびプラスチックのパッケージの違いについては、表 9-4 を参照してください。

$I_{OUT} = 0A$ : 位相マージン = 83°、ゲインマージン = 29dB

$I_{OUT} = 1.5A$ : 位相マージン = 99°、ゲインマージン = 19dB

図 6-20. ゲインおよび位相と周波数との関係 (ボード線図)

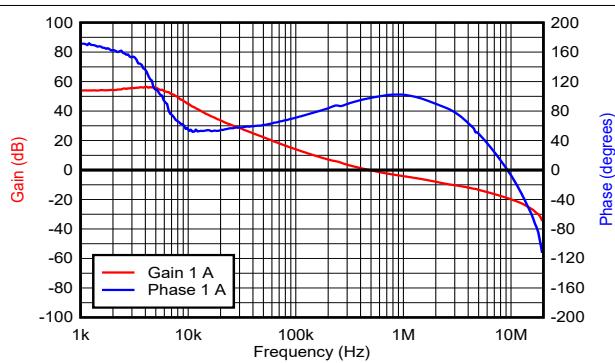

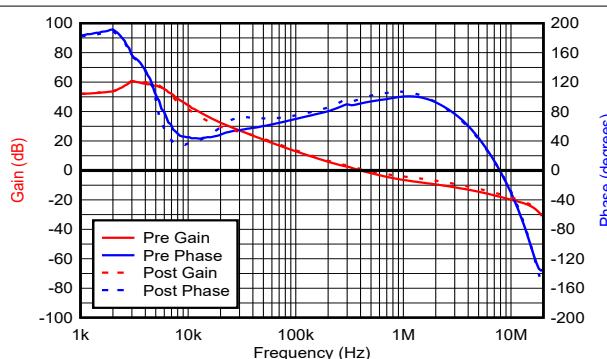

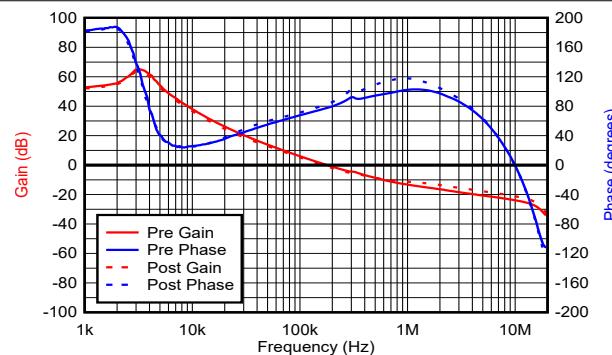

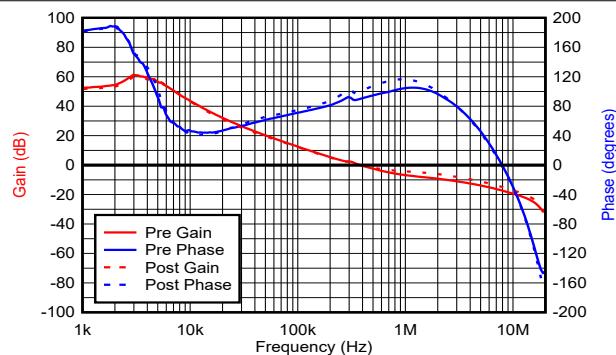

$C_{OUT} = 2 \times 100\mu F$ 。使用されたコンデンサと、セラミックおよびプラスチックのパッケージの違いについては、表 9-4 を参照してください。

位相マージン = 98°、ゲインマージン = 19dB

図 6-21. ゲインおよび位相と周波数との関係 (ボード線図)

## 6.7 代表的特性 (続き)

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{OUT} = 2 \times 100\mu F$ 、 $C_{SS} = 4.7\mu F$ 、 $R_{REF} = 12.0k\Omega$ 、 $R_{BIAS} = 10\Omega$ 、 $C_{BIAS} = 4.7\mu F$ 、 $T_A = 25^\circ C$ 、特に記述のない限り、積分ノイズは 10Hz～100kHz の帯域幅で報告。

## 6.7 代表的特性 (続き)

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{OUT} = 2 \times 100\mu F$ 、 $C_{SS} = 4.7\mu F$ 、 $R_{REF} = 12.0k\Omega$ 、 $R_{BIAS} = 10\Omega$ 、 $C_{BIAS} = 4.7\mu F$ 、 $T_A = 25^\circ C$ 、特に記述のない限り、積分ノイズは 10Hz～100kHz の帯域幅で報告。

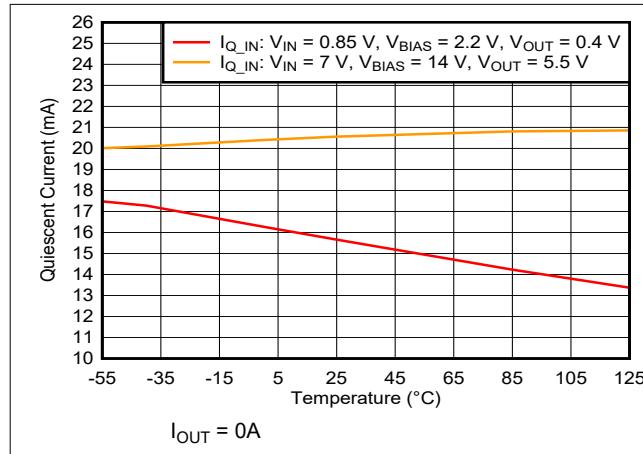

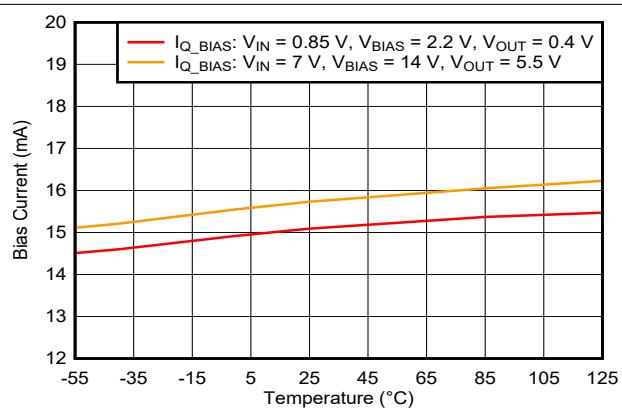

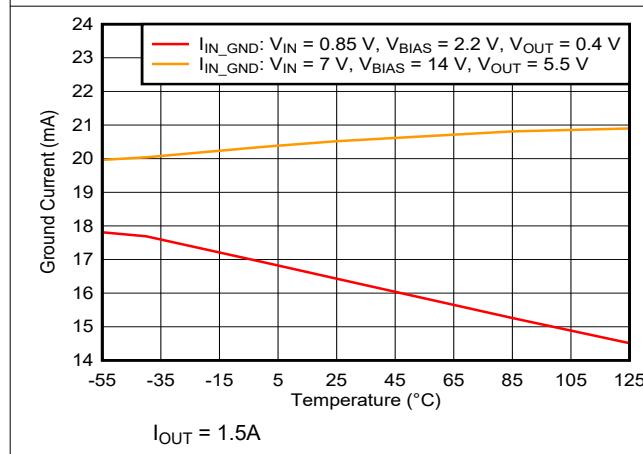

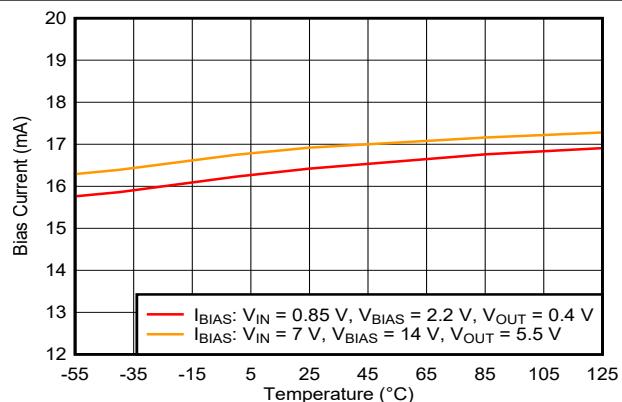

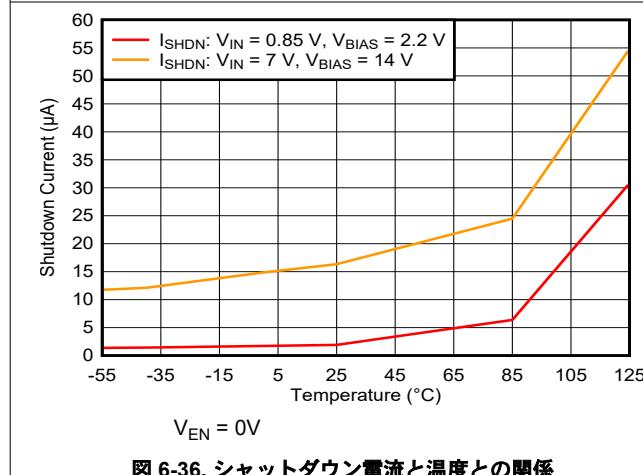

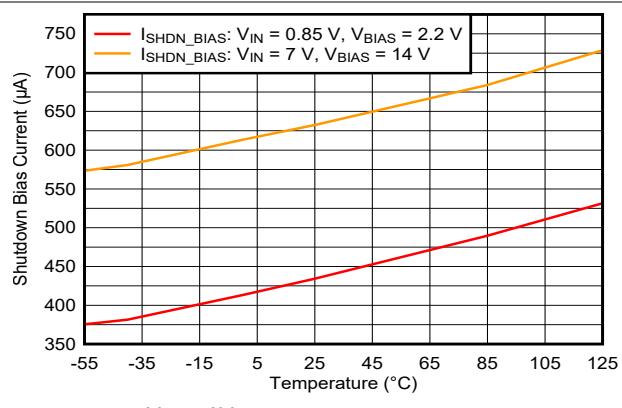

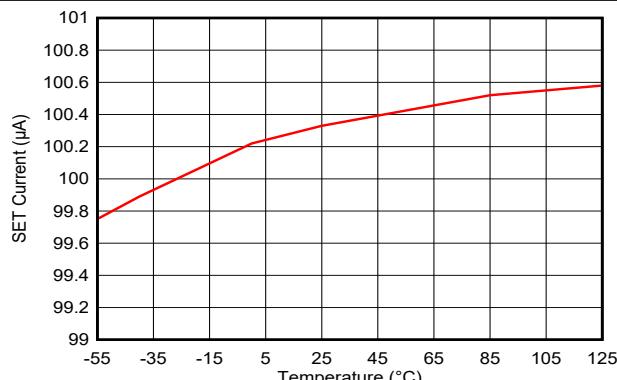

## 6.7 代表的特性 (続き)

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{OUT} = 2 \times 100\mu F$ 、 $C_{SS} = 4.7\mu F$ 、 $R_{REF} = 12.0k\Omega$ 、 $R_{BIAS} = 10\Omega$ 、 $C_{BIAS} = 4.7\mu F$ 、 $T_A = 25^\circ C$ 、特に記述のない限り、積分ノイズは 10Hz～100kHz の帯域幅で報告。

図 6-32. 静止電流と温度との関係

図 6-33. バイアス電流と温度との関係

図 6-34. グランド電流 vs 温度

図 6-35. バイアス電流と温度との関係

図 6-36. シャットダウン電流と温度との関係

図 6-37. バイアス シャットダウン電流と温度との関係

## 6.7 代表的特性 (続き)

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{OUT} = 2 \times 100\mu F$ 、 $C_{SS} = 4.7\mu F$ 、 $R_{REF} = 12.0k\Omega$ 、 $R_{BIAS} = 10\Omega$ 、 $C_{BIAS} = 4.7\mu F$ 、 $T_A = 25^\circ C$ 、特に記述のない限り、積分ノイズは 10Hz～100kHz の帯域幅で報告。

図 6-38. SET ピンの電流と温度との関係

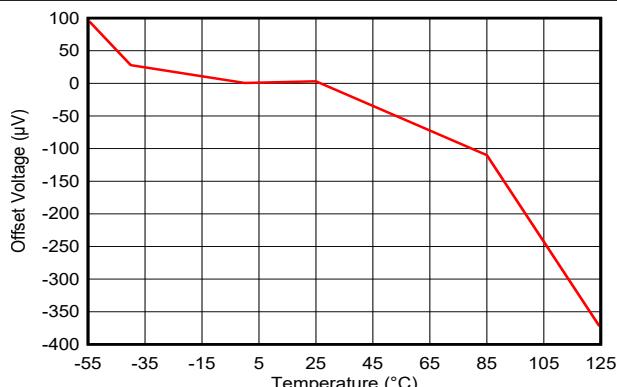

図 6-39. オフセット電圧と温度との関係

図 6-40. オフセット電圧と電流との関係

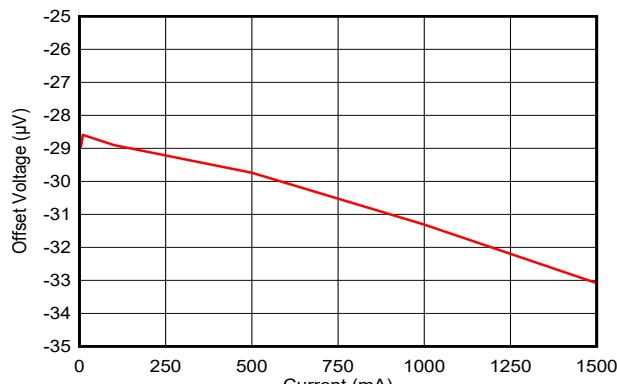

図 6-41. 出力電圧と温度との関係

$V_{EN} = 7V$        $V_{IN} = 7V$        $V_{BIAS} = 14V$

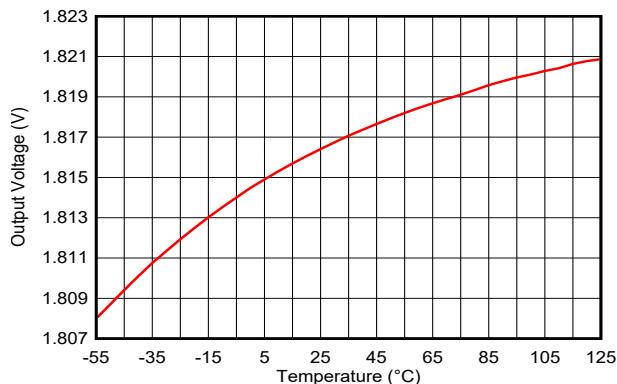

図 6-42. リーク電流と温度との関係

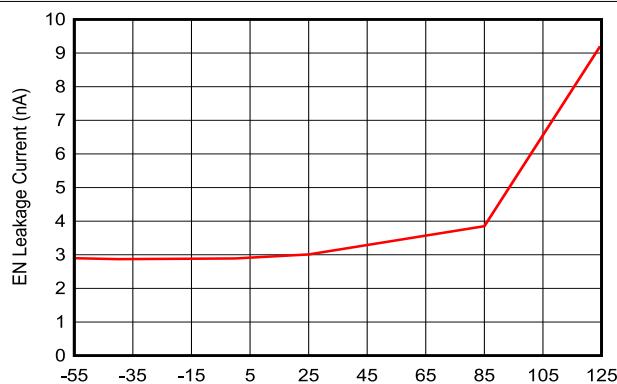

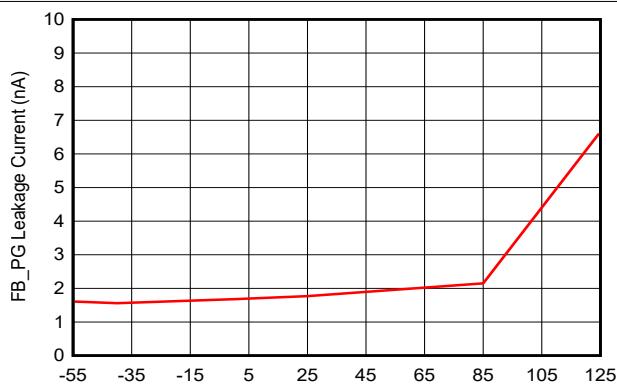

$V_{FB\_PG} = 6V$        $V_{IN} = 7V$        $V_{BIAS} = 14V$

$I_{OUT} = 1mA$

図 6-43. FB\_PG ピンのリーク電流と温度との関係

## 6.7 代表的特性 (続き)

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{OUT} = 2 \times 100\mu F$ 、 $C_{SS} = 4.7\mu F$ 、 $R_{REF} = 12.0k\Omega$ 、 $R_{BIAS} = 10\Omega$ 、 $C_{BIAS} = 4.7\mu F$ 、 $T_A = 25^\circ C$ 、特に記述のない限り、積分ノイズは 10Hz～100kHz の帯域幅で報告。

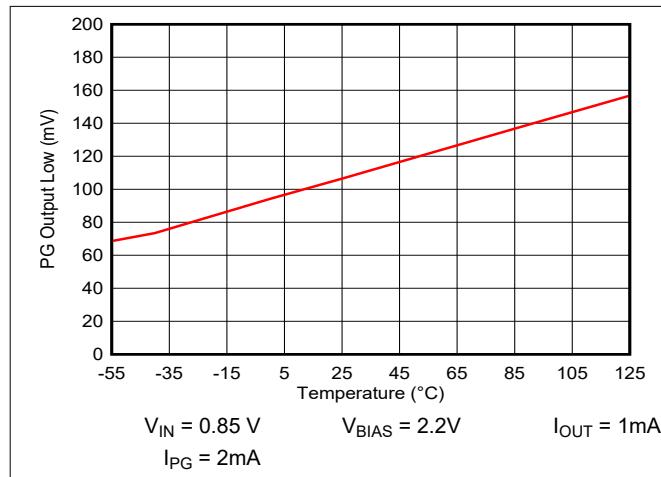

図 6-44. PG ピン出力 Low と温度との関係

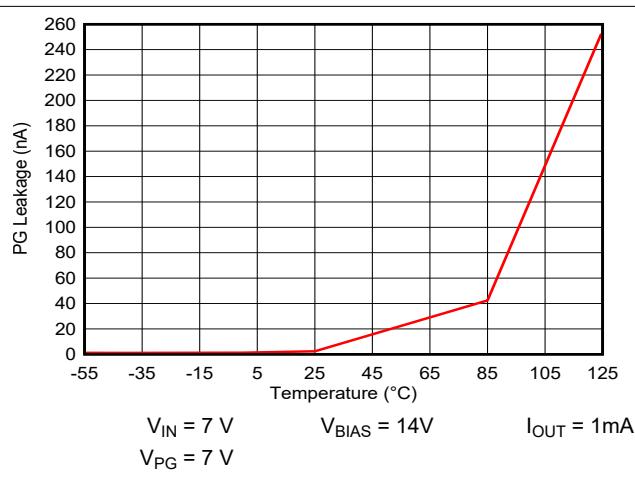

図 6-45. PG ピンのリーク電流と温度との関係

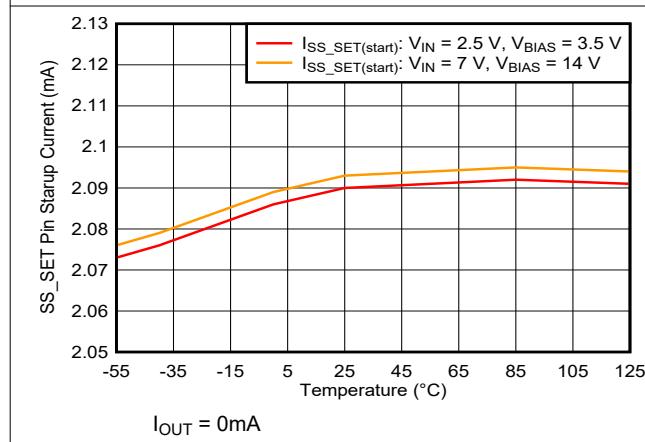

図 6-46. スタートアップ時の SS\_SET ピン電流と温度との関係

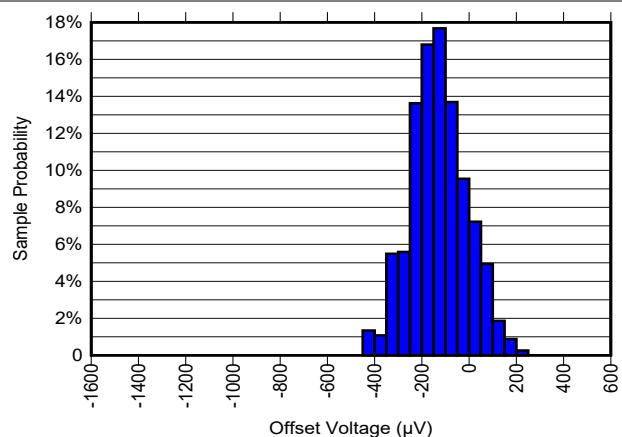

図 6-47. 出力オフセット電圧の分布 ( $T_A = -55^\circ C$ )

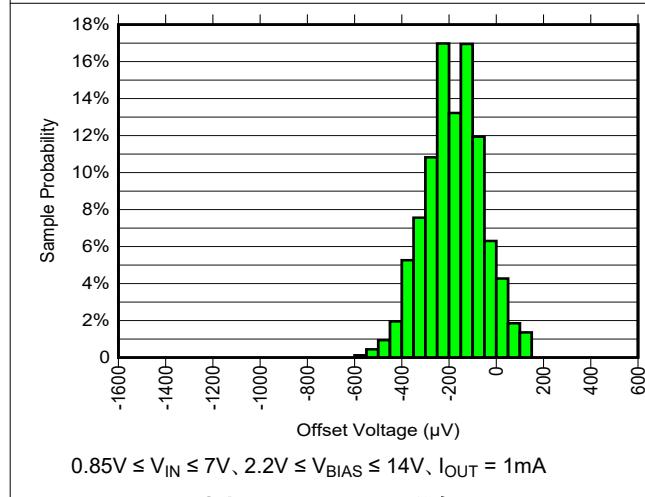

図 6-48. 出力オフセット電圧の分布 ( $T_A = 25^\circ C$ )

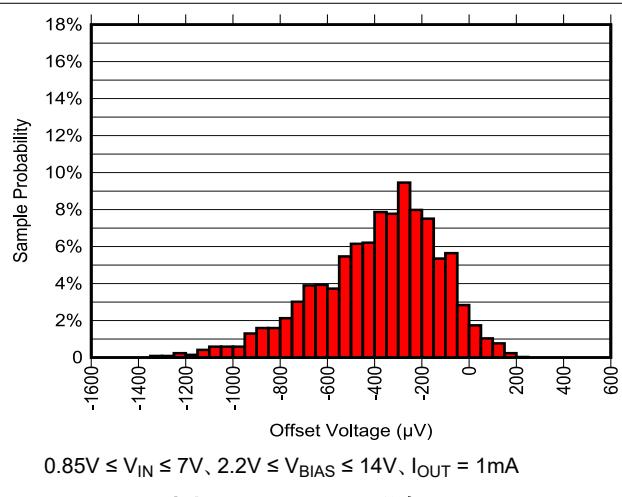

図 6-49. 出力オフセット電圧の分布 ( $T_A = 125^\circ C$ )

## 6.7 代表的特性 (続き)

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{OUT} = 2 \times 100\mu F$ 、 $C_{SS} = 4.7\mu F$ 、 $R_{REF} = 12.0k\Omega$ 、 $R_{BIAS} = 10\Omega$ 、 $C_{BIAS} = 4.7\mu F$ 、 $T_A = 25^\circ C$ 、特に記述のない限り、積分ノイズは 10Hz～100kHz の帯域幅で報告。

## 6.7 代表的特性 (続き)

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{OUT} = 2 \times 100\mu F$ 、 $C_{SS} = 4.7\mu F$ 、 $R_{REF} = 12.0k\Omega$ 、 $R_{BIAS} = 10\Omega$ 、 $C_{BIAS} = 4.7\mu F$ 、 $T_A = 25^\circ C$ 、特に記述のない限り、積分ノイズは 10Hz～100kHz の帯域幅で報告。

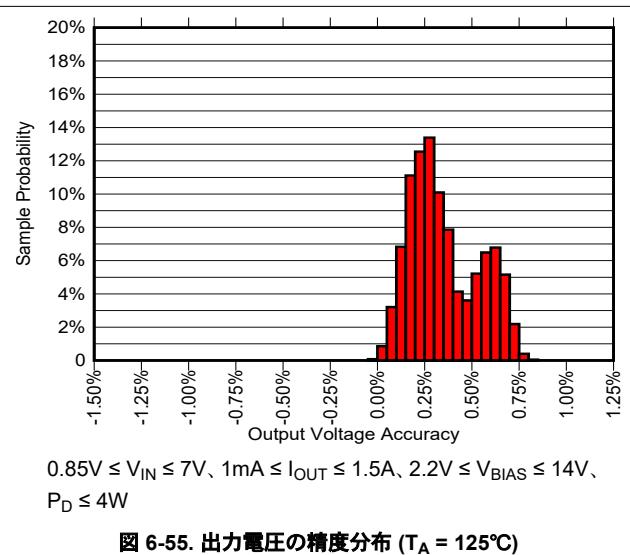

図 6-54. 出力電圧の精度分布 ( $T_A = 25^\circ C$ )

図 6-55. 出力電圧の精度分布 ( $T_A = 125^\circ C$ )

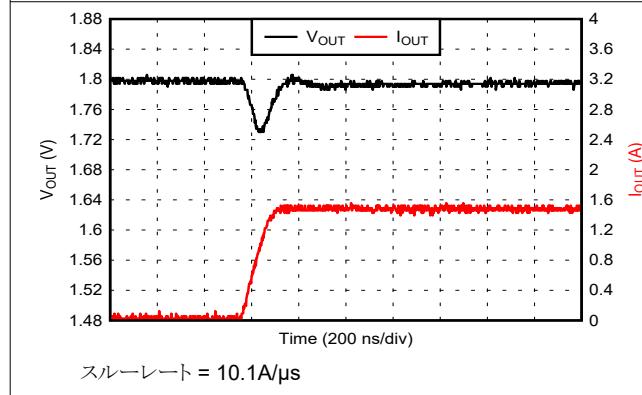

図 6-56. 負荷ステップ :  $1mA \sim 1.5A$

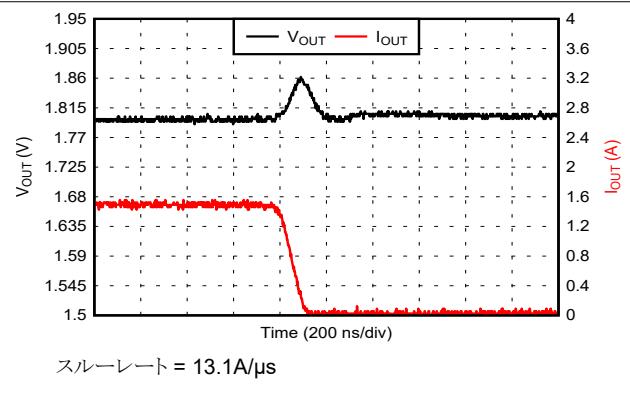

図 6-57. 負荷ステップ :  $1.5A \sim 1mA$

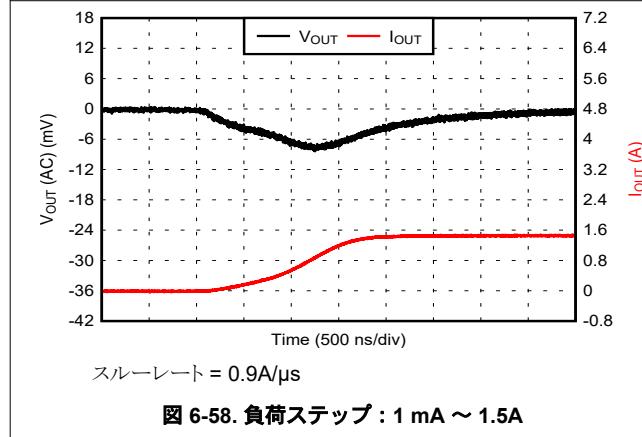

図 6-58. 負荷ステップ :  $1mA \sim 1.5A$

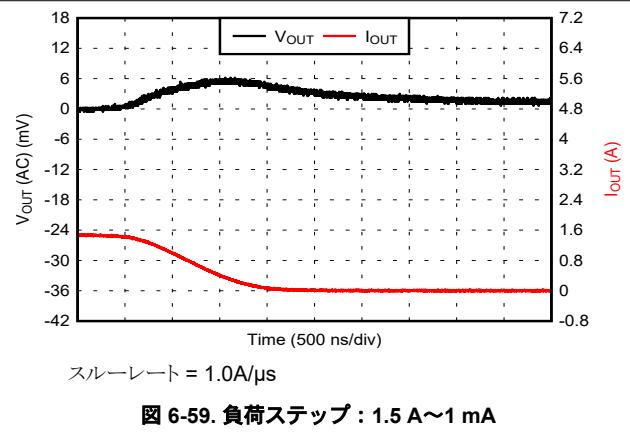

図 6-59. 負荷ステップ :  $1.5A \sim 1mA$

## 6.7 代表的特性 (続き)

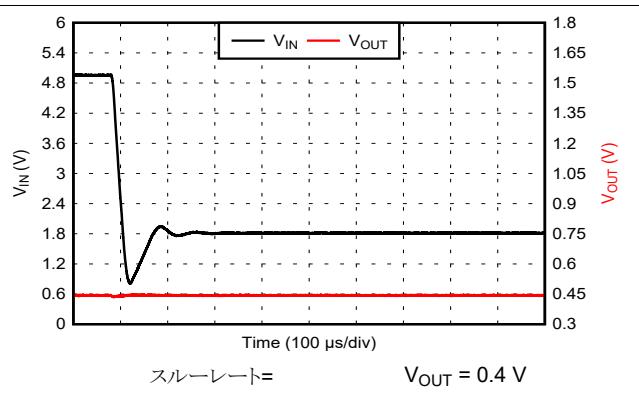

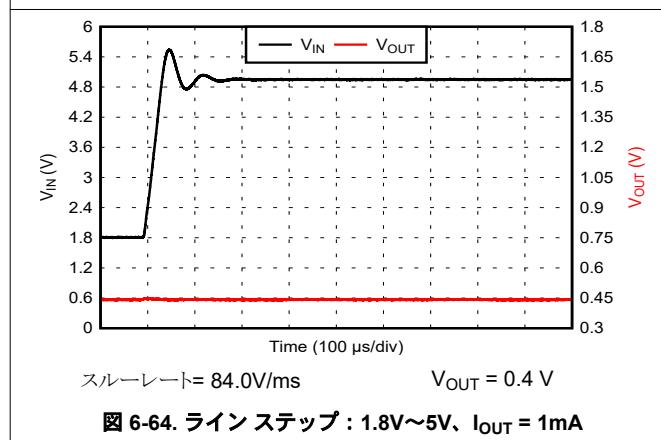

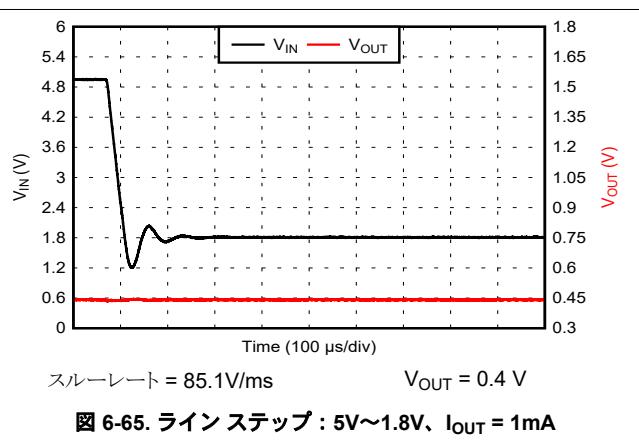

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{OUT} = 2 \times 100\mu F$ 、 $C_{SS} = 4.7\mu F$ 、 $R_{REF} = 12.0k\Omega$ 、 $R_{BIAS} = 10\Omega$ 、 $C_{BIAS} = 4.7\mu F$ 、 $T_A = 25^\circ C$ 、特に記述のない限り、積分ノイズは 10Hz～100kHz の帯域幅で報告。

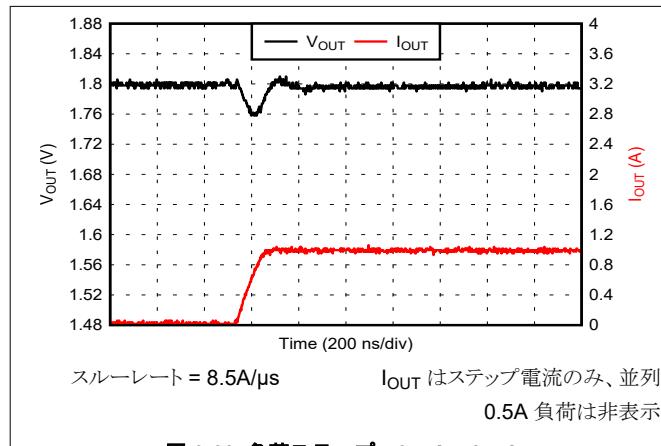

図 6-60. 負荷ステップ : 0.5 A～1.5 A

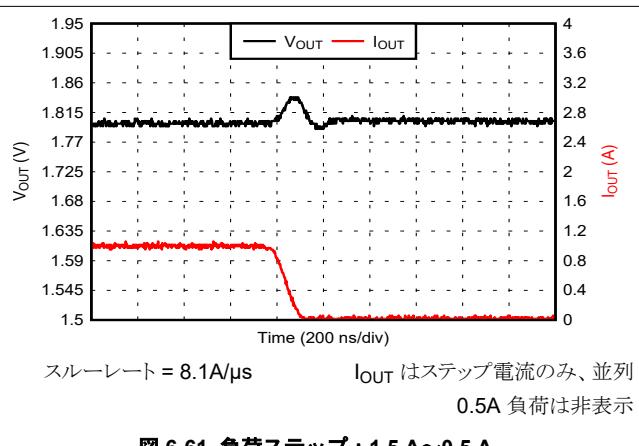

図 6-61. 負荷ステップ : 1.5 A～0.5 A

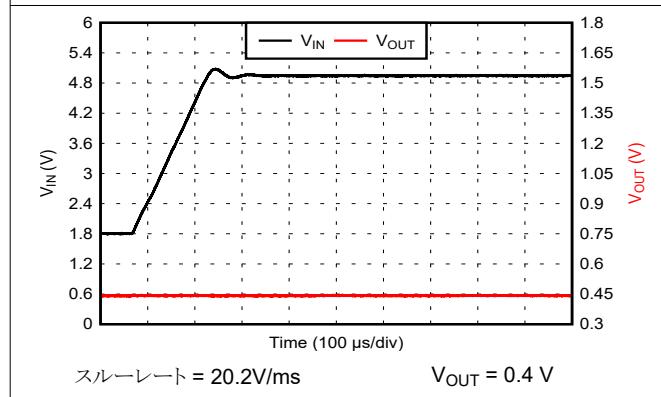

図 6-62. ラインステップ : 1.8V～5V、 $I_{OUT} = 1.5A$

図 6-63. ラインステップ : 5V～1.8V、 $I_{OUT} = 1.5A$

図 6-64. ラインステップ : 1.8V～5V、 $I_{OUT} = 1mA$

図 6-65. ラインステップ : 5V～1.8V、 $I_{OUT} = 1mA$

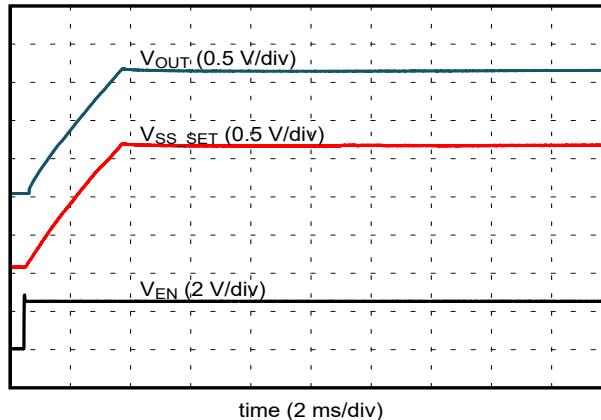

## 6.7 代表的特性 (続き)

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.8V$ 、 $V_{BIAS} = 5V$ 、 $I_{OUT} = 1A$ 、 $C_{OUT} = 2 \times 100\mu F$ 、 $C_{SS} = 4.7\mu F$ 、 $R_{REF} = 12.0k\Omega$ 、 $R_{BIAS} = 10\Omega$ 、 $C_{BIAS} = 4.7\mu F$ 、 $T_A = 25^\circ C$ 、特に記述のない限り、積分ノイズは 10Hz～100kHz の帯域幅で報告。

図 6-66. スタートアップ波形

## 7 パラメータ測定情報

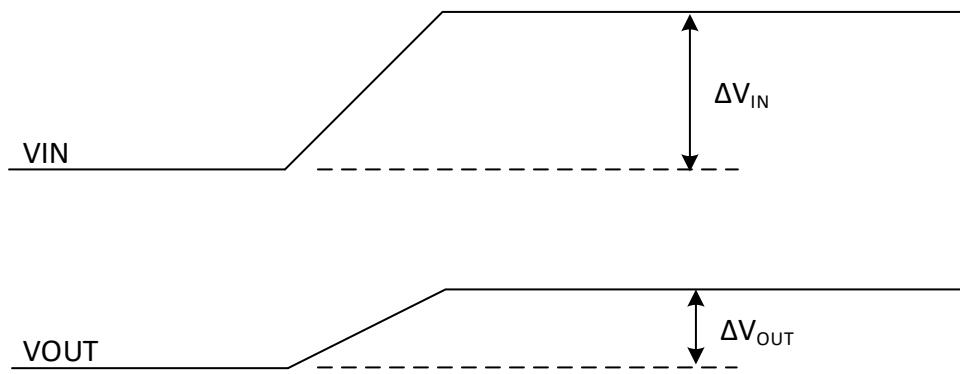

- A.  $\Delta V_{OUT} / \Delta V_{IN} = 3\mu V/V$  (標準値)。これは、 $V_{IN}$  が 1V 変化すると ( $\Delta V_{IN} = 1V$ )、 $V_{OUT}$  が 3 $\mu V$  変化する ( $\Delta V_{OUT} = 3\mu V$ ) ことを意味します。ラインレギュレーションは DC パラメータであるため、この波形は過渡がなくなった後、または  $V_{IN}$  のスルーレートが遅い場合にのみ有効であると考える必要があります。

図 7-1. ライン レギュレーション

- A.  $\Delta V_{OUT} / \Delta I_{OUT} = 500\mu V/A$  (標準値)。これは、 $I_{OUT}$  が 1A 変化すると ( $\Delta I_{OUT} = 1A$ )、 $V_{OUT}$  が 500 $\mu V$  変化する ( $\Delta V_{OUT} = 500\mu V$ ) ことを意味します。ロードレギュレーションは DC パラメータであるため、この波形は過渡がなくなった後、または  $I_{OUT}$  のスルーレートが遅い場合にのみ有効であると考える必要があります。

図 7-2. ロード レギュレーション

## 8 詳細説明

### 8.1 概要

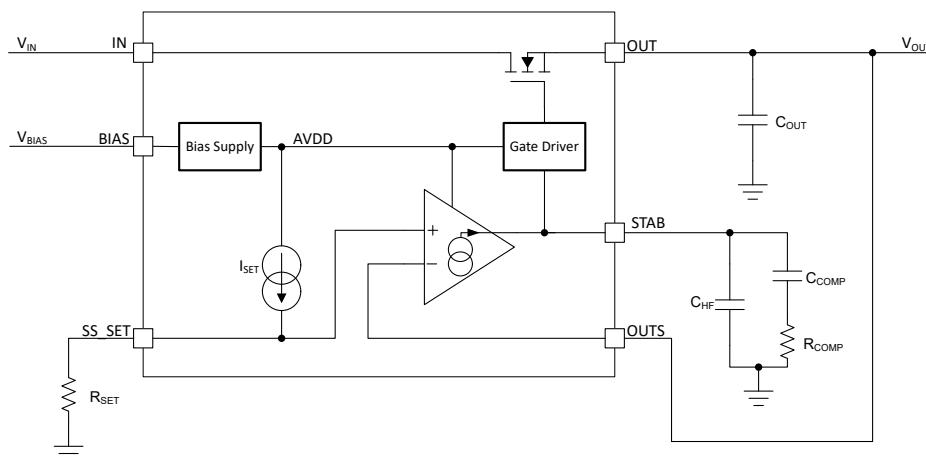

TPS7H1111 (TPS7H1111-SP および TPS7H1111-SEP) は超低ノイズ、高 PSRR、低ドロップアウトのリニア レギュレータ (LDO) で、宇宙環境での RF デバイスへの電力供給用に最適化されています。NMOS パス素子を使用し、0.85V～7V の入力範囲にわたって最大 1.5A の電流を供給できます。BIAS ピン (2.2V～14V) によりバイアス レールを使用できるため、 $V_{IN}$  と  $V_{OUT}$  の差が小さい動作が可能となり、消費電力が制限されます。このデバイスは、非常にクリーンな出力 レールを生成し、最小限の外付け部品で構成できます。

放射線性能と、低ノイズおよび高 PSRR 動作により、TPS7H1111 は人工衛星のノイズに敏感な部品への電力供給に理想的です。高性能なこのデバイスは、電源で発生する位相ノイズとクロックのジッタを制限できるため、高性能 ADC、DAC、VCO、PLL、SerDes、および他の RF 部品への電力供給に最適です。

デジタル負荷 (例:ASIC、FPGA、DSP) で低入力電圧、低出力電圧の動作を必要とする場合、TPS7H1111 の非常に優れた精度 (ライン、負荷、温度範囲全体にわたって  $+1.2\% / -1.3\%$ )、リモート センシング、優れた過渡性能、ソフト スタート機能によって、最適なシステム性能を実現できます。

さらに、このレギュレータにはさまざまな機能が組み込まれているため、電気系統が簡素化され、システムの柔軟性が向上します。これらの機能には、イネーブル機能 (EN)、構成可能なパワー グッド出力 (PG)、ソフト スタート制御 (SS\_SET)、動作を構成可能な内部電流制限 (CLM)、外部ループ補償 (STAB) が含まれます。

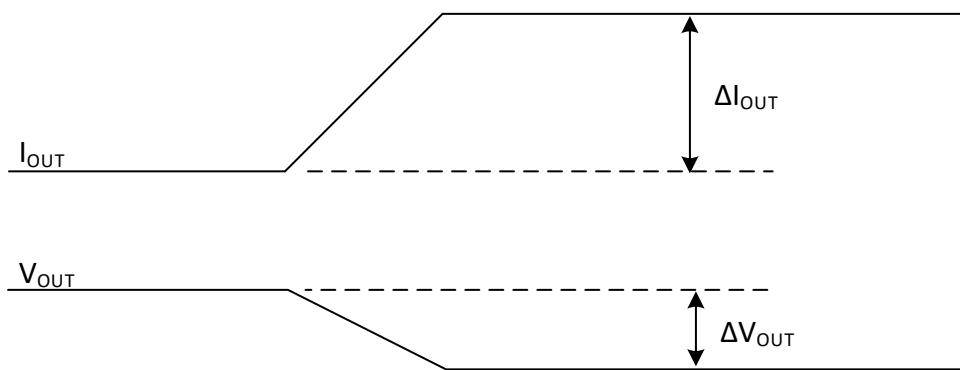

### 8.2 機能ブロック図

## 8.3 機能説明

### 8.3.1 バイアス電源

デバイスを正常に動作させるには、バイアス電源を **BIAS** ピンに接続する必要があります。ヘッドルーム電圧および出力電流の条件に応じて、バイアス電源電圧は、入力電圧電源と同じにすることも、別の高い電圧電源にすることもできます。ヘッドルーム電圧は、動作時の  $V_{IN}$  条件と  $V_{OUT}$  条件との差として定義されます ( $V_{headroom} = V_{IN} - V_{OUT}$ )。いずれの場合も、 $V_{BIAS}$  と  $V_{IN}$  の間にシーケンシング要件はありません。

表 8-1 で説明したように、ヘッドルーム電圧が 1.6V 以上の場合、別の高いバイアス電源は必要ありません。ヘッドルーム電圧が 1.6V 未満の場合、最高の性能を得るには、別の高いバイアス電源電圧が必要です。表 8-1 に示すすべての状況で、規定のドロップアウト電圧で 1.5A の最大出力電流を達成できます (「[電気的特性](#)」表を参照)。

**表 8-1. 最大パフォーマンス動作のバイアス レール要件**

| ヘッドルーム ( $V_{IN} - V_{OUT}$ ) | バイアス要件 <sup>(1)</sup>                                    |

|-------------------------------|----------------------------------------------------------|

| $\geq 1.6V$                   | $V_{IN}$ と同じ、または $V_{BIAS} \geq V_{IN}$ となる電圧レールを使用      |

| $< 1.6V$                      | $V_{IN}$ とは別の電圧レールを使用 ( $V_{BIAS} \geq V_{OUT} + 1.6V$ ) |

(1) いずれの場合も  $2.2V \leq V_{BIAS} \leq 14V$

表 8-2 に、標準電圧レールで実現可能で、1.5A の最大出力電流をサポートできる  $V_{BIAS}$ 、 $V_{IN}$ 、 $V_{OUT}$  の組み合わせの例を示します。ここに示すように、12V バイアス電源は、リストに記載されているすべての標準出力電圧レールをサポートします (通常は 5V 電源でも十分です)。また、 $V_{BIAS}$  電圧と  $V_{IN}$  電圧が同じ場合は、個別の電源は必要ありません。

**表 8-2. 最大性能で動作させるためのバイアス レールと標準レールの例**

| $V_{BIAS}$ (V) | $V_{IN}$ (V)  | $V_{OUT}$ (V) |

|----------------|---------------|---------------|

| 12             | 5             | 3.3           |

|                | 5、3.3         | 2.5           |

|                | 5、3.3、2.5     | 1.8           |

|                | 5、3.3、2.5、1.8 | 1.1           |

| 5              | 5、3.3         | 2.5           |

|                | 5、3.3、2.5     | 1.8           |

|                | 5、3.3、2.5、1.8 | 1.1           |

| 3.3            | 3.3、2.5、1.8   | 1.1           |

一般的には上記のバイアス電圧要件に従うことが推奨されますが、実現不可能な場合もあります (ヘッドルームが小さく、個別のバイアス電圧レールが利用できない場合など)。この場合でも、TPS7H1111 を動作させることは可能ですが、出力電流が小さくなります (PSRR などの性能が低下する可能性もあります)。この条件 ( $V_{BIAS} = V_{IN}$ 、ヘッドルームが小さい) は、「[電気的特性](#)」の表で「 $V_{BIAS} = V_{IN}$  でのドロップアウト電圧」として規定されています。結果のドロップアウト電圧要件を満たすと、本デバイスで適切な動作が維持されます。

サポートされている組み合わせで最大性能が得られない可能性のある例として、 $V_{BIAS} = V_{IN} = 5V$ 、 $V_{OUT} = 3.3V$  の場合があります。5V レールの許容誤差が 5% で、3.3V 出力の仕様最大許容誤差が +1.2% であるとすると、ワーストケースのヘッドルームは  $V_{headroom} = 4.75 - 3.34 = 1.41V$  です。この 1.41V は推奨される 1.6V 未満です。ただし、「[電気的特性](#)」表に示すように、このヘッドルームは全負荷電流 1.5A で必要とされるドロップアウトよりも大きいので、最大電流がサポートされることが予測されますが、他のパラメータ (PSRR など) は最大性能が得られない可能性があります。

バイアスレール上のノイズは、 $PSRR_{BIAS}$  仕様によって減衰されてから、出力に結合されます。バイアスレールが超クリーンなレールでない限り、このノイズ結合がクリーンな出力電圧の生成を制限する要因となります。そのため、RC フィルタを使用して **BIAS** ピンへのノイズ入力を最小限に抑える必要があります。**BIAS** ピンには低電流要件があるため、これは可能です。**BIAS** ピンから出力電圧へのノイズ伝搬を最小限に抑えるには、通常は  $10\Omega$  と  $4.7\mu F$  で十分です。発生する IR

の電圧降下によってバイアス電圧が正常な動作には低くなりすぎることがないように、十分に低い抵抗値を選択する必要があります。

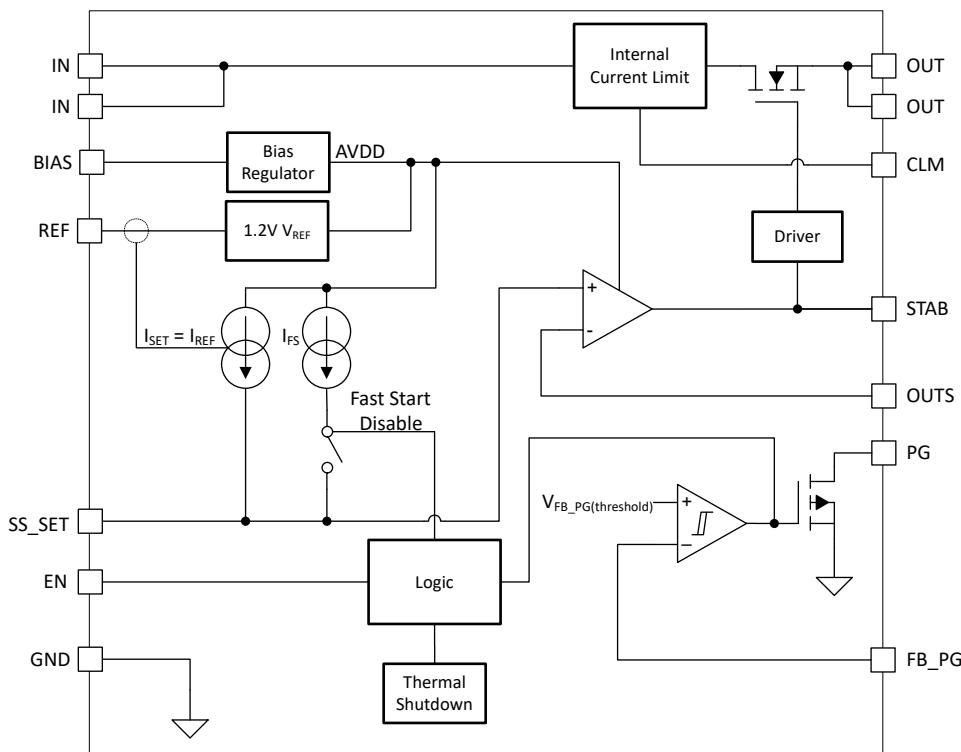

### 8.3.2 出力電圧構成

TPS7H1111 の出力電圧は、SS\_SET ピンと GND の間に抵抗  $R_{SET}$  を配置することで設定されます。公称動作では、SS\_SET ピンから  $100\mu\text{A}$  が output されます。 $R_{SET}$  を適切に選択すると、SS\_SET ピンに必要な出力電圧は式 1 で計算されます。この電圧は、図 8-1 に示すように、内部ユニティゲイン誤差アンプを介して出力に複製されます。

$$V_{SS\_SET} = I_{SET} \times R_{SET} \quad (1)$$

ここで、

- $I_{SET} = 100\mu\text{A}$  (標準値)

- $V_{SS\_SET}$  = 目的の出力電圧  $V_{OUT}$  に構成された設定電圧

図 8-1. 出力電圧構成の概略回路図

$100\mu\text{A}$  のリファレンス電流は、REF ピンと GND との間に  $12\text{k}\Omega$  抵抗を配置することで構成されます。 $R_{REF}$  抵抗の両端に  $1.2\text{V}$  を印加すると、約  $100\mu\text{A}$  のリファレンス電流が生成されます。この電流は SS\_SET ピンにミラーリングされ、高精度のリファレンス電流を生成します。電流を正確に設定するため、一般的には  $R_{REF}$  および  $R_{SET}$  には  $0.1\%$  精度の抵抗が推奨されます。 $0.1\%$  精度の抵抗を使用すると、 $R_{REF}$  抵抗による  $I_{SS\_SET}$  誤差は  $0.1\%$  になります。また、 $R_{SET}$  抵抗の  $0.1\%$  の誤差は、 $V_{OUT}$  の精度誤差にも影響します。TPS7H1111 の精度仕様は、ライン、負荷、温度の全範囲にわたって  $+1.2\% / -1.3\%$  ですが、抵抗の許容誤差は別途追加する必要があります。表 8-3 に、一般的な出力電圧と抵抗値を示します。

**表 8-3.  $V_{OUT}$  に対する  $R_{SET}$  の値**

| 出力電圧、 $V_{OUT}$ | 許容誤差 0.1% の抵抗の値 |

|-----------------|-----------------|

| 0.4V            | 4.02k $\Omega$  |

| 0.7V            | 6.98k $\Omega$  |

| 1V              | 10k $\Omega$    |

| 1.1V            | 11k $\Omega$    |

| 1.2V            | 12k $\Omega$    |

| 1.5V            | 15k $\Omega$    |

| 1.8V            | 18k $\Omega$    |

| 2.5V            | 24.9k $\Omega$  |

| 3.3V            | 33.2k $\Omega$  |

| 4V              | 40.2k $\Omega$  |

| 5V              | 49.9k $\Omega$  |

さらに、より高い精度が必要な場合は、マッチングされた抵抗を利用できます（多くの場合、0.1% よりも優れた精度比で提供）。たとえば、 $R_{REF}$  に公称  $12\text{k}\Omega \pm 5\%$  の抵抗を選択し、 $R_{SET} / R_{REF}$  比が 0.01%（またはそれ以下）になるようなマッチングされた抵抗を使用できます。この場合、設定電圧を計算には式 1 の代わりに式 2 を使用します。

$$V_{SS\_SET} = (1.2 / R_{REF}) \times R_{SET} \quad (2)$$

ここで、

- $V_{SS\_SET}$  = 目的の出力電圧  $V_{OUT}$  に構成された設定電圧

式 2 を使用すると、 $R_{REF}$  と  $R_{SET}$  抵抗のミスマッチによる設定出力電圧の誤差を簡単に計算できます。ただし、抵抗比を改善すると出力精度が向上する可能性がありますが、他の誤差発生源は依然として存在します。これらの発生源には、固有のリファレンス電流精度と誤差アンプのオフセット電圧が含まれます。

出力電圧精度  $V_{ACC}$  は、「電気的特性」表で最小精度 -1.3%、最大精度 +1.2% と規定されています。この仕様は、-55°C～125°C の温度範囲全体、全入力電圧 ( $0.85\text{V} \leq V_{IN} \leq 7\text{V}$  および  $2.2\text{V} \leq V_{BIAS} \leq 14\text{V}$ )、および全負荷 ( $1\text{mA} \leq I_{OUT} \leq 1.5\text{A}$ ) に適用されます。測定に関する追加の詳細は、次のとおりです。

- $V_{IN}$ 、 $V_{BIAS}$ 、 $I_{OUT}$ 、温度の範囲は、仕様がすべてのライン、負荷、温度の組み合わせに適用されることを意味します。これは、さまざまなコーナーを網羅する複数のバイアス条件をテストすることにより達成されています。

- 「電気的特性」の脚注 4 には、 $V_{BIAS} \geq V_{IN}$  および  $V_{BIAS} \geq V_{OUT} + 1.6\text{V}$  が規定されています。これは、 $V_{IN}$  と  $V_{BIAS}$  のすべての組み合わせが実現可能ではないためです（たとえば、 $V_{IN} = 7\text{V}$  および  $V_{BIAS} = 2.2\text{V}$  はあり得ません）。

- 「電気的特性」の脚注 5 には、測定時の消費電力が最大 4W に制限されていると記載されています。これは、テストの熱的制限によるものです。熱特性に優れた代表的なアプリケーション ボードには、固有の制限はありません。

- より堅牢な測定精度を実現するため、テスト条件では 0mA ではなく 1mA の最小値が規定されています。ただし、通常のアプリケーションでは、TPS7H1111 デバイスに安定性のための最小負荷電流はありません。

- TID 後の仕様は、室温で測定されます（高温でのアニーリングを防止するための MIL 規格）。TID 後の TPS7H1111 は、最小精度 -0.7%、最大精度 +1.1% と規定されています。これを、TID 前の最小精度 -0.7% および最大精度 +0.9% と比較します。

- 次の誤差項は  $V_{ACC}$  パラメータ自体で対処されるため、 $V_{ACC}$  仕様に含めることは推奨されません： $I_{SET}$  電流精度、 $V_{OS}$ （出力オフセット電圧）、 $V_{REF}$  電圧精度、 $\Delta V_{OUT}/\Delta V_{IN}$ （ラインレギュレーション）、 $\Delta V_{OUT}/\Delta I_{OUT}$ （ロードレギュレーション）、 $V_{OUTtempco}$ 。

- $R_{REF}$  や  $R_{SET}$  抵抗の許容誤差などの外付け部品による誤差は、パラメータに含まれていないため、 $V_{ACC}$  仕様に追加できます。

出力電圧の精度を決定する方法の詳細については、セクション 9.2.1.2.3 を参照してください。

### 8.3.3 電圧源を使用した出力電圧構成

TPS7H1111 の出力電圧は **SS\_SET** 電圧 (からオフセット誤差を減算した電圧) と等しいため、**SS\_SET** に電圧を供給して TPS7H1111 を構成することも可能です。図 8-2 に示すように、電圧源  $V_{SET}$  を **SS\_SET** に供給します。DAC を電圧源として使用すると、構成可能な電圧制御が可能になります。

図 8-2. **SS\_SET** に電圧源を供給して出力電圧を構成する概略回路図

この方法を使用する場合、いくつかの固有の考慮事項があります。

- **SS\_SET** に電圧源を供給する場合、超低ノイズのリファレンス電流に依存する代わりに、 $V_{SET}$  のノイズがユニティゲイン誤差アンプを介して出力に渡されます。ノイズを最小限に抑えるため、図に示すように、 $V_{SET}$  と **SS\_SET** の間に RC フィルタを使用することをお勧めします。

- TPS7H1111 の出力電圧は **SS\_SET** に直接追従するため、スタートアップ中にソフトスタートはありません。必要なソフトスタート時間を確保するため、 $V_{SET}$  電圧のスルーレートを制御することをお勧めします。 $V_{SET}$  と **SS\_SET** の間に RC フィルタを配置すると、このスルーレートの制御に役立つ場合があります。

- **SS\_SET** ピンは、動作中は公称  $100\mu\text{A}$  を出力し、「ソフトスタート」時 ( $V_{FB\_PG} < V_{FB\_PG(rising)}$ ) は  $2.1\text{mA}$  を出力します。この電流を処理するために、シャント抵抗が必要になることがあります。

### 8.3.4 イネーブル

イネーブル ピンが **Low** になると、デバイスはシャットダウン モードに移行し、出力電圧のレギュレーションは行われません。通常、 $V_{IN}$  と **GND** の間に外付け分圧抵抗を使用して **EN** を供給します。式 3 に示すように、目的のプリセット入力電圧に達したときにデバイスをオンにするよう、抵抗のサイズを適切に設定できます。

$$V_{IN(rising)} = V_{EN(rising)} \times (R_{EN\_TOP} + R_{EN\_BOT}) / R_{EN\_BOT} \quad (3)$$

同様に、 $V_{IN(falling)}$  電圧も式 4 を使用して計算できます。 $V_{IN(rising)}$  と  $V_{IN(falling)}$  は、構成可能な UVLO (低電圧誤動作防止) スレッショルドと考えることができます。

$$V_{IN(falling)} = V_{EN(falling)} \times (R_{EN\_TOP} + R_{EN\_BOT}) / R_{EN\_BOT} \quad (4)$$

TPS7H1111 は  $V_{EN}$  が  $0.6\text{V}$  (標準値) になった時点でオンになりますが、 $V_{EN}$  の最終値は  $0.8\text{V}$  を超えるようにすることを推奨します。これは、通常動作時にイネーブル スレッショルドの上に適切なマージンを確保し、重イオン暴露中の SEFI を防ぐためです。この推奨事項は、式 5 を満たすことで達成されます。

$$V_{IN(falling)} \times R_{EN\_BOT} / (R_{EN\_TOP} + R_{EN\_BOT}) = V_{EN(falling)} > 0.8\text{V} \quad (5)$$

または、**EN** ピンをマイクロコントローラまたは FPGA から直接駆動することもできます。イネーブル ピンの電圧スレッショルドは低いため、 $1.1$ 、 $1.8$ 、 $2.5$ 、 $3.3\text{V}$  のロジック レベルをサポートできます。同様に、 $V_{EN}$  の最終値が  $0.8\text{V}$  を上回るようすることを推奨します。これは通常、標準ロジック レベルで簡単に達成できます。

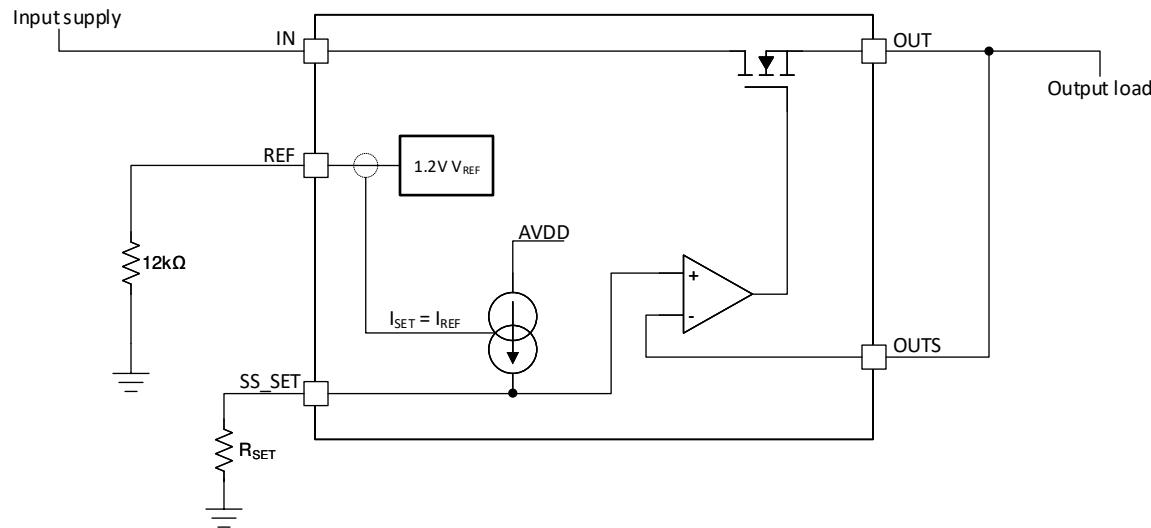

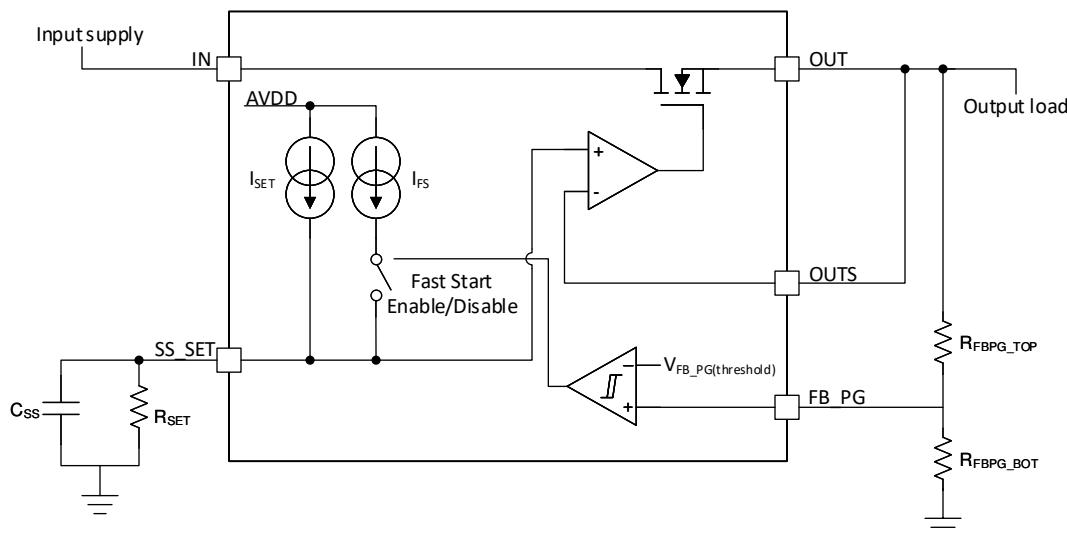

### 8.3.5 ソフトスタートとノイズ低減

**SS\_SET** ピンは、出力電圧の設定に加えて、ソフトスタート時間のプログラミングと、内部リファレンス電流用のノイズ フィルタの作成という 2 つの重要な機能を果たします。ほとんどのアプリケーションでは、十分な低ノイズ性能を得るために、少なくとも  $4.7\mu\text{F}$  コンデンサが推奨されます。より大きな値のコンデンサも許容されますが、コンデンサの値を  $4.7\mu\text{F}$  より大きくしていくと、出力ノイズ減少の効果はだいに減少します。

このコンデンサは、**SS\_SET** 電圧のランプ レートも低下させるため、LDO のターンオン時間（ソフトスタート）を制御します。ただし、コンデンサが  $I_{SET}$  電流（公称  $100\mu\text{A}$ ）によってのみ充電される場合は、スタートアップ時間が過剰になります。そのため、スタートアップ中にアクティブになる追加の高速充電電流源 ( $I_{FS} \approx 2\text{mA}$ ) があります。その結果、 $4.7\mu\text{F}$  コンデンサのソフトスタート時間は公称  $3.7\text{ms}$  となります。図 8-3 に、この回路の概略図を示します。

図 8-3. スタートアップ回路を示す概略回路図

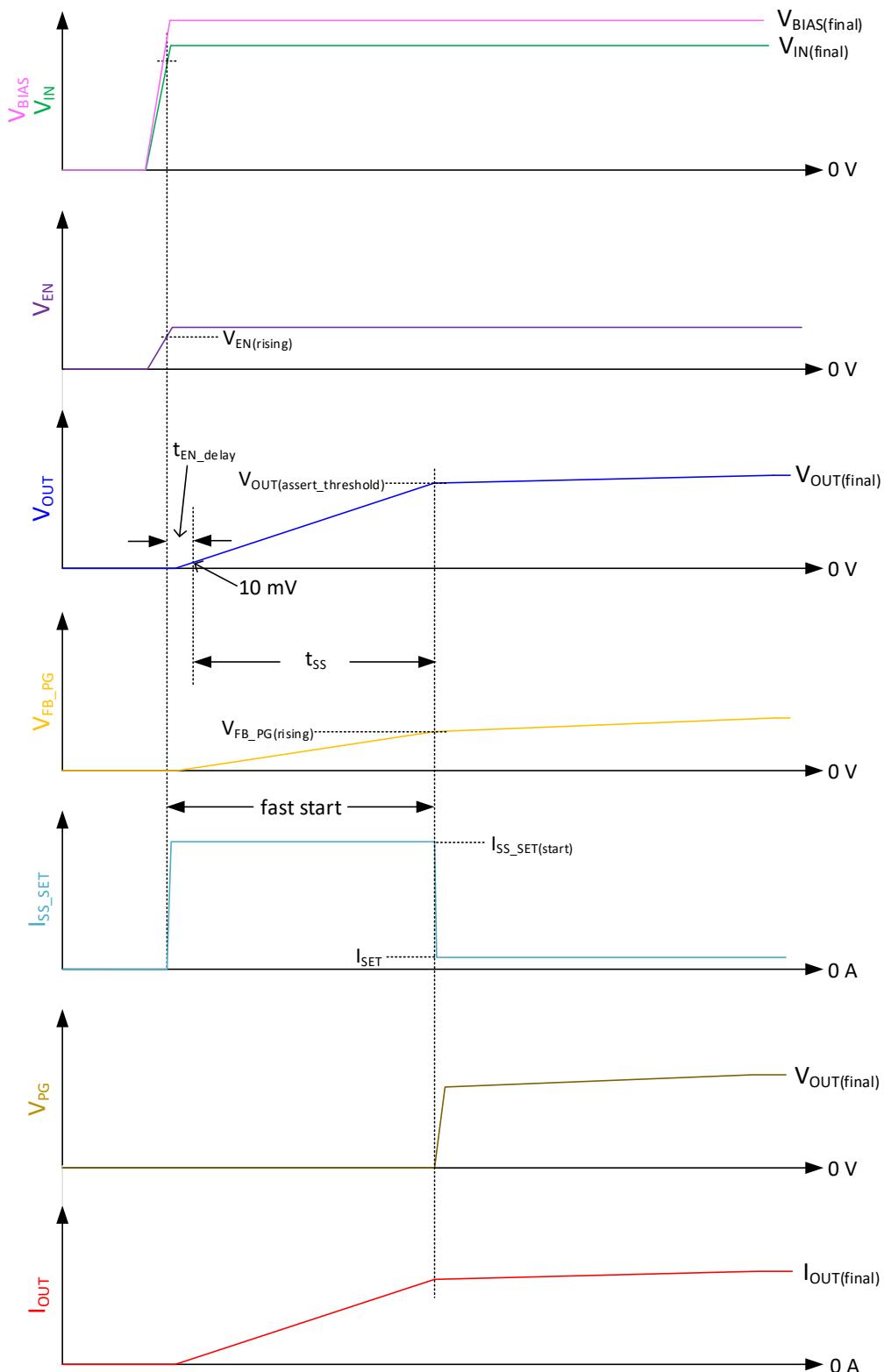

この高速充電回路は、**FB\_PG** スレッショルド（標準  $300\text{mV}$ ）に達するまでアクティブになります。**FB\_PG** スレッショルドに達すると、高速スタート電流はオフになります。[式 6](#) に示すソフトスタート時間が完了します。 $C_{SS}$  は、 $100\mu\text{A}$ （標準値）のリファレンス電流で、最終的な値（ $R_{SET}$  抵抗により決定）まで充電を継続します。図 8-4 に、スタートアップ波形の例を示します。この波形では、分圧された  $V_{IN}$  が **EN** に供給されていると想定しています。

$$t_{SS} \approx C_{SS} \times V_{OUT(assert\_threshold)} / I_{SS\_SET(startup)} \quad (6)$$

ここで、

- $t_{SS}$  = ソフトスタート時間

- $I_{SS\_SET(startup)} = I_{FS} + I_{SET} = 2.1\text{mA}$ （標準値）

- $V_{(assert\_threshold)}$  = **PG** がアサートされる  $V_{OUT}$  の構成値（通常は  $V_{OUT(final)}$  の 90%、[セクション 8.3.6](#) を参照）

高速充電電流 ( $I_{FS}$ ) と設定電流 ( $I_{SET}$ ) は、ソフトスタート時間 ( $t_{SS}$ ) 中はどちらもアクティブであり、「電気的特性」表に  $I_{SS\_SET(start)}$  として示されています。この  $2.1\text{mA}$  の標準値は、 $12\text{k}\Omega$  の  $R_{REF}$  抵抗に対して有効です。高速充電電流は  $R_{REF}$  抵抗を流れる電流から内部的に生成されるため、 $12\text{k}\Omega$  より大きいまたは小さい値を使用すると、 $I_{FS}$  電流が減少または増加します。

高速スタート回路が不要な場合は、**FB\_PG** ピンを  $V_{OUT}$  に接続します。これにより、**FB\_PG** スレッショルドに短時間で到達するため、高速スタート回路が迅速にオフになります。これは、[セクション 8.3.6](#) で説明しているように、**PG** ピンの動作に影響することに注意してください。

図 8-4. スタートアップ波形を示す概略回路図

### 8.3.6 構成可能なパワー グッド

パワー グッド インジケータ ピン (PG) は、出力電圧が目的の値に達するとアサートされるオープンドレイン ピンです。PG ピンは、抵抗を介して  $V_{OUT}$ 、 $V_{IN}$ 、または推奨最大電圧 7V 未満の別の電圧レベルにプルアップできます。PG によりシンクされる最大電流が推奨動作条件電流の最大値である 2mA 未満に維持されるように抵抗のサイズを選択してください。

$V_{IN}$  または  $V_{BIAS}$  がデバイスに供給される前に PG を外部電圧にプルアップした場合、駆動強度が不十分なため PG がプルダウンされない可能性があることに注意してください。「電気的特性」表に規定されている  $V_{IN(MIN\_PG)}$  は、0.6mA 以下で PG を 0.5V 未満にプルダウンするのに十分なプルダウン強度が PG に供給されるようにするために、 $V_{IN}$  または  $V_{BIAS}$  のいずれかが到達する必要がある最小値です。 $V_{IN}$  と  $V_{BIAS}$  がそれぞれの適切な最終電圧に達すると、PG ピンの駆動能力は最大になります。

分圧抵抗を介して FB\_PG ピンに出力電圧を供給することで、PG のアサート レベルを構成できます。FB\_PG ピンの標準スレッショルドは 300mV です。このスレッショルド以上になると、PG ピンがアサートされます。式 7 に、PG がアサートされている場合に  $V_{OUT}$  値を計算する方法を示します (FB\_PG ピンのリーク電流は、影響が最小限であるため考慮されていません)。セクション 8.3.5 で説明されているように、このレベルに達すると、高速スタート回路もオフになります。

$$V_{FB\_PG(rising)} = V_{OUT(assert\_threshold)} \times R_{FBPG\_BOT} / (R_{FBPG\_TOP} + R_{FBPG\_BOT}) \quad (7)$$

最終出力電圧に達した時点で PG が確実にアサートされるようにするには、出力電圧のワーストケースの許容誤差、FB\_PG スレッショルド、抵抗の許容誤差レベルを考慮する必要があります。通常、 $V_{(assert\_threshold)}$  が  $V_{OUT(final)}$  の 90% 以下になるように分圧抵抗を構成すれば十分です。

PG のデアサート スレッショルドは、式 8 を使用して計算することもできます。

$$V_{FB\_PG(rising)} - V_{FB\_PG(hysteresis)} = V_{OUT(deassert\_threshold)} \times R_{FBPG\_BOT} / (R_{FBPG\_TOP} + R_{FBPG\_BOT}) \quad (8)$$

PG ピンを使用しない場合は、グランドにプルダウンできます。ただし、セクション 8.3.5 に示す高速スタート回路が必要な場合は、FB\_PG ピンを適切に構成する必要があります。

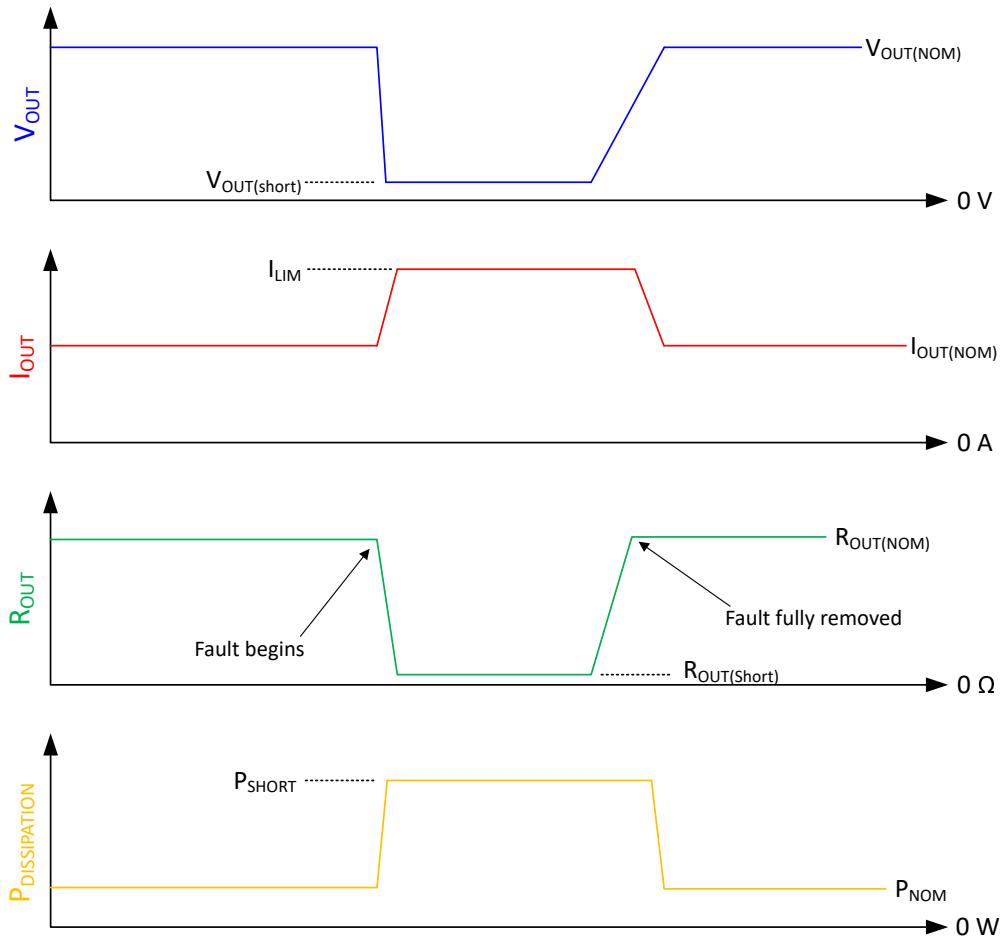

### 8.3.7 電流制限

内部電流制限  $I_{LIM}$  は電流制限値です。電流制限動作には、CLM ピンの値によって 2 種類あります。CLM が High のときは、ブリックウォール電流制限があります。CLM が Low のときは、ターンオフ電流制限があります。電流制限動作を制御するため、CLM は  $V_{IN}$  または GND に直接接続できます。デバイスがイネーブルのときにこのピンの値を変更しないでください。また、このピンはフローティングにしないでください。

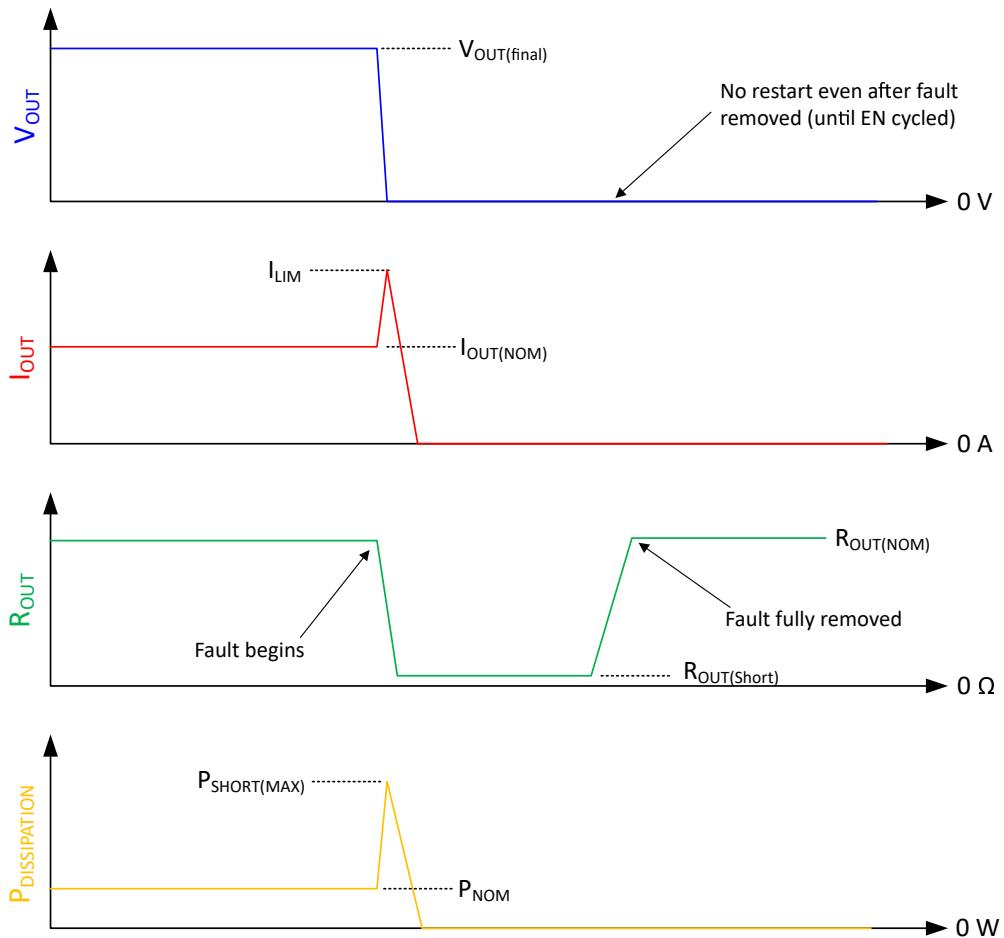

図 8-5 に、ブリックウォール電流制限 (定電流制限) を示します。このモードでは、 $I_{LIM}$  に達し、電流制限回路に応答する時間がある場合、TPS7H1111 LDO は定電流レギュレーション モードに入ります。つまり、出力電流を  $I_{LIM}$  に維持するのに必要な値まで出力電圧が降下します。障害が解消されると、デバイスはレギュレーションを再開します。通常、障害中は SS\_SET ピンを Low にプルダウンして  $C_{SS}$  コンデンサを迅速に放電するため、初期のスタートアップ時と同じソフトスタート時間があります。ただし、障害が非常に短時間である場合、 $C_{SS}$  コンデンサが完全に放電されないことがあります。その場合はスタートアップ時間が短くなります。

ブリックウォール電流制限では消費電力が大きいため、TPS7H1111 がサーマル シャットダウンに移行し、温度が十分に下がってサーマル シャットダウンが終了するまで、デバイスのレギュレーションは停止します。

## 警告

TPS7H1111 は、ブリックウォール電流制限モードに無限にとどまるようには設計されていません。

図 8-5. ブリックウォール電流制限波形の概略図 (CLM High)

CLM が Low のときは、ターンオフ電流制限があります。その動作を図 8-6 に示します。ターンオフ電流制限では、電流制限  $I_{LIM}$  に達すると、TPS7H1111 LDO はレギュレーションを停止します (約  $28\mu\text{s}$  の短い遅延後)。EN がサイクル (Low に移行してから High に移行) するまで、LDO はレギュレーションを再開しません。

ターンオフ電流制限の主な利点は、電流制限に達した後に大きな消費電力が持続しないことです。ただし、障害が解消された後にデバイスが自動的にレギュレーションを再開しないことが主な欠点です。したがって、外部モニタで障害がいつ発生したかを判定し、EN ピンをいつトグルするかを決定する必要があります。これは通常、PG ピンを監視する既存のデバイス (FPGA やマイクロコントローラなど) に簡単に実装できます。モニタが PG ピンのデアサートを検出したときに、EN をトグルしてレギュレーションの再開を試みることができます。

EN が High  $\rightarrow$  Low  $\rightarrow$  High とトグルする際、 $t_{EN\_LOW}$  ( $20\mu\text{s}$ ) 以上 Low となるようにする必要があります。また、再起動時に十分なソフトスタートを確保し、電流制限が再びすぐにかかるないようにするため、SS\_SET が公称値の 5% に放電されるまで EN をトグルしないことも推奨します。

図 8-6. ターンオフ電流制限波形の概略図 (CLM Low)

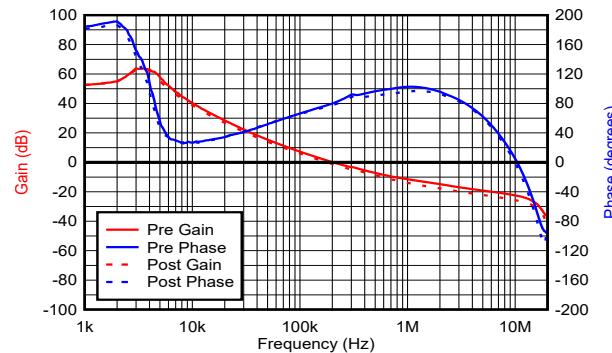

### 8.3.8 安定性

出力容量および寄生容量のデフォルト範囲内の推奨動作条件内で動作している場合、デフォルトの外部補償 ( $C_{COMP} = 4.7nF$ 、 $R_{COMP} = 5k\Omega$ ) で十分な安定性が得られます。

推奨動作条件とは異なる出力容量の部品を使用する場合は、異なる補償が必要になることがあります。安定性に影響を及ぼす主な要因は、出力容量、ESR (等価直列抵抗)、ESL (等価直列インダクタンス) です。詳細については、セクション 8.3.8.2 を参照してください。

安定性は、制御ループのボード線図を作成することで検証できます。これは、フィードバックパスに信号を注入することにより行うことができます。通常、OUT と OUTS の間にある  $5\Omega \sim 50\Omega$  の抵抗の両端に信号を注入します。この抵抗は、他の測定を行うときや公称動作中は取り外してください (または、 $0\Omega$  のシャントを使用してください)。位相マージンの一般的なターゲットは  $50^\circ$ 、ゲインマージンのターゲットは  $6dB$  です。

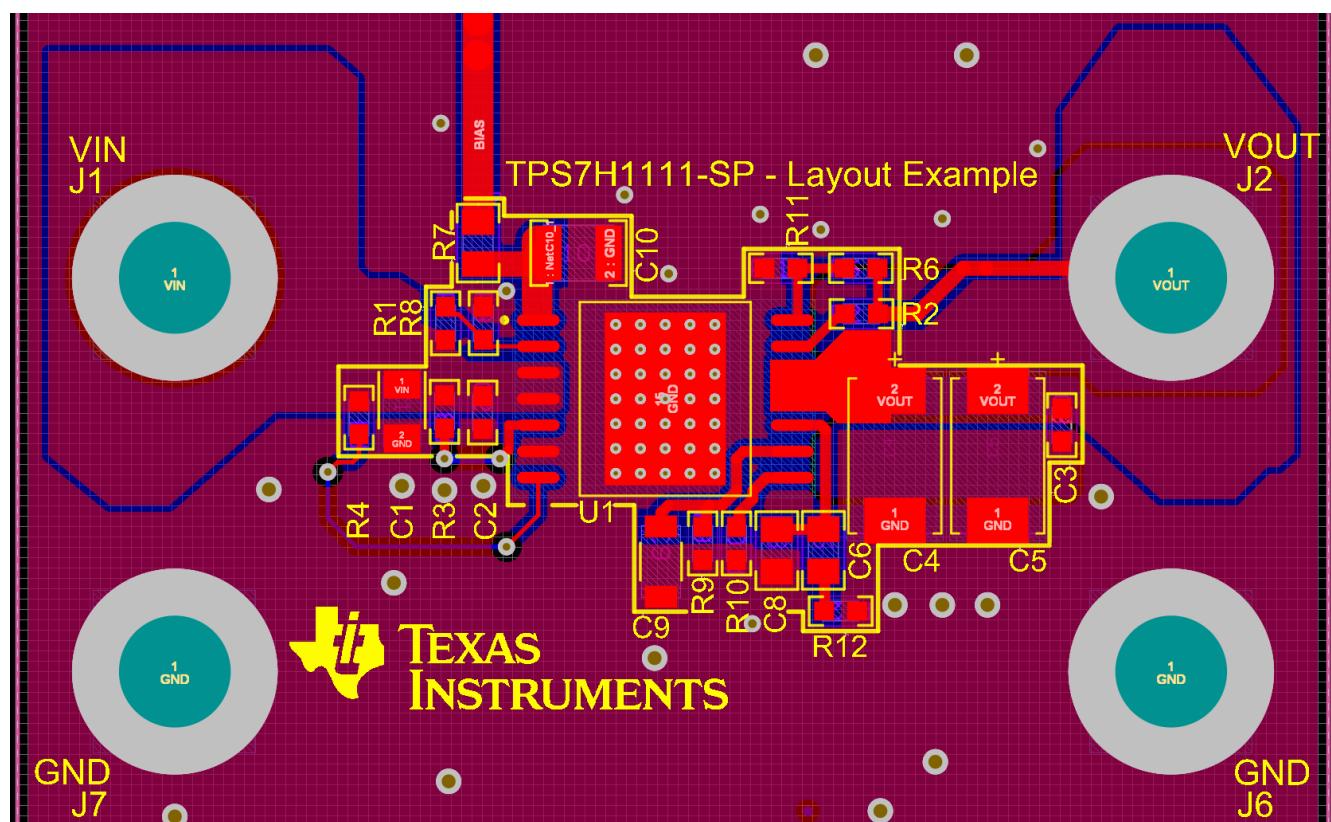

#### 8.3.8.1 出力容量

TPS7H1111 は、1 つの  $220\mu F$  タンタル出力コンデンサ、または 2 つの  $100\mu F$  コンデンサを使用するように最適化されています。許容される容量、ESR、ESL の全範囲は、「推奨動作条件」に規定されています。選択したコンデンサがすべての動作条件の要件を満たしていることを確認してください。また、1 つの  $0.1\mu F$  セラミックコンデンサを追加で使用することもできます。1 つまたは複数のタンタルコンデンサは TPS7H1111 の出力の近くに配置し、セラミックコンデンサは負荷ポイントの近くに配置します。

ESR (等価直列抵抗) は、コンデンサの周波数によって大きく異なるため、考慮する必要のある重要な寄生要素です。タンタルコンデンサの ESR 値は通常  $100kHz$  で規定され、「推奨動作条件」表の値は  $100kHz$  での値にほぼ対応しま

す。ただし実際には、TPS7H1111 制御ループの安定性に主に影響するのは、ループ クロスオーバー周波数での ESR です。ループ クロスオーバー周波数は、100kHz を上回ることも下回ることもあります。そのため、ESR 値の範囲は適切なガイドラインと考えることができますが、安定性を追加検証することができます。

また、容量、ESR、ESL の要件はバルク容量全体に対するものであることに注意してください。ESR が 40mΩ、ESL が 2nH の 100μF コンデンサを 2 つ使用する場合、合計容量は 200μF、ESR は 20mΩ、ESL は 1nH となります。これらの ESR および ESL の要件を考慮する際は、1 つのセラミック コンデンサは考慮しないでください。

0.1μF より大きいセラミック コンデンサは、共振周波数が低いため、通常は使用できません。この低い共振周波数は、通常は TPS7H1111 レギュレータのループ帯域幅内です (約 10MHz など)。そのため、低共振ポイントと低 ESR が組み合わさると、ループ帯域幅とデバイスの安定性に悪影響を及ぼします。帯域幅が狭いと PSRR に悪影響を及ぼすため、セラミック容量を追加する利点が失われます。

ただし、0.1μF を上回るセラミック コンデンサを使用する必要がある場合は、ループ帯域幅よりも対数スケールの比率で 10 ~ 20 高い共振周波数を持つセラミック コンデンサを使用することをお勧めします。または、直列抵抗を追加して ESR を増加させることもできます。これにより、強い共振ポイントを防止できます。

テキサス・インスツルメンツでは、さまざまな宇宙グレードのコンデンサのゲインマージンと位相マージンを測定し、良好な安定性マージンを実証しています。詳細については、[セクション 9.3](#) を参照してください。

標準的なバルク容量と 1 つの 0.1μF コンデンサ以外のコンデンサを使用する場合は、コンデンサとシステム全体をシミュレーションすることをお勧めします。また、ボード線図を作成し、実際のシステムで負荷ステップを実行して、安定性マージンが十分であることを確認することも推奨されます。

### 8.3.8.2 補償

図 8-7 に示すように、 $C_{COMP} = 4.7nF$ 、 $R_{COMP} = 5k\Omega$  での補償を利用して TPS7H1111 を補償することを推奨します。 $C_{HF}$  は必要ありません。

ただし、異なる制御ループ応答が必要な場合や、異なる出力容量、ESL、ESR を使用する場合は、異なる補償ネットワークが必要になることがあります。誤差アンプは OTA (トランスコンダクタンス オペアンプ) であるため、OTA に従来の補償技法を使用できます。テキサス・インスツルメンツは、推奨されるタイプ I 補償が最適であると考えていますが、図 8-7 にタイプ II 補償の例を示します。

図 8-7. 汎用タイプ II 補償

抵抗分圧器を使用してフィードバック ピンに供給するリニア レギュレータとは異なり、フィード フォワード コンデンサ ( $C_{FF}$ ) を使用して制御ループを変更することはできません。抵抗分圧器 LDO の場合、フィード フォワード コンデンサにより出力電圧とフィードバック ピンとの間に高周波短絡が発生します。ただし、TPS7H1111 アーキテクチャには分圧器はなく、代わりに出力電圧が誤差アンプの負の入力端子に直接供給されます。誤差アンプはユニティ ゲイン構成で動作するため、フィード フォワード コンデンサで通常得られるノイズの低減と PSRR の増加という利点が得られる可能性があります。

### 8.3.9 カレントシェア（電流共有）

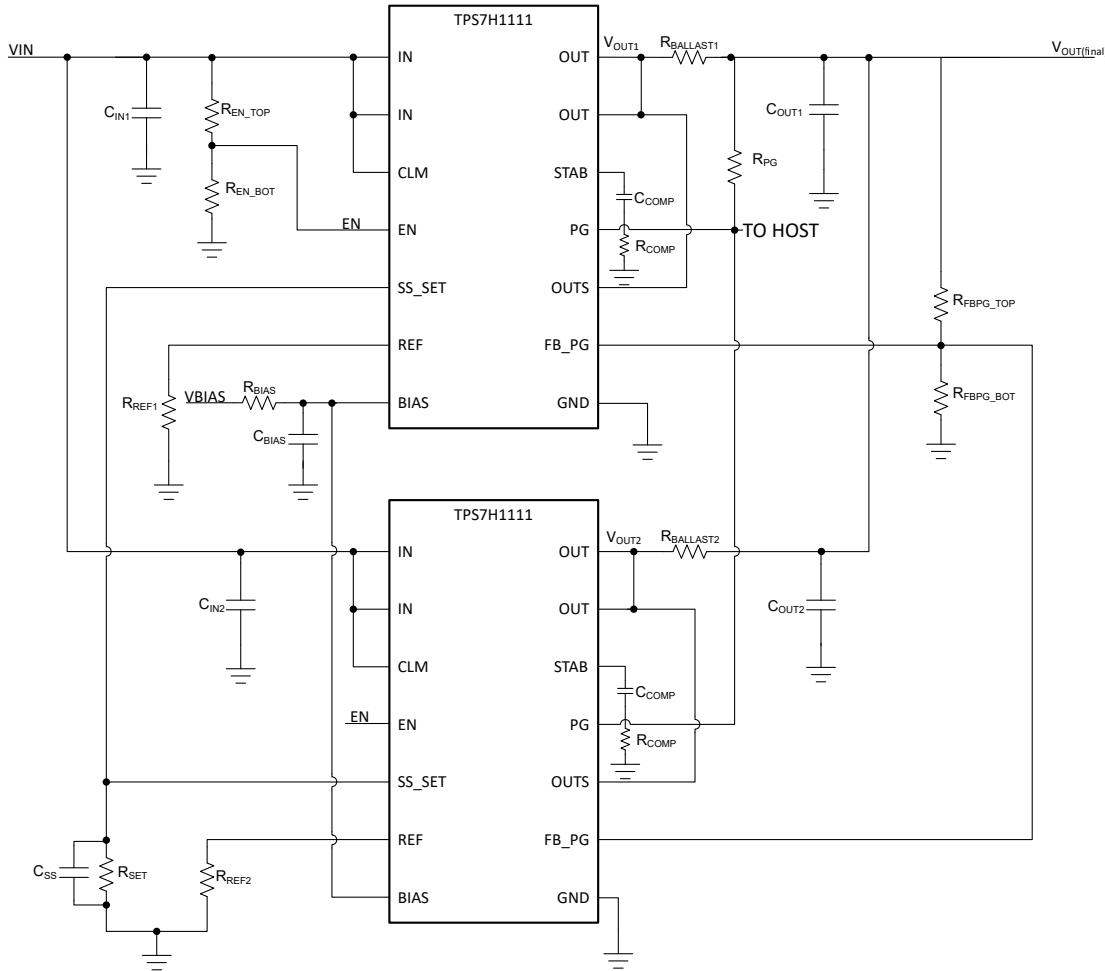

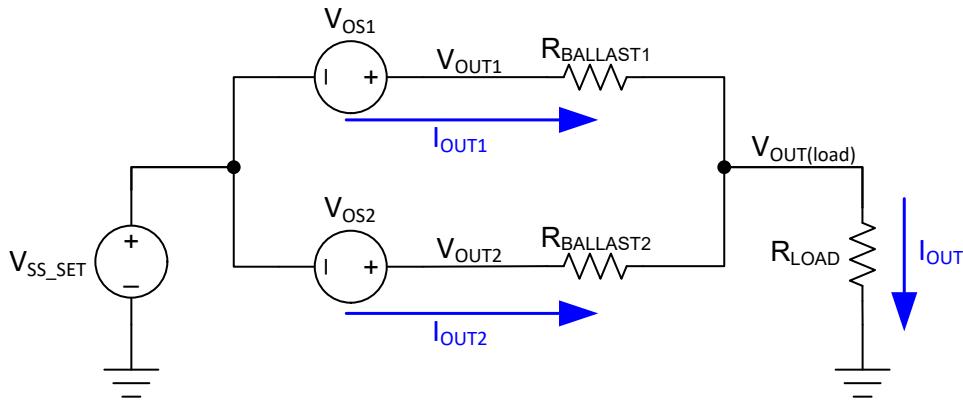

TPS7H1111 では、出力電流を増加させたり、放熱を分散させたりするため、複数デバイスの並列接続がサポートされています。1つのデバイスは 1.5A の電流を出力できますが、2つのデバイスで出力できる電流は 3A をわずかに下回ります。これは、各デバイスが正確に 50% の電流を供給しないためです。2つのデバイス間の電流のミスマッチは、各デバイスの誤差アンプのオフセット  $V_{OS}$  の差によるものです。リファレンス電流  $I_{SET}$  の差によるミスマッチは、 $SS\_SET$  ネットを互いに接続することで解消されます。これを、図 8-8 に概略回路図で示します。

抵抗を流れる電流は  $200\mu A$  (標準値) であるため、通常値の半分の  $R_{SET}$  抵抗を使用する必要があります。さらに、スタートアップ時間を等価にするため、 $C_{SS}$  コンデンサを 2つ (または通常値の 2倍のコンデンサを 1つ) 使用する必要があります。最後に、各デバイスは通常の出力容量を持つ必要があります。2つのデバイスを並列に接続すると、デバイスが 1つである場合に比べて  $V_{OUT(final)}$  の容量は 2倍になります。図 8-8 の出力コンデンサは、バラスト抵抗の後 (負荷に最も近い位置) に配置されています。この配置により、TPS7H1111 制御ループで見られるように、コンデンサにある程度の実効  $ESR$  が追加されます。バラスト抵抗の前の OUT ピンに直接コンデンサを追加することも可能ですが、出力コンデンサと負荷の間にバラスト抵抗が配置されるため、負荷ステップ中の電圧降下がわずかに大きくなる可能性があります。

最初に 2つのデバイス間のミスマッチを計算するには、合計出力電流  $I_{OUT}$ 、設定出力電圧  $V_{SS\_SET}$ 、各デバイスのオフセット電圧  $V_{OS}$ 、およびバラスト抵抗  $R_{ballast}$  が既知である必要があります。必要な電流マッチング要件を満たすようにバラスト抵抗を選択できますが、バラスト抵抗が大きいほど、バラスト抵抗の両端での  $IR$  降下によりロードレギュレーションが悪化することに注意してください。次に、合計出力電圧  $V_{OUT(final)}$  を式 9 を使用して計算する必要があります。これは、負荷で計測される電圧です。

$$V_{OUT(final)} = [(V_{SS\_SET} + V_{OS1}) + (V_{SS\_SET} + V_{OS2}) - I_{OUT} \times R_{ballast}] / 2 \quad (9)$$

次に、式 10 および式 11 を使用して各デバイスの電流を計算します。

$$I_{OUT1} = (V_{SS\_SET} + V_{OS1} - V_{OUT(final)}) / R_{ballast} \quad (10)$$

$$I_{OUT2} = (V_{SS\_SET} + V_{OS2} - V_{OUT(final)}) / R_{ballast} \quad (11)$$

この計算された電流を、各デバイスを流れる理想的な電流  $I_{OUT(total)} / 2$  と比較できます。

図 8-8. カレント シェアの概略回路図

各デバイスのオフセットを測定して、各デバイスから供給される正確な電流を決定するのが理想的です。これは一般的には実現不可能であるため、「電気的特性」に示すワーストケースのオフセットの使用を検討することが多いです。その場合、 $V_{OS1}$  は規定された最大  $V_{OS}$  に、 $V_{OS2}$  は規定された最小  $V_{OS}$  に設定されます。ただしこの場合、ミスマッチの予測が過剰に大きくなる可能性があります。分析を容易にするため、図 6-47、図 6-48、図 6-49 に、オフセットデータの測定された複数の単位のヒストグラムを示します。また、セクション 9.2.2 に示すように、計算結果よりも良い測定値が得られます。

図 8-9 に、カレント シェアと誤差の発生源を示す簡略図を示します。

図 8-9. カレント シェアの概略回路図

### 8.3.10 PSRR

TPS7H1111 の PSRR (電源除去比) は、 $V_{IN}$  での入力ノイズが出力  $V_{OUT}$  に達するまでに減衰される量です。これは、数学的には式 12 で定義されます。

$$PSRR = 20 \times \log(V_{IN(AC)} / V_{OUT(AC)}) \quad (12)$$

入力ノイズは通常、アップストリーム コンバータのスイッチング リップルが最大の要素です。このノイズは、スイッチング周波数とその高調波で発生します。

さまざまな条件下、異なる周波数における PSRR 値は、「電気的特性」および代表的特性の図 6-1～図 6-11 に示されています。TPS7H1111 は、広範な条件にわたって非常に優れた PSRR が得られるよう設計されています。PSRR をさらに向上するには、動作条件を微調整できます。通常、TPS7H1111 の PSRR は(重要順に)以下によって向上させることができます。

- 入力電源のヘッドルームの拡大 ( $V_{IN} - V_{OUT}$  の増加)

- バイアス電源のヘッドルームの拡大 ( $V_{BIAS} - V_{OUT}$  の増加)

- 出力電流の削減

- BIAS レールに使用する RC フィルタ サイズの増加 (バイアス電源がノイズの主な発生源である場合のみ)

以下の要因では、TPS7H1111 の PSRR はわずかに向上するだけです。

- 温度上昇

- ソフトスタート容量の増加

- フェライトビーズの追加 (セクション 9.2.1.3 を参照)

- 入力電圧の増加

- 出力電圧の増加

TPS7H1111 アーキテクチャは、ループ帯域幅が広いため、高い PSRR に最適化されています。帯域幅を広く維持するため、出力容量は推奨動作条件の範囲内にする必要があります。出力容量を大きくして PSRR を改善する従来の手法は有効ではありません。これは、容量を追加すると TPS7H1111 のループ帯域幅が狭くなる可能性があるためです。この帯域幅の低下により、容量の効果以上に PSRR が低下します。

高周波 (10MHz 超など) でさらに高い PSRR が必要な場合は、フェライトビーズを使用できます。ループ帯域幅や安定性が低下しないようにするため、フェライトビーズは、セクション 9.2.1 に示すように、TPS7H1111 の制御ループの外に配置する必要があります。

$V_{IN}$  から  $V_{OUT}$  の PSRR に加え、 $V_{BIAS}$  から  $V_{OUT}$  の PSRR が  $PSRR_{BIAS}$  として規定されています。これは、式 13 で定義されます。

$$PSRR_{BIAS} = 20 \times \log(V_{BIAS(AC)} / V_{OUT(AC)}) \quad (13)$$

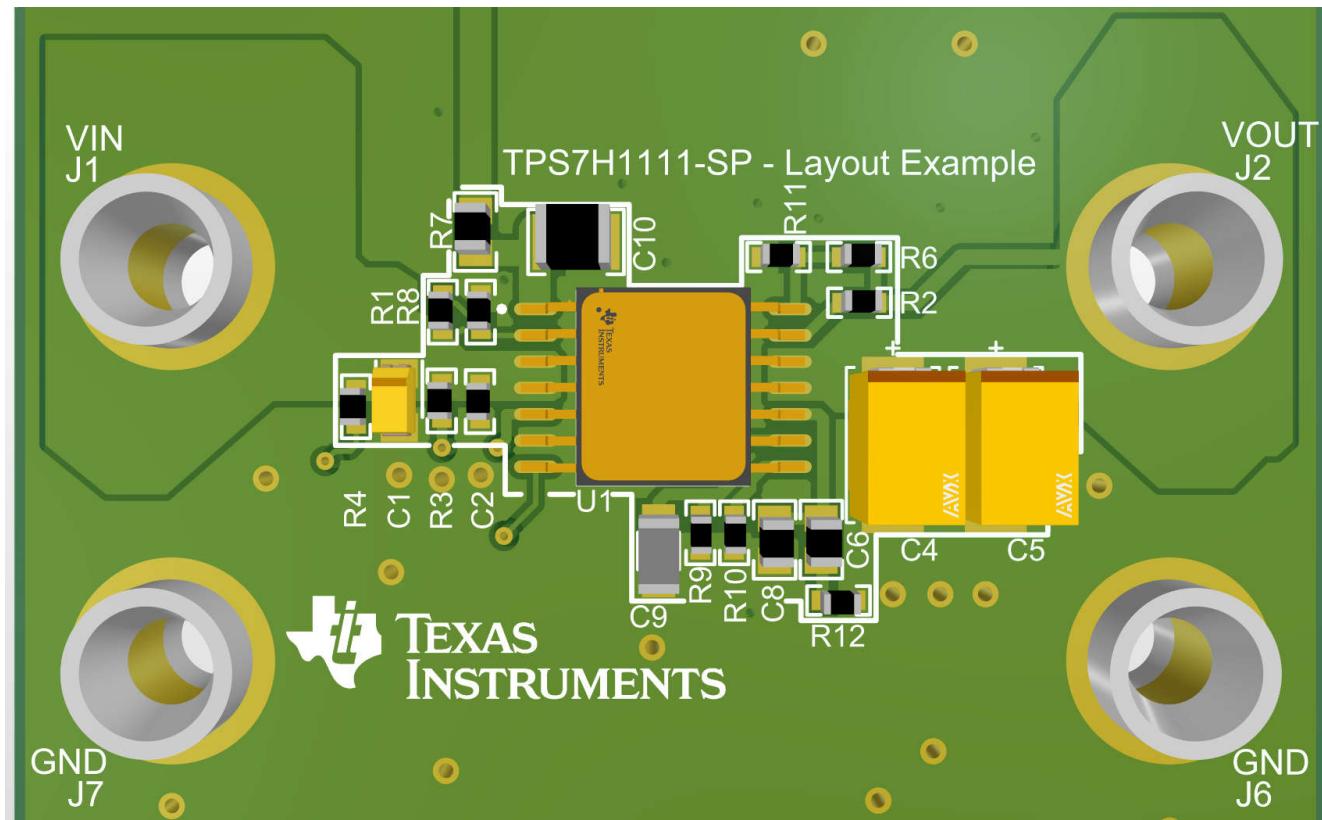

バイアス電源は電流が比較的小さいため、バイアス電源と BIAS ピンの間に RC フィルタ (通常は  $10\Omega$  と  $4.7\mu F$ ) を挿入して、 $PSRR_{BIAS}$  を増加できます。RC フィルタと内部バイアス レギュレータの内部リップル除去を組み合わせると、図 6-13 に示すように非常に高い  $PSRR_{BIAS}$  が得られます。そのため、 $100\text{kHz}$ ~ $1\text{MHz}$  の標準スイッチング周波数 (入力リップルをフィルタ処理するために高いリップル除去が最も重要) では、デバイス全体の  $PSRR$  の主要な制限因子にならないようにするために、 $PSRR_{BIAS}$  が非常に高く維持されます。RC フィルタを使用できない場合、図 6-12 に示すように、 $PSRR_{BIAS}$  値が低下します。