SN74AHC1G08-Q1

JAJSRG2E - OCTOBER 2004 - REVISED FEBRUARY 2024

# SN74AHC1G08-Q1 車載対応、シングル、2 入力、正論理 AND ゲート

# 1 特長

- 車載アプリケーション認定済み

- 動作範囲:2V~5.5V

- 最大 t<sub>pd</sub> 9ns (5V 時)

- 低消費電力、最大 I<sub>CC</sub>: 20μA

- 5V で ±8mA の出力駆動能力

- 全入力でのシュミットトリガアクションにより、低速の入 力立ち上がり/立ち下がり時間を許容

# 2 アプリケーション

- デジタル信号のイネーブルまたはディセーブル

- インジケータ LED の制御

- 通信モジュールとシステム・コントローラの間の変換

# 3 概要

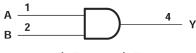

SN74AHC1G08 はシングル 2 入力正論理 AND ゲート です。デバイスは、ブール関数  $Y = A \cdot B$  または  $Y = \overline{A} + \overline{B}$ を正論理で実行します。

#### パッケージ情報

| 部品番号         | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> | 本体サイズ <sup>(3)</sup> |

|--------------|----------------------|--------------------------|----------------------|

| SN74AHC1G08- | DBV (SOT-23, 5)      | 2.8mm × 2.8mm            | 2.9mm × 1.6mm        |

| Q1           | DCK (SC-70, 5)       | 2.00mm × 1.25mm          | 2mm × 1.25mm         |

- (1) 詳細については、セクション 11 を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

- (3) 本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

論理図 (正論理)

English Data Sheet: SCLS592

# **Table of Contents**

| 1 特長                                                           |

|----------------------------------------------------------------|

|                                                                |

| 2 アプリケーション                                                     |

| 3 概要                                                           |

| 4 Pin Configuration and Functions                              |

| 5 Specifications                                               |

| 5.1 Absolute Maximum Ratings                                   |

| 5.2 ESD Ratings                                                |

| 5.3 Recommended Operating Conditions                           |

| 5.4 Thermal Information                                        |

| 5.5 Electrical Characteristics                                 |

| 5.6 Switching Characteristics, V <sub>CC</sub> = 3.3 V ± 0.3 V |

| 5.7 Switching Characteristics, V <sub>CC</sub> = 5 V ± 0.5 V   |

| 5.8 Operating Characteristics                                  |

| 6 Parameter Measurement Information                            |

| 7 Detailed Description                                         |

| 7.1 Overview                                                   |

| 7.2 Functional Block Diagram                                   |

| 7.5 Feature Description                 |                  |

|-----------------------------------------|------------------|

| 7.4 Device Functional Modes             | 8                |

| 8 Application and Implementation        | 9                |

| 8.1 Typical Application                 |                  |

| 8.2 Power Supply Recommendations        | 9                |

| 8.3 Layout                              | 9                |

| 9 Device and Documentation Support      | <mark>11</mark>  |

| 9.1 Documentation Support (Analog)      | <mark>11</mark>  |

| 9.2ドキュメントの更新通知を受け取る方法                   | <mark>11</mark>  |

| 9.3 サポート・リソース                           | 11               |

| 9.4 Trademarks                          | <mark>11</mark>  |

| 9.5 静電気放電に関する注意事項                       | <mark>11</mark>  |

| 9.6 用語集                                 | <mark>11</mark>  |

| 10 Revision History                     | <mark>11</mark>  |

| 11 Mechanical, Packaging, and Orderable |                  |

| Information                             | 1 <mark>2</mark> |

|                                         |                  |

English Data Sheet: SCLS592

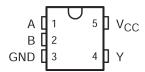

# **4 Pin Configuration and Functions**

図 4-1. DBV or DCK Package (Top View)

表 4-1. Pin Functions

|     | Più             |      |             |  |  |  |  |  |  |  |  |  |

|-----|-----------------|------|-------------|--|--|--|--|--|--|--|--|--|

|     | PIN             |      | DESCRIPTION |  |  |  |  |  |  |  |  |  |

| NO. | NAME            | 1172 | DESCRIPTION |  |  |  |  |  |  |  |  |  |

| 1   | A               | I    | Input A     |  |  |  |  |  |  |  |  |  |

| 2   | В               | I    | Input B     |  |  |  |  |  |  |  |  |  |

| 3   | GND             | _    | Ground Pin  |  |  |  |  |  |  |  |  |  |

| 4   | Y               | 0    | Output Y    |  |  |  |  |  |  |  |  |  |

| 5   | V <sub>CC</sub> | _    | Power Pin   |  |  |  |  |  |  |  |  |  |

# **5 Specifications**

# 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                    |                                                   |                                      | MIN  | MAX                   | UNIT |

|--------------------|---------------------------------------------------|--------------------------------------|------|-----------------------|------|

| V <sub>CC</sub>    | Supply voltage                                    |                                      | -0.5 | 7                     | V    |

| V <sub>I</sub> (2) | Input voltage                                     |                                      | -0.5 | 7                     | V    |

| V <sub>O</sub> (2) | Output voltage                                    |                                      | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| I <sub>IK</sub>    | Input clamp current                               | (V <sub>I</sub> < 0)                 |      | -20                   | mA   |

| I <sub>OK</sub>    | Output clamp current                              | $(V_O < 0 \text{ or } V_O > V_{CC})$ |      | ±20                   | mA   |

| Io                 | Continuous output current                         | $(V_O = 0 \text{ to } V_{CC})$       |      | ±25                   | mA   |

|                    | Continuous current through V <sub>CC</sub> or GND |                                      |      | ±50                   | mA   |

| T <sub>stg</sub>   | Storage temperature range                         |                                      | -65  | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 5.2 ESD Ratings

|                    |                          |                                                         | VALUE | UNIT |

|--------------------|--------------------------|---------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge  | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> | Liectiostatic discriarge | Charged device model (CDM), per AEC Q100-011            | ±1000 | '    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing must be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 5.3 Recommended Operating Conditions

over recommended operating free-air temperature range (unless otherwise noted)3

|                 |                                    |                                            | MIN  | MAX             | MIN  | MAX      | UNIT   |  |

|-----------------|------------------------------------|--------------------------------------------|------|-----------------|------|----------|--------|--|

| V <sub>CC</sub> | Supply voltage                     |                                            | 2    | 5.5             | 2    | 5.5      | V      |  |

|                 |                                    | V <sub>CC</sub> = 2 V                      | 1.5  |                 | 1.5  |          |        |  |

| V <sub>IH</sub> | High-level input voltage           | V <sub>CC</sub> = 3 V                      | 2.1  |                 | 2.1  |          | V      |  |

|                 |                                    | V <sub>CC</sub> = 5.5 V                    | 3.85 |                 | 3.85 |          |        |  |

|                 |                                    | V <sub>CC</sub> = 2 V                      |      | 0.5             |      | 0.5      |        |  |

| V <sub>IL</sub> | Low-level input voltage            | V <sub>CC</sub> = 3 V                      |      | 0.9             |      | 0.9      | V      |  |

|                 |                                    | V <sub>CC</sub> = 5.5 V                    |      | 1.65            |      | 1.65     |        |  |

| VI              | Input voltage                      |                                            | 0    | 5.5             | 0    | 5.5      | V      |  |

| Vo              | Output voltage                     |                                            | 0    | V <sub>CC</sub> | 0    | $V_{CC}$ | V      |  |

|                 |                                    | V <sub>CC</sub> = 2 V                      |      | -50             |      | -50      | μΑ     |  |

| I <sub>OH</sub> | High-level output current          | $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ |      | -4              |      | -4       | mA     |  |

|                 |                                    | $V_{CC} = 5 V \pm 0.5 V$                   |      | -8              |      | -8       | IIIA   |  |

|                 |                                    | V <sub>CC</sub> = 2 V                      |      | 50              |      | 50       | μΑ     |  |

| I <sub>OL</sub> | Low-level output current           | $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ |      | 4               |      | 4        | mA     |  |

|                 |                                    | $V_{CC} = 5 V \pm 0.5 V$                   |      | 8               |      | 8        | IIIA   |  |

| Δt/Δν           | Input transition rise or fall rate | $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ |      | 100             |      | 100      | ns/V   |  |

| ΔυΔν            | input transition rise of fall fate | $V_{CC} = 5 V \pm 0.5 V$                   |      | 20              |      | 20       | 115/ V |  |

| т               | Operating free air temperature     | I Suffix                                   | -40  | 85              |      |          | °C     |  |

| T <sub>A</sub>  | Operating free-air temperature     | Q Suffix                                   |      | -40             |      | 125      | ,C     |  |

<sup>(1)</sup> All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

4 資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

Product Folder Links: SN74AHC1G08-Q1

<sup>(2)</sup> The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

## **5.4 Thermal Information**

|                                                         | SN74AH0 | C1G08-Q1 |      |

|---------------------------------------------------------|---------|----------|------|

| THERMAL METRIC <sup>(1)</sup>                           | DBV     | DCK      | UNIT |

|                                                         | 5 PINS  | 5 PINS   |      |

| R <sub>θJA</sub> Junction-to-ambient thermal resistance | 278     | 289.2    | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report (SPRA953).

#### 5.5 Electrical Characteristics

over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER       | TEST CONDITIONS                         | V <sub>cc</sub> | T <sub>A</sub> = 25°C |     |      | -40°C TO 85°C |      | -40 C TO<br>125°C |      | UNIT |

|-----------------|-----------------------------------------|-----------------|-----------------------|-----|------|---------------|------|-------------------|------|------|

|                 |                                         |                 | MIN                   | TYP | MAX  | MIN           | MAX  | MIN               | MAX  |      |

|                 |                                         | 2 V             | 1.9                   | 2   |      | 1.9           |      | 1.9               |      |      |

|                 | I <sub>OH</sub> = −50 mA                | 3 V             | 2.9                   | 3   |      | 2.9           |      | 2.9               |      |      |

| V <sub>OH</sub> |                                         | 4.5 V           | 4.4                   | 4.5 |      | 4.4           |      | 4.4               |      | V    |

|                 | I <sub>OH</sub> = -4 mA                 | 3 V             | 2.58                  |     |      | 2.48          |      | 2.4               |      |      |

|                 | I <sub>OH</sub> = -8 mA                 | 4.5 V           | 3.94                  |     |      | 3.8           |      | 3.7               |      |      |

|                 |                                         | 2 V             |                       |     | 0.1  |               | 0.1  |                   | 0.1  |      |

|                 | I <sub>OL</sub> = 50 mA                 | 3 V             |                       |     | 0.1  |               | 0.1  |                   | 0.1  |      |

| V <sub>OL</sub> |                                         | 4.5 V           |                       | ,   | 0.1  |               | 0.1  |                   | 0.1  | V    |

|                 | I <sub>OL</sub> = 4 mA                  | 3 V             |                       |     | 0.36 |               | 0.44 |                   | 0.52 |      |

|                 | I <sub>OL</sub> = 8 mA                  | 4.5 V           |                       |     | 0.36 |               | 0.44 |                   | 0.52 |      |

| I <sub>I</sub>  | V <sub>I</sub> = 5.5 V or GND           | 0 V to 5.5 V    |                       |     | ±0.1 |               | ±1   |                   | ±1   | μΑ   |

| I <sub>CC</sub> | $V_I = V \text{ or GND}, I_O = 0$       | 5.5 V           |                       |     | 1    |               | 10   |                   | 20   | μΑ   |

| Ci              | V <sub>I</sub> = V <sub>CC</sub> or GND | 5 V             |                       | 4   | 10   |               | 10   |                   | 10   | pF   |

# 5.6 Switching Characteristics, $V_{CC}$ = 3.3 V ± 0.3 V

over recommended operating free-air temperature range,  $V_{CC}$  = 3.3 V ± 0.3 V (unless otherwise noted) (see Load Circuit and Voltage Waveforms)

| PARAMETER        | FROM<br>(INPUT) | то (оитрит) | OUTPUT<br>CAPACITAN    | T <sub>A</sub> = 25 C |              | -40°C TO | O 85°C | –40°C<br>125°C |     | UNIT |    |      |

|------------------|-----------------|-------------|------------------------|-----------------------|--------------|----------|--------|----------------|-----|------|----|------|

|                  | (INFOT)         |             | CE                     |                       | TYP          | MAX      | MIN    | MAX            | MIN | MAX  |    |      |

| t <sub>PLH</sub> | A or B          | Y           | C <sub>1</sub> = 15 pF |                       | 6.2          | 8.8      | 1      | 10.5           |     | 12.5 |    |      |

| t <sub>PHL</sub> | AUID            |             |                        | OL = 13 pi            | ι ΟΕ – 13 με |          | 6.2    | 8.8            | 1   | 10.5 |    | 12.5 |

| t <sub>PLH</sub> | A or B          | Y           | C <sub>I</sub> = 50 pF |                       | 8.7          | 12.3     | 1      | 14             |     | 16.5 |    |      |

| t <sub>PHL</sub> | AOID            |             | OL = 30 pi             |                       | 8.7          | 12.3     | 1      | 14             |     | 16.5 | ns |      |

# 5.7 Switching Characteristics, $V_{CC}$ = 5 V ± 0.5 V

over recommended operating free-air temperature range,  $V_{CC}$  = 5 V ± 0.5 V (unless otherwise noted) (see Load Circuit and Voltage Waveforms)

| PARAMETER        | FROM<br>(INPUT) | то (оитрит) | OUTPUT<br>CAPACITAN    | T <sub>A</sub> = 25°C |            |     | -40°C TO 85°C |     | -40°C TC<br>125°C | )   | UNIT |   |     |

|------------------|-----------------|-------------|------------------------|-----------------------|------------|-----|---------------|-----|-------------------|-----|------|---|-----|

|                  | (INPOT)         |             | CE                     | MIN                   | TYP        | MAX | MIN           | MAX | MIN               | MAX |      |   |     |

| t <sub>PLH</sub> | A or B          | V           | C <sub>I</sub> = 15 pF |                       | 4.3        | 5.9 |               | 7   |                   | 9   | ns   |   |     |

| t <sub>PHL</sub> | AOID            | 1           | 1 OL - 13 pr           | Ι Ι ΟΕ - 13 βι        | CL = 13 pi |     | 4.3           | 5.9 |                   | 7   |      | 9 | 115 |

| t <sub>PLH</sub> | A or B          | V           | C <sub>1</sub> = 50 pF |                       | 5.8        | 7.9 |               | 9   |                   | 11  | ns   |   |     |

| t <sub>PHL</sub> | AOIB            | 1           | C <sub>L</sub> = 30 pi |                       | 5.8        | 7.9 |               | 9   |                   | 11  | 115  |   |     |

# 5.8 Operating Characteristics

$V_{CC}$  = 5 V,  $T_A$  = 25°C

| PARAMETER       |                               | TEST (   | CONDITIONS | TYP | UNIT |

|-----------------|-------------------------------|----------|------------|-----|------|

| C <sub>pd</sub> | Power dissipation capacitance | No load, | f = 1 MHz  | 18  | pF   |

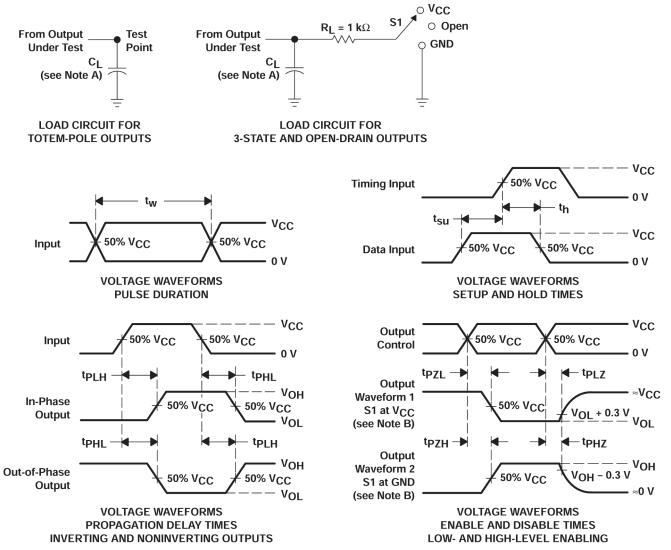

#### **6 Parameter Measurement Information**

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz,  $Z_O = 50 \Omega$ ,  $t_f \leq$  3 ns,  $t_f \leq$  3 ns.

- D. The outputs are measured one at a time, with one input transition per measurement.

- E. All parameters and waveforms are not applicable to all devices.

図 6-1. Load Circuit and Voltage Waveforms

| TEST                               | S1              |

|------------------------------------|-----------------|

| t <sub>PLH</sub> /t <sub>PHL</sub> | Open            |

| t <sub>PLZ</sub> /t <sub>PZL</sub> | V <sub>CC</sub> |

| t <sub>PHZ</sub> /t <sub>PZH</sub> | GND             |

| Open Drain                         | V <sub>CC</sub> |

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

7

# 7 Detailed Description

#### 7.1 Overview

The SN74AHC1G08-Q1 contains four independent 2-input AND Gates with Schmitt-trigger inputs. Each gate performs the Boolean function  $Y = A \times B$  in positive logic. The output level is referenced to the supply voltage  $(V_{CC})$  and supports 1.8-V, 2.5-V, 3.3-V, and 5-V CMOS levels.

# 7.2 Functional Block Diagram

図 7-1. Logic Diagram (Positive Logic)

## 7.3 Feature Description

#### 7.3.1 CMOS Schmitt-Trigger Inputs

This device includes inputs with the Schmitt-trigger architecture. These inputs are high impedance and are typically modeled as a resistor in parallel with the input capacitance given in the *Electrical Characteristics* table from the input to ground. The worst case resistance is calculated with the maximum input voltage, given in the *Absolute Maximum Ratings* table, and the maximum input leakage current, given in the *Electrical Characteristics* table, using Ohm's law  $(R = V \div I)$ .

The Schmitt-trigger input architecture provides hysteresis as defined by  $\Delta V_T$  in the *Electrical Characteristics* table, which makes this device extremely tolerant to slow or noisy inputs. While the inputs can be driven much slower than standard CMOS inputs, it is still recommended to properly terminate unused inputs. Driving the inputs with slow transitioning signals will increase dynamic current consumption of the device. For additional information regarding Schmitt-trigger inputs, please see *Understanding Schmitt Triggers*.

#### 7.4 Device Functional Modes

表 7-1 lists the functional modes of the SN74AHC1G08-Q1.

表 7-1. Function Table

| INPU | TS <sup>(1)</sup> | OUTPUT<br>Y |  |  |  |

|------|-------------------|-------------|--|--|--|

| Α    | В                 |             |  |  |  |

| Н    | Н                 | Н           |  |  |  |

| L    | X                 | L           |  |  |  |

| X    | L                 | L           |  |  |  |

H = high voltage level, L = low voltage level, X = do not care, Z = high impedance

# 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

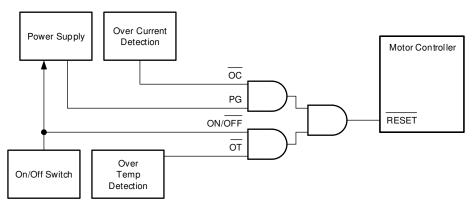

## 8.1 Typical Application

図 8-1. Typical Application Block Diagram

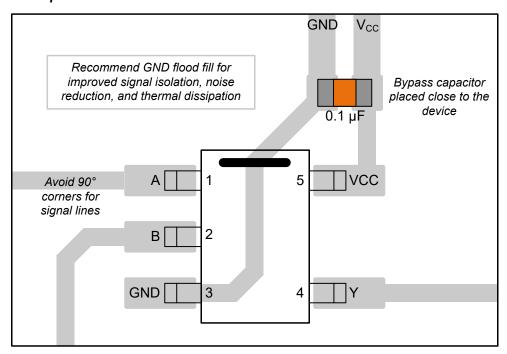

#### 8.2 Power Supply Recommendations

The power supply can be any voltage between the minimum and maximum supply voltage rating located in the *Recommended Operating Conditions*. Each  $V_{CC}$  terminal should have a good bypass capacitor to prevent power disturbance. A 0.1- $\mu$ F capacitor is recommended for this device. It is acceptable to parallel multiple bypass capacitors to reject different frequencies of noise. The 0.1- $\mu$ F and 1- $\mu$ F capacitors are commonly used in parallel. The bypass capacitor should be installed as close to the power terminal as possible for best results, as shown in the following layout example.

#### 8.3 Layout

#### 8.3.1 Layout Guidelines

When using multiple-input and multiple-channel logic devices, inputs must never be left floating. In many cases, functions or parts of functions of digital logic devices are unused (for example, when only two inputs of a triple-input AND gate are used or only 3 of the 4 buffer gates are used). Such unused input pins must not be left unconnected because the undefined voltages at the outside connections result in undefined operational states. All unused inputs of digital logic devices must be connected to a logic high or logic low voltage, as defined by the input voltage specifications, to prevent them from floating. The logic level that must be applied to any particular unused input depends on the function of the device. Generally, the inputs are tied to GND or  $V_{CC}$ , whichever makes more sense for the logic function or is more convenient.

## 8.3.1.1 Layout Example

図 8-2. Example Layout for the SN74AHC1G08-Q1

English Data Sheet: SCLS592

# 9 Device and Documentation Support

## 9.1 Documentation Support (Analog)

#### 9.1.1 Related Documentation

For related documentation, see the following:

- Texas Instruments, CMOS Power Consumption and Cpd Calculation application note

- Texas Instruments, Designing With Logic application note

- Texas Instruments, Thermal Characteristics of Standard Linear and Logic (SLL) Packages and Devices

application note

- Texas Instruments, Implications of Slow or Floating CMOS Inputs application note

#### 9.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.com のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

## 9.3 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 9.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 9.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 9.6 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

#### 10 Revision History

# Changes from Revision D (October 2023) to Revision E (February 2024)Page• Updated RθJA values: DBV = 206 to 278, all values in °C/W5

# Changes from Revision C (October 2004) to Revision D (October 2023)

Page

- Updated RθJA values: DCK = 252 to 289.2, all values in °C/W .......

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

11

# 11 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 13-Feb-2024

#### PACKAGING INFORMATION

| Orderable Device   | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|--------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

| SN74AHC1G08QDBVRQ1 | ACTIVE | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | A08U                 | Samples |

| SN74AHC1G08QDCKRQ1 | ACTIVE | SC70         | DCK                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | AEU                  | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 13-Feb-2024

#### OTHER QUALIFIED VERSIONS OF SN74AHC1G08-Q1:

• Catalog : SN74AHC1G08

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 13-Feb-2024

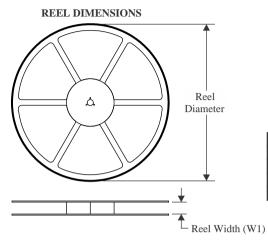

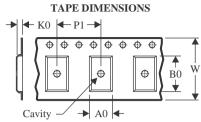

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

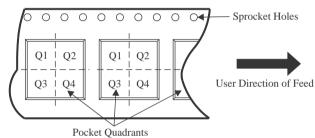

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device             | U      | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------------|--------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN74AHC1G08QDBVRQ1 | SOT-23 | DBV                | 5 | 3000 | 179.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| SN74AHC1G08QDCKRQ1 | SC70   | DCK                | 5 | 3000 | 179.0                    | 8.4                      | 2.2        | 2.5        | 1.2        | 4.0        | 8.0       | Q3               |

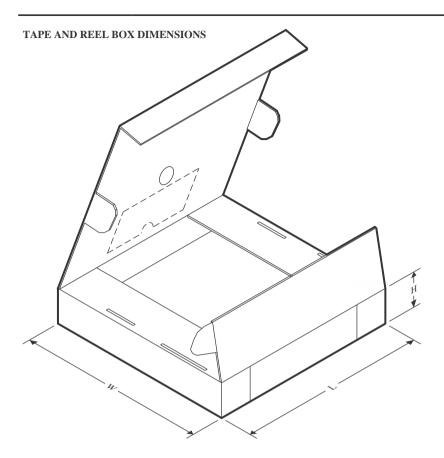

www.ti.com 13-Feb-2024

#### \*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN74AHC1G08QDBVRQ1 | SOT-23       | DBV             | 5    | 3000 | 200.0       | 183.0      | 25.0        |

| SN74AHC1G08QDCKRQ1 | SC70         | DCK             | 5    | 3000 | 200.0       | 183.0      | 25.0        |

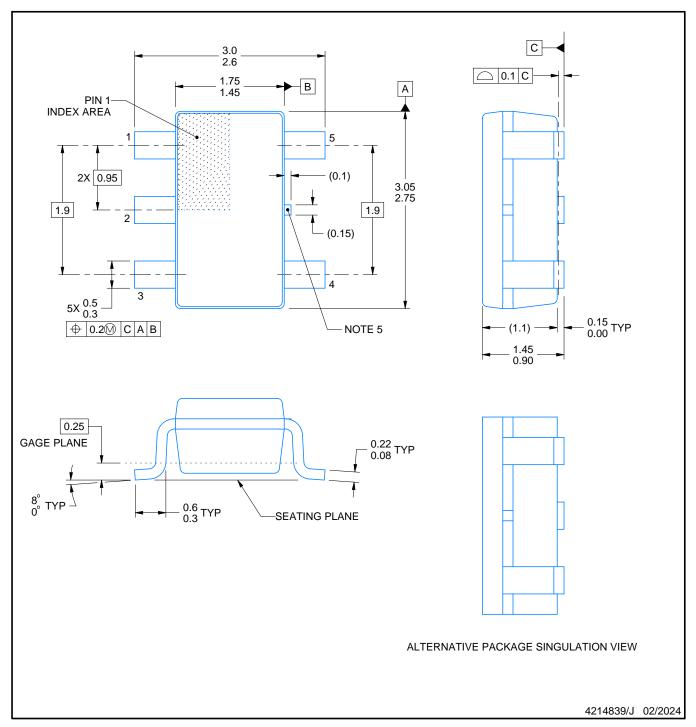

#### NOTES:

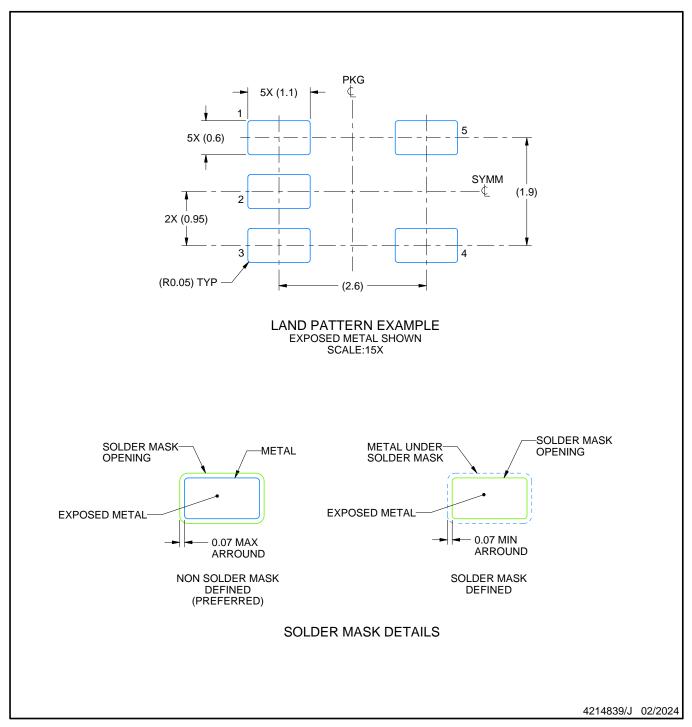

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-178.

- 4. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

- 5. Support pin may differ or may not be present.

NOTES: (continued)

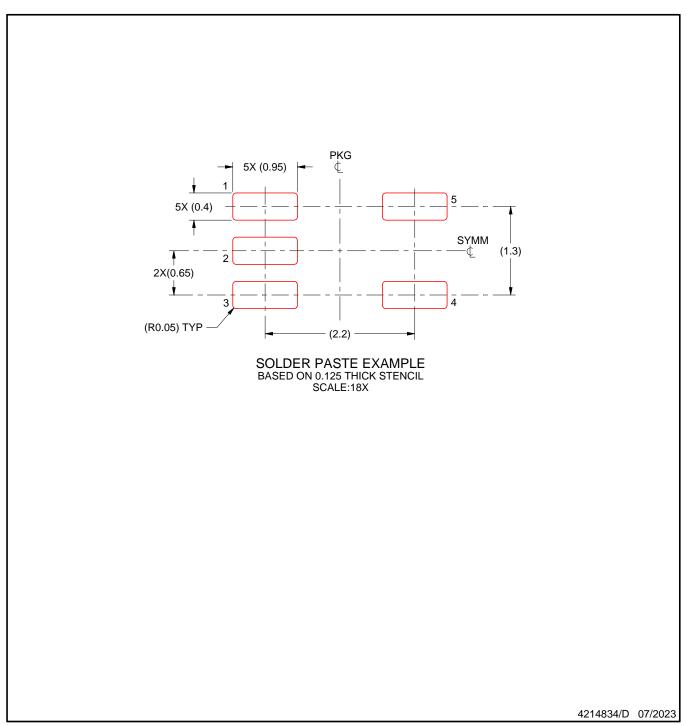

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

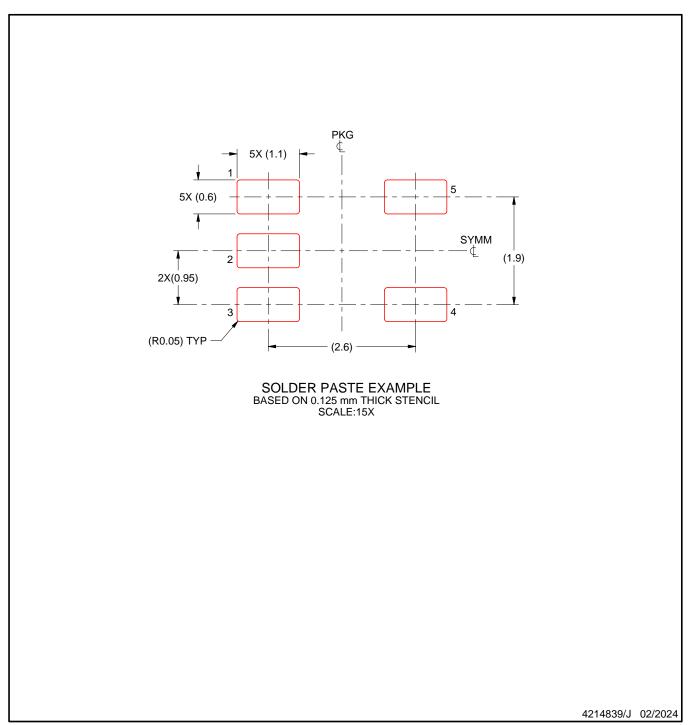

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

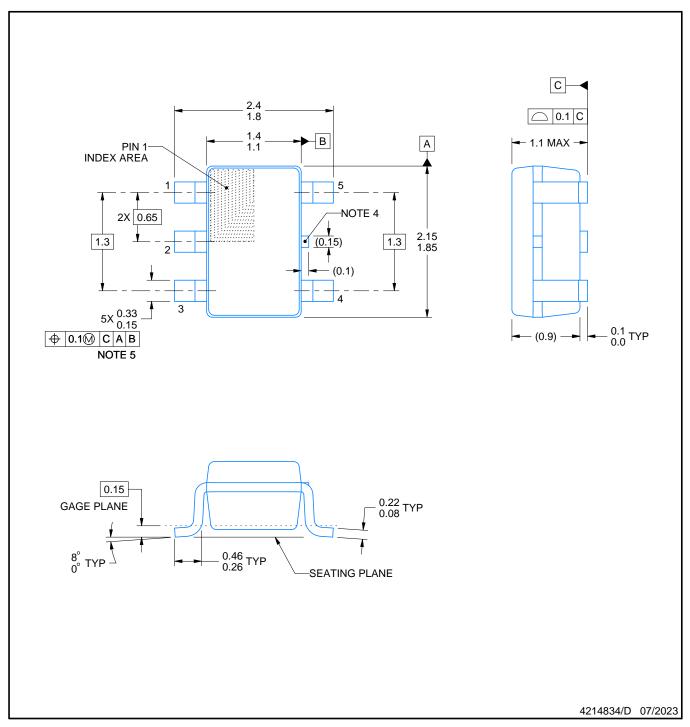

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-203.

- 4. Support pin may differ or may not be present.5. Lead width does not comply with JEDEC.

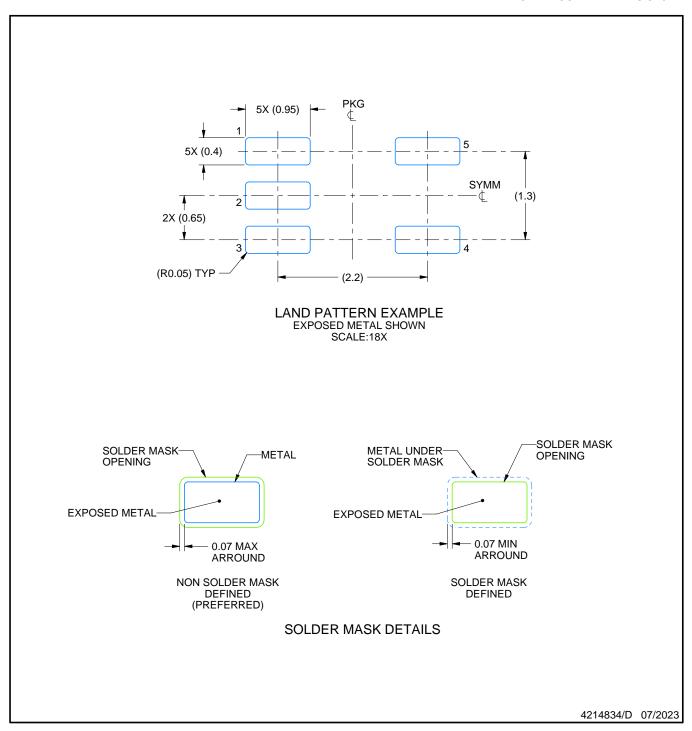

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated