CSD86336Q3D

JAJSEY5 - MARCH 2018

# CSD86336Q3D 同期整流降圧型NexFET™パワー・ブロック

### 特長

- ハーフ・ブリッジ・パワー・ブロック

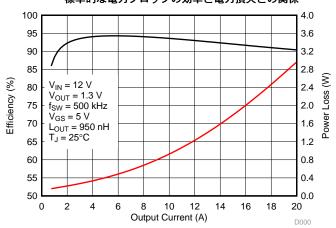

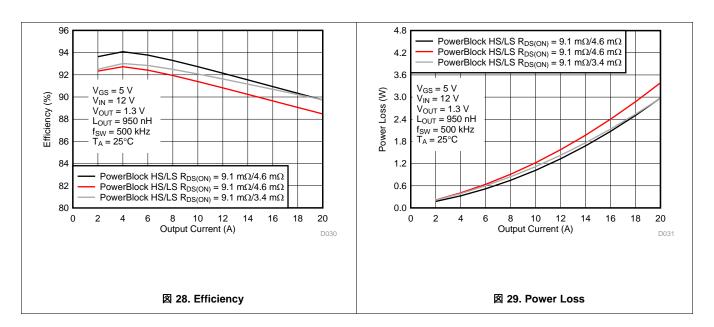

- 12A時に93.0%のシステム効率

- 最大20Aで動作

- 高周波数での動作(最高1.5MHz)

- 高密度SON、占有面積3.3mmx3.3mm

- 5Vゲートの駆動に最適化

- 低いスイッチング損失

- インダクタンスの非常に低いパッケージ

- RoHS準拠

- ハロゲン不使用

- 鉛フリーの端子メッキ処理

## アプリケーション

- 同期整流降圧コンバータ

- 高周波数のアプリケーション

- 大電流、低いデューティ・サイクルのアプリケーショ

- マルチフェーズの同期整流降圧コンバータ

- POL DC/DCコンバータ

- IMVP、VRM、VRDアプリケーション

#### 3 概要

CSD86336Q3D NexFET™ パワー・ブロックは、同期整 流降圧アプリケーション向けに最適化された設計で、大電 流、高効率、高周波数の能力を小さな3.3mm×3.3mm の外形に収めています。この製品は5Vのゲート駆動アプ リケーション用に最適化されており、外部のコントローラバ ライバからの任意の5Vゲート・ドライブと組み合わせて、高 密度の電源を実現できます。

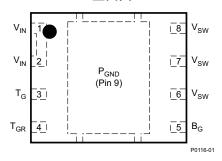

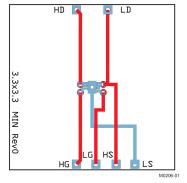

#### 上面図

#### 製品情報(1)

| デバイス         | メディア            | 数量   | パッケージ                | 出荷         |

|--------------|-----------------|------|----------------------|------------|

| CSD86336Q3D  | 13インチ・リール       | 2500 | SON<br>3.30mm×3.30mm | テー<br>プ・アン |

| CSD86336Q3DT | <b>7</b> インチ・リー | 250  | プラスチック・パッケージ         | ド・リール      |

(1) 提供されているすべてのパッケージについては、巻末の注文情報 を参照してください。

### 標準的な電力ブロックの効率と電力損失との関係

# 目次

| 1                 | 特長 1                                                                                              |   | 6.4 Normalized Curves                                     | . 13 |

|-------------------|---------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------|------|

| 2                 | アプリケーション                                                                                          |   | 6.5 Calculating Power Loss and Safe Operating Area (SOA)  |      |

| 3<br>4            | 概要                                                                                                | 7 | Layout                                                    |      |

| <del>-</del><br>5 | Specifications                                                                                    |   | 7.1 Recommended Schematic Overview                        | . 16 |

| 3                 | 5.1 Absolute Maximum Ratings                                                                      | 8 | 7.2 Recommended PCB Design Overview<br>デバイスおよびドキュメントのサポート |      |

|                   | 5.2 Recommended Operating Conditions                                                              | 0 | 8.1 ドキュメントの更新通知を受け取る方法                                    | . 19 |

|                   | 5.4 Power Block Performance                                                                       |   | 8.2 コミュニティ・リソース<br>8.3 商標                                 |      |

|                   | 5.5 Electrical Characteristics – Q1 Control FET                                                   |   | 8.4 静電気放電に関する注意事項<br>8.5 Glossary                         |      |

|                   | 5.7 Typical Power Block Device Characteristics 6 5.8 Typical Power Block MOSFET Characteristics 8 | 9 |                                                           |      |

| 6                 | Application and Implementation 11                                                                 |   | 9.1 Q3Dパッケージの寸法<br>9.2 ピン構成                               |      |

|                   | 6.1 Application Information                                                                       |   | 9.3 推奨ランド・パターン                                            | . 21 |

|                   | 6.3 Safe Operating Area (SOA) Curves                                                              |   | 9.4 推奨ステンシル                                               | . 22 |

|                   |                                                                                                   |   |                                                           |      |

## 4 改訂履歴

| 日付      | 改訂内容 | 注  |

|---------|------|----|

| 2018年3月 | *    | 初版 |

JAJSEY5 - MARCH 2018 www.ti.com

## **Specifications**

## 5.1 Absolute Maximum Ratings

TA =  $25^{\circ}$ C (unless otherwise noted)<sup>(1)</sup>

|                                      |                                                | MIN | MAX | UNIT |

|--------------------------------------|------------------------------------------------|-----|-----|------|

|                                      | V <sub>IN</sub> to P <sub>GND</sub>            |     | 25  |      |

|                                      | V <sub>SW</sub> to P <sub>GND</sub>            |     | 25  |      |

| Voltage                              | V <sub>SW</sub> to P <sub>GND</sub> (10 ns)    |     | 27  | V    |

|                                      | $T_G$ to $T_{GR}$                              | -8  | 10  |      |

|                                      | B <sub>G</sub> to P <sub>GND</sub>             | -8  | 10  |      |

| Pulsed current                       | rating, IDM <sup>(2)</sup>                     |     | 60  | Α    |

| Power dissipat                       | tion, P <sub>D</sub>                           |     | 6   | W    |

| Avalanche<br>energy, E <sub>AS</sub> | Sync FET, I <sub>D</sub> = 40 A, L = 0.1 mH    |     | 80  |      |

|                                      | Control FET, I <sub>D</sub> = 26 A, L = 0.1 mH |     | 34  | mJ   |

| T <sub>J</sub> and T <sub>STG</sub>  | Operating junction and storage temperature     | -55 | 150 | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated is not implied. Exposure to absolutemaximum-rated conditions for extended periods may affect device reliability.

### 5.2 Recommended Operating Conditions

$T_A = 25$ °C (unless otherwise noted)

|                  |                                                     | MIN | MAX  | UNIT |

|------------------|-----------------------------------------------------|-----|------|------|

| $V_{GS}$         | Gate drive voltage                                  | 4.5 | 8    | V    |

| V <sub>IN</sub>  | Input supply voltage <sup>(1)</sup>                 |     | 22   | V    |

| $f_{SW}$         | Switching frequency C <sub>BST</sub> = 0.1 µF (min) |     | 1500 | kHz  |

|                  | Operating current                                   |     | 20   | А    |

| TJ               | Operating temperature                               |     | 125  | °C   |

| T <sub>STG</sub> | Storage temperature                                 |     | 125  | °C   |

<sup>(1)</sup> Operating at high V<sub>IN</sub> can create excessive AC voltage overshoots on the switch node (V<sub>SW</sub>) during MOSFET switching transients. For reliable operation, the switch node (V<sub>SW</sub>) to ground voltage must remain at or below the Absolute Maximum Ratings.

#### 5.3 Thermal Information

$T_A = 25^{\circ}C$  (unless otherwise noted)

|                 | THERMAL METRIC                                                            | MIN | MAX | UNIT |

|-----------------|---------------------------------------------------------------------------|-----|-----|------|

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance (min Cu) <sup>(1)</sup>            |     | 105 | °C/W |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance (max Cu) <sup>(1)</sup> (2)        |     | 55  | °C/W |

| $R_{\theta JC}$ | Junction-to-case thermal resistance (top of package) (1)                  |     | 17  | °C/W |

| $R_{\theta JC}$ | Junction-to-case thermal resistance (P <sub>GND</sub> pin) <sup>(1)</sup> |     | 3.2 | °C/W |

<sup>(1)</sup>  $R_{BJC}$  is determined with the device mounted on a 1-in<sup>2</sup> (6.45-cm<sup>2</sup>), 2-oz (0.071-mm) thick Cu pad on a 1.5-in x 1.5-in  $(3.81\text{-cm} \times 3.81\text{-cm})$ , 0.06-in (1.52-mm) thick FR4 board.  $R_{\theta JC}$  is specified by design while  $R_{\theta JA}$  is determined by the user's board

#### 5.4 Power Block Performance

$T_A = 25$ °C (unless otherwise noted)

| PARAMETER         |                                                  | TEST CONDITIONS                                                                                                                                                                     | MIN | TYP | MAX | UNIT |

|-------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| P <sub>LOSS</sub> | Power loss <sup>(1)</sup>                        | $V_{IN} = 12 \text{ V}, V_{GS} = 5 \text{ V}, V_{OUT} = 1.3 \text{ V}, I_{OUT} = 15 \text{ A},$<br>$f_{SW} = 500 \text{ kHz}, L_{OUT} = 950 \text{ nH}, T_{J} = 25^{\circ}\text{C}$ |     | 1.8 |     | W    |

| I <sub>QVIN</sub> | V <sub>IN</sub> quiescent current <sup>(1)</sup> | $T_G$ to $T_{GR} = 0$ V, $B_G$ to $P_{GND} = 0$ V, $V_{IN} = 12$ V                                                                                                                  |     | 10  |     | μΑ   |

Measurement made with six 10-μF (TDK C3216X5R1C106KT or equivalent) ceramic capacitors placed across V<sub>IN</sub> to P<sub>GND</sub> pins and using a high-current 5-V driver IC.

Pulse duration =  $50 \mu S$ . Duty cycle = 0.01.

Device mounted on FR4 material with 1-in<sup>2</sup> (6.45-cm<sup>2</sup>) Cu

# TEXAS INSTRUMENTS

## 5.5 Electrical Characteristics – Q1 Control FET

$T_i = 25$  °C (unless otherwise noted)

|                     | PARAMETER                        | TEST CONDITIONS                                                                                                                                          | MIN          | TYP  | MAX  | UNIT |

|---------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|------|

| STATIC              | CHARACTERISTICS                  |                                                                                                                                                          |              |      |      |      |

| BV <sub>DSS</sub>   | Drain-to-source voltage          | $V_{GS} = 0 \text{ V}, I_{DS} = 250 \mu\text{A}$                                                                                                         | 25           |      |      | V    |

| I <sub>DSS</sub>    | Drain-to-source leakage current  | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 20 V                                                                                                            |              |      | 1    | μA   |

| I <sub>GSS</sub>    | Gate-to-source leakage current   | $V_{DS} = 0 \text{ V}, V_{GS} = +10 / -8 \text{ V}$                                                                                                      |              |      | 100  | nA   |

| V <sub>GS(th)</sub> | Gate-to-source threshold voltage | $V_{DS} = V_{GS}$ , $I_{DS} = 250 \mu A$                                                                                                                 | 1.1          | 1.5  | 1.9  | V    |

| Z <sub>DS(on)</sub> | Effective AC on-impedance        | $V_{IN} = 12 \text{ V}, V_{GS} = 5 \text{ V}, V_{OUT} = 1.3 \text{ V}, \\ I_{OUT} = 20 \text{ A}, f_{SW} = 500 \text{ kHz}, \\ L_{OUT} = 950 \text{ nH}$ |              | 9.1  |      | mΩ   |

| 9 <sub>fs</sub>     | Transconductance                 | $V_{DS} = 2.5 \text{ V}, I_{DS} = 14 \text{ A}$                                                                                                          |              | 40   |      | S    |

| DYNAN               | IIC CHARACTERISTICS              | •                                                                                                                                                        |              |      | •    |      |

| C <sub>ISS</sub>    | Input capacitance                |                                                                                                                                                          | 38           |      | 494  | pF   |

| C <sub>OSS</sub>    | Output capacitance               | $V_{GS} = 0 \text{ V}, V_{DS} = 12.5 \text{ V}, f = 1 \text{ Mhz}$                                                                                       |              | 263  | 342  | pF   |

| C <sub>RSS</sub>    | Reverse transfer capacitance     |                                                                                                                                                          |              | 14.1 | 18.3 | pF   |

| R <sub>G</sub>      | Series gate resistance           |                                                                                                                                                          |              | 4.0  | 8.0  | Ω    |

| Qg                  | Gate charge total (4.5 V)        |                                                                                                                                                          |              | 2.9  | 3.8  | nC   |

| Q <sub>gd</sub>     | Gate charge – gate-to-drain      | V 42.5.V. L 44.A                                                                                                                                         |              | 0.6  |      | nC   |

| Q <sub>gs</sub>     | Gate charge – gate-to-source     | V <sub>DS</sub> = 12.5 V, I <sub>DS</sub> = 14 A                                                                                                         |              | 1.4  |      | nC   |

| Q <sub>g(th)</sub>  | Gate charge at V <sub>th</sub>   |                                                                                                                                                          |              | 0.6  |      | nC   |

| Q <sub>OSS</sub>    | Output charge                    | $V_{DS} = 12.5 \text{ V}, V_{GS} = 0 \text{ V}$                                                                                                          |              | 5.4  |      | nC   |

| t <sub>d(on)</sub>  | Turn on delay time               |                                                                                                                                                          |              | 5    |      | ns   |

| t <sub>r</sub>      | Rise time                        | V <sub>DS</sub> = 12.5 V, V <sub>GS</sub> = 4.5 V, I <sub>DS</sub> = 14 A,                                                                               |              | 10   |      | ns   |

| t <sub>d(off)</sub> | Turn off delay time              | $R_G = 0 \Omega$                                                                                                                                         |              | 7    |      | ns   |

| t <sub>f</sub>      | Fall time                        |                                                                                                                                                          |              | 2    |      | ns   |

| DIODE               | CHARACTERISTICS                  |                                                                                                                                                          | <del>.</del> |      |      |      |

| $V_{SD}$            | Diode forward voltage            | I <sub>DS</sub> = 14 A, V <sub>GS</sub> = 0 V                                                                                                            |              | 0.86 | 1.0  | V    |

| Q <sub>rr</sub>     | Reverse recovery charge          | V 40.5.V. I 44.A. di/dr. 000.A/                                                                                                                          |              | 14.7 |      | nC   |

| t <sub>rr</sub>     | Reverse recovery time            | V <sub>DS</sub> = 12.5 V, I <sub>F</sub> = 14 A, di/dt = 300 A/μs                                                                                        |              | 15   |      | ns   |

|                     |                                  |                                                                                                                                                          |              |      |      |      |

JAJSEY5 - MARCH 2018

## 5.6 Electrical Characteristics - Q2 Sync FET

$T_i = 25$  °C (unless otherwise noted)

|                     | PARAMETER                        | TEST CONDITIONS                                                                                                                                          | MIN | TYP  | MAX  | UNIT |

|---------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| STATIC              | CHARACTERISTICS                  |                                                                                                                                                          |     |      |      |      |

| BV <sub>DSS</sub>   | Drain-to-source voltage          | $V_{GS} = 0 \text{ V}, I_{DS} = 250 \mu\text{A}$                                                                                                         | 25  |      |      | V    |

| I <sub>DSS</sub>    | Drain-to-source leakage current  | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 20 V                                                                                                            |     |      | 1    | μA   |

| I <sub>GSS</sub>    | Gate-to-source leakage current   | $V_{DS} = 0 \text{ V}, V_{GS} = +10 / -8 \text{ V}$                                                                                                      |     |      | 100  | nA   |

| V <sub>GS(th)</sub> | Gate-to-source threshold voltage | $V_{DS} = V_{GS}, I_{DS} = 250 \mu A$                                                                                                                    | 1.0 | 1.3  | 1.6  | V    |

| Z <sub>DS(on)</sub> | Effective AC on-impedance        | $V_{IN} = 12 \text{ V}, V_{GS} = 5 \text{ V}, V_{OUT} = 1.3 \text{ V}, \\ I_{OUT} = 20 \text{ A}, f_{SW} = 500 \text{ kHz}, \\ L_{OUT} = 950 \text{ nH}$ |     | 3.4  |      | mΩ   |

| g <sub>fs</sub>     | Transconductance                 | $V_{DS} = 2.5 \text{ V}, I_{DS} = 14 \text{ A}$                                                                                                          |     | 57   |      | S    |

| DYNAM               | IC CHARACTERISTICS               |                                                                                                                                                          | •   |      |      |      |

| C <sub>ISS</sub>    | Input capacitance                |                                                                                                                                                          | 728 |      | 970  | pF   |

| Coss                | Output capacitance               | $V_{GS} = 0 \text{ V}, V_{DS} = 12.5 \text{ V}, f = 1 \text{ Mhz}$                                                                                       |     | 501  | 664  | pF   |

| C <sub>RSS</sub>    | Reverse transfer capacitance     |                                                                                                                                                          |     | 26   | 33   | pF   |

| $R_G$               | Series gate resistance           |                                                                                                                                                          |     | 0.65 | 1.3  | Ω    |

| $Q_g$               | Gate charge total (4.5 V)        |                                                                                                                                                          |     | 5.7  | 7.4  | nC   |

| $Q_{gd}$            | Gate charge – gate-to-drain      | V 40.5 V 1 44.A                                                                                                                                          |     | 1.2  |      | nC   |

| $Q_{gs}$            | Gate charge – gate-to-source     | V <sub>DS</sub> = 12.5 V, I <sub>DS</sub> = 14 A                                                                                                         |     | 2.1  |      | nC   |

| $Q_{g(th)}$         | Gate charge at V <sub>th</sub>   |                                                                                                                                                          |     | 1.0  |      | nC   |

| Q <sub>OSS</sub>    | Output charge                    | $V_{DS} = 12.5 \text{ V}, V_{GS} = 0 \text{ V}$                                                                                                          |     | 10.3 |      | nC   |

| t <sub>d(on)</sub>  | Turn on delay time               |                                                                                                                                                          |     | 4    |      | ns   |

| t <sub>r</sub>      | Rise time                        | $V_{DS} = 12.5 \text{ V}, V_{GS} = 4.5 \text{ V}, I_{DS} = 14 \text{ A},$                                                                                |     | 10   |      | ns   |

| t <sub>d(off)</sub> | Turn off delay time              | $R_G = 0 \Omega$                                                                                                                                         |     | 8    |      | ns   |

| t <sub>f</sub>      | Fall time                        |                                                                                                                                                          |     | 2    |      | ns   |

| DIODE               | CHARACTERISTICS                  |                                                                                                                                                          | -   |      |      |      |

| V <sub>SD</sub>     | Diode forward voltage            | I <sub>DS</sub> = 14 A, V <sub>GS</sub> = 0 V                                                                                                            |     | 0.82 | 0.95 | V    |

| Q <sub>rr</sub>     | Reverse recovery charge          | V 42.5.V. I 44.A. di/dt 200.A/v-                                                                                                                         |     | 25.4 |      | nC   |

| t <sub>rr</sub>     | Reverse recovery time            | $V_{DS} = 12.5 \text{ V}, I_F = 14 \text{ A}, di/dt = 300 \text{ A/}\mu\text{s}$                                                                         |     | 18   |      | ns   |

$\label{eq:maxR} \begin{array}{l} \text{Max R}_{\theta \text{JA}} = 55^{\circ}\text{C/W} \\ \text{when mounted on 1 in}^2 \end{array}$ (6.45 cm<sup>2</sup>) of 2-oz (0.071-mm) thick Cu.

Max  $R_{\theta JA} = 105^{\circ}C/W$ when mounted on minimum pad area of 2-oz (0.071-mm) thick Cu.

JAJSEY5 – MARCH 2018 www.tij.co.jp

# TEXAS INSTRUMENTS

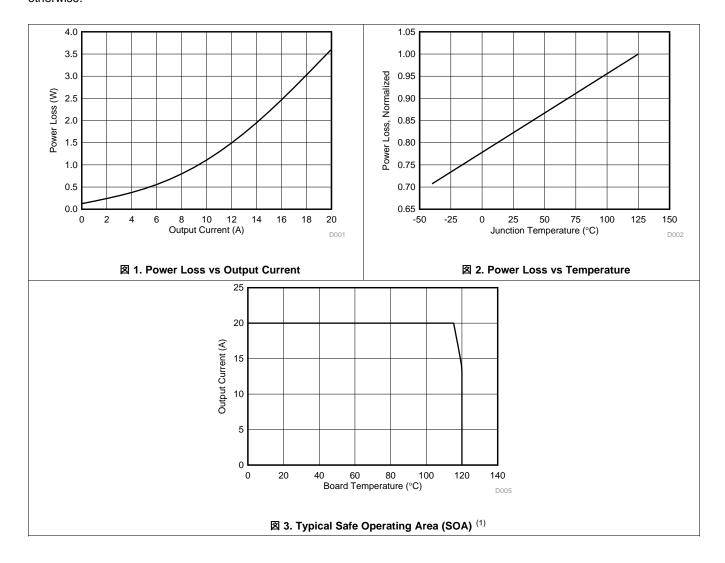

## 5.7 Typical Power Block Device Characteristics

Test conditions:  $V_{IN}$  = 12 V,  $V_{DD}$  = 5 V,  $f_{SW}$  = 500 kHz,  $V_{OUT}$  = 1.3 V,  $L_{OUT}$  = 0.95  $\mu$ H,  $I_{OUT}$  = 20 A,  $T_{J}$  = 125°C, unless stated otherwise.

<sup>(1)</sup> The Typical Power Block System Characteristic curves are based on measurements made on a PCB design with dimensions of 4 in (W) × 3.5 in (L) × 0.062 in (H) and 6 copper layers of 1-oz copper thickness. See *Application and Implementation* section for detailed explanation.

www.tij.co.jp

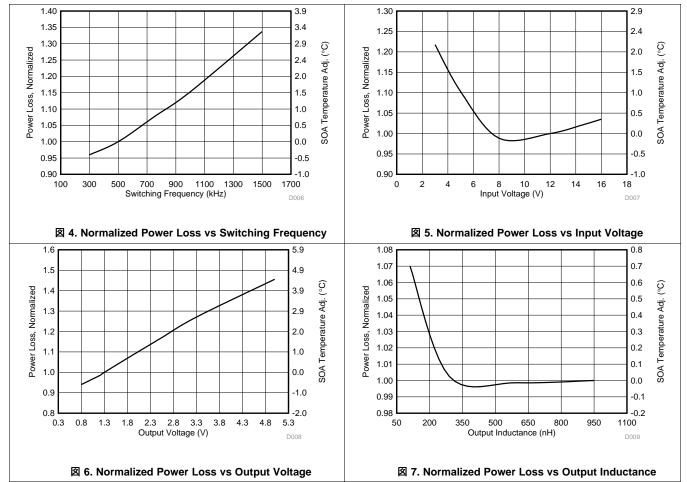

## **Typical Power Block Device Characteristics (continued)**

Test conditions:  $V_{IN}$  = 12 V,  $V_{DD}$  = 5 V,  $f_{SW}$  = 500 kHz,  $V_{OUT}$  = 1.3 V,  $L_{OUT}$  = 0.95  $\mu$ H,  $I_{OUT}$  = 20 A,  $T_{J}$  = 125°C, unless stated otherwise.

# TEXAS INSTRUMENTS

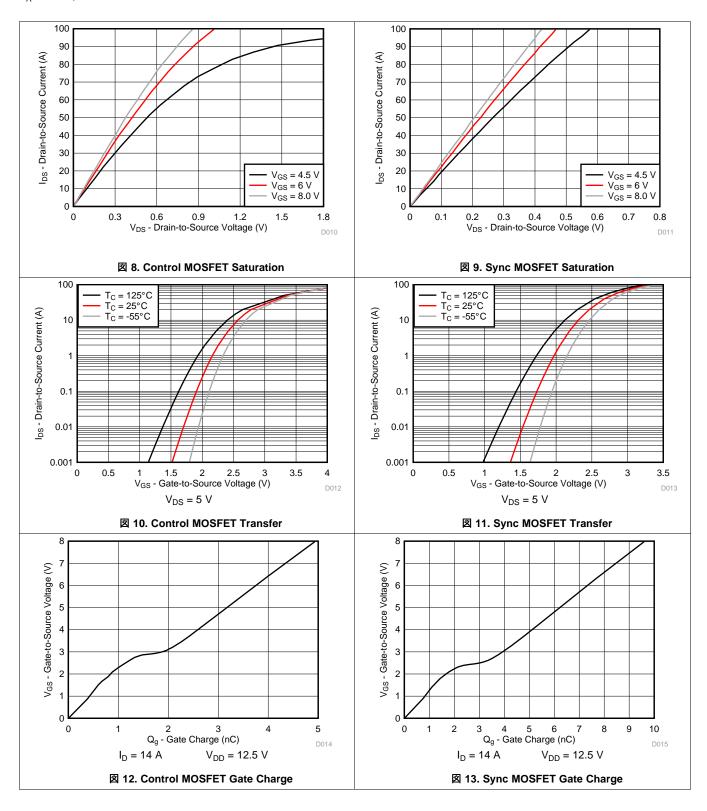

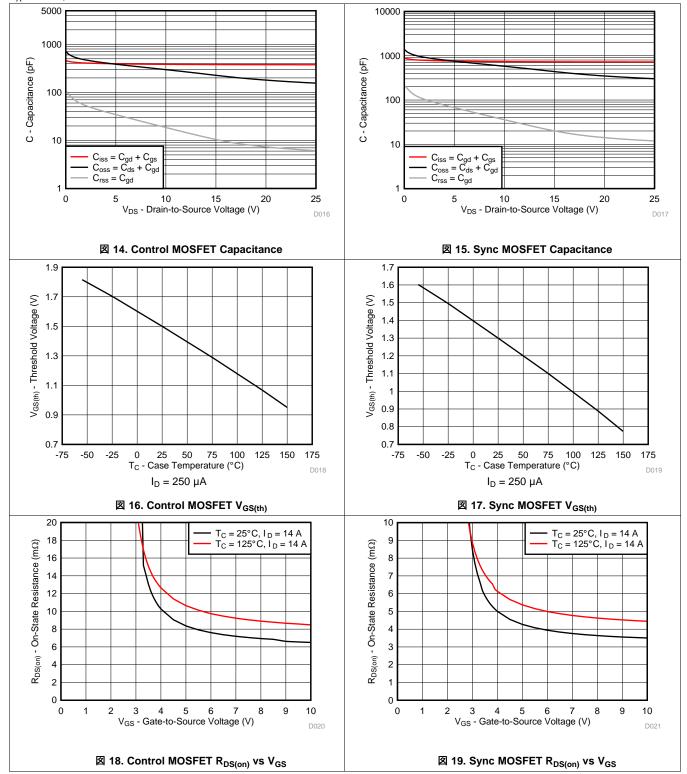

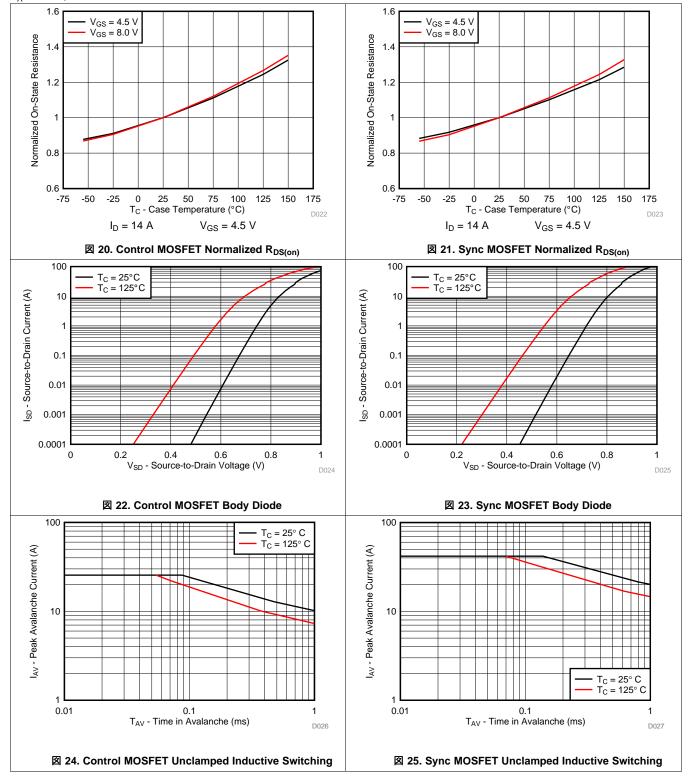

## 5.8 Typical Power Block MOSFET Characteristics

$T_A = 25$ °C, unless stated otherwise.

JAJSEY5 - MARCH 2018 www.tij.co.jp

## Typical Power Block MOSFET Characteristics (continued)

$T_A = 25$ °C, unless stated otherwise.

# TEXAS INSTRUMENTS

### Typical Power Block MOSFET Characteristics (continued)

$T_A = 25$ °C, unless stated otherwise.

JAJSEY5 - MARCH 2018 www.tii.co.ip

## **Application and Implementation**

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 6.1 Application Information

#### 6.1.1 Equivalent System Performance

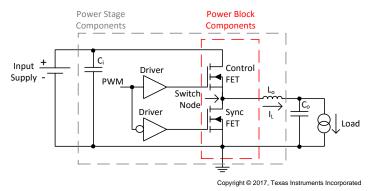

Many of today's high-performance computing systems require low-power consumption in an effort to reduce system operating temperatures and improve overall system efficiency. This has created a major emphasis on improving the conversion efficiency of today's synchronous buck topology. In particular, there has been an emphasis in improving the performance of the critical power semiconductor in the power stage of this application (see 226). As such, optimization of the power semiconductors in these applications, needs to go beyond simply reducing R<sub>DS(ON)</sub>.

図 26. Synchronous Buck Topology

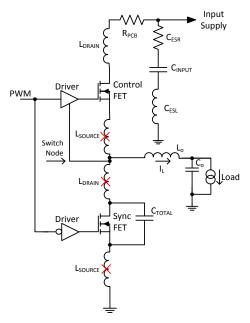

The CSD86336Q3D is part of Tl's power block product family which is a highly optimized product for use in a synchronous buck topology requiring high current, high efficiency, and high frequency. It incorporates TI's latest generation silicon which has been optimized for switching performance, as well as minimizing losses associated with Q<sub>GD</sub>, Q<sub>GS</sub>, and Q<sub>RR</sub>. Furthermore, TI's patented packaging technology has minimized losses by nearly eliminating parasitic elements between the control FET and sync FET connections (see 27). A key challenge solved by TI's patented packaging technology is the system level impact of Common Source Inductance (CSI). CSI greatly impedes the switching characteristics of any MOSFET which in turn increases switching losses and reduces system efficiency. As a result, the effects of CSI need to be considered during the MOSFET selection process. In addition, standard MOSFET switching loss equations used to predict system efficiency need to be modified in order to account for the effects of CSI. Further details behind the effects of CSI and modification of switching loss equations are outlined in Power Loss Calculation With Common Source Inductance Consideration for Synchronous Buck Converters (SLPA009).

#### **Application Information (continued)**

**図 27. Elimination of Common Source Inductance**

The combination of TI's latest generation silicon and optimized packaging technology has created a benchmarking solution that outperforms industry standard MOSFET chipsets of similar  $R_{DS(ON)}$  and MOSFET chipsets with lower  $R_{DS(ON)}$ . 28 and 29 compare the efficiency and power loss performance of the CSD86336Q3D versus industry standard MOSFET chipsets commonly used in this type of application. This comparison purely focuses on the efficiency and generated loss of the power semiconductors only. The performance of CSD86336Q3D clearly highlights the importance of considering the effective AC on-impedance  $(Z_{DS(ON)})$  during the MOSFET selection process of any new design. Simply normalizing to traditional MOSFET  $R_{DS(ON)}$  specifications is not an indicator of the actual in-circuit performance when using TI's power block technology.

www.tij.co.jp

## Application Information (continued)

表 1 compares the traditional DC measured R<sub>DS(ON)</sub> of CSD86336Q3D versus its Z<sub>DS(ON)</sub>. This comparison takes into account the improved efficiency associated with TI's patented packaging technology. As such, when comparing TI's power block products to individually packaged discrete MOSFETs or dual MOSFETs in a standard package, the in-circuit switching performance of the solution must be considered. In this example, individually packaged discrete MOSFETs or dual MOSFETs in a standard package would need to have DC measured  $R_{DS(ON)}$  values that are equivalent to the  $Z_{DS(ON)}$  value of CSD86336Q3D in order to have the same efficiency performance at full load. Mid to light-load efficiency will still be lower with individually packaged discrete MOSFETs or dual MOSFETs in a standard package.

| 表 | 1. | Compari | ison of | R <sub>DS(ON)</sub> | vs Z | Z <sub>DS(ON)</sub> |

|---|----|---------|---------|---------------------|------|---------------------|

|---|----|---------|---------|---------------------|------|---------------------|

| PARAMETER                                                             | HS  |      | LS  |     |

|-----------------------------------------------------------------------|-----|------|-----|-----|

| PARAMETER                                                             | TYP | MAX  | TYP | MAX |

| Effective AC on-impedance Z <sub>DS(ON)</sub> (V <sub>GS</sub> = 5 V) | 9.1 | _    | 3.4 | _   |

| DC measured R <sub>DS(ON)</sub> (V <sub>GS</sub> = 4.5 V)             | 9.1 | 11.4 | 4.6 | 5.7 |

The CSD86336Q3D NexFET™ power block is an optimized design for synchronous buck applications using 5-V gate drive. The control FET and sync FET silicon are parametrically tuned to yield the lowest power loss and highest system efficiency. As a result, a new rating method is needed which is tailored towards a more systemscentric environment. System-level performance curves such as power loss, safe operating area (SOA), and normalized graphs allow engineers to predict the product performance in the actual application.

#### 6.2 Power Loss Curves

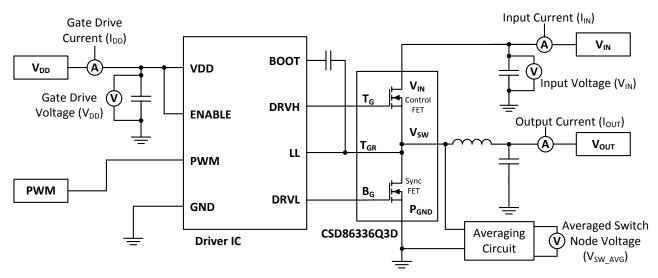

MOSFET centric parameters such as  $R_{DS(ON)}$  and  $Q_{od}$  are needed to estimate the loss generated by the devices. In an effort to simplify the design process for engineers, Texas Instruments has provided measured power loss performance curves. 2 1 plots the power loss of the CSD86336Q3D as a function of load current. This curve is measured by configuring and running the CSD86336Q3D as it would be in the final application (see 3 30). The measured power loss is the CSD86336Q3D loss and consists of both input conversion loss and gate drive loss. 式 1 is used to generate the power loss curve.

$$(V_{IN} \times I_{IN}) + (V_{DD} \times I_{DD}) - (V_{SW AVG} \times I_{OUT}) = power loss$$

(1)

The power loss curve in 2 1 is measured at the maximum recommended junction temperatures of 125°C under isothermal test conditions.

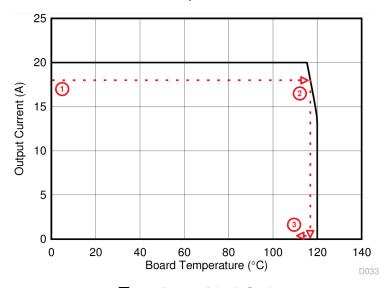

#### 6.3 Safe Operating Area (SOA) Curves

The SOA curve in the CSD86336Q3D data sheet provides guidance on the temperature boundaries within an operating system by incorporating the thermal resistance and system power loss. Z 3 outlines the temperature conditions required for a given load current. The area under the curve dictates the safe operating area. All the curves are based on measurements made on a PCB design with dimensions of 4 in (W) x 3.5 in (L) x 0.062 in (T) and 6 copper layers of 1-oz copper thickness.

#### 6.4 Normalized Curves

The normalized curves in the CSD86336Q3D data sheet provides guidance on the power loss and SOA adjustments based on their application specific needs. These curves show how the power loss and SOA boundaries will adjust for a given set of systems conditions. The primary Y-axis is the normalized change in power loss and the secondary Y-axis is the change in system temperature required in order to comply with the SOA curve. The change in power loss is a multiplier for the power loss curve and the change in temperature is subtracted from the SOA curve.

JAJSEY5 – MARCH 2018 www.tij.co.jp

# TEXAS INSTRUMENTS

#### **Normalized Curves (continued)**

Copyright © 2017, Texas Instruments Incorporated

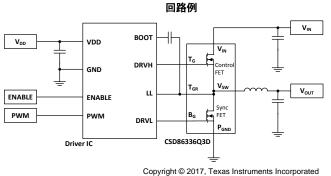

図 30. Typical Application

## 6.5 Calculating Power Loss and Safe Operating Area (SOA)

The user can estimate power loss and SOA boundaries by arithmetic means (see *Design Example*). Though the power loss and SOA curves in this data sheet are taken for a specific set of test conditions, the following procedure will outline the steps the user should take to predict product performance for any set of system conditions.

#### 6.5.1 Design Example

Operating conditions:

- Output current = 18.0 A

- Input voltage = 5.0 V

- Output voltage = 1.8 V

- Switching frequency = 750 kHz

- Inductor = 290 nH

## 6.5.2 Calculating Power Loss

- Power loss at 18 A = 3.03 W (☒ 1)

- Normalized power loss for input voltage ≈ 1.1 (図 5)

- Normalized power loss for output voltage ≈ 1.07 (図 6)

- Normalized power loss for output inductor ≈ 1.0 (図 7)

- Final calculated power loss = 3.03 W x 1.1 x 1.07 x 1.08 x 1.0 ≈ 3.85 W

#### 6.5.3 Calculating SOA Adjustments

- SOA adjustment for input voltage ≈ 1.0°C (図 5)

- SOA adjustment for output voltage ≈ 0.68°C (図 6)

- SOA adjustment for output inductor ≈ 0.02°C (図 7)

- Final calculated SOA adjustment = 1.0 + 0.68 + 0.75 + 0.02 ≈ 2.45°C

JAJSEY5 - MARCH 2018 www.tij.co.jp

## Calculating Power Loss and Safe Operating Area (SOA) (continued)

In the design example above, the estimated power loss of the CSD86336Q3D would increase to 3.85 W. In addition, the maximum allowable board and/or ambient temperature would have to decrease by 2.45°C. Z 31 graphically shows how the SOA curve would be adjusted accordingly.

- 1. Start by drawing a horizontal line from the application current to the SOA curve.

- 2. Draw a vertical line from the SOA curve intercept down to the board/ambient temperature.

- 3. Adjust the SOA board/ambient temperature by subtracting the temperature adjustment value.

In the design example, the SOA temperature adjustment yields a reduction in allowable board/ambient temperature of 2.45°C. In the event the adjustment value is a negative number, subtracting the negative number would yield an increase in allowable board/ambient temperature.

図 31. Power Block SOA

# TEXAS INSTRUMENTS

## 7 Layout

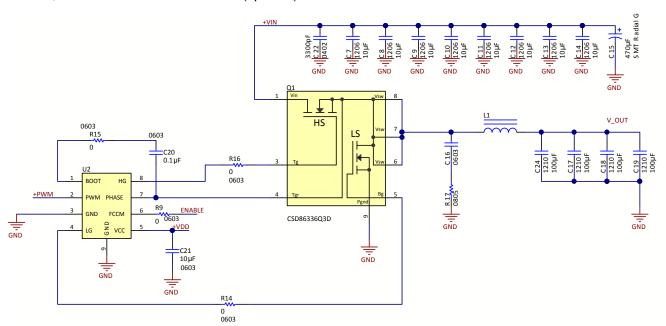

#### 7.1 Recommended Schematic Overview

There are several critical components that must be used in conjunction with this power block device.

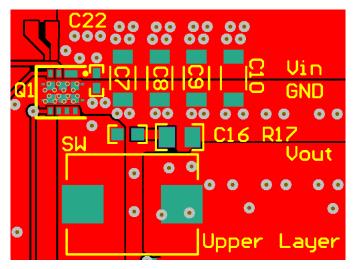

32 shows a portion of a schematic with the critical components needed for proper operation.

- C22: Bypass capacitor for V<sub>IN</sub> to help with ringing reduction

- C20: Bootstrap capacitor

- C21: Bypass capacitor for V<sub>DD</sub>

- C7-C14: Bypass capacitors for V<sub>IN</sub> (minimum of 40 μF)

- C15: Electrolytic capacitor for V<sub>IN</sub>

- R14, R16: Place holder for gate resistor (optional)

- R15: Place holder for bootstrap resistor (optional)

- R17, C16: Place holder for snubber (optional)

Copyright © 2017, Texas Instruments Incorporated

図 32. Recommended Schematic

JAJSEY5 - MARCH 2018 www.tij.co.jp

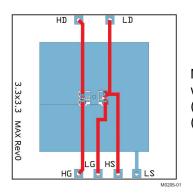

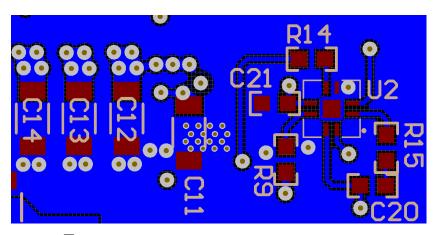

## 7.2 Recommended PCB Design Overview

There are two key system-level parameters that can be addressed with a proper PCB design: electrical and thermal performance. Properly optimizing the PCB layout yields maximum performance in both areas. A brief description on how to address each parameter follows.

#### 7.2.1 Electrical Performance

The power block has the ability to switch at voltage rates greater than 10 kV/us. Special care must be taken with the PCB layout design and placement of the input capacitors, inductor, driver IC and output capacitors.

- The placement of the input capacitors relative to the power block's VIN and PGND pins should have the highest priority during the component placement routine. It is critical to minimize these node lengths. As such, ceramic input capacitors need to be placed as close as possible to the VIN and PGND pins (see 33). It is recommended that one 3.3-nF (or similar), 0402, 50-V ceramic capacitor be placed on the top side of the board as close as possible to VIN and PGND pins. In addition, a minimum of 40 μF of bulk ceramic capacitance should be placed as close as possible to the power block in a design. For high-density design, some of these ceramic capacitors can be placed on the bottom layer of PCB with appropriate number of vias interconnecting both layers.

- The driver IC should be placed relatively close to the power block gate pins. T<sub>G</sub> and B<sub>G</sub> should connect to the outputs of the driver IC. The T<sub>GR</sub> pin serves as the return path of the high-side gate drive circuitry and should be connected to the phase pin of the IC (sometimes called LX, LL, SW, PH, etc.). The bootstrap capacitor for the driver IC will also connect to this pin.

- The switching node of the output inductor should be placed relatively close to the power block VSW pins. Minimizing the node length between these two components will reduce the PCB conduction losses and actually reduce the switching noise level. In the event the switch node waveform exhibits ringing that reaches undesirable levels, the use of a boost resistor or RC snubber can be an effective way to easily reduce the peak ring level. The recommended boost resistor value will range between 1.0  $\Omega$  to 4.7  $\Omega$  depending on the output characteristics of driver IC used in conjunction with the power block. The RC snubber values can range from 0.5  $\Omega$  to 2.2  $\Omega$  for the R and 330 pF to 2200 pF for the C. Please refer to *Snubber Circuits*: Theory, Design and Application (SLUP100) for more details on how to properly tune the RC snubber values. The RC snubber should be placed as close as possible to the VSW node and PGND (see ☒ 33 and ☒ 34).

- Keong W. Kam, David Pommerenke, "EMI Analysis Methods for Synchronous Buck Converter EMI Root Cause Analysis", University of Missouri – Rolla

JAJSEY5 – MARCH 2018 www.tij.co.jp

### Recommended PCB Design Overview (continued)

#### 7.2.2 Thermal Performance

The power block has the ability to utilize the GND planes as the primary thermal path. As such, the use of thermal vias is an effective way to pull away heat from the device and into the system board. Concerns of solder voids and manufacturability problems can be addressed by the use of three basic tactics to minimize the amount of solder attach that will wick down the via barrel:

- Intentionally space out the vias from each other to avoid a cluster of holes in a given area.

- Tent the opposite side of the via with solder-mask.

In the end, the number and drill size of the thermal vias should align with the end user's PCB design rules and manufacturing capabilities.

図 33. Recommended PCB Layout (Top Down View)

図 34. Recommended PCB Layout (Bottom View)

JAJSEY5 - MARCH 2018 www.tij.co.jp

## 8 デバイスおよびドキュメントのサポート

#### ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通 知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の 詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

#### 8.2 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™オンライン・コミュニティ TIのE2E (Engineer-to-Engineer) コミュニティ。エンジニア間の共同作 業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有 し、アイディアを検討して、問題解決に役立てることができます。

設計サポート *TIの設計サポート* 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることが できます。技術サポート用の連絡先情報も参照できます。

#### 8.3 商標

NexFET, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 8.4 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内 蔵しています。保存時または取り扱い時は、MOSゲートに対す る静電破壊を防 止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

#### 8.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# TEXAS INSTRUMENTS

## 9 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

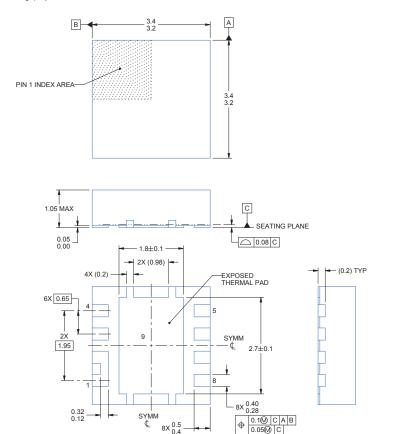

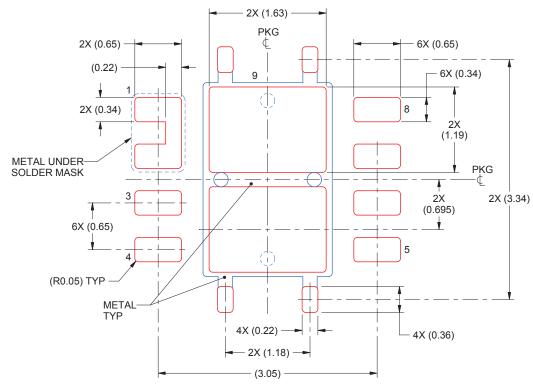

### 9.1 Q3Dパッケージの寸法

4218873/A 10/2016

- 1. すべての直線寸法はミリメートル(mm)単位です。括弧内のすべての寸法は、参照のみを目的としたものです。寸法と 許容誤差は、ASME Y14.5M準拠です。

- 2. この図面は、予告なく変更される可能性があります。

- 3. 最良の熱特性および機械的な性能を実現するため、パッケージのサーマル・パッドはプリント基板にハンダ付けする必要があります。

#### 9.2 ピン構成

| 位置          | 機能              |

|-------------|-----------------|

| ピン1         | $V_{IN}$        |

| ピン2         | $V_{IN}$        |

| ピン3         | $T_G$           |

| ピン4         | $T_GR$          |

| ピン5         | $B_G$           |

| ピン6         | $V_{SW}$        |

| ピン <b>7</b> | $V_{SW}$        |

| ピン8         | V <sub>SW</sub> |

| ピン9         | $P_{GND}$       |

www.tij.co.jp JAJSEY5 – MARCH 2018

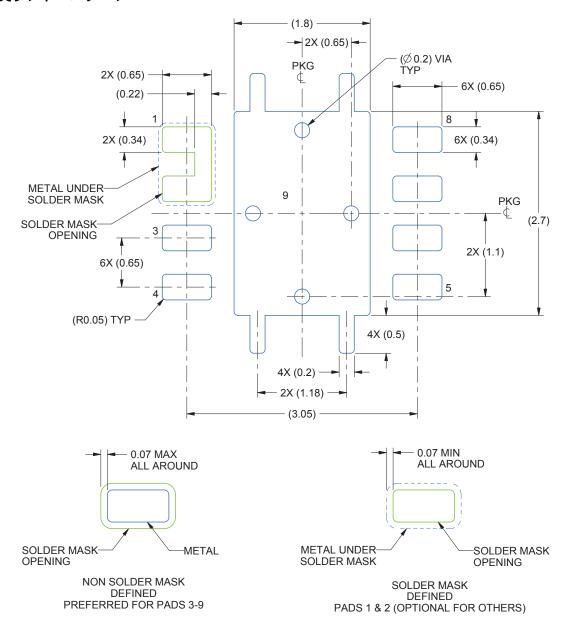

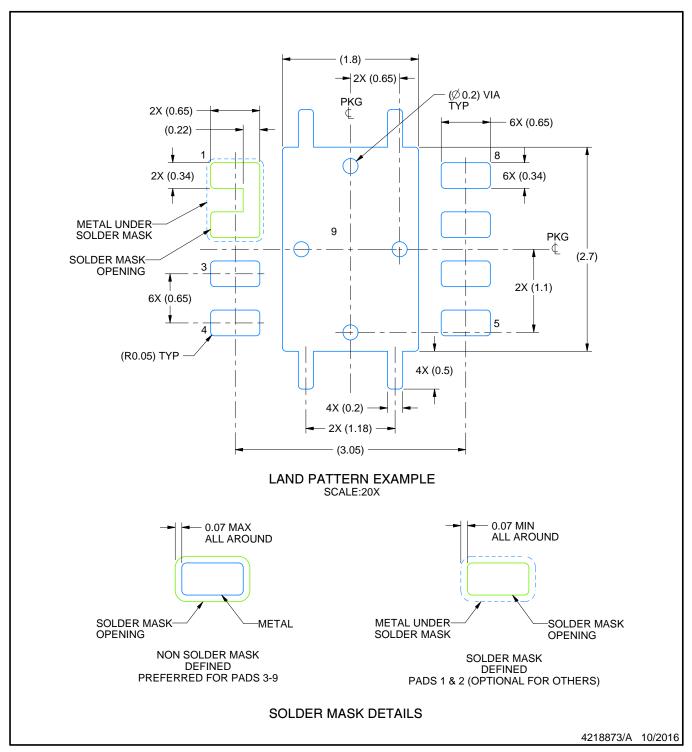

### 9.3 推奨ランド・パターン

Instruments

- 1. すべての直線寸法はミリメートル(mm)単位です。括弧内のすべての寸法は、参照のみを目的としたものです。寸法と 許容誤差は、ASME Y14.5M準拠です。

- 2. このパッケージは、基板上のサーマル・パッドにハンダ付けされるよう設計されています。詳細については、 『QFN/SON PCBアタッチメント』(SLUA271)を参照してください。

- 3. ビアはアプリケーションに応じてのオプションです。デバイスのデータシートを参照してください。一部またはすべてを実装する場合に推奨されるビアの場所が示されています。

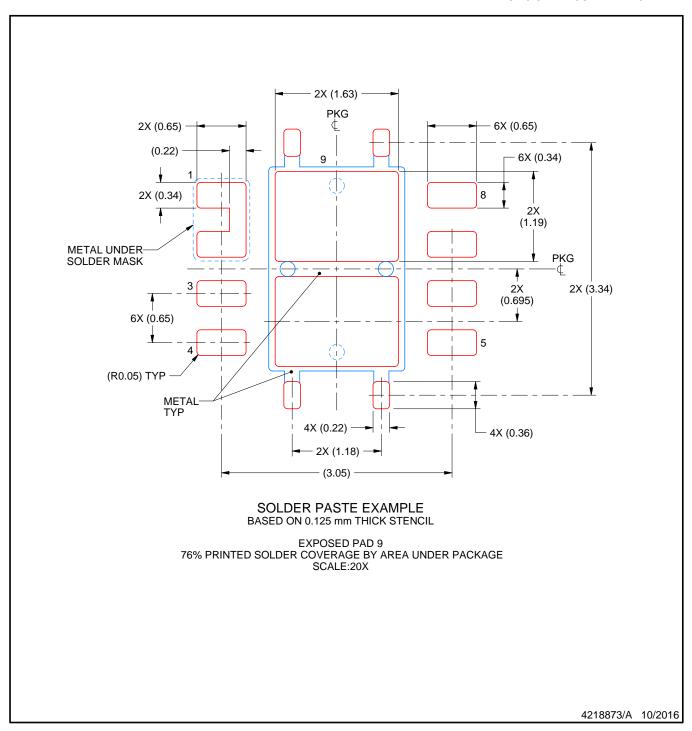

### 9.4 推奨ステンシル

- 1. すべての直線寸法はミリメートル(mm)単位です。括弧内のすべての寸法は、参照のみを目的としたものです。寸法と 許容誤差は、ASME Y14.5M準拠です。

- 2. レーザ・カット・アパーチャの壁面を台形にし、角に丸みを付けることで、ペースト離れが良くなります。IPC-7525には、別の設計推奨事項が存在する可能性があります。

www.ti.com 28-Jun-2023

#### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan               | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|------------------------|-------------------------------|--------------------|--------------|----------------------|---------|

| CSD86336Q3D      | ACTIVE        | VSON-CLIP    | DPB                | 8    | 2500           | RoHS-Exempt<br>& Green | SN                            | Level-1-260C-UNLIM | -55 to 150   | 86336D               | Samples |

| CSD86336Q3DT     | ACTIVE        | VSON-CLIP    | DPB                | 8    | 250            | RoHS-Exempt<br>& Green | SN                            | Level-1-260C-UNLIM | -55 to 150   | 86336D               | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **PACKAGE OPTION ADDENDUM**

www.ti.com 28-Jun-2023

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 29-Jun-2023

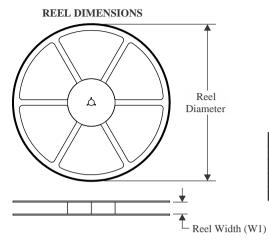

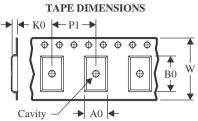

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

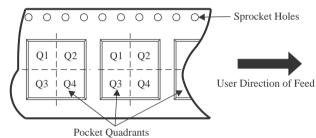

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CSD86336Q3D  | VSON-<br>CLIP   | DPB                | 8 | 2500 | 330.0                    | 12.4                     | 3.6        | 3.6        | 1.2        | 8.0        | 12.0      | Q1               |

| CSD86336Q3DT | VSON-<br>CLIP   | DPB                | 8 | 250  | 330.0                    | 12.4                     | 3.6        | 3.6        | 1.2        | 8.0        | 12.0      | Q1               |

www.ti.com 29-Jun-2023

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| CSD86336Q3D  | VSON-CLIP    | DPB             | 8    | 2500 | 336.6       | 336.6      | 41.3        |

| CSD86336Q3DT | VSON-CLIP    | DPB             | 8    | 250  | 336.6       | 336.6      | 41.3        |

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If some or all are implemented, recommended via locations are shown.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated