CSD18543Q3A

JAJSCR2 - DECEMBER 2016

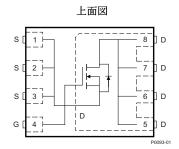

# CSD18543Q3A 60V NチャネルNexFET™パワーMOSFET

## 1 特長

- 非常に低いQ<sub>a</sub>およびQ<sub>ad</sub>

- 低いR<sub>DS(on)</sub>

- 低い熱抵抗

- アバランシェ定格

- 鉛不使用

- RoHS準拠

- ハロゲン不使用

- SON 3.3mm×3.3mmプラスチック・パッケージ

## 2 アプリケーション

- ソリッドステート・リレー・スイッチ

- DC/DC変換

- 2次側同期整流

- 絶縁コンバータの1次側スイッチ

- モータ制御

## 3 概要

この60V、 $8.1m\Omega$ 、 $SON 3.3mm \times 3.3mm$  NexFETTMパワーMOSFETは、電力変換アプリケーションにおいて損失を最小限に抑えるよう設計されています。

### 製品概要

| T <sub>A</sub> = 25° | С                 | 標準値                      | 単位   |       |  |  |  |

|----------------------|-------------------|--------------------------|------|-------|--|--|--|

| $V_{DS}$             | ドレイン-ソース間電圧       | 60                       |      | V     |  |  |  |

| $Q_g$                | 総ゲート電荷量(10V) 11.1 |                          |      |       |  |  |  |

| $Q_{gd}$             | ゲート-ドレイン間ゲート電荷量   | 1.7                      | nC   |       |  |  |  |

| R <sub>DS(on)</sub>  | ドレイン・ソース間オン抵抗     | V <sub>GS</sub> = 4.5V 1 | 12.0 | mΩ    |  |  |  |

|                      | トレイン・ノーへ同々ン松机     | V <sub>GS</sub> = 10V    | 8.1  | 11177 |  |  |  |

| $V_{GS(th)}$         | スレッショルド電圧         | 2.0                      | V    |       |  |  |  |

### 製品情報(1)

| デバイス         | メディア                 | 数量   | パッケージ                | 出荷       |

|--------------|----------------------|------|----------------------|----------|

| CSD18543Q3A  | 13インチ・リール            | 2500 | SON<br>3.30mm×3.30mm | テープ・アンド・ |

| CSD18543Q3AT | <b>7</b> インチ・リー<br>ル | 250  | プラスチック・パッケー<br>ジ     | リール      |

(1) 提供されているすべてのパッケージについては、巻末の注文情報 を参照してください。

#### 絶対最大定格

|                  | 48/19AX/ (7CTL                               |            |      |  |  |  |  |  |  |

|------------------|----------------------------------------------|------------|------|--|--|--|--|--|--|

| $T_A = 2$        | 25°C                                         | 値          | 単位   |  |  |  |  |  |  |

| $V_{DS}$         | ドレイン-ソース間電圧                                  | 60         | V    |  |  |  |  |  |  |

| $V_{GS}$         | ゲート-ソース間電圧                                   | ±20        | V    |  |  |  |  |  |  |

|                  | 連続ドレイン電流(パッケージ制限)                            | 35         |      |  |  |  |  |  |  |

| $I_D$            | 連続ドレイン電流(シリコン制限)、T <sub>C</sub> = 25°C       | 60         | Α    |  |  |  |  |  |  |

|                  | 連続ドレイン電流(1)                                  | 12         |      |  |  |  |  |  |  |

| $I_{DM}$         | パルス・ドレイン電流 <sup>(2)</sup>                    | 156        | Α    |  |  |  |  |  |  |

| 1                | 消費電力(1)                                      | 2.8        | 10/  |  |  |  |  |  |  |

| $P_D$            | 消費電力、T <sub>C</sub> = 25°C                   | 66         | W    |  |  |  |  |  |  |

| T <sub>J</sub> 、 | 動作時の接合部、                                     | -55~150    | °C   |  |  |  |  |  |  |

| $T_{\text{stg}}$ | 保管温度                                         | -55° × 150 | C    |  |  |  |  |  |  |

| E <sub>AS</sub>  | アバランシュ・エネルギー、単一パルス                           | 55         | mJ   |  |  |  |  |  |  |

| ►AS              | $I_D = 33A$ , $L = 0.1mH$ , $R_G = 25\Omega$ | 33         | IIIJ |  |  |  |  |  |  |

- (1) 厚さ0.06inのFR4 PCB上に構築された面積1in²、2オンスのCu パッド上で、標準値R $_{ ext{0JA}}$  = 45 $^{\circ}$ C/W

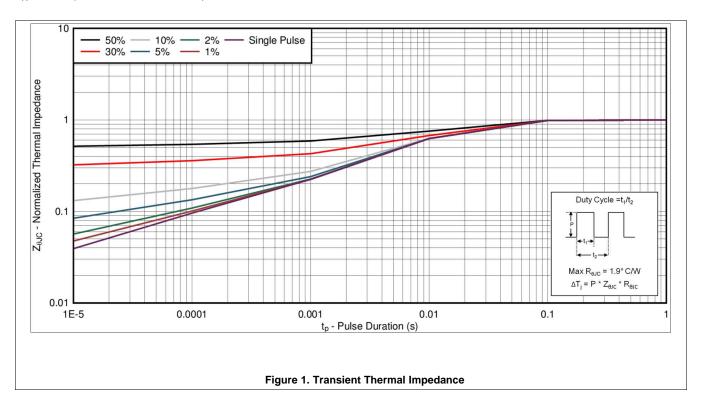

- (2) 最大R<sub> $\theta$ JC</sub> = 1.9°C/W、パルス期間  $\leq$  100 $\mu$ s、デューティ・サイクル < 10 $\ell$

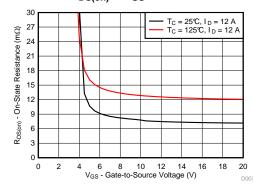

## R<sub>DS(on)</sub>とV<sub>GS</sub>との関係

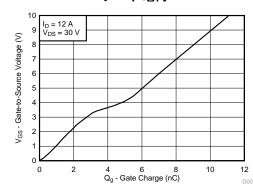

#### ゲート電荷

# 目次

| 1 | 特長                                 | 1 | 6.   | i.1 ドキュメントの更新通知を受け取る方法  |

|---|------------------------------------|---|------|-------------------------|

| 2 | アプリケーション                           | 1 | 6.   | i.2 コミュニティ・リソース         |

|   | 概要                                 |   | 6.   | 6.3 商標7                 |

| - | 改訂履歴                               |   | 6.   | i.4 静電気放電に関する注意事項 7     |

|   | Specifications                     |   | 6.   | 5.5 用語集                 |

| • | 5.1 Electrical Characteristics     |   | 7 メン | カニカル、パッケージ、および注文情報8     |

|   | 5.2 Thermal Information            | _ | 7.   | '.1 Q3Aパッケージの寸法8        |

|   | 5.3 Typical MOSFET Characteristics |   | 7.   | '.2 Q3Aの推奨PCBパターン9      |

| 6 | デバイスおよびドキュメントのサポート                 |   | 7.   | 7.3 Q3Aの推奨ステンシル・パターン10  |

| U | 7 / "[/NOAUTT 4/V [V/)             | • | 7.   | 7.4 Q3Aのテープ・アンド・リール情報10 |

# 4 改訂履歴

| 日付       | 改訂内容 | 注  |

|----------|------|----|

| 2016年12月 | *    | 初版 |

# 5 Specifications

www.ti.com

#### 5.1 Electrical Characteristics

$T_A = 25^{\circ}C$  (unless otherwise stated)

|                     | PARAMETER                        | TEST CONDITIONS                                                  | MIN T | YP MAX   | UNIT |

|---------------------|----------------------------------|------------------------------------------------------------------|-------|----------|------|

| STATIC              | CHARACTERISTICS                  |                                                                  |       |          |      |

| BV <sub>DSS</sub>   | Drain-to-source voltage          | V <sub>GS</sub> = 0 V, I <sub>D</sub> = 250 μA                   | 60    |          | V    |

| I <sub>DSS</sub>    | Drain-to-source leakage current  | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 48 V                    |       | 1        | μА   |

| I <sub>GSS</sub>    | Gate-to-source leakage current   | V <sub>DS</sub> = 0 V, V <sub>GS</sub> = 20 V                    |       | 100      | nA   |

| V <sub>GS(th)</sub> | Gate-to-source threshold voltage | $V_{DS} = V_{GS}, I_{D} = 250 \mu A$                             | 1.5   | 2.0 2.7  | V    |

|                     | Drain-to-source                  | V <sub>GS</sub> = 4.5 V, I <sub>D</sub> = 12 A                   | 1:    | 2.0 15.6 | mΩ   |

| R <sub>DS(on)</sub> | on resistance                    | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 12 A                    |       | 3.1 9.9  | mΩ   |

| 9 <sub>fs</sub>     | Transconductance                 | V <sub>DS</sub> = 6 V, I <sub>D</sub> = 12 A                     |       | 40       | S    |

| DYNAMI              | C CHARACTERISTICS                |                                                                  |       |          |      |

| C <sub>iss</sub>    | Input capacitance                |                                                                  | 8     | 85 1150  | pF   |

| C <sub>oss</sub>    | Output capacitance               | $V_{GS} = 0 \text{ V}, V_{DS} = 30 \text{ V}, f = 1 \text{ MHz}$ | 1     | 68 218   | pF   |

| C <sub>rss</sub>    | Reverse transfer capacitance     |                                                                  |       | 4.8 6.2  | pF   |

| R <sub>G</sub>      | Series gate resistance           |                                                                  |       | 0.5 1.0  | Ω    |

| Qg                  | Gate charge total (4.5 V)        |                                                                  |       | 5.6 7.3  | . 0  |

| Qg                  | Gate charge total (10 V)         |                                                                  | 1     | 1.1 14.5 | nC   |

| $Q_{gd}$            | Gate charge gate-to-drain        | V <sub>DS</sub> = 30 V, I <sub>D</sub> = 12 A                    |       | 1.7      | nC   |

| Q <sub>gs</sub>     | Gate charge gate-to-source       |                                                                  | ;     | 3.1      | nC   |

| Q <sub>g(th)</sub>  | Gate charge at V <sub>th</sub>   |                                                                  |       | 2.0      | nC   |

| Q <sub>oss</sub>    | Output charge                    | V <sub>DS</sub> = 30 V, V <sub>GS</sub> = 0 V                    |       | 24       | nC   |

| t <sub>d(on)</sub>  | Turnon delay time                |                                                                  |       | 9        | ns   |

| t <sub>r</sub>      | Rise time                        | V <sub>DS</sub> = 30 V, V <sub>GS</sub> = 10 V,                  |       | 18       | ns   |

| t <sub>d(off)</sub> | Turnoff delay time               | $I_{DS} = 12 \text{ A}, R_G = 0 \Omega$                          |       | 8        | ns   |

| t <sub>f</sub>      | Fall time                        |                                                                  |       | 4        | ns   |

| DIODE C             | HARACTERISTICS                   |                                                                  |       |          | •    |

| $V_{SD}$            | Diode forward voltage            | I <sub>SD</sub> = 12 A, V <sub>GS</sub> = 0 V                    |       | 0.8 1.0  | V    |

| Q <sub>rr</sub>     | Reverse recovery charge          | $V_{DS} = 30 \text{ V}, I_F = 12 \text{ A},$                     |       | 37       | nC   |

| t <sub>rr</sub>     | Reverse recovery time            | di/dt = 300 A/μs                                                 |       | 27       | ns   |

### 5.2 Thermal Information

$T_A = 25$ °C (unless otherwise stated)

|                 | THERMAL METRIC                                           | MIN | TYP | MAX | UNIT |

|-----------------|----------------------------------------------------------|-----|-----|-----|------|

| $R_{\theta JC}$ | Junction-to-case thermal resistance <sup>(1)</sup>       |     |     | 1.9 | °C/W |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance <sup>(1)(2)</sup> |     |     | 55  | C/VV |

<sup>(1)</sup> R<sub>θJC</sub> is determined with the device mounted on a 1-in² (6.45-cm²), 2-oz (0.071-mm) thick Cu pad on a 1.5-in x 1.5-in (3.81-cm x 3.81-cm), 0.06-in (1.52-mm) thick FR4 PCB. R<sub>θJC</sub> is specified by design, whereas R<sub>θJA</sub> is determined by the user's board design.

<sup>(2)</sup> Device mounted on FR4 material with 1-in<sup>2</sup> (6.45-cm<sup>2</sup>), 2-oz (0.071-mm) thick Cu.

Max  $R_{\theta JA} = 55^{\circ} C/W$  when mounted on 1 in<sup>2</sup> (6.45 cm<sup>2</sup>) of 2-oz (0.071-mm) thick Cu.

Max  $R_{\theta JA} = 160^{\circ}\text{C/W}$  when mounted on a minimum pad area of 2-oz (0.071-mm) thick Cu.

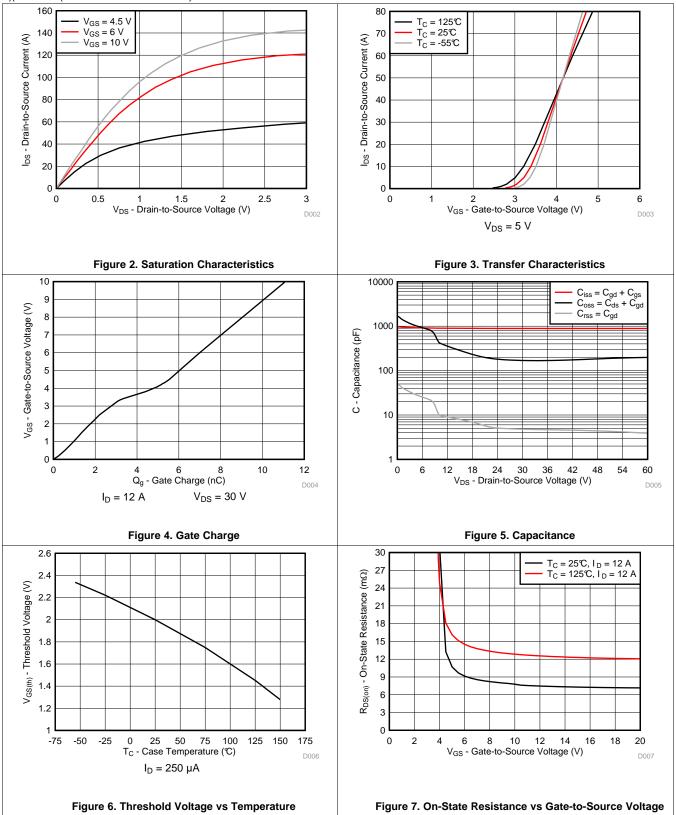

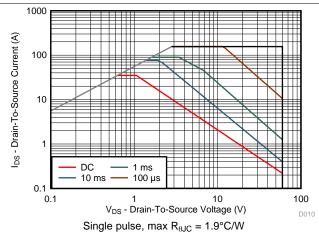

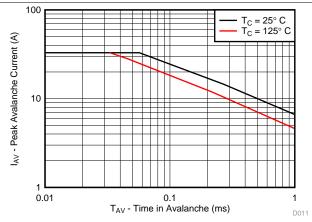

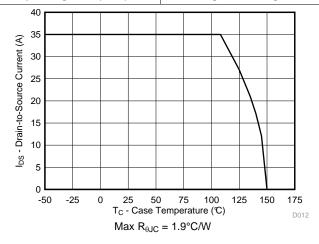

## 5.3 Typical MOSFET Characteristics

$T_A = 25$ °C (unless otherwise stated)

www.ti.com

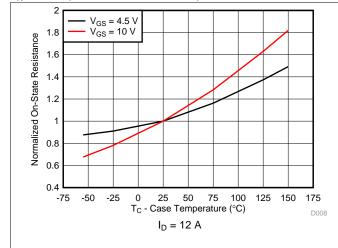

## **Typical MOSFET Characteristics (continued)**

$T_A = 25$ °C (unless otherwise stated)

## TEXAS INSTRUMENTS

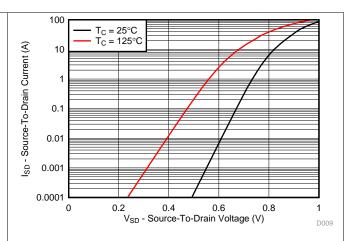

## **Typical MOSFET Characteristics (continued)**

$T_A = 25$ °C (unless otherwise stated)

Figure 8. Normalized On-State Resistance vs Temperature

Figure 9. Typical Diode Forward Voltage

Figure 10. Maximum Safe Operating Area (SOA)

Figure 11. Single Pulse Unclamped Inductive Switching

Figure 12. Maximum Drain Current vs Temperature

www.tij.co.jp JAJSCR2 – DECEMBER 2016

## 6 デバイスおよびドキュメントのサポート

#### 6.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

#### 6.2 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™オンライン・コミュニティ *TIのE2E(Engineer-to-Engineer)コミュニティ。*エンジニア間の共同作業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有し、アイディアを検討して、問題解決に役立てることができます。

設計サポート *TIの設計サポート* 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることができます。技術サポート用の連絡先情報も参照できます。

#### 6.3 商標

NexFET, E2E are trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 6.4 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

#### 6.5 用語集

SLYZ022 — TI用語集.

この用語集には、用語や略語の一覧および定義が記載されています。

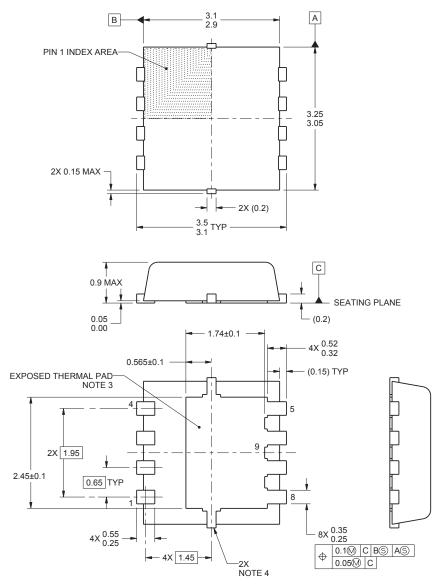

# 7 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

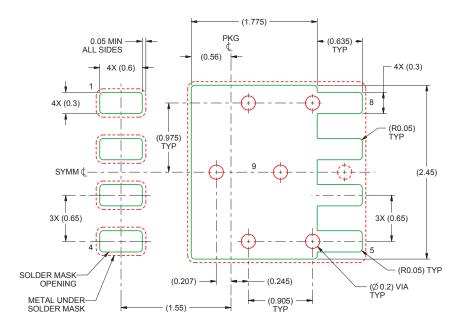

#### 7.1 Q3Aパッケージの寸法

- 1. すべての直線寸法はミリメートル(mm)単位です。括弧内のすべての寸法は、参照のみを目的としたものです。寸法と 許容誤差は、ASME Y14.5M準拠です。

- 2. この図面は、予告なく変更される可能性があります。

- 3. 熱特性および機械的な性能を実現するため、パッケージのサーマル・パッドはプリント基板にハンダ付けする必要があります。

- 4. 金属被覆部分はベンダのオプションで、パッケージには含まれていない場合があります。

- 5. すべての寸法には、バリや突起部は含まれていません。

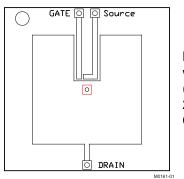

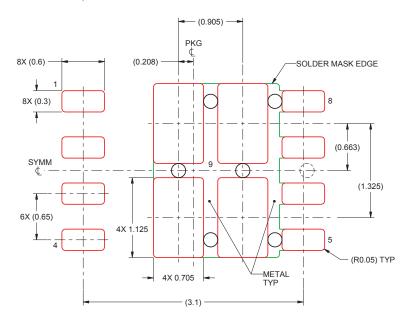

### 7.2 Q3Aの推奨PCBパターン

- 1. このパッケージは、基板上のサーマル・パッドにハンダ付けされるよう設計されています。詳細については、 『QFN/SON PCBアタッチメント』(SLUA271)を参照してください。

- 2. ビアはアプリケーションに応じてのオプションです。デバイスのデータシートを参照してください。一部またはすべてを実装する場合に推奨されるビアの場所が示されています。

PCB設計の推奨回路レイアウトについては、『PCBレイアウト技法によるリンギングの低減』(SLPA005)を参照してください。

## 7.3 Q3Aの推奨ステンシル・パターン

1. レーザ・カット・アパーチャの壁面を台形にし、角に丸みを付けることで、ペースト離れが良くなります。IPC-7525には、別の設計推奨事項が存在する可能性があります。

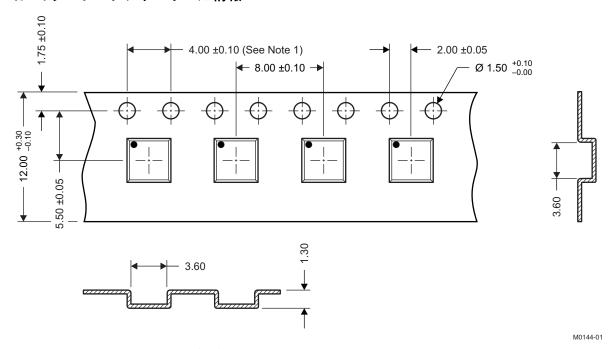

## 7.4 Q3Aのテープ・アンド・リール情報

Notes: 1. 10スプロケット・ホール・ピッチの累積許容誤差は $\pm 0.2$ 。

- 2. キャンバーは100mm内に1mmを超えないこと、250mm以上では累積しない

- 3. 材質: 黒色の静電散逸性ポリスチレン

- 4. すべての寸法は、特記されていない限りmm単位

- 5. 厚さ: 0.30±0.05mm。

- 6. MSL1 260℃ (IRおよび対流方式) PbFリフロー互換

## PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| CSD18543Q3A      | ACTIVE | VSONP        | DNH                | 8    | 2500           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -55 to 150   | 18543                   | Samples |

| CSD18543Q3AT     | ACTIVE | VSONP        | DNH                | 8    | 250            | RoHS & Green | SN                            | Level-1-260C-UNLIM | -55 to 150   | 18543                   | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

#### 重要なお知らせと免責事項

TI は、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションが適用される各種規格や、その他のあらゆる安全性、セキュリティ、またはその他の要件を満たしていることを確実にする責任を、お客様のみが単独で負うものとします。上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件(www.tij.co.jp/ja-jp/legal/termsofsale.html)、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供 する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用されるTI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

Copyright © 2020, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社