# AFE58JD28 16チャネル超音波AFE、電力102mW/チャネル、ノイズ0.8nV/ $\sqrt{\text{Hz}}$ 、14ビット/65MSPSまたは12ビット/80MSPS ADC、デジタル復調器、JESDまたはLVDSインターフェイス、およびパッシブCWミキサー

## 1 特長

- 超音波アプリケーション用の16チャネルAFE

- TGCおよびCWモードに最適化された信号チェーン

- 4つのTGCプロファイルをプログラム可能

- 低ノイズのアンプ(LNA)

- プログラム可能なゲイン: 21dB, 18dB, 15dB

- リニア入力信号の振幅: 0.37V<sub>PP</sub>, 0.5V<sub>PP</sub>, 0.71V<sub>PP</sub>

- アクティブ・タミネーション

- 電圧制御アッテネータ(VCAT):

- 減衰範囲: 0dB~36dB

- プログラム可能なゲイン・アンプ(PGA)

- 18dB~27dBで3dB単位

- 3次、リニア位相のローパス・フィルタ(LPF)

- カットオフ周波数は10MHz~30MHz

- ADCモード(アイドル・チャネルSNR)

- 14ビット、65MSPSモード: 75dBFS

- 12ビット、80MSPSモード: 72dBFS

- ノイズおよび電力に最適化:

- TGCモード: 0.8nV/ $\sqrt{\text{Hz}}$ , 65MSPS、14ビット出力で102mW/Ch

- CWモード: 63mW/Ch

- 非常に優れたデバイス間のゲイン一致

- $\pm 0.4\text{dB}$  (標準値)

- 高速で一貫した過負荷からの回復

- 連続波形(CW)パス

- 2.5MHzのキャリアから1kHzの周波数オフセットで、-159dBc/Hzの低いクローズ・イン位相ノイズ

- 位相分解能:  $\lambda/16$

- 16xおよび8xのCWクロックをサポート

- 3次および5次高調波の12dBの抑制

- デジタルI/Q復調器

- フラクショナル間引きフィルタ:  $M = 1\sim 63$ 、増分0.25

- 間引き後のデータ・スループット低減

- 32のプリセット・プロファイルを持つオンチップRAM

- 最高速度1GbpsのLVDSインターフェイス

- 5GbpsのJESDインターフェイス

- JESD204Bサブクラス0、1、2

- JESDレーンごとに2、4、8チャネル

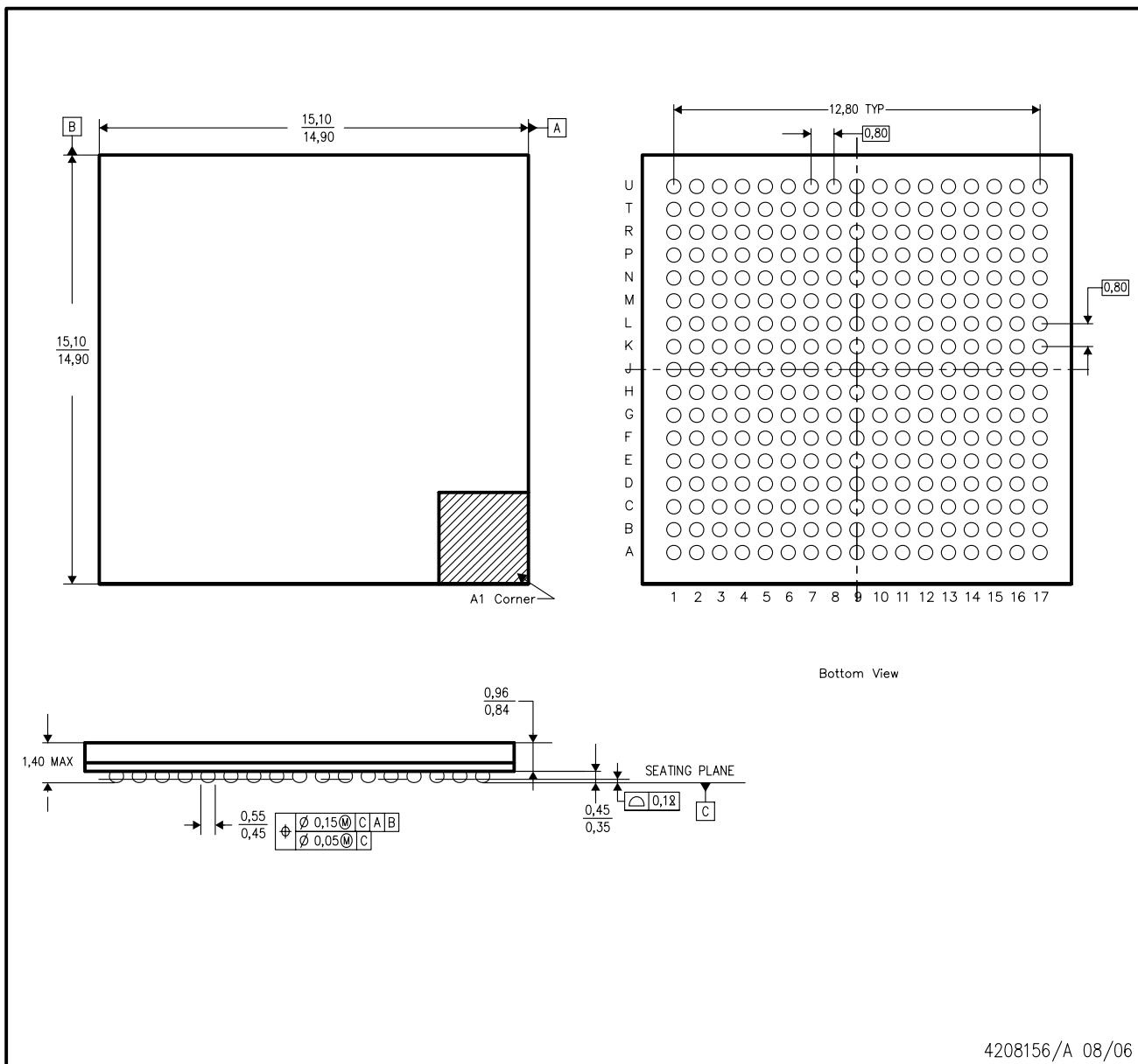

- 小型のパッケージ: 15mm×15mm NFBGA-289

## 2 アプリケーション

- 医療用超音波画像処理

- 非破壊的評価機器

- ソナー・イメージング機器

## 3 概要

AFE58JD28デバイスは、高度に統合されたアナログ・プロセントエンド(AFE)ソリューションで、高性能、低消費電力、小さなサイズが要求される超音波システム向けに特化して設計されています。

### 製品情報<sup>(1)</sup>

| 型番        | パッケージ       | 本体サイズ(公称)       |

|-----------|-------------|-----------------|

| AFE58JD28 | nFBGA (289) | 15.00mm×15.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にあるパッケージ・オプションについての付録を参照してください。

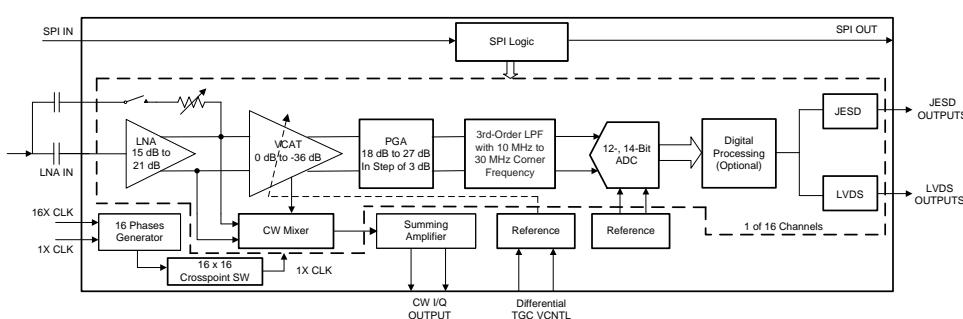

### ブロック概略図

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、[www.ti.com](http://www.ti.com)で閲覧でき、その内容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

## 4 概要（続き）

AFE58JD28は、医療用超音波アプリケーションに最適化された、統合AFEです。このデバイスは、2つのダイを持つマルチチップ・モジュール(MCM)により実現されています。ダイの1つは電圧制御アンプ(VCA)で、もう1つはアナログ/デジタル・コンバータ(ADC)です。VCAダイには16のチャネルがあり、ADCダイの16のチャネルと接続します。

VCAダイの各チャネルは、時間ゲイン補償(TGC)モード、または連続波形(CW)モードに設定できます。TGCモードでは、各チャネルに低ノイズのアンプ(LNA)、電圧制御アッテネータ(VCAT)、プログラム可能なゲイン・アンプ(PGA)、3次のローパス・フィルタ(LPF)が含まれます。LNAのゲインは、21dB、18dB、15dBにプログラム可能です。また、LNAはアクティブ・ターミネーションをサポートしています。VCATは0dB～36dBの減衰範囲をサポートし、アナログ電圧制御により減衰を実行します。PGAのゲイン・オプションは、3dB単位で18dB～27dBです。LPFカットオフ周波数は10MHz～30MHzで、各種の周波数の超音波アプリケーションに対応できます。CWモードでは、LNAの出力は低消費電力のパッシブ・ミキサーに送られ、16種類の位相遅延を選択できます。その後で出力は、バンドパス・フィルタ付きの加算アンプへ送られます。それぞれのアナログ入力信号へ各種の位相遅延を適用することで、オンチップのビームフォーミングを実行できます。CWミキサーの高調波フィルタは、3次および5次の高調波を抑制し、CWドップラー測定の感度を向上します。

ADCダイの16のチャネルは、14ビットまたは12ビットの分解能で動作するよう設定できます。ADCの分解能は変換速度とのトレードオフになり、分解能14ビットでは65MSPS、12ビットでは80MSPSまでの速度で動作可能です。ADCは、電力とサンプリング・レートでスケーリングを行うよう設計されています。ADCの出力インターフェイスは、低電圧差動信号処理(LVDS)を経由して出力され、低コストのフィールド・プログラマブル・ゲート・アレイ(FPGA)と簡単に接続できます。

さらに、AFE58JD28にはデジタル復調器と、JESD204Bデータ・パッキング・ブロックが含まれています。デジタル同相および直交(I/Q)復調器と、プログラム可能な間引きフィルタにより、低消費電力において計算量の多いアルゴリズムを高速化できます。また、このデバイスはオプションのJESD204Bインターフェイスもサポートし、最高5Gbpsで動作するため、チャネル数の多いシステムにおける回路基板の配線の課題をさらに軽減できます。

このデバイスは、システム性能を最適化するため、各種の電力とノイズの組み合わせを選択できます。この理由から、これらのデバイスは、厳格なバッテリ駆動時間の要件があるシステムに適した超音波AFEソリューションとなります。

このデバイスは、15mm×15mmのNFBGA-289パッケージで供給され、AFE5818およびAFE5816アミリとピン互換です。

## 5 デバイスおよびドキュメントのサポート

### 5.1 ドキュメントのサポート

#### 5.1.1 関連資料

関連資料については、以下を参照してください。

- 『AFE5818 16チャネル、超音波アナログ・フロントエンド、電力140mW/チャネル、ノイズ0.75nV/ $\sqrt{\text{Hz}}$ 、14ビット、65MSPSまたは12ビット、80MSPS ADC、およびパッシブCWミキサー』

- 『AFE5816 16チャネル、超音波AFE、電力90mW/チャネル、ノイズ1nV/ $\sqrt{\text{Hz}}$ 、14ビット、65MSPSまたは12ビット、80MSPS ADC、およびパッシブCWミキサー』

- 『AFE58JD18 16チャネル、超音波AFE、14ビット、65MSPSまたは12ビット、80MSPS ADC、パッシブCWミキサー、I/Q復調器、およびLVDS、JESD204B出力』

- 『TLV5626 内部基準電圧およびパワー・ダウン搭載、2.7V~5.5Vの低消費電力デュアル8ビット・デジタル/アナログ・コンバータ』

- 『DAC7821 12ビット、並列入力、マルチプライ・デジタル/アナログ・コンバータ』

- 『THS413x 高速、低ノイズ、完全差動I/Oアンプ』

- 『OPA1632 高性能、完全差動オーディオ・オペアンプ』

- 『広帯域の差動トランジスタインピーダンスDAC出力』

- 『LMK0482x 超低ノイズ、JESD204B準拠のクロック・ジッタ・クリーナ、デュアル・ループPLL搭載』

- 『CDCM7005 3.3V、高性能クロック・シンクロナイザ/ジッタ・クリーナ』

- 『CDCE72010 10出力の高性能クロック・シンセサイザ、ジッタ・クリーナ、およびクロック分配器』

- 『OPA2x11 ノイズ1.1nV/ $\sqrt{\text{Hz}}$ 、低消費電力、高精度オペアンプ』

- 『ADS8413 16ビット、2MSPS、LVDSシリアル・インターフェイス、SARアナログ/デジタル・コンバータ』

- 『ADS8472 16ビット、1MSPS、疑似バイポーラ、完全差動入力、Micropowerサンプリングのアナログ/デジタル・コンバータ、パラレル・インターフェイスおよび基準電圧搭載』

- 『高速データ・コンバータのクロック処理』テクニカル・ブリーフ

- 『ISO724x 高速、クワッド・チャネルのデジタル・アイソレータ』

- 『SN74AUP1T04 低消費電力、1.8/2.5/3.3V入力、3.3V CMOS出力、シングル・インバータ・ゲート』

- 『MicroStar BGAパッケージング・リファレンス・ガイド』

### 5.2 商標

All trademarks are the property of their respective owners.

### 5.3 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

### 5.4 Glossary

#### SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 6 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあります、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## MECHANICAL DATA

### ZAV (S-PBGA-N289)

### PLASTIC BALL GRID ARRAY

- NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- This is a lead-free solder ball design.

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier     | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|---------------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| AFE58JD28ZAV          | Active        | Production           | NFBGA (ZAV)   289 | 126   JEDEC<br>TRAY (5+1) | Yes         | SNAGCU                               | Level-3-260C-168 HR               | -40 to 85    | AFE58JD28           |

| AFE58JD28ZAV.A        | Active        | Production           | NFBGA (ZAV)   289 | 126   JEDEC<br>TRAY (5+1) | Yes         | SNAGCU                               | Level-3-260C-168 HR               | -40 to 85    | AFE58JD28           |

| AFE58JD28ZAV.B        | Active        | Production           | NFBGA (ZAV)   289 | 126   JEDEC<br>TRAY (5+1) | -           | Call TI                              | Call TI                           | -40 to 85    |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

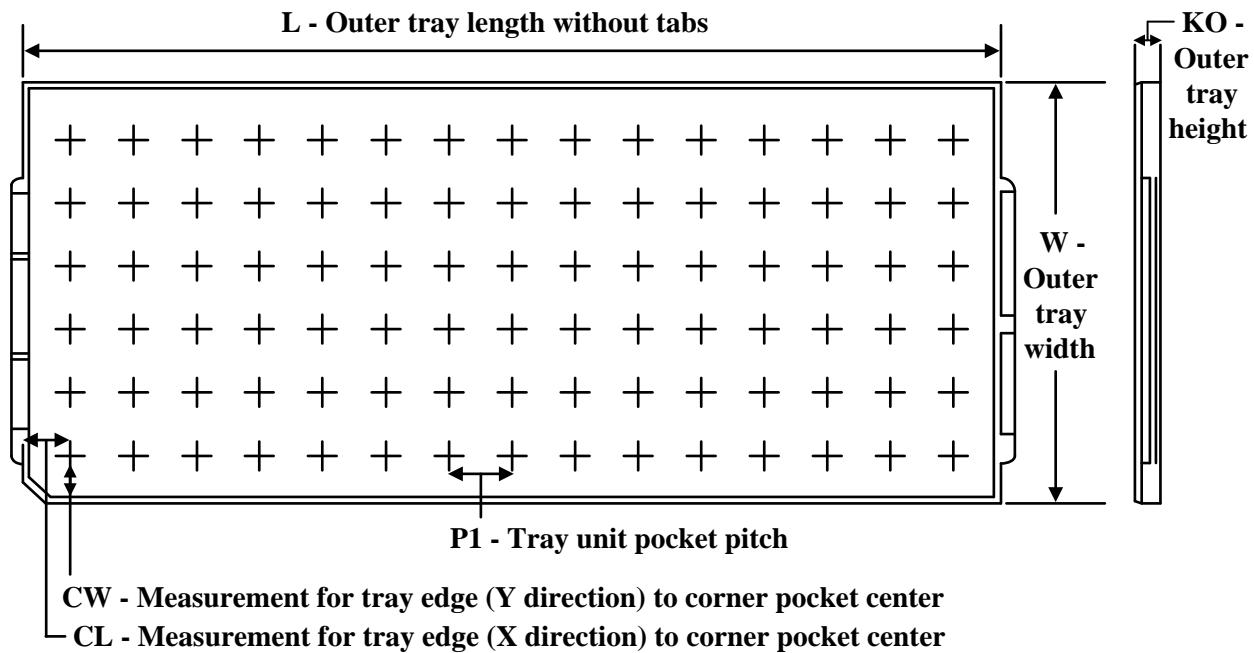

**TRAY**

Chamfer on Tray corner indicates Pin 1 orientation of packed units.

\*All dimensions are nominal

| Device         | Package Name | Package Type | Pins | SPQ | Unit array matrix | Max temperature (°C) | L (mm) | W (mm) | KO (µm) | P1 (mm) | CL (mm) | CW (mm) |

|----------------|--------------|--------------|------|-----|-------------------|----------------------|--------|--------|---------|---------|---------|---------|

| AFE58JD28ZAV   | ZAV          | NFBGA        | 289  | 126 | 7 X 18            | 150                  | 315    | 135.9  | 7620    | 17.2    | 11.3    | 16.35   |

| AFE58JD28ZAV.A | ZAV          | NFBGA        | 289  | 126 | 7 X 18            | 150                  | 315    | 135.9  | 7620    | 17.2    | 11.3    | 16.35   |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月