ZHCAC69 February 2023 TRF1108 , TRF1208

1 应用简报

引言

Xilinx RFSoC 平台集成了多达 16 个高速射频采样数据转换器器件。这些数据转换器支持高达 7GHz 甚至更高的信号频率。由于在一个器件中实现了这种级别的通道集成,因此传统的无源平衡-非平衡变压器接口与增益级耦合会引发物理布板空间问题。要将所有元件靠近具有如此多通道的数据转换器引脚放置是一项艰巨的任务。此外,变压器和平衡-非平衡变压器传统上具有窄带。因此,虽然数据转换器器件支持宽频率范围,但实际设计会受到平衡-非平衡变压器带宽性能的限制。

德州仪器 (TI) 的 TRF1208 和 TRF1108 器件引入了宽带有源平衡-非平衡变压器。TRF1208 支持 ADC 接口的单端到差分转换。TRF1108 支持差分至单端转换,能够为发送器器件提供更高的输出功率。这些器件尺寸小巧 (2mm × 2mm),与市场上一些较小的无源平衡-非平衡变压器相当。更重要的是,这些器件都是宽带器件,工作频率几乎高达 12GHz。通过这一个接口,无需修改主要元件即可支持所有频段。如果需要针对特定频率或布局拓扑优化该接口,只能修改少量无源匹配元件。

本报告使用相应器件的已发布 S 参数补全了仿真接口,以演示 TRF1x08 和 Xilinx RFSoC 之间的性能预期。这些仿真使用 Agilent® 的 ADS 电路仿真。这些仿真包括一个真实的互连拓扑结构,以考虑将器件连接在一起所需的真实布线长度。Xilinx RFSoC S 参数反映了 ZCU670 开发板。这些参数可通过 Xilinx 网页获得。TRF1x08 S 参数可从 TI 网站上各自的产品页面中获得。

RFSoC 接收器

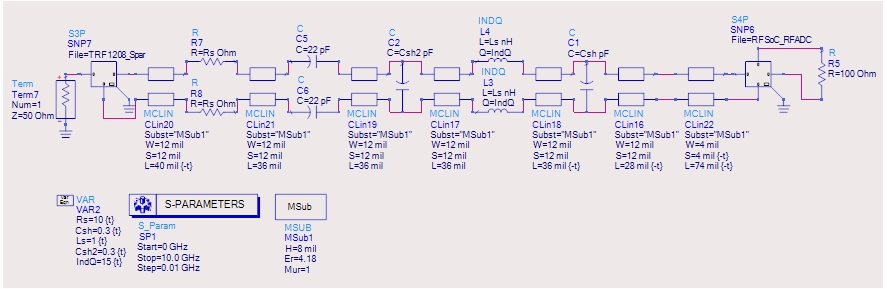

图 1-1 展示了包括互连走线在内的接收器电路拓扑。其目的是展示一种使用 0201 尺寸无源器件的紧凑型设计。默认情况下,差分走线彼此靠近。差分走线建模为具有指定宽度和间距的耦合线路,从而保持 100Ω 的差分阻抗。基板的高度定义为 8mil,介电常数为 4.1。高度保持在 8mil 至 10mil 范围内,以使布线宽度保持相对较小,但从顶层到接地层提供足够的间距,以尽可能地减小平面电容,从而在更高的频率下人为地降低性能。

电容器模型是一个标准的理想元件。如果需要,可以使用实际电容器的 S 参数模型来实现高工作频率。对于高频匹配电路,可以使用 AVX AccuP 系列等高品质高频微波电容器。电感器元件是一个纯电感器,其中包含损耗因子参数 Q。同样,此处可以使用特定电感器的器件特定 S 参数文件。Murata® LQP03 系列等高品质微波电感器在高频下工作良好。

图 1 RFSoC 接收器仿真电路图

图 1 RFSoC 接收器仿真电路图串联电阻器 R7 和 R8 提供较小的串联电阻,来保持放大器的稳定运行。电容器 C5 和 C6 是直流阻断电容器;应根据工作频率来选择这些电容器的值。元件 C1 和 C2 以及 L3 和 L4 表示匹配电路。除了匹配外,L3 和 L4 与 C1的组合提供了一个 L-C 低通抗混叠滤波器,来衰减放大器输出的宽带噪声或杂散。互连的布线长度表示连接 0201 尺寸元件的最小长度,同时保持贴片制造所需的足够禁止间距。

图 1-2 展示了每个仿真的物理布局表示。

图 2 RFSoC 接收器布局界面

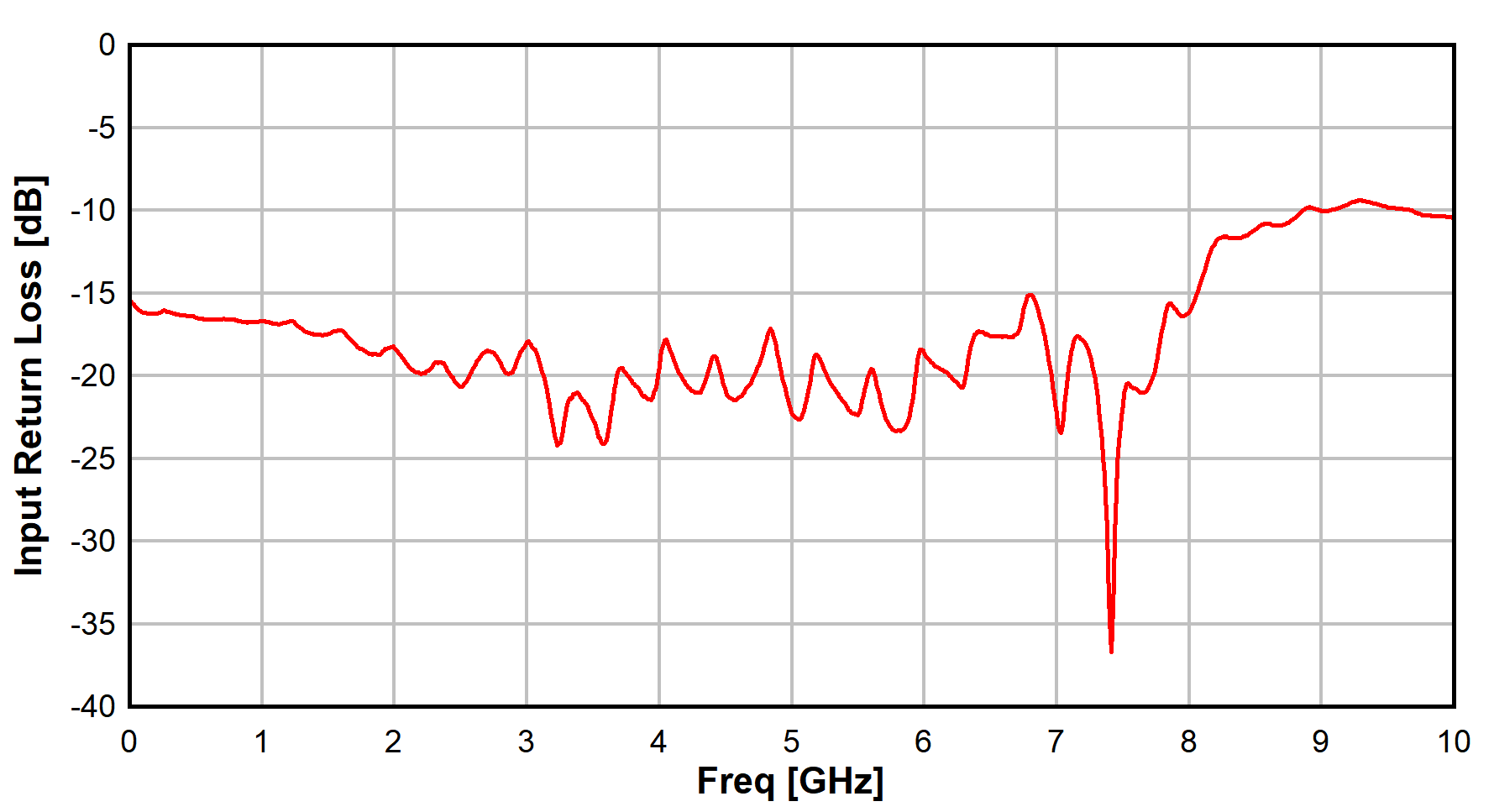

图 2 RFSoC 接收器布局界面该仿真的目的是实现良好的宽带回波损耗性能,尤其要注意高达 7GHz 频带的性能,其中器件(和电路板)的寄生效应开始明显影响并降低整体性能。该仿真会从 1GHz 扫描到 10GHz,这是 RFSoC S 参数文件中提供的频率限制。低频时,性能良好;在这些频带中,无需特定的匹配元件。这些器件可以简单地与适当的交流耦合电容器和抗混叠滤波器级联在一起。在 7GHz 左右的更高频率下,匹配元件会提高性能。图 1-3 展示了采用仿真原理图中匹配拓扑和值时仿真的回波损耗性能。

图 3 复合 RX 回波损耗性能

图 3 复合 RX 回波损耗性能复合回波损耗性能在 8GHz 以下范围内大多优于 –15dB,而在 10GHz 以下范围内则优于 –10dB。

RFSoC 发送器

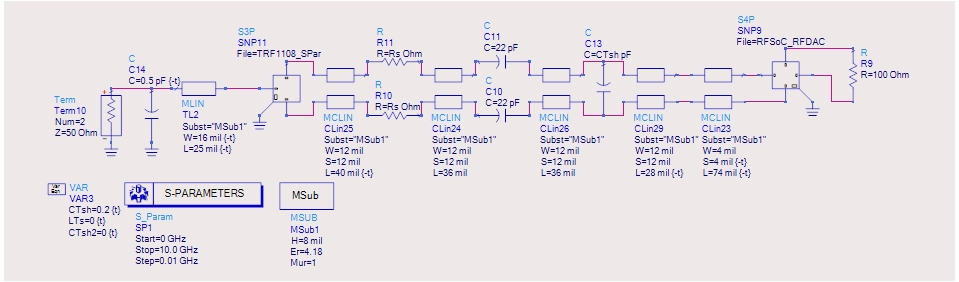

对发送器的类似分析使用 Xilinx RFSoC 和 TRF1108 发送器有源平衡-非平衡变压器的 RF-DAC S 参数。对于发送侧,DAC 和放大器之间不存在滤波问题。此设计在发送线路的更下方包含适当的滤波。DAC 的输出差分阻抗本身就很好,TRF1108 放大器的差分输入也是如此。这两者之间对匹配电路的需求极低。相应地,与 RX 情况相比,可以省去一些元件,从而简化输出拓扑。接口电路将一个小型分流电容器保持在靠近 DAC 器件引脚、一个串联耦合电容器和一个串联电阻器的位置。TRF1108 的单端输出阻抗在较高频率下会偏离 50Ω。此设计主要在 7GHz 以下范围内工作。输出端口与分流电容匹配,以改善该频率下的回波损耗。图 1-4 展示了发送器电路拓扑,而图 1-5 展示了 RF-DAC 和差分放大器输入之间的物理布局。

图 4 RFSoC 发送器仿真电路图

图 4 RFSoC 发送器仿真电路图 图 5 RFSoC 发送器布局界面

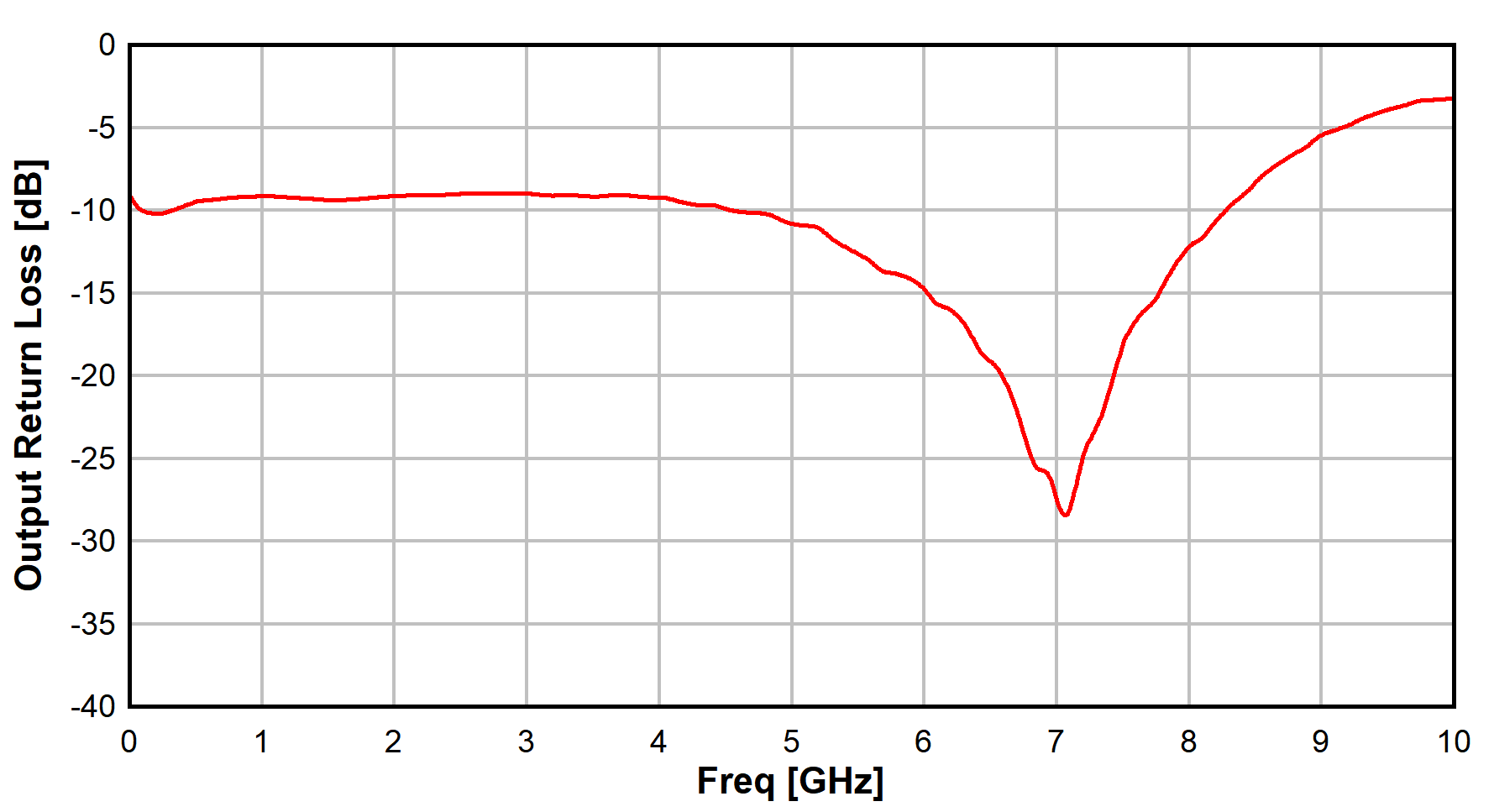

图 5 RFSoC 发送器布局界面与接收器情况类似,仿真频率从 1GHz 扫描到 10GHz。图 1-6 展示了输出回波损耗。回波损耗主要由放大器的 S22 性能决定。借助匹配元件,5GHz 至 8GHz 范围内的输出回波损耗优于 10dB,并在 7GHz 频率下更出色。调整输出电容器会略微改变优化点。由于输入和输出之间存在放大器隔离,RF-DAC 和放大器输入之间的匹配修改不会显著影响输出回波损耗。也就是说,放大器用作一个良好的缓冲器件。图 1-6 展示了在放大器匹配位置时的回波损耗性能。

图 6 复合 TX 回波损耗性能

图 6 复合 TX 回波损耗性能结论

每个器件本身都具有良好的宽带阻抗性能。正如预期的那样,由于设计和封装中存在内部寄生元件,较高频率下会出现性能下降。通过进行适当匹配,可以在更高的目标频率下提高性能。

每种设计都是不同的。本报告中的仿真旨在用作指南。每种布局都具有不同的 PCB 堆叠配置,这会影响布线宽度以保持所需的特性阻抗。设计中可能存在其他决定布线长度的因素。可以针对任何特定配置使用和修改电路拓扑,以获得近似值。此拓扑为适当匹配的元件提供了占位符,在考虑 PCB 板中不可预测变化或模型内不准确情况下的实际电路板测量值后,可以进行细微调整。