# EVM User's Guide: SK-AM64 SK-AM64B

## AM64x SK 评估模块 (EVM)

### 说明

AM64B 入门套件 (SK) 是一个基于 Sitara™ AM6442 处理器的低成本独立测试和开发平台，非常适合用于加速下一个设计的原型设计阶段。该套件包括有线 ( 以太网 ) 和无线 ( 2.4GHz 和 5GHz ) 连接、三个扩展头、多个引导选项和灵活的调试功能。

### 特性

- 软件 : TI 处理器 SDK Linux®/ RT Linux 内核、Yocto 文件系统、开箱即用演示，含 Wi-Fi™

- 处理 : AM64x , 含 2 个 Arm® Cortex®-A53、4 个 Arm Cortex-R5 和 2 个 TI PRU\_ICSSG

- 网络 : Wi-Fi ( 双频带 ) 、蓝牙®/低功耗蓝牙 5.1 ; 2 个 RJ-45 以太网 1000/100Mbps

- 连接 : 可通过 micro-USB 连接 1 个 Type A USB 3.1 gen1 ( 超高速 ) 、板载 XDS110 JTAG 仿真器和 3 个 UART

- 扩展和原型设计 : 40 引脚 Raspberry Pi (RPI4) HAT、PRU-ICSSG 实时 I/O 和 TI-MCU 头

- 存储 : 2GB LPDDR4

- SK 上的可引导接口 : 可拆卸 uSD、USB、16MB OSPI、以太网、通用异步接收器/发送器 (UART)

此设计采用了 HDMI® 技术。

## 1 评估模块概述

### 1.1 简介

本评估模块用户指南介绍了 AM64x SKEVM 的硬件架构。AM64x 处理器包含一个双核 64 位 Arm® Cortex®-A53 微处理器、2 个双核 Arm Cortex-R5F MCU 和一个 Arm Cortex-M4F MCU。

AM64x 入门套件是一个独立测试和开发平台，非常适合用于加速下一个设计的原型设计阶段。该套件包括：有线和无线连接、三个扩展头、多个引导选项和灵活的调试功能。

此入门套件还配有 TI 的 AM64x 处理器和优化的功能集，允许用户使用基于以太网的接口、USB 接口、有线串行接口以及 2.4GHz 和 5GHz 无线通信制造商业和工业器件。两个板载 1Gbps 以太网端口用于有线连接，此外还有三个扩展头 ( PRU、MCU、User ) 用于扩展电路板功能。此入门套件采用标准串行协议 ( 如 UART、I2C 和 SPI )，可用作通信网关与多个其他器件进行连接。该入门套件从标准 USB-C 端口接收 5V 电源，支持用户访问 AM64x 的 R5F 内核，使器件非常适合用作可编程逻辑控制器 (PLC) 或电机控制器，可实时处理传感器输入并管理外设，同时在 A53 内核上运行 Linux，并使器件作为远程工业通信网络中的中央引擎。嵌入式仿真逻辑允许使用标准开发工具 ( 例如 TI 的 Code Composer Studio™ ) 进行仿真和调试。

#### 备注

此评估板是预量产版本，具有若干已知问题，这些问题不得带入生产系统。相关详细信息，请参阅 [节 5.1](#)。

在定制电路板设计过程中，客户倾向于重复使用 SK 设计文件，并在此基础上进行设计调整。此外，客户也会重复使用一些常见实现方式，包括 SOC、存储器以及通信接口等。鉴于 SK 被寄予实现更多附加功能的厚望，客户会对 SK 实现进行优化调整，以满足自身电路板设计的要求。在对 SK 原理图进行优化时，会在定制设计中引入误差，这类误差可能导致功能、性能或可靠性方面的问题。优化过程中，如客户对 SK 实施存在疑惑，可能会导致设计错误。许多这类优化和设计错误在各种设计中很常见。根据以往的经验教训和数据表中的引脚连接建议，我们在 SK 原理图的各部分附近添加了全面的设计要点 (D-Note:)、审核提示 (R-Note:) 和 Cad 注解 (Cad Note:)，客户可以查看并遵循这些说明，以便更大限度减少设计中的错误。此外，设计文件下载包中还包含了一系列附加文件，以便更好地辅助客户的评估工作。

### 1.2 套件内容

#### AM64B SKEVM 的主要特性如下：

- 包括 AM64x SoC、存储器、引导接口、板载 JTAG 和电源电路。

- 为硬件附加电路板提供通用扩展接口。

- 在独立模式下运行，无需任何子卡。

- 通过 USB Type-C 连接器供电。

- 通过千兆位以太网端口 (2 个) 和 USB 3.0 Type-A 接口 (1 个) 进行外部通信。

- 端接在 Type-A USB 主机连接器上的 USB3.0 高速接口。

- 支持 Wi-Fi 和蓝牙的 Wi-Link WL1837 模块。

- 可选择提供子卡所需的电源 ( 在 3V3 上限制为 500mA，在 5V 电源轨上限制为 155mA )。

#### AM64x 片上系统 (SoC) :

- AM64x 将两个支持 TSN 技术的 Sitara 千兆位 PRU-ICSSG 实例与最多两个 Arm Cortex-A53 内核、最多四个 Cortex-R5F MCU 和一个 Cortex-M4F MCU 合并到一起。SoC 焊接到不带插座的 PCB 上。

#### 存储器

- 2GB DDR4，支持高达 1600MT/s 的数据速率

- Micro 安全数字 (SD) 卡，提供 UHS-1 支持

- 512Mb OSPI EEPROM

- 512Kb 内部集成电路 (I2C) 板 ID EEPROM

#### 高速接口：

- 两个 CPSW 千兆位以太网 (RGMII) 端口，可与德州仪器 (TI) 千兆位以太网 PHY 连接

- 一个 USB3.0 主机接口，端接 USB Type-A 连接器，用于数据传输

#### 扩展总线：

- 3 个扩展连接器，使用 0.1" 间隔 0.025" 方形柱连接器

- 1 个与 Raspberry Pi 兼容的 40 引脚扩展连接器，可无缝集成 HAT 板

- 1 个 PRU 54 引脚连接器，可连接 PRG0 接口

- 1 个 MCU 28 引脚连接器

#### 调试：

- XDS110 板载仿真器

- 支持外部仿真器的 20 引脚 JTAG 连接

- 自动在板载和外部仿真器（优先级较高）之间进行选择

- 通过 CP2105 提供的 Micro-B USB 连接器连接双端口通用异步接收器/发送器 (UART) 与 USB 电路

- 2 个 8 位 DIP 开关，供用户选择 SoC 引导模式

- 1 个用于中断 SoC GPIO 的按钮

- LED。1 个用于主电源，1 个用于指示 PMIC 良好，1 个用于 MCU 域，1 个用于 MCU 域 GPIO，另外的连接到两个工业接口

#### 电源：

- SK-AM64B EVM 通过 USB Type-C 连接器供电。

- LM61460AASQRJRRQ1 稳压器将 5V 降压至 3V3。VCC3V3SYS\_EXT 是 PMIC 的输入电源。

- 入门套件上的 TPS6522053RHBR PMIC 和其他分立式稳压器为 SoC 和其他外设（LPDDR4、Wi-Fi 模块和 OSPI、时钟缓冲器、电平转换器和逻辑门）提供所有必要的电源。

- 还提供专用稳压器，用于：

- 为测试自动化接头部分的常开电路供电

- SoC 的 E-Fuse 编程。

- XDS110 调试器部分。

- 用于 SoC 和外设的 3V3。

- 用于以太网 PHY 的 1V0。

- 推荐的电源：**

- CUI Inc. 5V 15W 交流/直流外部壁式安装适配器 - SWC15-S5-NB

- GlobalTek Inc. 5V 15W 交流/直流外部壁式安装适配器 - WR9QA3000USBC3MNA-CIMR6B

- Qualtek USB 2.0 线缆 C 公头转 C 公头 3.28' 屏蔽电缆，通过笔记本电脑 Type-C 端口为电路板供电 - 3021091-01M

- 状态输出：用于指示电源状态的 LED

#### 合规性：

- 符合 RoHS 标准

- 符合 REACH 标准

### 1.3 器件信息

SK-AM64B 评估模块 (EVM) 是一个开发平台，旨在展示 Sitara AM64x 处理器的功能。该处理器包含一个双核 64 位 Arm® Cortex®-A53 微处理器、2 个双核 Arm Cortex-R5F MCU 和一个 Arm Cortex-M4F MCU。

该 EVM 集成了内核 AM64x SoC 和关键辅助电路，包括用于实现高性能运行的 MT53E1G16D1FW-046 WT LPDDR4 存储器。EVM 通过 USB C 型连接器和 TPS6522053RHBR 电源管理 IC 供电以实现稳定的电压调节，并配备 DP83867IRRGZ 以太网 PHY 收发器以提供以太网接口。为扩展和原型设计提供了 TI-MCU 接头、40 引脚 Raspberry Pi™ HAT 接头、PRU-ICSSG 实时 I/O。提供 A 型 USB 3.0、千兆位以太网等标准接口用于外设扩展和系统连接。开发人员借助这种集成式设计可以立即为工业自动化、网络通信及其他嵌入式应用场景开发应用程序原型。

嵌入式仿真逻辑允许使用标准开发工具（例如 Code Composer Studio 集成式开发环境 (IDE) (CCSTUDIO)）进行仿真和调试。

## 2 硬件

### 2.1 EVM 版本和组件型号

各种 AM64 SK EVM PCB 设计版本以及组件型号在表 2-1 中列出。具体 PCB 版本如 PCB 上的丝印所示。具体组件型号在另外的贴纸标签中显示。表 2-2 列出了电路板已知问题。

**表 2-1. AM64 SK EVM PCB 设计版本和组件型号**

| PCB 版本    | 版本和组件型号描述                                                                            |

|-----------|--------------------------------------------------------------------------------------|

| PROC100E1 | 第一款原型，AM64 SK EVM 的提前发布版本。使用了蓝色阻焊层。实现 Sitara™ AM6442 MPU。                            |

| PROC100E2 | AM64 SK EVM 的首个正式版本。使用了白色阻焊层。实现 Sitara AM6442 MPU。                                   |

| PROC100E3 | SK-AM64 EVM 的量产版本。使用了红色阻焊层。采用两个 PMIC 电源解决方案实现 Sitara AM64x MPU。                      |

| PROC100E4 | SK-AM64 EVM 的原型修订版本。使用了绿色阻焊层。采用单个 PMIC 电源解决方案实现 Sitara AM64x MPU                     |

| PROC100A  | SK-AM64B EVM 的量产版本。使用了红色阻焊层。采用单个 PMIC 电源解决方案实现高安全性-现场安全 (HS-FS) 芯片 Sitara AM64x MPU。 |

**表 2-2. 已知问题汇总**

| ID | 严重程度 | 总结                      | 受影响的硬件版本    | 修复    |

|----|------|-------------------------|-------------|-------|

| 1  | 高电平  | 电源解决方案未满足 AM64x 电源要求    | E1、E2、E3    | E4    |

| 2  | 高电平  | 不满足 AM64x 电压规格          | E1、E2、E3    | E4    |

| 3  | INFO | 请勿将 MMC0 用于 SDIO 器件     | E1、E2       | E3    |

| 4  | 中    | 在压力基准条件下的 LPDDR4 数据速率限制 | E1、E2       | E3    |

| 5  | INFO | UART 控制台上的垃圾字符          | E3          | E3A   |

| 6  | 中    | 测试断电信号悬空                | E4          | 修订版 A |

| 7  | 高电平  | uSD 引导无法正常工作            | E1、E2、E3、E4 | 修订版 A |

## 2.2 重要使用说明

请在使用 **AM64x** 入门套件之前通读本节内容。这些说明的作用是尽可能减少您在评估时遇到的问题。如果您有任何问题，请在 **E2E** 上创建新问题并请求解答。

根据本文档后文“配置”部分中介绍的引导模式，验证您要使用的引导介质。

**AM64x** 入门套件应通过 **USB-C** 端口供电（不支持数据或显示交替模式）/

**AM64x** 入门套件上的 **USB-C** 电源控制器需要电力输送源的协商序列，并且需要一个能够提供 **5V/3A** 电流的电源。如果电力输送源无法满足这些要求，**AM64x** 入门套件底部的红色 **LED** 会亮起。

旧版低成本市电电压 **5VDC USB Type-A** 砖型产品主要用于为消费类电子产品供电或充电，无法正常完成 **AM64x** 入门套件中 **USB-C** 电源控制器的协商序列，而且会使 **EVM** 无法上电。“加电/断电过程”一节介绍了推荐电源的指导原则。

**注意** **AM64x** 入门套件不能通过 **40** 引脚“用户扩展连接器”上的 **5V0** 或 **3V3** 引脚供电。**AM64x** 入门套件的设计不支持通过扩展头供电。

**注意** **AM64x** 入门套件的扩展头没有失效防护。这就意味着 **AM64x** 入门套件断电时，扩展板不能驱动任何 **I/O** 引脚。这样会违反 **AM64x** 数据表规范，并可能会导致处理器或板上的其他元件损坏，而且这不在保修范围内。

**40** 引脚“用户扩展连接器”旨在匹配信号类型和 **RPI4 40** 引脚连接器上的硬件接口，因此支持大部分由社区开发的硬件级附加电路板。由于每个 **SoC** 供应商对引脚功能复用的决策不同，一些更深入的备用引脚功能可能与 **RPI4** 上的接口不匹配。

**注意**：关于 **HAT** 与 **40** 引脚“用户扩展连接器”的兼容性：在将 **HAT** 连接到 **AM64x** 入门套件之前，请始终检查您的 **HAT** 所需的硬件资源，以及有效引脚功能。引脚多路复用设置可能需要首先更改引导加载程序。

**注意**：易受 **ESD** 影响

静电放电 (ESD) 会损坏设备并损害电路。电子印制电路卡处理不当会产生 ESD，并可能导致完全或间歇性故障。

入门套件评估板包含对 ESD 敏感的电子器件。因此，处理这些板时必须小心谨慎。**SK EVM** 必须在受控的实验室环境下使用，测试工程师和开发人员应调整所有 ESD 安全预防措施。

有关预防措施，请参阅以下内容：

- 确保用户在受 ESD 保护的实验室环境中使用设备。

- 处理产品的人员必须接受过电子培训并遵守良好的工程实践标准。

- 穿戴防 ESD 外套、防 ESD 拖鞋或腕带，确保装备与皮肤接触良好。

- 仅通过元件的手柄或边缘处理元件；切勿触摸印刷电路板或连接器。

- 避免印刷电路板与衣物接触。腕带仅保护元件免受人体 ESD 电压的影响；衣物上的 ESD 电压仍会造成损坏，因此请穿上防 ESD 外套。

## 2.3 系统说明

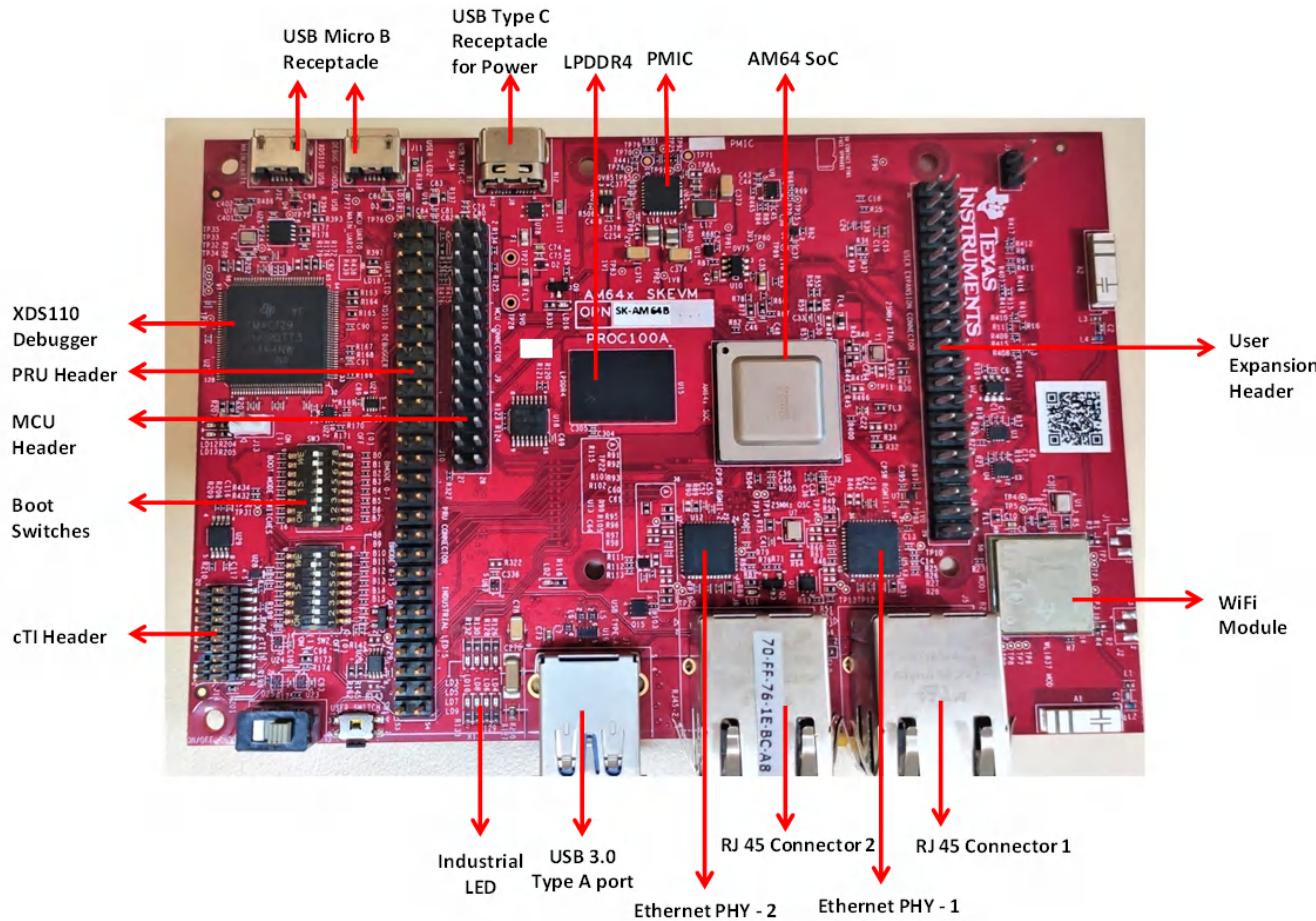

图 2-1. 入门套件处理器板的顶视图

注意：两个 USB Micro-B 插座

J12 : XDS110 USB 转 MAIN UART1

J11 : 调试控制台 ( MCU UART0 和 MAIN UART1 )

图 2-2. 入门套件处理器板的底视图

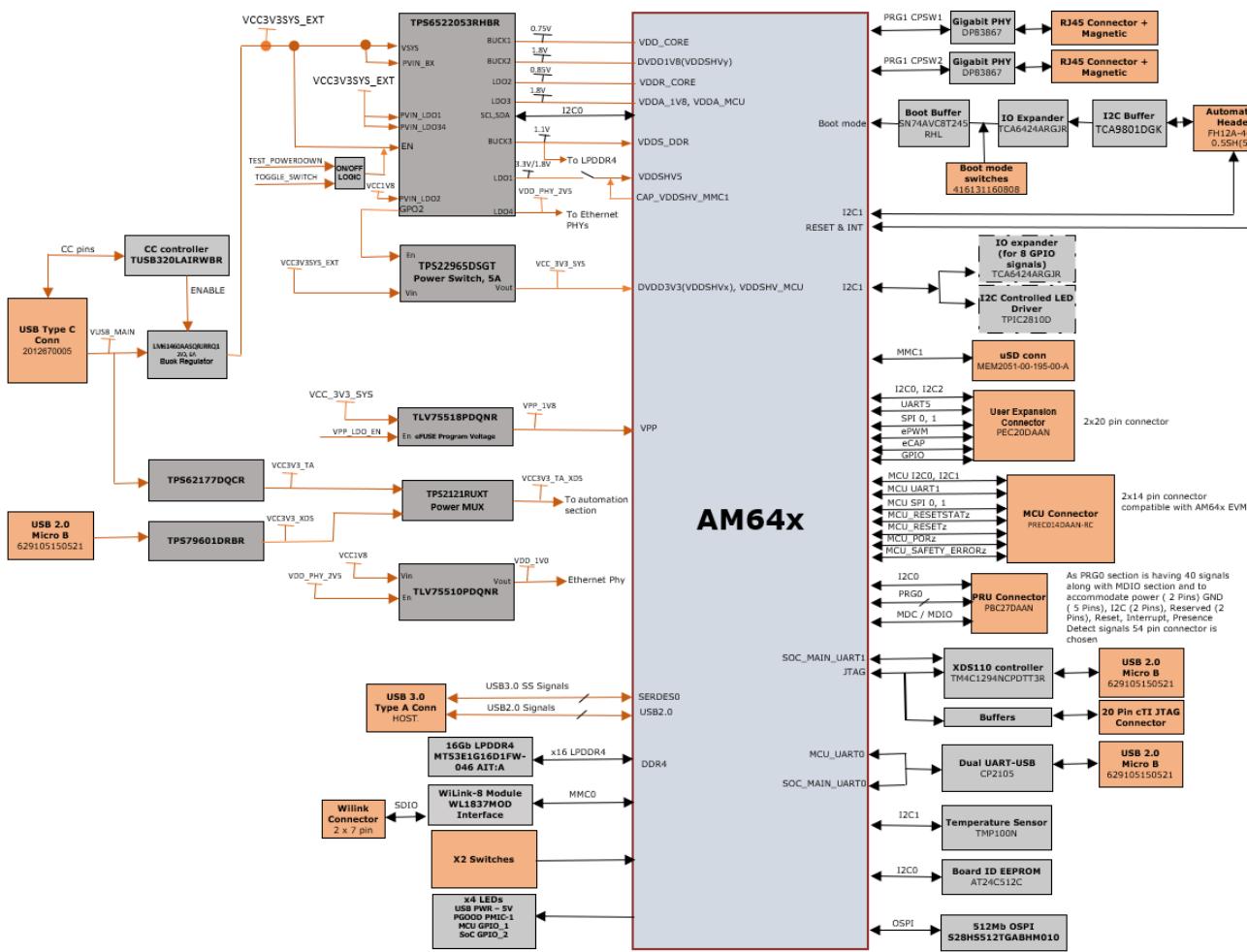

### 2.3.1 功能方框图

图 2-3 展示了 AM64x SK EVM 的功能方框图。

图 2-3. 入门套件处理器板功能方框图

## 2.3.2 加电/断电过程

EVM 的电源是通过外部交流/直流转换器提供的，为 USB Type-C 端口提供 5V、3A (最大值) 直流电压。

### 2.3.2.1 加电过程

#### 备注

Processor SDK Linux 图像默认提供交互式用户演示。引导后，电路板将作为无线接入点，SSID 为 **AM64xSK-AP**，密码为 **tiwilink8**。连接后，导航到 <http://192.168.43.1:8081> 可找到演示。位于产品页的“软件快速入门指南”中提供了更多详情。

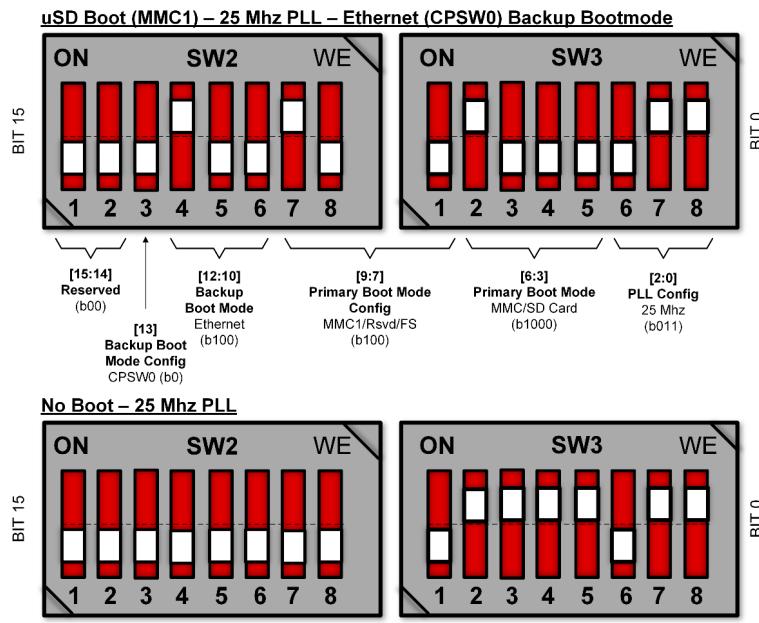

1. 将 SK EVM 引导开关选择器 (SW2、SW3) 置于所选的引导模式下。SD 卡引导模式和不引导的示例如下所示。其他选项请参阅节 2.3.3.4.1。

图 2-4. 通用引导模式开关位置

2. 连接引导介质 (如果适用)。

3. 将 5 V USB Type-C 电缆连接到 SK EVM Type-C (J8) 连接器。

4. 将 Type-C 电缆的另一端连接到电源：交流电源适配器或 Type C 源设备 (例如笔记本计算机)。

5. 使用 ON/OFF 滑动开关 SW5 给电路板上电。

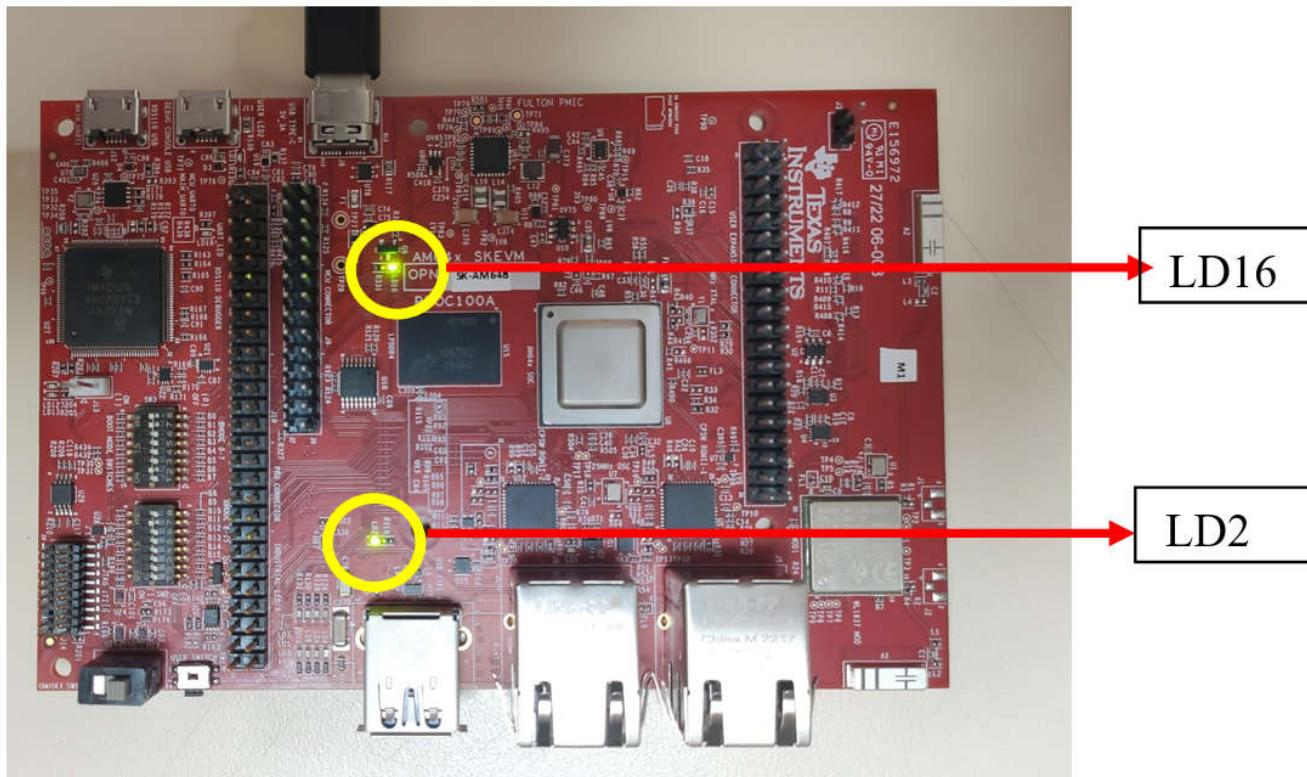

6. 根据以下参考照片检查 LED 显示情况。以下 LED 亮起：LD2 和 LD16 位于电路板顶部。

图 2-5. 顶部 LED

7. XDS110 JTAG 和 UART 调试控制台输出分别路由到 Micro USB 端口 J12 和 J11。

**备注**

Linux 控制台输出路由到第二个枚举的 ttyUSB 端口。

### 2.3.2.2 断电过程

1. 使用 ON/OFF 滑动开关 SW5 关闭电路板电源。

2. 从交流/直流转换器断开交流电源。

3. 从 EVM 移除 USB Type-C 电缆。

### 2.3.3 外设和主要元件描述

以下各节概述了 AM64x SK EVM 上的不同接口和电路。

### 2.3.3.1 计时

#### 2.3.3.1.1 以太网 PHY 时钟

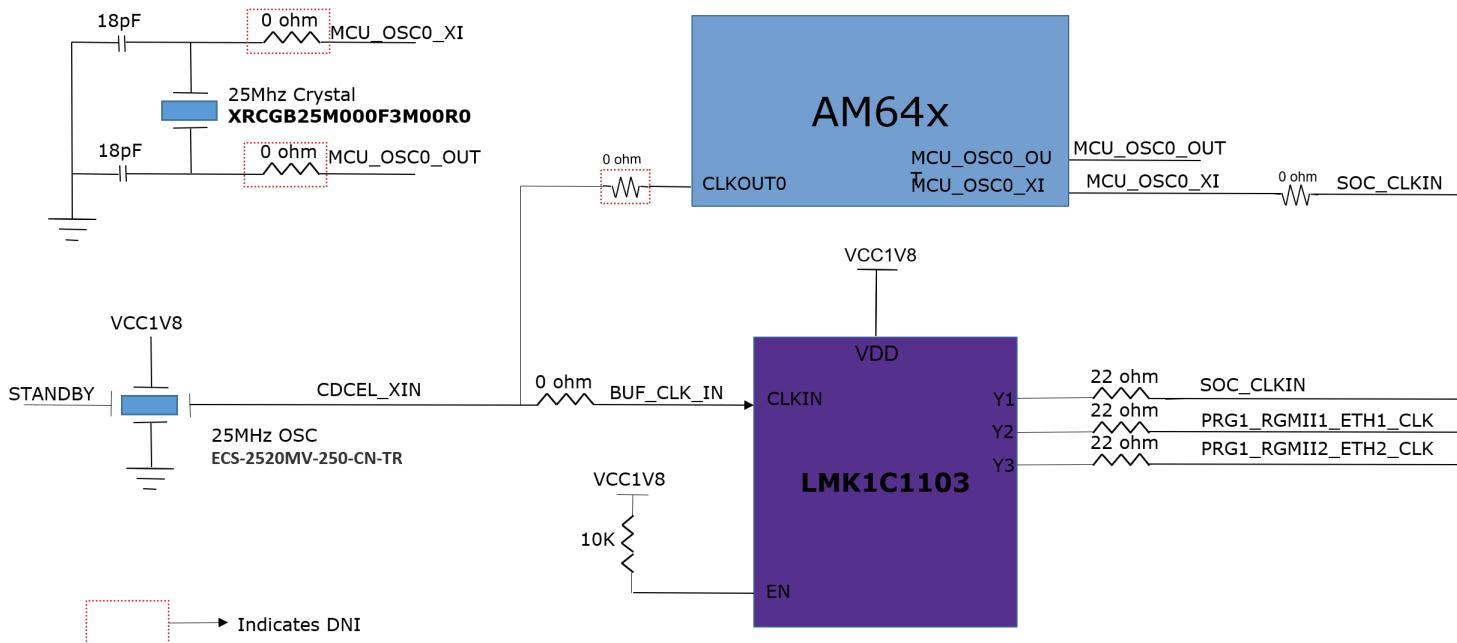

器件型号为 **LMK1C1103PWR** 的时钟缓冲器用于驱动以太网 PHY 的 25 MHz 时钟。LMK1C1103PWR 是 1:3 LVC MOS 时钟缓冲器，根据 25 MHz 晶振/LVC MOS 参考输入提供四个 25 MHz LVC MOS 时钟输出。时钟缓冲器的源是 SoC 的 CLKOUT0 引脚或一个 25MHz 振荡器 (**ECS-2520MV-250-CN-TR**)。可以使用一组电阻进行选择。默认情况下，振荡器用作 SK-AM64B EVM 中时钟缓冲器的输入。时钟缓冲器 LMK1C1103PWR 的输出 Y2 和 Y3 用作 SKEVM 中两个千兆位以太网 PHY 的参考时钟输入。

图 2-6. AM64x SK EVM 时钟树

#### 备注

红色框中的电阻器是 DNI。

#### 2.3.3.1.2 AM64x SoC 时钟

时钟缓冲器 LMK1C1103PWR 的输出 Y0 用作 SKEVM 上的 SoC 的参考时钟。还提供可选的 25MHz 晶振 (XRCGB25M000F3M00R0) 用于驱动 SoC。使用电阻器为 SoC 选择时钟。默认情况下为 SoC 提供 SoC\_CLKIN 时钟缓冲器的输出。有关时钟源的选择，请参阅表 2-3。

表 2-3. SoC 时钟源

| SoC 时钟源   | 器件型号               | 安装      | 拆除      |

|-----------|--------------------|---------|---------|

| 时钟缓冲器     | LMK1C1103PWR       | R116    | R40、R41 |

| 25 MHz 晶振 | XRCGB25M000F3M00R0 | R40、R41 | R116    |

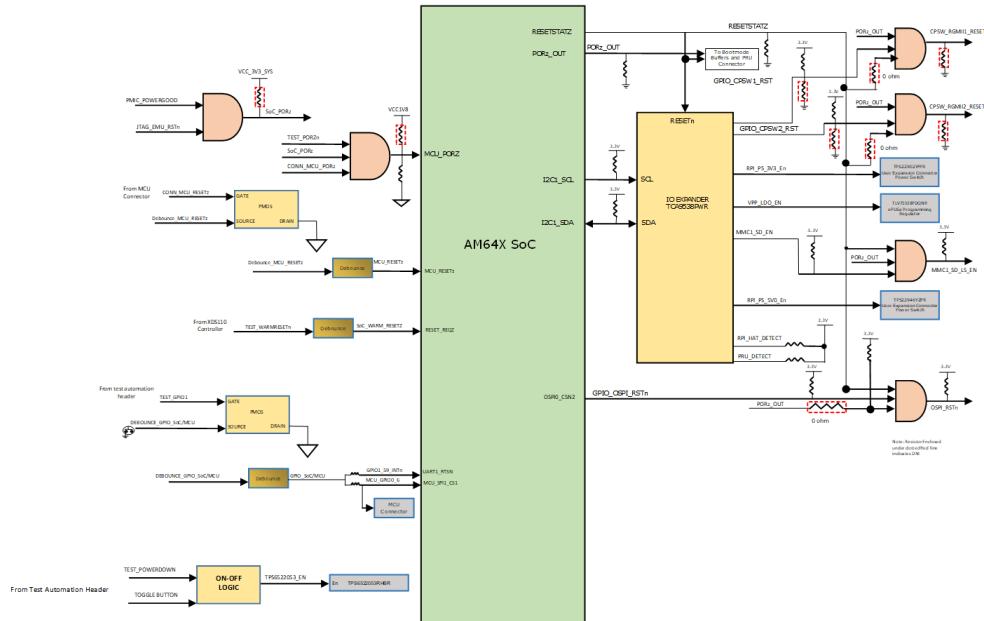

### 2.3.3.2 复位

AM64x SoC 可进行以下复位：

- RESETSTAT<sub>z</sub> 是 MAIN 域的热复位状态输出。

- POR<sub>z</sub>\_OUT 是 MAIN 域和 MCU 域的加电复位状态。

- MCU\_POR<sub>z</sub> 是 MCU 域和 MAIN 域的上电/冷复位输入。

- MCU\_RESET<sub>z</sub> 是 MCU 域的热复位输入。

- `MCU_RESETSTATz` 是 MCU 域的热复位状态输出。

SoC\_PORz 信号通过对 PMIC 的 PGOOD 信号和 JTAG 仿真器复位进行与操作来提供。MCU\_PORz 通过对 MCU 连接器的 CONN MCU PORz、测试自动化连接器的 TEST PORZn 以及 SoC PORz 进行与操作来提供。

SoC 的 MCU 域热复位 (MCU\_RESETz) 和 MCU 域冷复位 (MCU\_PORz) 分别由安全连接器的 CONN\_MCU\_RESETz 和 CONN\_MCU\_PORz 实现。

加电复位后，连接到 **MAIN** 域的所有外设均通过 **RESETSTATZ** 以及 **GPIO** 控件实现复位，如图 2-7 中所示。

图 2-7. AM64x SK EVM 的整体复位架构

### 2.3.3.3 电源

### 2.3.3.3.1 电源输入

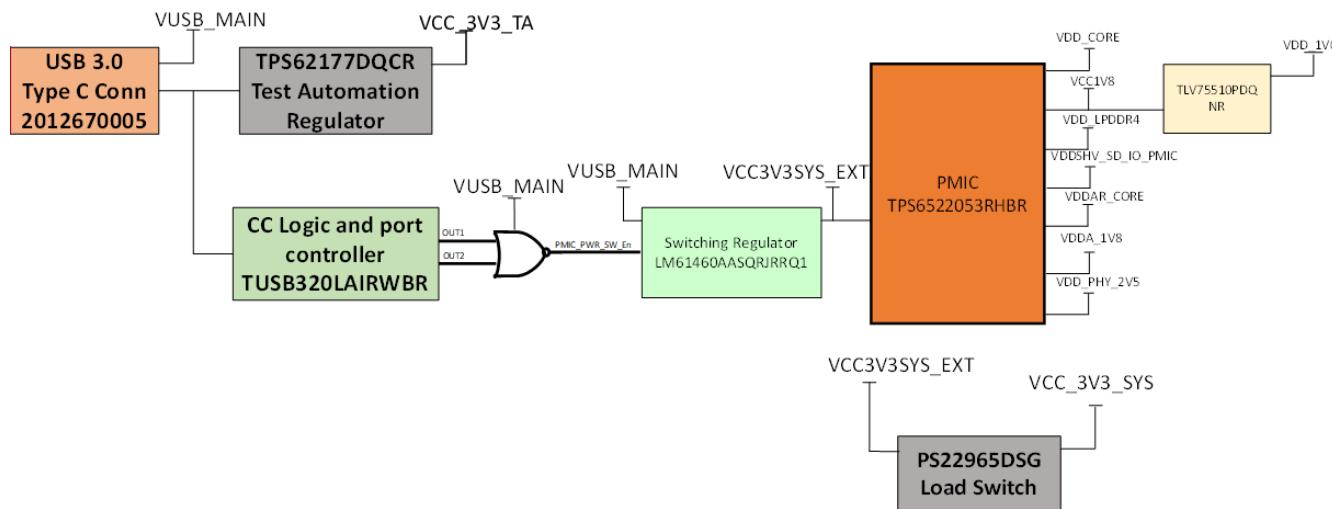

AM64x SK EVM 接收来自 USB Type-C 连接器的 5V 输入。以下各节介绍了为 SK EVM 板供电的配电网络拓扑，可支持元件和参考电压。

SK-AM64B EVM 板包含基于 PMIC 和若干分立式稳压器的电源解决方案。电源的初始级是来自 Type-C USB 连接器（器件型号 2012670005，由 Molex 提供）的 5V，支持 3A 电流额定值以及必要的过流和电压浪涌保护电路。来自 USB 连接器的 5V 输入 (V<sub>USB\_MAIN</sub>) 用于借助开关稳压器（器件型号 LM61460AASQRJRRQ1）生成 3.3V (V<sub>CC3V3SYS\_EXT</sub>)，这是 PMIC 部分的输入电源。PMIC 生成 SKEVM 所需的电压。

提供 **ON/OFF** 切换开关（器件型号为 **AS11AP**），用于初始化电路板的上电和断电序列。当开关处于 **OFF** 位置时，该开关将 **TPS6522053\_EN** 使能信号接地，当开关处于 **ON** 位置时启用 **PMIC TPS6522053RHBR**，从而启动上电序列。将开关滑至 **OFF** 位置时，**TPS6522053RHBR PMIC** 使能引脚处于低电平，此时将启动断电序列。

此外，来自测试自动化接头的 TEST\_POWERDOWN 也会连接到 TPS6522053RHBR PMIC 的使能引脚，通过测试自动化板控制 EVM 的开/关。测试自动化连接器需要 3.3V 电源，由电源多路复用器（器件型号：TPS2121RUXT）提供。电源多路复用器的输入为 3V3，来自两个不同的电源。首先，使用 LDO（器件型号：TPS79601DRBR）从 5V (XDS\_USB\_VBUS) 生成 3V3 电源。只要 Micro B 电缆连接到 J12，就会生成该电源。其次，使用开关降压稳压器（器件型号：TPS62177DQCR）从 5V (VUSB\_MAIN) 生成 3V3 输入。这是一个常开稳压器，只要插入 USB Type C 电缆，就可提供必要的电源。当 J12 上的 Type C 电缆和 Micro B 电缆均连接时，多路复用器优先级设置为第一个输入电源 (VCC3V3\_XDS)。如果 USB 未连接到 J12，则多路复用器输出来自 VCC3V3\_TA，这是一个常开电源。

### 2.3.3.3.2 用于电源输入的 USB Type-C 接口

AM64x SKEVM 是通过 USB Type-C 连接器供电的。USB Type-C 电源能够在 5V 时提供 3A 电流，而且能通过 CC1 和 CC2 信号广播拉电流能力。在 SK EVM 上，USB Type-C 连接器上的 CC1 和 CC2 与 TUSB320LAIRWBR 端口控制器 IC 相连。此器件使用 CC 引脚来确定端口连接和分离、电缆方向、角色检测以及对 Type-C 电流模式的端口控制。Type-C 电缆翻转插入时，此 IC 支持引脚交换。CC 逻辑块通过监视 CC1 和 CC2 引脚上的上拉或下拉电阻来确定 USB 端口的连接时间、电缆的方向以及检测到的角色。CC 逻辑根据检测到的角色来确定 Type-C 电流模式为默认、中等还是高。引脚 PORT 通过电阻下拉接地，可将其配置为 UFP ( 面向上游的端口 ) 模式。在 UFP 模式下，通过实施 VBUS 检测来确定是否连接成功。引脚 ADDR 保持开路，可配置为 GPIO 模式。OUT1 和 OUT2 引脚连接到或非门。OUT1 和 OUT2 引脚上均为低电平有效，可广播已连接状态的高电流 (3A)，使 VUSB\_MAIN 电源开关提供 VUSB\_PMIC，从而为一个 PMIC 供电。在 UFP 模式下，TUSB320 器件在两个 CC 引脚上始终应用下拉电阻 (Rd)。TUSB320 器件监控 CC 引脚电压电平，该电压电平与由所连接 DFP 通告的 Type-C 模式电流相符。TUSB320 器件可去除 CC 引脚的抖动，等待 VBUS 检测，直到成功连接。TUSB320 器件作为 UFP，可检测由 DFP 通告的电流电平，并通过 OUT1 和 OUT2 GPIO 与系统进行通信。SKEVM 电源要求是在 3A 时提供 5V。如果电源不能在 3A 时提供 5V，或非门的输出会变为高电平，从而禁用 VUSB\_Main 电源开关。因此所有电源均保持关断状态，VCC3V3\_TA 除外。只有电源能够在 3 A 时提供 5 V 电压，此电路板才能完全通电。

图 2-8. 用于电源输入的 USB Type-C 接口

表 2-4. USB Type C 电缆的拉电流能力和状态

| OUT1 | OUT2 | 广播                |

|------|------|-------------------|

| 高电平  | 高电平  | 未连接状态下的默认电流       |

| 高电平  | 低电平  | 连接状态下的默认电流        |

| 低电平  | 高电平  | 连接状态下的中等电流 (1.5A) |

| 低电平  | 低电平  | 连接状态下的高电流 (3.0A)  |

### 2.3.3.3.3 电源故障指示

红色 LED LD15 用于通过使用 USB Type C 配置通道逻辑和端口控制器 IC 来指示电源故障情况（例如，电流小于 3A）。

**表 2-5. 电源故障指示 LED**

| LED  | 亮起状态          | 熄灭状态           |

|------|---------------|----------------|

| LD15 | 电源提供的功率小于 15W | 电源提供所需的 15W 功率 |

### 2.3.3.3.4 电源

SK-AM64B EVM 板利用一个 PMIC 和三个分立式稳压器为 SoC、各种存储器、Wi-Link 模块和板上的其他外设提供必要的电压和功率。SKEVM 板上提供的电源的探测点在表 2-6 中介绍。

**表 2-6. 电源测试点**

| Sl.No | 电源                    | 探测点    | 接地   | 探测点  | 预期电压 (V) |

|-------|-----------------------|--------|------|------|----------|

| 顶部点   |                       |        |      |      |          |

| 1     | VUSB_MAIN             | TP28   | DGND | J3.2 | 5        |

| 2     | XDS_USB_VBUS          | TP75   | DGND | J3.2 | 5        |

| 3     | VCC_3V3_SYS           | TP80   | DGND | J3.2 | 3.3      |

| 4     | VDDAR_CORE            | TP85   | DGND | J3.2 | 0.85     |

| 5     | VPP_1V8               | TP89   | DGND | J3.2 | 0        |

| 6     | VDD_CORE              | TP81   | DGND | J3.2 | 0.75     |

| 7     | VDD_LPDDR4            | TP83   | DGND | J3.2 | 1.1      |

| 8     | VDD_1V0               | TP88   | DGND | J3.2 | 1        |

| 9     | VCC1V8                | TP82   | DGND | J3.2 | 1.8      |

| 10    | VDD_PHY_2V5           | TP87   | DGND | J3.2 | 2.5      |

| 11    | VDDSHV_SD_IO_PM<br>IC | TP84   | DGND | J3.2 | 3.3      |

| 12    | VDD_MMC1              | C47.1  | DGND | J3.2 | 3.3      |

| 13    | VBUS_USB_CP2105       | TP76   | DGND | J3.2 | 5        |

| 14    | VCC3V3_XDS            | TP74   | DGND | J3.2 | 3.3      |

| 15    | VDDSHV_SD_IO          | TP15   | DGND | J3.2 | 3.3      |

| 底部点   |                       |        |      |      |          |

| 16    | VCC3V3SYS_EXT         | TP78   | DGND | J3.2 | 3.3      |

| 17    | VDDA_1V8              | TP86   | DGND | J3.2 | 1.8      |

| 18    | VCC3V3_TA             | C340.1 | DGND | J3.2 | 3.3      |

| 19    | VCC3V3_TA_XDS         | C421.1 | DGND | J3.2 | 3.3      |

表 2-7 详细介绍了 SKEVM 板上提供的电源正常 LED，使用户能够确认每个电源的状态正常。图 2-7 突出显示了 SK EVM 板中的电源正常 LED。

表 2-7. 电源 LED

| SI.No | 电源                | LED 器件参考 |

|-------|-------------------|----------|

| 1     | VCC3V3SYS_EXT     | LD2      |

| 2     | VCC_3V3_SYS       | LD16     |

| 3     | VDDAR_CORE        | LD16     |

| 4     | VDDA_1V8          | LD16     |

| 5     | VDD_LPDDR4        | LD16     |

| 6     | VDD_CORE          | LD16     |

| 7     | VCC1V8            | LD16     |

| 8     | VDDSHV_SD_IO_PMIC | LD16     |

| 9     | VDD_PHY_2V5       | LD16     |

| 10    | VDDA_1V8          | LD16     |

| 11    | VDD_CP2105        | LD18     |

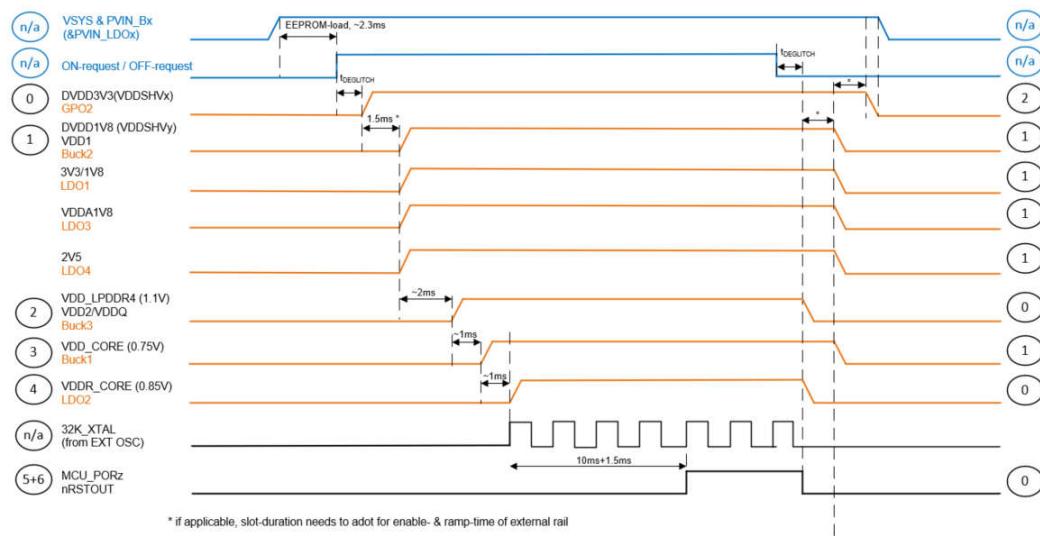

### 2.3.3.3.5 电源时序

图 2-9 展示了 SK EVM 板上所有电源的加电和断电序列。

图 2-9. 加电和断电时序控制

### 2.3.3.6 电源

AM64x SoC 的 SoC 核心电压 (VDD\_CORE) 设为 0.75V。将 SoC 阵列核心电压 (VDDR\_CORE) 和其他阵列核心电压 (VDDA\_0P85\_SERDES0\_C、VDDA\_0P85\_SERDES0、VDDA\_0P85\_USB0、VDD\_DLL\_MMCO 和 VDD\_MMCO) 配置为 0.85V，通过通用电源轨供电。

SoC 具有不同的 IO 组。每个 IO 组由特定电源供电，如表 2-8 所示。

表 2-8. SoC 电源

| SI.No | 电源                       | SoC 电源轨             | IO 电源组  | 电源   |

|-------|--------------------------|---------------------|---------|------|

| 1     | VDDAR_CORE               | VDDA_0P85_SERDES0   | SERDES0 | 0.85 |

|       |                          | VDDA_0P85_SERDES0_C |         | 0.85 |

|       |                          | VDDA_0P85_USB0      | USB0    | 0.85 |

|       |                          | VDD_MMCO            | MMC0    | 0.85 |

|       |                          | VDDR_CORE           | CORE    | 0.85 |

| 2     | SoC_DVDD3V3              | VDDSHV MCU          | MCU     | 3.3  |

|       |                          | VDDA_3P3_USB0       | USB0    | 3.3  |

|       |                          | VDDSHV0             | 通用      | 3.3  |

|       |                          | VDDSHV1             | PRG0    | 3.3  |

|       |                          | VDDSHV2             | PRG1    | 3.3  |

|       |                          | VDDSHV3             | GPMC    | 3.3  |

|       |                          | VMON_3P3 MCU        |         | 3.3  |

|       |                          | VMON_3P3 SOC        |         | 3.3  |

| 3     | VDDA_1V8 MCU             | VDDA MCU            | MCU     | 1.8  |

| 4     | VDDA_1V8 SERDES          | VDDA_1P8 SERDES0    | SERDES0 | 1.8  |

| 5     | VDDA_1V8_USB0            | VDDA_1P8_USB0       | USB0    | 1.8  |

| 6     | VDDA_1V8                 | VDDS_OSC            | OSC0    | 1.8  |

|       |                          | VDDA_TEMP_0/1       |         | 1.8  |

|       |                          | VDDA_PLL_0/1/2      |         | 1.8  |

| 7     | VDDS_DDR                 | VDDS_DDR            | DDR0    | 1.1  |

|       |                          | VDDS_DDR_C          |         | 1.1  |

| 8     | SOC_DVDD1V8              | VDDSHV4             | 闪存      | 1.8  |

|       |                          | VDDS_MMCO           | MMC0    | 1.8  |

|       |                          | VMON_1P8 MCU        |         | 1.8  |

|       |                          | VMON_1P8 SOC        |         | 1.8  |

| 9     | VDDSHV_SD_IO             | VDDSHV5             | MMC1    | 3.3  |

| 10    | VDDS_MMCO/<br>ADC0_VREFP | VDDS_MMCO           | MMC0    | 0    |

### 2.3.3.4 配置

#### 2.3.3.4.1 引导模式

SK EVM 板的引导模式由两组开关 ( SW2 和 SW3 ) 定义，或由连接到测试自动化连接器的 I2C 缓冲器定义。这样 AM64x 引导模式就可由用户控制 ( DIP 开关控制 ) 或由测试自动化接头控制。所有引导模式引脚至少都需要为上拉或下拉电阻留出空间。必须切换以支持所需引导模式的任何引导模式引脚，必须有一个弱下拉电阻器和一个能够连接较强的上拉电阻器的开关 ( Wurth 提供的 416131160808 )。开关在 OFF 位置时会断开上拉电阻的连接。如果引导模式引脚并非通过开关控制，则包含上拉和下拉电阻焊盘。AM64x 的各种引导模式必须由用户借助 8 位 DIP 开关进行控制。SK EVM 支持以下引导模式：

- OSPI

- MMC1 - SD 卡

- CSPW 以太网

- USB 器件

SoC 的引导模式引脚在正常运行期间可提供关联的替代功能。因此，使用缓冲器 IC 提供隔离可满足替代引脚的功能。缓冲器输出连接到 AM64x 的引导模式引脚 ON，在复位周期中需要引导模式时会启用此输出。缓冲器的输入连接到 DIP 开关电路，以及测试自动化电路所设 I2C 缓冲器的输出。如果由测试自动化电路控制引导模式，则所有开关都将手动设在 OFF 位置。引导模式缓冲器由常开电源供电，以确保即使 SoC 重新下电上电，引导模式仍然存在。

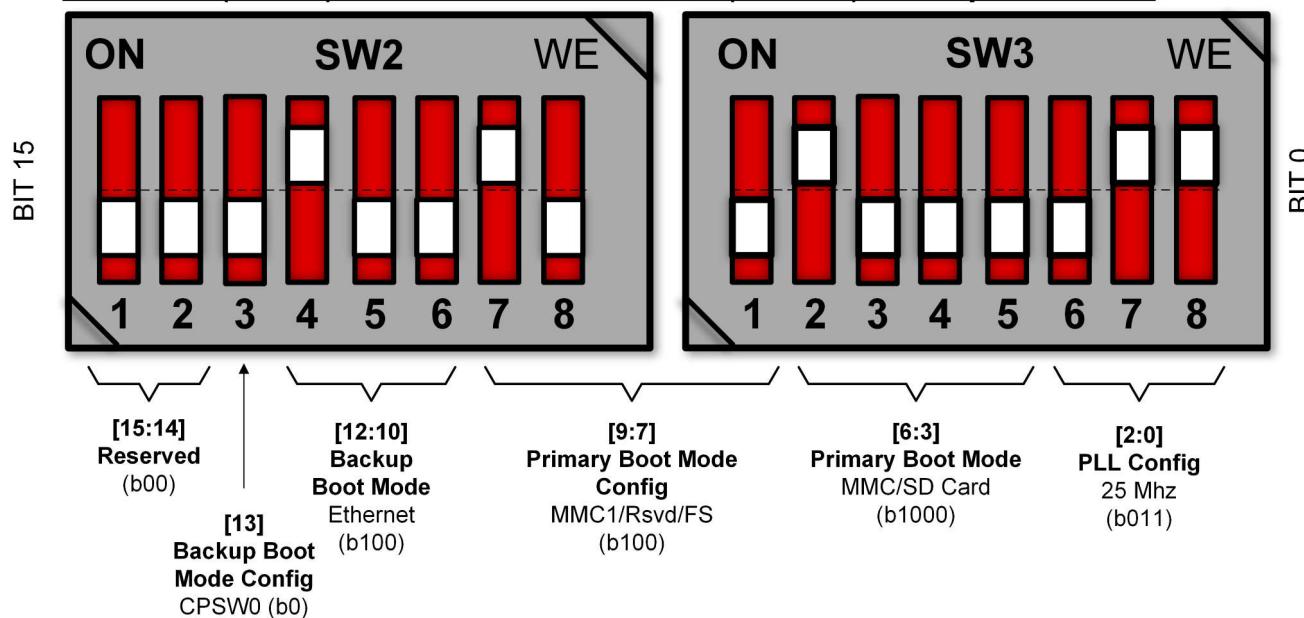

图 2-10 和表 2-9 提供了在器件通电之前选择引导模式的指南。

**uSD Boot (MMC1) – 25 Mhz PLL – Ethernet (CPSW0) Backup Bootmode**

**Note:** Actual Board Silkscreen May Appear Inverted in this Orientation. Follow Physical Switch Text

**图 2-10. 引导模式开关位置示例**

**表 2-9. 引导模式引脚映射**

| 位 15 | 位 14 | 位 13     | 位 12   | 位 11 | 位 10    | 位 9 | 位 8 | 位 7   | 位 6 | 位 5 | 位 4 | 位 3    | 位 2 | 位 1 | 位 0 |

|------|------|----------|--------|------|---------|-----|-----|-------|-----|-----|-----|--------|-----|-----|-----|

| 保留   | 保留   | 备用引导模式配置 | 备用引导模式 |      | 主引导模式配置 |     |     | 主引导模式 |     |     |     | PLL 配置 |     |     |     |

- 引导模式 [0:2] - 表示 PLL 配置的系统时钟频率。默认情况下，此位设为 25MHz。

表 2-10 详细介绍了 PLL 参考时钟选择。

表 2-10. PLL 参考时钟选择, 引导模式 [2:0]

| SW3.6 | SW3.7 | SW3.8 | PLL REF CLK (MHz)   |

|-------|-------|-------|---------------------|

| 关闭    | 关闭    | 关闭    | 19.2                |

| 关闭    | 关闭    | 打开    | 20                  |

| 关闭    | 打开    | 关闭    | 24                  |

| 关闭    | 打开    | 打开    | 25                  |

| 打开    | 关闭    | 关闭    | 26                  |

| 打开    | 关闭    | 打开    | 27                  |

| 打开    | 打开    | 关闭    | 保留                  |

| 打开    | 打开    | 打开    | 无 PLL 配置完成 ( 低速备份 ) |

- 引导模式 [3:6] - 提供主引导模式配置，在 POR 之后选择请求的引导模式，即要从中引导的外设/存储器。[表 2-11 提供主引导器件选择详情。](#)

表 2-11. 引导器件选择, 引导模式 [6:3]

| SW3.2 | SW3.3 | SW3.4 | SW3.5 | 所选的主引导器件  |

|-------|-------|-------|-------|-----------|

| 关闭    | 关闭    | 关闭    | 关闭    | 保留        |

| 关闭    | 关闭    | 关闭    | 打开    | OSPI      |

| 关闭    | 关闭    | 打开    | 关闭    | QSPI      |

| 关闭    | 关闭    | 打开    | 打开    | SPI       |

| 关闭    | 打开    | 关闭    | 关闭    | 以太网 RGMII |

| 关闭    | 打开    | 关闭    | 打开    | 以太网 RMII  |

| 关闭    | 打开    | 打开    | 关闭    | I2C       |

| 关闭    | 打开    | 打开    | 打开    | UART      |

| 打开    | 关闭    | 关闭    | 关闭    | MMC/SD 卡  |

| 打开    | 关闭    | 关闭    | 打开    | emmc      |

| 打开    | 关闭    | 打开    | 关闭    | USB       |

| 打开    | 关闭    | 打开    | 打开    | 保留        |

| 打开    | 打开    | 关闭    | 关闭    | GPMC NOR  |

| 打开    | 打开    | 关闭    | 打开    | PCIe      |

| 打开    | 打开    | 打开    | 关闭    | xSPI      |

| 打开    | 打开    | 打开    | 打开    | 无引导/开发引导  |

- 引导模式 [10:12] - 选择备用引导模式，即主引导器件出现故障时，要从中引导的外设/存储器。

[表 2-12 提供备用引导模式选择详情。](#)

表 2-12. 备用引导模式选择, 引导模式 [12:10]

| SW2.4 | SW2.5 | SW2.6 | 所选的备用引导器件   |

|-------|-------|-------|-------------|

| 关闭    | 关闭    | 关闭    | 无 ( 无备用模式 ) |

| 关闭    | 关闭    | 打开    | USB         |

| 关闭    | 打开    | 关闭    | 保留          |

| 关闭    | 打开    | 打开    | UART        |

| 打开    | 关闭    | 关闭    | 以太网         |

| 打开    | 关闭    | 打开    | MMC/SD      |

| 打开    | 打开    | 关闭    | SPI         |

| 打开    | 打开    | 打开    | I2C         |

- 引导模式 [9:7] - 这些引脚提供可选设置，与所选主引导器件搭配使用。

表 2-13 提供了主引导介质配置详情。

**表 2-13. 主引导介质配置，引导模式 [9:7]**

| SW2.7  | SW2.8   | SW3.1     | 引导器件      |

|--------|---------|-----------|-----------|

| 保留     |         |           | 保留        |

| 速度     | Iclk    | Csel      | OSPI      |

| 保留     | Iclk    | Csel      | QSPI      |

| 保留     | 模式      | Csel      | SPI       |

| Clkout | 延迟      | Link stat | 以太网 RGMII |

| Clkout | Clk src | 保留        | 以太网 RMII  |

| 总线复位   | 保留      | Addr      | I2C       |

| 保留     |         |           | UART      |

| 端口     | 保留      | Fs/raw    | MMC/SD 卡  |

| 保留     |         |           | eMMC      |

| 保留     | 模式      | 通道交换      | USB       |

| 保留     |         |           | 保留        |

| 保留     |         |           | GPMC NOR  |

| 保留     |         | 计时        | PCIe      |

| 速度     | 引脚命令    | Csel      | xSPI      |

| 保留     |         | 无/开发      | 无引导/开发引导  |

- 引导模式 [13] - 这些引脚提供可选设置，与备用引导器件搭配使用。开关 SW2.6 在 ON 时设为 1、OFF 时设为 0，请参阅器件特定 TRM。

- 引导模式 [14:15] - 保留。

表 2-14 提供了备用引导介质配置选项。

**表 2-14. 备用引导介质配置，引导模式 [13]**

| SW2.3 | 引导器件   |

|-------|--------|

| 保留    | 无      |

| 模式    | USB    |

| 保留    | 保留     |

| 保留    | UART   |

| IF    | 以太网    |

| 端口    | MMC/SD |

| 保留    | SPI    |

| 保留    | I2C    |

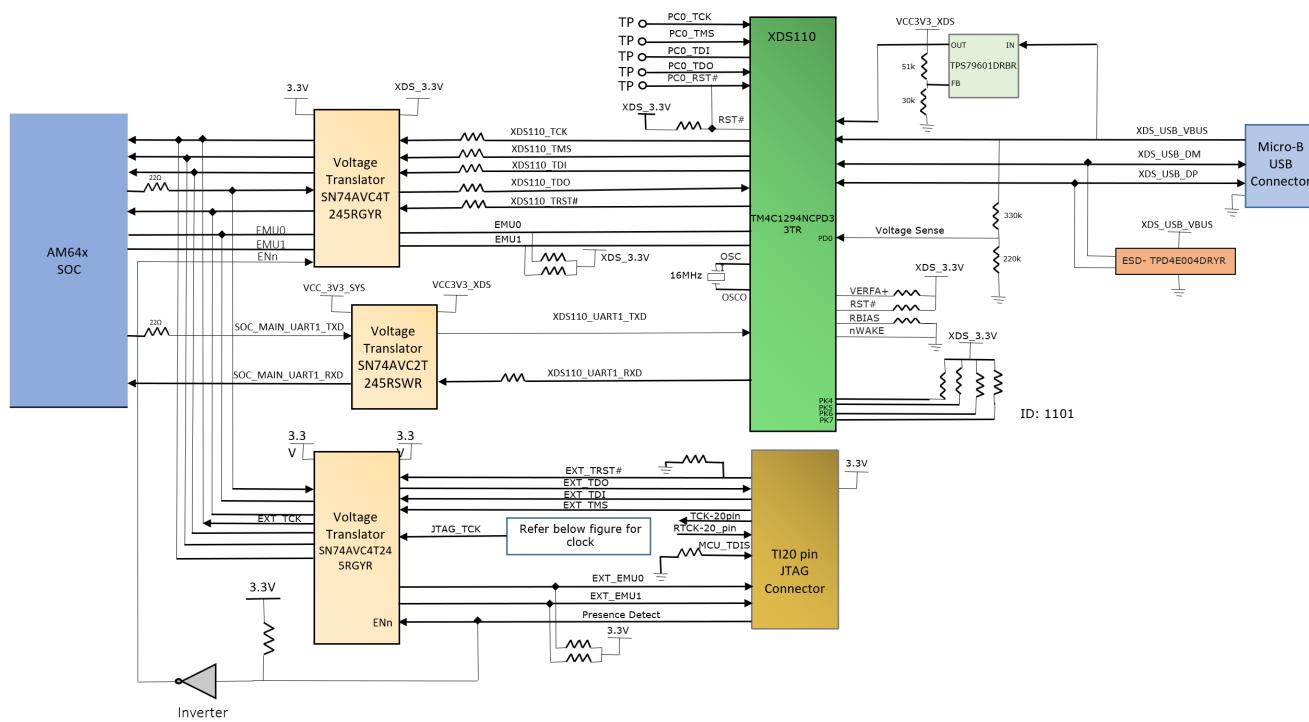

### 2.3.3.5 JTAG

在 SKEVM 上，可以选择通过一个 20 引脚标准 JTAG cTI 接头 (J14) 提供一个 JTAG 接口。这样用户就可连接外部 JTAG 仿真器。使用电压转换缓冲器将 cTI 接头的 JTAG 信号与 EVM 的其余部分相隔离。XDS110 部分和 cTI 接头部分的电压转换器输出进行多路复用并连接到 SoC JTAG 接口。如果使用存在检测电路感知到了与 cTI 20 引脚 JTAG 连接器的连接，则多路复用将设为将 20 引脚信号路由到 AM64x，以代替板载仿真电路。

cTI 20 引脚 JTAG 连接器 J14 的引脚布局在表 2-15 中提供。为 USB 信号提供 ESD 保护 ( 器件型号 TPD4E004 )，以便将 ESD 电流脉冲引向 VCC 或 GND。TPD4E004 可为高达  $\pm 15\text{kV}$  的人体放电模型 (HBM) ESD 脉冲 ( 在 IEC 61000-4-2 中指定 ) 提供保护，并提供  $\pm 8\text{kV}$  接触放电和  $\pm 12\text{kV}$  空气间隙放电。cTI 20 引脚连接器的引脚布局详情，请参阅表 2-15。

表 2-15. cTI 20 引脚连接器 (J14) 引脚布局

| 引脚编号 | 信号             | 引脚编号 | 信号            |

|------|----------------|------|---------------|

| 1    | JTAG_TMS       | 11   | JTAG_cTI_TCK  |

| 2    | JTAG_TRST#     | 12   | DGND          |

| 3    | JTAG_TDI       | 13   | JTAG_EMU0     |

| 4    | JTAG_TDIS      | 14   | JTAG_EMU1     |

| 5    | VCC_3V3_SYS    | 15   | JTAG_EMU_RSTN |

| 6    | NC             | 16   | DGND          |

| 7    | JTAG_TDO       | 17   | NC            |

| 8    | SEL_XDS110_INV | 18   | NC            |

| 9    | JTAG_cTI_RTCK  | 19   | NC            |

| 10   | DGND           | 20   | DGND          |

图 2-11. JTAG 接口

SKEVM 板包括 XDS110 类板载仿真和一个测试自动化接头，以支持软件构建的 TI 内部测试。仿真器的连接使用 USB2.0 micro-B 连接器 (J12) 以及用作供电 USB 从器件的电路。来自连接器的 VBUS 电源用于为仿真电路供电，这样即使在断开 EVM 电源时，与仿真器的连接也不会断开。使用电压转换缓冲器将 XDS110 电路与 EVM 的其余部分相隔离。此外，XDS110 还可在同一 USB 端口为 USB 信号转换提供 UART。SoC MAIN 域 (没有流控制) 的 UART1 通过隔离器连接到 XDS110 UART 端口。

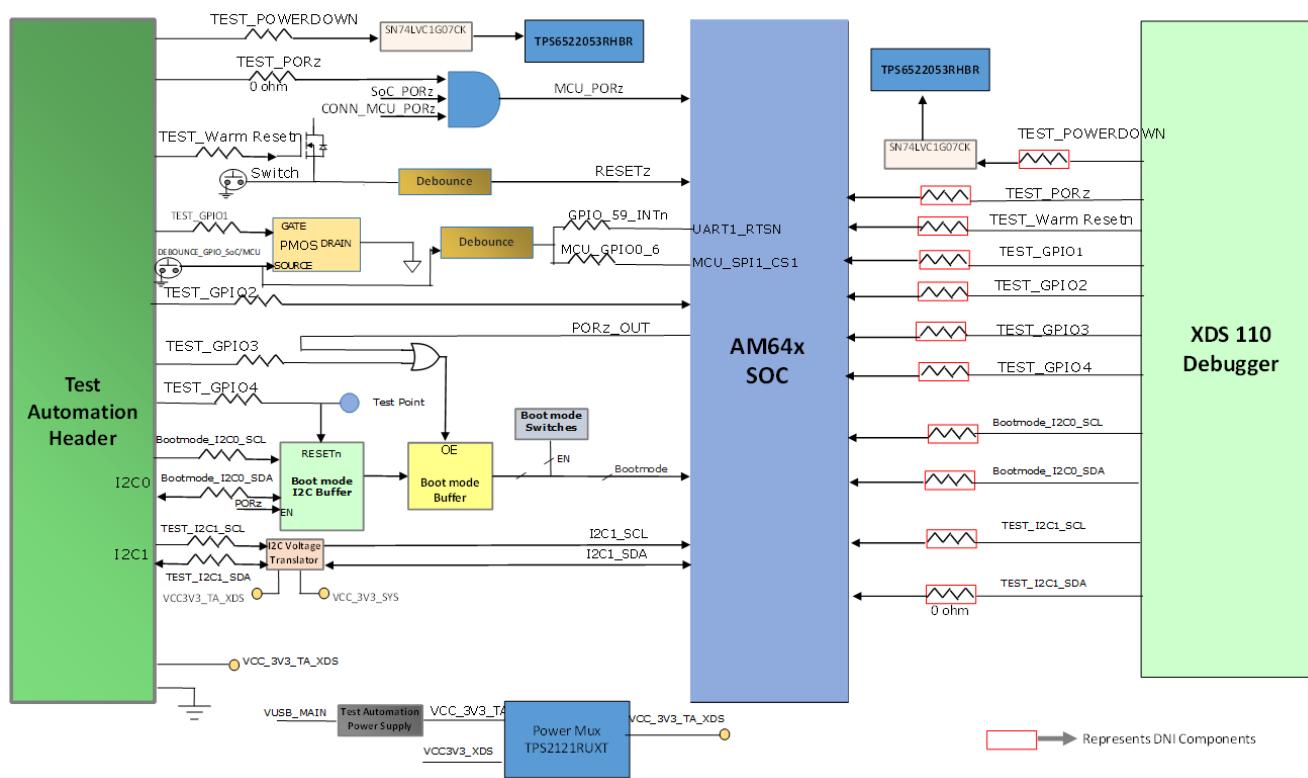

### 2.3.3.6 测试自动化

SKEVM 具有 40 引脚的测试自动化接头 (J16)，使外部控制器能够操纵一些基本操作，例如断电、POR、热复位、引导模式控制等。测试自动化接头包括四个 GPIO 和两个 I2C 接口 (I2C1、引导模式 I2C0)。

测试自动化电路具有电压转换电路，使控制器与 AM64x 使用的 IO 电压相隔离。AM64x 的引导模式必须由用户使用 DIP 开关进行控制，或通过 I2C IO 扩展器由测试自动化接头控制。

引导模式缓冲器用于隔离通过 DIP 开关或 I2C IO 扩展器驱动的引导模式控制。测试自动化电路由电源多路复用器 (TPS2121RUXT) 供电，该多路复用器具有由专用稳压器生成的输入电源 VCC3V3\_TA 和由 LDO 生成的

VCC3V3\_XDS (它是 XDS110 调试器部分的电源)。测试自动化接头 J16 的基本控件如下。表 2-16 提供了有关测试自动化接头信号的详情。

或者, 测试自动化接头功能可由 XDS110 控制器实现。因此, 为断电、POR、热复位、引导模式控制和 GPIO 信号提供了电阻选项 (R420、R421、R422、R423、R424、R425、R426、R427、R436、R437、R438 和 R439)。默认情况下将这些电阻标为 DNI, 以便外部控制器通过自动化接头控制基本操作。开发完用于 XDS110 的固件后, 安装上述电阻, 并将电阻 R380、R381、R382、R383、R384、R385、R386、R432、R433、R434 和 R435 标为 DNI, 以便通过 XDS110 微控制器控制基本操作。

为引导模式信号提供适当隔离, 以支持正常运行。SoC\_I2C [1] 连接到测试自动化接头, 与外部控制器进行通信。测试自动化接头的 I2C 接口之一连接到引导模式缓冲器, 以控制 AM64x 的引导模式, 另一 I2C 接口连接到 AM64x 的 I2C1 端口。

表 2-16 列出了从测试自动化接头路由的复位信号。AM64x 的引导模式可由用户或测试自动化接头控制。用户分别使用板上的两个 8 位置 DIP 开关控制引导模式。当开关设在 ON 位置时, 这些开关会将一个上拉电阻连接到缓冲器的输出端。当开关设在 OFF 位置时, 一个较弱的下拉电阻会将信号保持为低电平。缓冲器的输出连接到 AM64x 上的引导模式引脚, 在复位周期中如果需要引导模式, 则会启用输出; 缓冲器的输入连接到由测试自动化电路设置的 I2C 缓冲器的输出。

**表 2-16. 路由到测试自动化接头 J16 的信号列表**

| 信号            | 信号类型 | 功能                    |

|---------------|------|-----------------------|

| POWER_DOWN    | GPIO | 指示 EVM 将所有电路断电        |

| PORZn         | GPIO | 创建一个传到 AM64X 的 PORz   |

| WARM_RESETn   | GPIO | 创建一个传到 AM64X 的 RESETz |

| GPIO1         | GPIO | 与 AM64X 进行通信的 GPIO    |

| GPIO2         | GPIO | 与 AM64X 进行通信的 GPIO    |

| GPIO3         | GPIO | 用于启用 BOOTMODE 缓冲器     |

| GPIO4         | GPIO | 用于复位引导模式 IO 扩展器       |

| Bootmode I2C0 | I2C  | 与引导模式 I2C 缓冲器进行通信     |

| I2C1          | I2C  | 与 AM64x 进行通信          |

如果由测试自动化电路控制引导模式, 则所有开关都必须手动设在 OFF 位置。用于引导模式的引脚还具有其他功能, 在正常运行期间禁用引导模式缓冲器将隔离这些功能。图 2-12 展示了与 AM64x 连接的测试自动化信号。

图 2-12. 测试自动化接头

可以选择通过零欧电阻将测试自动化接头信号连接到 XDS110 微控制器。默认情况下将这些电阻标为 DNI。

表 2-17. 自动化接头信号连接到 XDS110

| TM4C1294 引脚名称 | 信号名称            |

|---------------|-----------------|

| PM0           | TEST_POWERDOWN  |

| PM1           | TEST_PORZn      |

| PM2           | TEST_WARMRESETn |

| PM3           | TEST_GPIO1      |

| PM4           | TEST_GPIO2      |

| PM5           | TEST_GPIO3      |

| PM6           | TEST_GPIO4      |

| PM7           | TEST_POWERDOWN  |

| PG0           | TEST_PORZn      |

| PG1           | TEST_WARMRESETn |

表 2-18 列出了测试自动化接头的引脚布局和 IO 方向。

表 2-18. 测试自动化接头 (J16) 引脚布局

| 引脚编号 | 信号名称             | IO 方向 (wrt SoC) |

|------|------------------|-----------------|

| 1    | VCC3V3_TA        | 电源 (输出)         |

| 2    | VCC3V3_TA        | 电源 (输出)         |

| 3    | VCC3V3_TA        | 电源 (输出)         |

| 4    | NC               | 不适用             |

| 5    | NC               | 不适用             |

| 6    | NC               | 不适用             |

| 7    | DGND             | 接地              |

| 8    | NC               | 不适用             |

| 9    | NC               | 不适用             |

| 10   | NC               | 不适用             |

| 11   | NC               | 不适用             |

| 12   | NC               | 不适用             |

| 13   | NC               | 不适用             |

| 14   | NC               | 不适用             |

| 15   | NC               | 不适用             |

| 16   | DGND             | 接地              |

| 17   | NC               | 不适用             |

| 18   | NC               | 不适用             |

| 19   | NC               | 不适用             |

| 20   | NC               | 不适用             |

| 21   | NC               | 不适用             |

| 22   | NC               | 不适用             |

| 23   | NC               | 不适用             |

| 24   | NC               | 不适用             |

| 25   | DGND             | 接地              |

| 26   | TEST_POWERDOWN   | 输入              |

| 27   | TEST_PORZn       | 输入              |

| 28   | TEST_WARMRESETn  | 输入              |

| 29   | NC               | 不适用             |

| 30   | TEST_GPIO1       | 双向              |

| 31   | TEST_GPIO2       | 双向              |

| 32   | TEST_GPIO3       | 输入              |

| 33   | TEST_GPIO4       | 输入              |

| 34   | DGND             | 接地              |

| 35   | NC               | 不适用             |

| 36   | SOC_I2C1_TA_SCL  | 双向              |

| 37   | BOOTMODE_I2C_SCL | 双向              |

| 38   | SOC_I2C1_TA_SDA  | 双向              |

| 39   | BOOTMODE_I2C_SDA | 双向              |

| 40   | DGND             | 接地              |

| 41   | DGND             | 接地              |

| 42   | DGND             | 接地              |

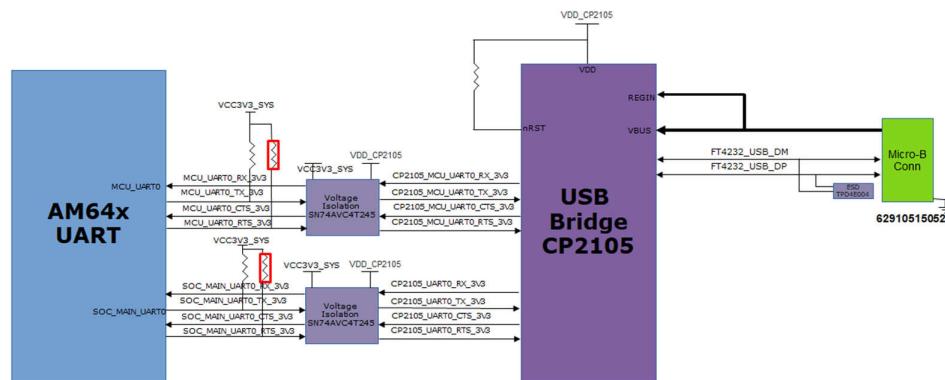

### 2.3.3.7 UART 接口

AM64x 提供的两个 UART 端口 **MAIN\_UART0** 和 **MCU\_UART0** 连接到双通道 USB 转 UART 桥接器 (CP2105) , 并端接至 USB Micro B 连接器 J11。CP2105 的两个端口利用 RXD、TXD、RTS 和 CTS 信号连接到 **MAIN\_UART0** 和 **MCU\_UART0**。

USB 接口电路用于总线供电配置 , 而电压转换器 (SN74AVC4T245) 用于隔离 AM64x IO。CP2105 包含一个片上 5V 到 3.45V 稳压器。这样 CP2105 就可配置为 USB 总线供电设备。VDD 引脚上的稳压器输出可用于驱动 IO 电源 , 并作为电压转换器的电源轨之一。在内部 , 同一 VDD 用于 CP2105 核心部分的运行。CP2105 还包含一个集成时钟 , 因此无需外部晶体。来自 SOC 的 **MAIN\_UART0** 和 **MCU\_UART0** 处于 3.3V IO 电平。该器件使用内部 POR 电路。在正常运行时 , nRST 引脚需要通过 10K 电阻器上拉至 3V3 供电。由于该器件在总线供电配置下运行 , 来自 USB 连接器的 VBUS 需要连接至 CP2105 的 “REGIN” 引脚 , 作为内部稳压器的输入。

对 USB 信号提供 ESD 保护 , 以便将 ESD 电流脉冲引向 VCC 或 GND。TPD4E004 可为高达  $\pm 15\text{kV}$  的人体放电模型 (HBM) ESD 脉冲 (在 IEC 61000-4-2 中指定) 提供保护 , 并提供  $\pm 8\text{kV}$  接触放电和  $\pm 12\text{kV}$  空气间隙放电。

图 2-13 展示了与 AM64x 连接的双 UART 转 USB 桥接器。

图 2-13. UART 接口

### 2.3.3.8 存储器接口

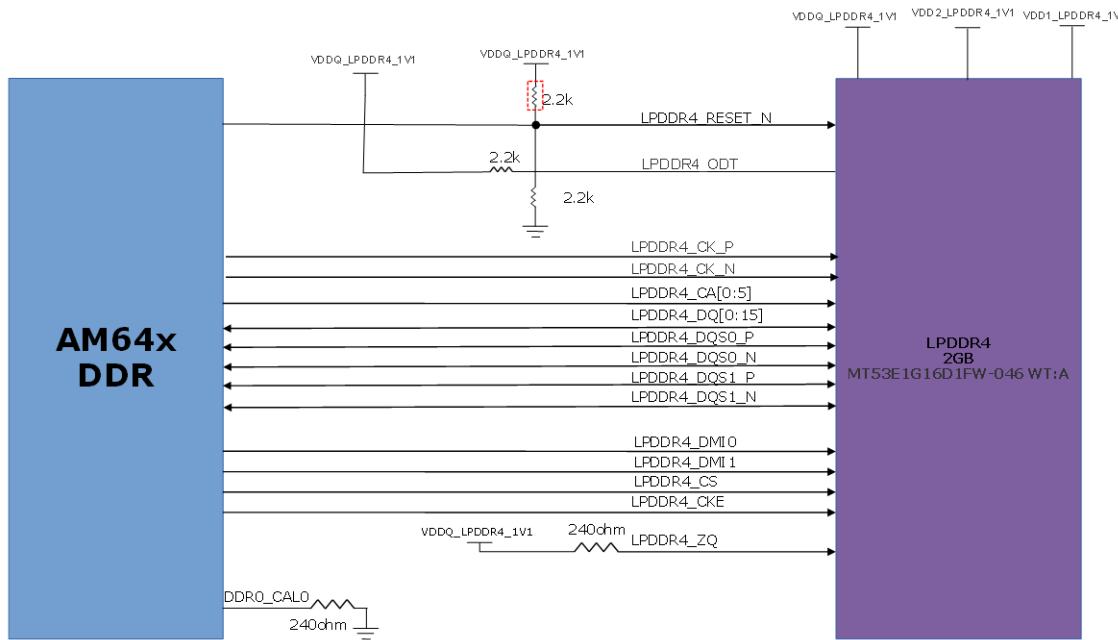

#### 2.3.3.8.1 LPDDR4 接口

SK EVM 具有 2GB、16 位宽 LPDDR4 存储器，运行数据速率为每引脚 4226Mbps。使用 Micron 的 MT53E1G16D1FW-046 WT: A。LPDDR 存储器采用板载安装形式（单芯片），需要 1.1V，降低了功率需求。LPDDR4 器件需要 1.1V 的 I/O 功率和内核 2 功率，以及 1.8V 的 DRAM 激活电源（内核 1）。

LPDDR4 复位是由 SOC 控制的低电平有效信号，将该信号上拉可设置默认有效状态，也提供了下拉空间。一个  $240\Omega$  电阻从 ZQ 引脚连接到 LPDDR4 器件的 1.1V 电源，SoC DDR0\_CAL 引脚接地。

为 DQ、DQS 和 DM\_n 信号提供了 ODT（片上终端）。该器件能够提供三种不同的 ODT 模式：标称、动态和 Park，终端值为：RTT (Park)、RTT (NOM) 和 RTT (WR)。图 2-14 展示了 LPDDR4 和 AM64x 之间的 DDR 接口。

图 2-14. LPDDR4 接口

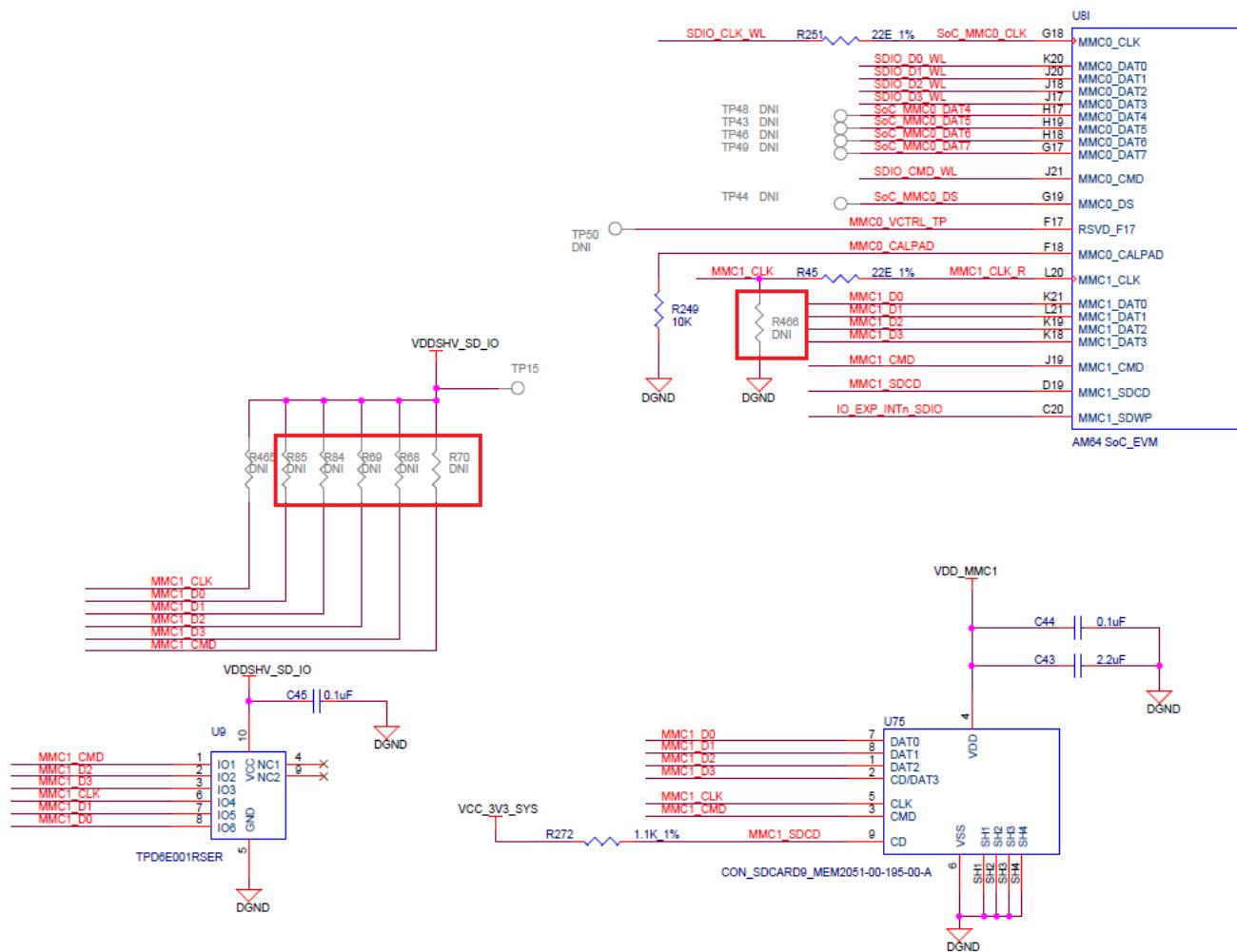

#### 2.3.3.8.2 MMC 接口

AM64x 处理器提供两个 MMC 接口。其中一个连接到 Wilink 模块，另一个用于 micro SD 卡接口。

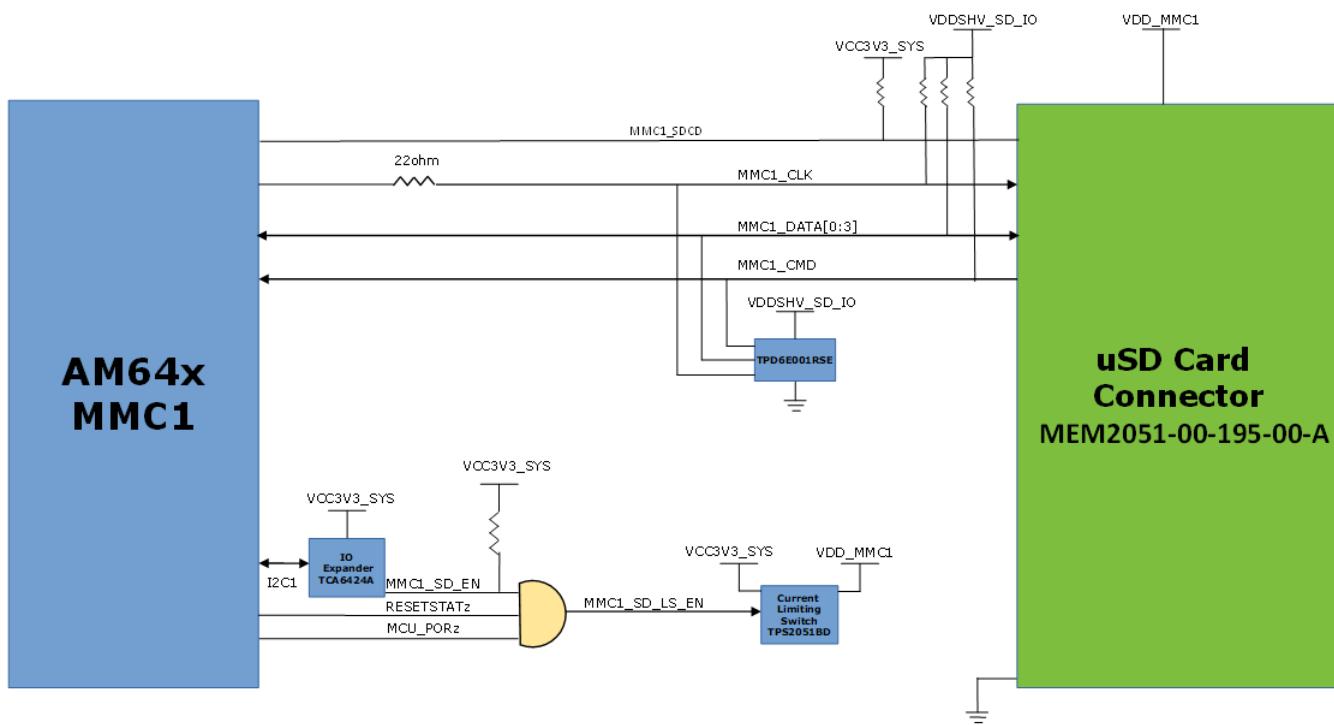

#### 2.3.3.8.2.1 Micro SD 接口

SKEVM 板提供一个 micro SD 卡接口，连接到 AM64x SOC 的 MMC1 端口。micro-SD 卡接口支持 16GB 密度的 UHS1 操作，包括 1.8V 和 3.3V 时的 IO 操作。AM64x SoC 中包含的支持 IO 电压开关的电路与 SD 信号的 IO 电压连接，允许处理器协商 IO 电压。对于高速卡，SOC 的 ROM 代码尝试找到卡和控制器可以支持的最快速度，并可以转换为 1.8V。来自 SOC 的内部 SDIO LDO 输出在 CAP\_VDDSHV\_SDLDO 引脚上提供，连接到 SD 信号的 IO 电压以及 SOC 的 VDDSHV\_MMC1 的电源引脚，SOC 是 MMC1 接口的电源。

为数据、时钟和命令信号提供 ESD 保护器件 (TPD6E001RSE)。TPD6E001RSE 是线路终止器件，集成了 TVS 二极管，提供系统级 IEC 61000-4-2 ESD 保护、 $\pm 8\text{kV}$  接触放电和  $\pm 15\text{kV}$  空气间隙放电。

SD 卡设为在 SD 模式下运行。SD 卡连接器的 CD (卡检测) 引脚被拉低，连接到 SOC 的 CD 引脚。图 2-15 展示了 micro-SD 卡接口的方框图。

图 2-15. Micro SD 接口

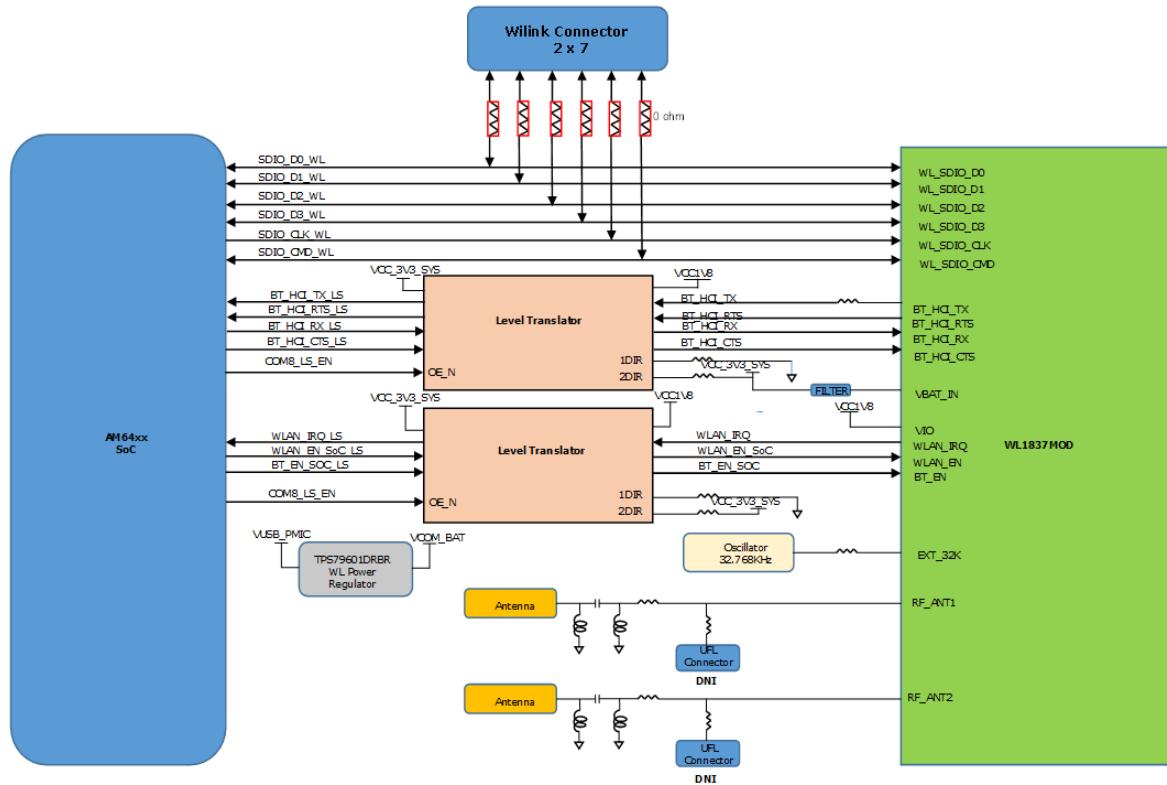

#### 2.3.3.8.2.2 WiLink 接口

SKEVM 板上有 TI 的 WiLink 模块 (WL1837MODGIMOC), 连接到 AM64x SoC 的 MMC0 端口。WL1837MOD 是一套支持 Wi-Fi 的双频带 2.4GHz 和 5GHz 模块解决方案, 配有两根支持工业温度级的天线 (W3006)。该模块连接到 MMC0 接口的 4 位 IO, 支持 IEEE 标准 802.11a/b/g/n 数据速率 (20MHz 或 40MHz SISO 或 20MHz MIMO)。该模块提供更高的吞吐量和更大的范围, 使 Wi-Fi 和蓝牙共存于一种低功耗设计中。

该器件支持以下蓝牙功能 :

- 蓝牙 4.2 安全连接以及 CSA2

- 并发运行以及蓝牙、低功耗蓝牙无线技术、音频处理和 WLAN 的内置共存和优先级处理。

- 支持片上 SBC 编码 + A2DP 的专用音频处理器

- 辅助 A2DP (A3DP) : 内部实现 SBC 编码

- 辅助 WB 语音 (AWBS) : 在内部实现经过修改的 SBC 编解码器

- 图 2-16 展示了与 AM64x 连接的 Wilink 模块的方框图。

SKEVM 不支持 A2DP BT 音频配置文件或 HF 配置文件。

该模块需要两个电源, 3.3V 用于 VBAT\_IN, 1.8V 用于 VIO\_IN。PMIC 为 WL1837MOD WiLink 模块供电, 还可通过专用稳压器供电 (可选, 默认为 DNI)。

SOC 的 MMC0 接口由 VDDSHV\_MMCO 电源 (连接到 1.8V IO 电源) 供电。蓝牙 UART 信号, 启用的 BT、WLAN、WLAN\_IRQ 信号使用电平转换器 (SN74AVC4T245RSVR) 连接到 AM64x 的 GPIO。输入时钟使用 32.768KHz 振荡器提供。

在 SOC 的 MMC0\_DAT [4:7] 引脚上, 以及 WL1837 模块的 WL\_GPIO、BT\_UART\_DEBUG、WL\_UART\_DEBUG 引脚上提供测试点。

还提供 14 引脚 Wi-Link 连接器。外部 Wi-Fi 模块 (不支持蓝牙模块) 可通过 14 引脚 Wi-Link 连接器与 SoC 进行通信。默认情况下, 连接到 14 引脚 Wi-Link 连接器的信号上不安装 14 引脚 Wi-Link 连接器和 OE 电阻。

图 2-16. WiLink 模块接口

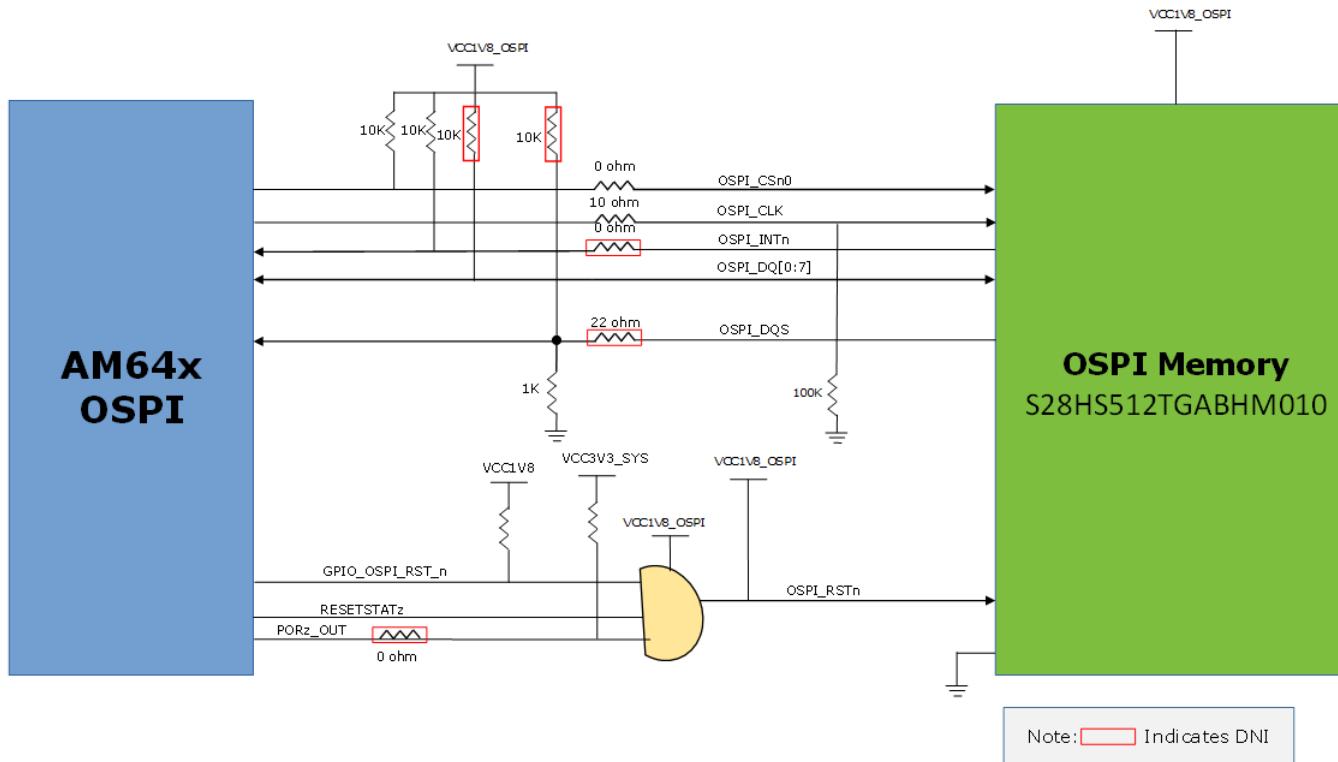

### 2.3.3.8.2.3 OSPI 接口

SK EVM 板包含由 Cypress 提供、器件型号为 S28HS512TGABHM010 的 512Mb OSPI 存储器器件，可连接到 AM64x SOC 的 OSPI0 接口。OSPI 支持高达 166MHz 的存储器速度。OSPI 闪存由 1.8V IO 供电。为闪存存储器的 VCC 和 VCCQ 引脚提供 1.8V 电源。

闪存的复位连接到一个电路，对来自 SoC 的 RESETSTATz、PORz\_OUT 和 OSPI0\_CS2 (GPIO\_OSPI\_RSTn) 进行与操作。可对热复位和冷复位应用复位。在 GPIO\_OSPI\_RSTn 上提供了上拉阻力，其来自 SOC 引脚，用于设置默认有效状态。

两个信号路由到 OSPI0\_DQS：

1. 从存储器器件路由到 OSPI0\_DQS

2. 从 SoC 路由到 OSPI0\_LBCLK

若要路由来自存储器器件的 DQS：DNI R33 和 R39。

若要路由来自 SoC 的 OSPI0\_LBCLK：安装 R33 和 R39。

OSPI 和 QSPI 实现方式：为 DATA [7:0]、DQS、INT# 和 CLK 信号提供 0Ω 电阻器。在 DATA [7:0] 上提供了安装外部上拉电阻器的空间，以防止总线悬空。

图 2-17 展示了 AM64x SK EVM 的 OSPI 接口方框图。

图 2-17. OSPI 接口

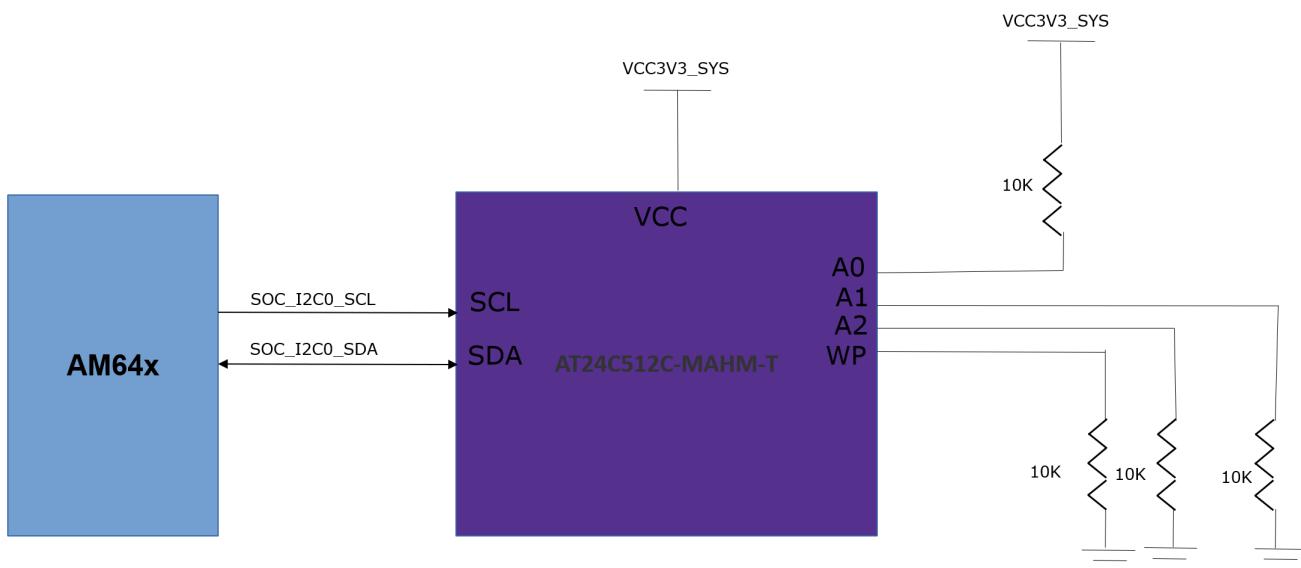

#### 2.3.3.8.2.4 板 ID EEPROM 接口

AM64x 处理器由其版本和序列号（存储在板载 EEPROM 中）进行标识。板 ID 存储器应配置为对地址 0x51 进行响应。使用来自 Microchip 的 AT24C512C-MAHM-T，它与 SOC 的 I2C0 端口连接。EEPROM 的 I2C 地址可以修改，方法是将 A0、A1、A2 引脚设为 LOW。写保护输入如果连接到 GND，则允许执行正常写入操作。当 WP 引脚直接连接到 VCC 时，将禁止执行对受保护存储器的所有写入操作。如果引脚保持悬空，则 WP 引脚将从内部下拉至 GND。WP 在此处通过 10k 电阻器连接 GND。

图 2-18. 板 ID EEPROM

### 2.3.3.9 以太网接口

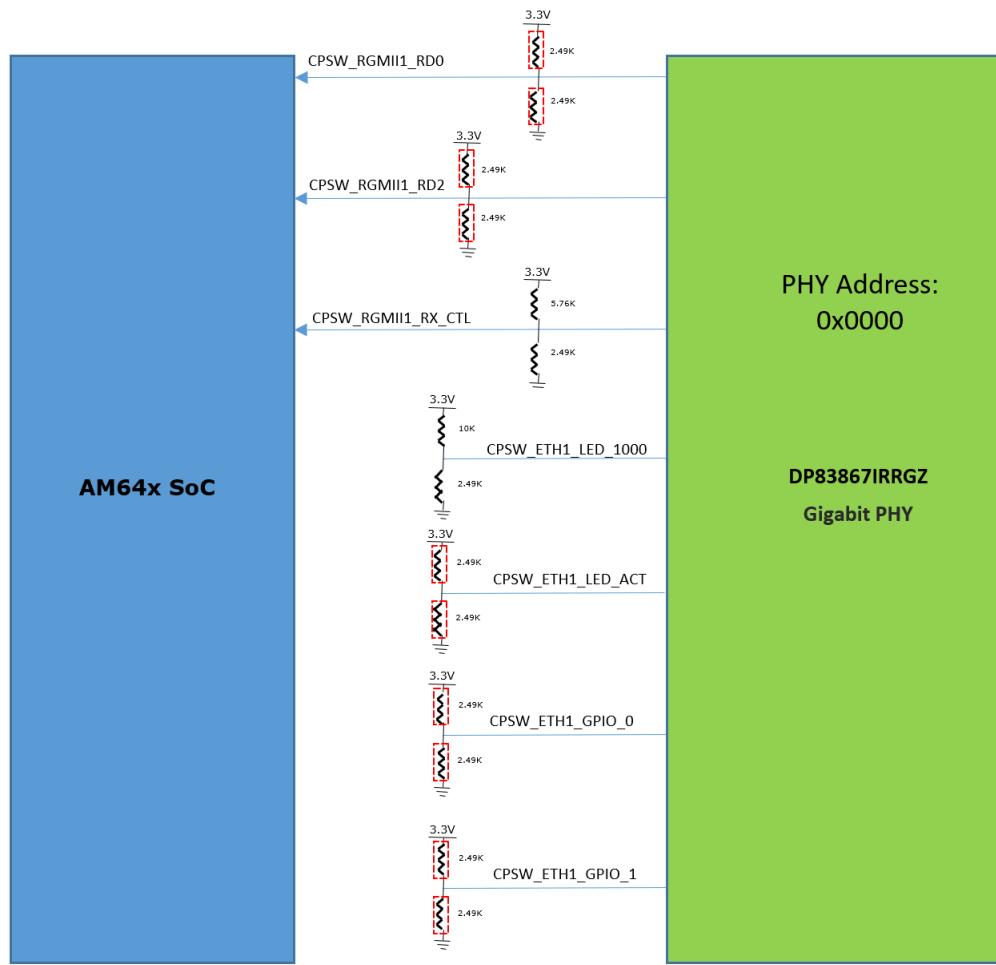

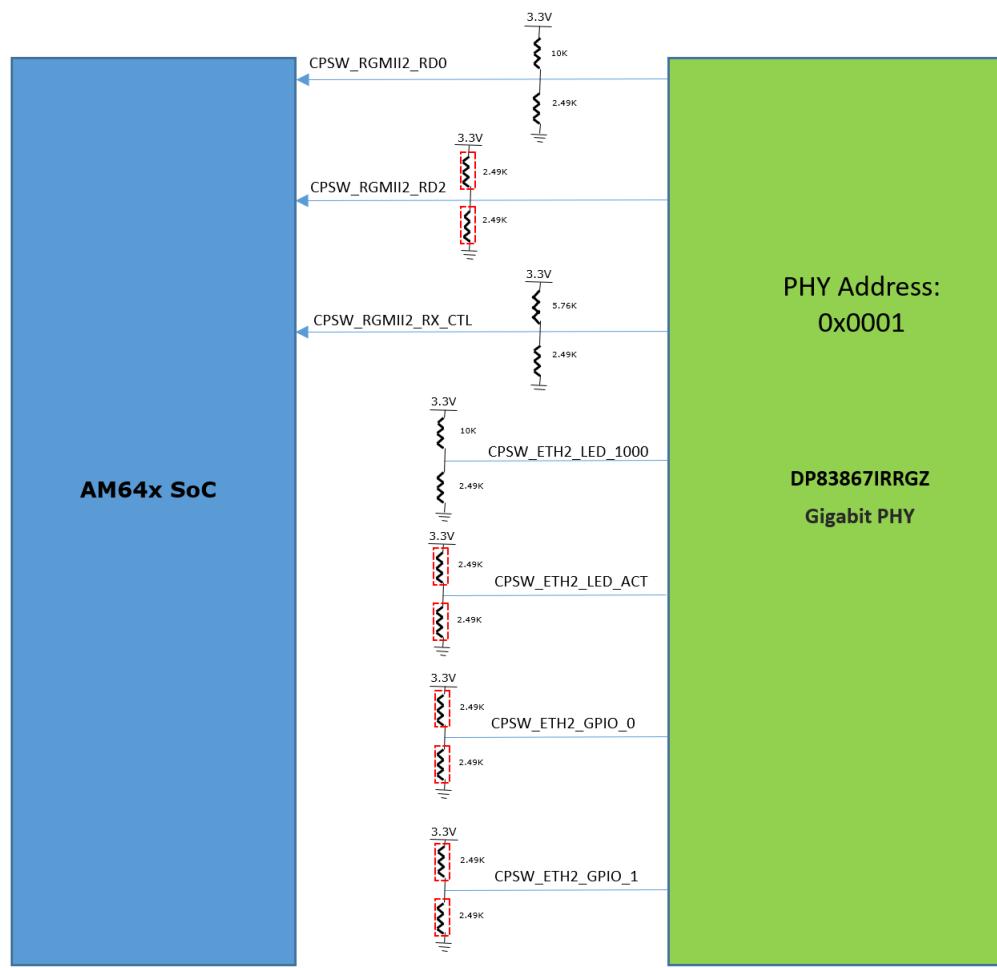

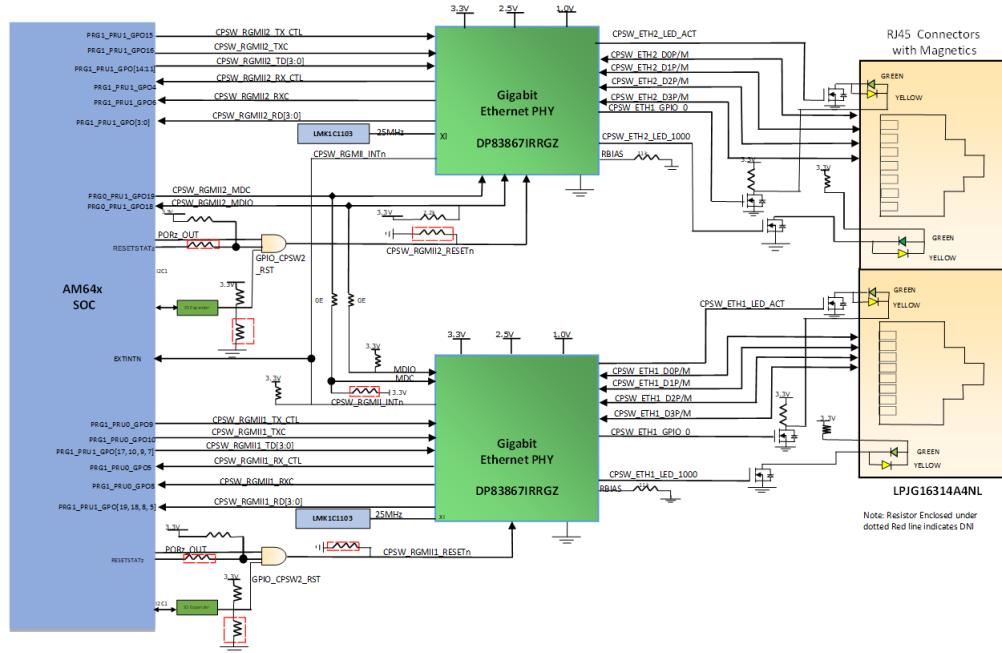

SKEVM 提供两个千兆位以太网端口，用于外部通信。AM64xx SoC 的 RGMII 千兆位以太网 CPSW 端口的两个通道分别与两个千兆位以太网 PHY 收发器 DP83867 连接，它们最终端接两个具有集成磁性元件的 RJ45 连接器。

PHY DP83867 的 48 引脚版本配置为广播 1Gb 操作，内部延迟设置为与 AM64x 的内部延迟相适应。与 PRG1 共享的 RGMII1 信号用于 RX 路径，允许 PRG0 连接到板上的 PRU 接头。PRG1 的 CPSW\_RGMII1 和 CPSW\_RGMII2 端口共享一个通用 MDIO 总线，与外部 PHY 收发器通信。

板上使用两个端口 RJ45 连接器 (LPJG16314A4NL) 进行以太网 10/100/1G 连接。RJ45 连接器具有集成磁性元件和 LED，用于指示 1000BASE-T 链接和接收或发送活动。

#### 2.3.3.9.1 DP83867 PHY 默认配置

DP83867 PHY 使用四级电阻器 strap 配置，可生成四种不同的电压范围。电阻器连接到 RX 数据和控制引脚，它们通常由 PHY 驱动，是 AM64x 的输入。每种模式的电压范围如下所示。

模式 1 - 0V 至 0.3234V

模式 2 - 0.462V 到 0.6303V

模式 3 - 0.7425V 到 0.9372V

模式 4 - 2.2902V 到 2.904V

DP83867 器件包括内部下拉电阻器。选择外部拉电阻器的值，为 AM64x 的引脚提供尽可能接近接地或 3.3V 的电压。图 2-19 中显示了 Strap 配置。表 2-19 中提供了 strap 配置值

表 2-19. Strap 配置值

| 模式 | 目标电压          |               |               | 理想 Rhi<br>(k Ω) | 理想 Rio<br>(k Ω) |

|----|---------------|---------------|---------------|-----------------|-----------------|

|    | Vmin(V)       | Vtyp(V)       | Vmax(V)       |                 |                 |

| 1  | 0             | 0             | 0.098 * VDDIO | 断开              | 断开              |

| 2  | 0.140 * VDDIO | 0.165 * VDDIO | 0.191 * VDDIO | 10              | 2.49            |

| 3  | 0.225 * VDDIO | 0.255 * VDDIO | 0.284 * VDDIO | 5.76            | 2.49            |

| 4  | 0.694 * VDDIO | 0.763 * VDDIO | 0.886 * VDDIO | 2.49            | 断开              |

CPSW PHY-1 和 CPSW PHY-2 实现了地址 strap 配置，分别用于设置地址 -00000 (0h) 和 00001(01h)。默认情况下，由于 strap 配置引脚具有内部下拉电阻器，所有 strap 配置引脚均提供了上拉和下拉占用空间，除了 LED\_0。LED\_0 用于镜像启用，默认情况下设为模式 1，模式 4 不适用，模式 2、模式 3 选项不能满足要求。表 2-20 和表 2-21 中提供了 CPSW RGMII1 Ethernet PHY 和 CPSW RGMII1 以太网 PHY 的默认 strap 设置。

图 2-19. CPSW 以太网 PHY-1 Strap 设置

图 2-20. CPSW 以太网 PHY-2 Strap 设置

表 2-20. CPSW RGMII-1 以太网 PHY 的默认 Strap 设置

| Strap 设置 | 引脚名称          | Strap 功能            | PRG1_PRU1、<br>PRG1_PRU0 的模式 | PRG1 的 Strap 功能<br>值 | 说明                      |

|----------|---------------|---------------------|-----------------------------|----------------------|-------------------------|

| PHY 地址   | RX_D2         | PHY_AD3             | 1                           | 0                    | PHY 地址 : 0000           |

|          |               | PHY_AD2             | 1                           | 0                    |                         |

|          | RX_D0         | PHY_AD1             | 1                           | 0                    |                         |

|          |               | PHY_AD0             | 1                           | 0                    |                         |

| 自动协商     | RX_DV/RX_CTRL | 自动协商                | 3                           | 0                    | 自动协商禁用 = 0              |

| 运行模式     | LED2          | RGMII 时钟偏差 TX[1]    | 5                           | 0                    | RGMII TX 时钟偏差设<br>为 0ns |

|          |               | RGMII 时钟偏差 TX[0]    | 5                           | 0                    |                         |

|          | LED_1         | RGMII 时钟偏差 TX[2]    | 5                           | 1                    |                         |

|          |               | ANEG_SEL            | 1                           | 0                    |                         |

|          | LED_0         | 镜像启用                | 1                           | 0                    | 通告能力 10/100/1000        |

|          | GPIO_1        | RGMII 时钟偏差<br>RX[2] | 1                           | 0                    | RGMII RX 时钟偏差设<br>为 2ns |

|          |               | RGMII 时钟偏差 TX[1]    | 1                           | 0                    |                         |

|          | GPIO_0        | RGMII 时钟偏差<br>RX[0] | 1                           | 0                    |                         |

表 2-21. CPSW RGMII-2 以太网 PHY 的默认 strap 设置

| Strap 设置 | 引脚名称          | Strap 功能         | PRG1_PRU1、<br>PRG1_PRU0 的模式 | PRG0 和 PRG1 的<br>Strap 功能值 | 说明                  |

|----------|---------------|------------------|-----------------------------|----------------------------|---------------------|

| PHY 地址   | RX_D2         | PHY_AD3          | 1                           | 0                          | PHY 地址 : 0001       |

|          |               | PHY_AD2          | 1                           | 0                          |                     |

|          | RX_D0         | PHY_AD1          | 2                           | 0                          |                     |

|          |               | PHY_AD0          | 2                           | 1                          |                     |

| 自动协商     | RX_DV/RX_CTRL | 自动协商             | 3                           | 0                          | 自动协商禁用 = 0          |

| 运行模式     | LED2          | RGMII 时钟偏差 TX[1] | 5                           | 0                          | RGMII TX 时钟偏差设为 0ns |

|          |               | RGMII 时钟偏差 TX[0] | 5                           | 0                          |                     |

|          | LED_1         | RGMII 时钟偏差 TX[2] | 5                           | 1                          | 通告能力 10/100/1000    |

|          |               | ANEG_SEL         | 1                           | 0                          |                     |

|          | LED_0         | 镜像启用             | 1                           | 0                          | 镜像启用已禁用             |

|          |               | RGMII 时钟偏差 RX[2] | 1                           | 0                          | RGMII RX 时钟偏差设为 2ns |

|          | GPIO_1        | RGMII 时钟偏差 TX[1] | 1                           | 0                          |                     |

|          | GPIO_0        | RGMII 时钟偏差 RX[0] | 1                           | 0                          |                     |

### 2.3.3.9.2 DP83867 - 电源、时钟、复位、中断和LED

PHY 器件包括集成式 MDI 终端电阻器。因此未提供外部终端。

电源：来自 PRG0 和 PRG1 域的 RGMII 信号处于 3.3V IO 电平。千兆位 PHY 器件 DP83867 需要 3.3V 的 I/O 功率，以及 2.5V 和 1.0V 的模拟电源

时钟：通过时钟缓冲器 LMK1C1103 ( 独立输出 ) 向 PHY 提供 25 MHz LVCMOS 时钟。

复位：PHY 的复位是通过一个电路将 IO 扩展器的 PORz\_OUT 和 GPIO，以及来自 SoC 的 RESETSTATz ( 可选 ) 进行与操作。默认情况下，RESETSTATz 不用于复位 PHY。IO 扩展器可通过 AM64x SOC 的 I2C1 端口进行控制。为 GPIO 提供了一个上拉电阻器和一个下拉电阻器的占用空间，可设置默认值。每个以太网 PHY 分别包含由 GPIO 驱动的复位信号。可通过对 RESET\_N 引脚施加持续时间至少为 1 微秒的低脉冲来实现硬件复位。

中断：将来自 PRG1 域的两个 CPSW RGMII PHY 的中断连接在一起，并连接到 AM64x SOC 的 EXTINTN 引脚。

四个可配置的 LED 引脚和以太网 PHY 的两个 GPIO 用于指示链路状态。LED 可多路复用若干功能，用于不同的工作模式。可使用 DP83867 器件上的 LEDCR1 寄存器地址 0x0018 选择 LED 工作模式。默认配置如下所示。

**LED0**：默认情况下，此引脚表示链接已建立。其他功能可通过 DP83867 器件中的 LEDCR1 [3:0] 寄存器位配置。LDE0 在 CPSW PHY (DP83867) 中未使用，这也是一个 strap 配置引脚，用于设置镜像启用。这些功能并不需要，因此未提供针对 LED0 的 strap 配置。

**LED\_1**：默认情况下，此引脚表示 1000BASE-T 链接已建立。可使用 strap 配置电阻器将此设置改为自动协商 10/100Mbps。其他功能可通过 DP83867 器件中的 LEDCR1 [7:4] 寄存器位配置。LED\_1 也是 strap 配置引脚，具有内部下拉电阻，用于在 DP83867 器件中设置 RGMII TX 时钟偏差。由于此引脚在两个器件上均设为有效，如果直接驱动 LED，会导致 LED 照明变暗。因此使用 MOSFET 来驱动 LED。

**LED\_2**：默认情况下，此引脚表示接收或发送活动。其他功能可通过 DP83867 器件中的 LEDCR1 [11:18] 寄存器位配置。LED\_2 也是 strap 配置引脚，具有内部下拉电阻器，用于在 DP83867 器件中设置 RGMII TX 时钟偏差。默认条件是自动协商，链路速率为 10/100/1000Mbps，可以使用提供的 strap 配置电阻器改变这种条件。如果直接驱动 LED，用于 strap 设置的上拉电阻器会导致 LED 照明暗淡。因此使用 MOSFET 来驱动 LED。

**GPIO0**：在 DP83867 PHY 中，可通过 GPIO 多路复用器控制寄存器 1 (GPIO\_MUX\_CTRL1) 将 GPIO 配置为发挥 LED3 的功能，并可通过对 LEDCR1 寄存器进行编程来设置 LED 配置，而且该引脚用于指示作为 100Mbps 连接运行。使用 MOSFET 来驱动 LED，如下图所示。

**GPIO1**：在 DP83867 PHY 中，可通过 GPIO 多路复用器控制寄存器 1 (GPIO\_MUX\_CTRL1) 将 GPIO 配置为发挥 LED3 的功能，LED 配置可通过编程 LEDCR1 寄存器进行设置。这也是一个 strap 配置引脚，用于设置快速链路丢失 (FDP)，当前为禁用状态。

以太网 RJ45 连接器中的 LED 指示：通过外部 MOSFET 实现 LED 控制。

**RJ45 连接器 LED 指示 - CPSW (DP83867)**：LED1 连接到 RJ45 LED ( 绿色 )，指示 1000 MHz 链接；LED2 连接到 RJ45 LED ( 黄色 )，指示发送/接收活动。通过外部 MOSFET 实现 LED 控制。

图 2-21. 以太网接口

备注

红色框中的电阻器是 DNI 元件

### 2.3.3.9.3 工业应用 LED

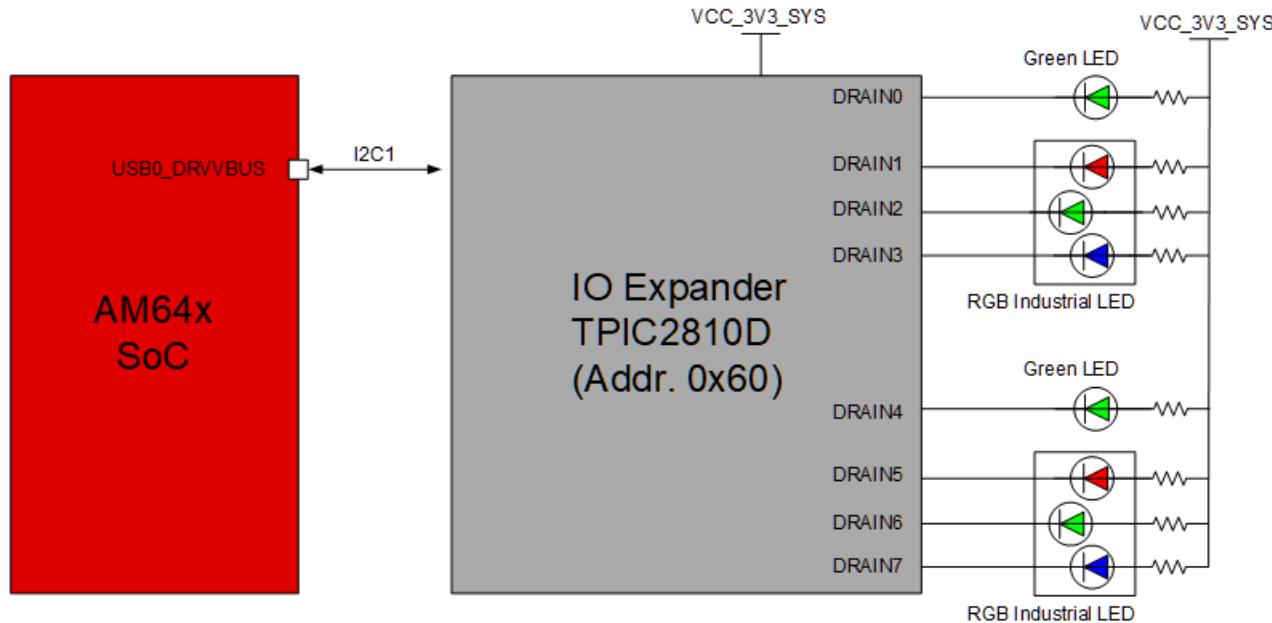

有 8 个 LED 连接到基于 I2C 的 LED 驱动器 (TPIC2810D) , 它由 SoC 通过 I2C1 端口进行控制。这 8 个 LED 可根据用户应用进行切换。这 8 个 LED 主要用于工业应用。

图 2-22. 以太网接口 - LED

### 2.3.3.10 USB 3.0 接口

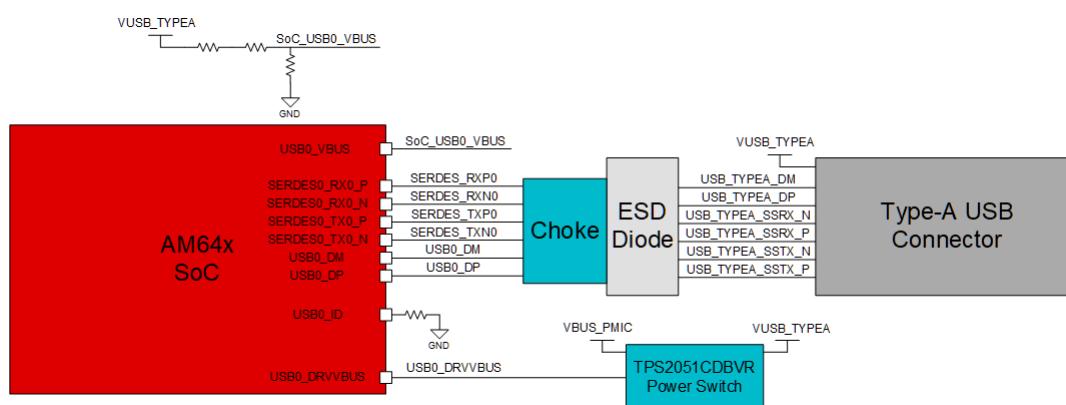

在 AM64x SKEVM 上 , 通过 USB Type-A 连接器 (692121030100) 提供 USB 3.0 主机接口 , 支持高达 5Gbps 的数据速率。来自 Type-A 连接器的超高速差分信号通过扼流圈和 ESD 保护器件连接至 SoC 的 SERDES-0 块。

Type-A 连接器的 USB2.0 线路直接与 AM64x SOC 的 USB0 端口连接。来自 SoC 的 USB0\_DRVVBUS 支持 5V 电源开关 , 以提供 VUSB\_TYPEA 电源 , 供 USB Type-A 连接器使用。

所有 USB3.0 线路 ( TX\_P 、 RX\_P 、 TX\_N 和 RX\_N ) 均应包含满足 USB 3.0 速度和电容规范的 ESD 保护器件 , 用以分散 ESD 冲击。应在 USB 数据线路上提供共模扼流圈 , 用以保护 EMI/EMC 。包含器件型号为 TPD4S012 的 ESD 保护器件 , 针对 USB2.0 DP/DM 信号分散 ESD 冲击。

图 2-23. USB 3.0 主机接口

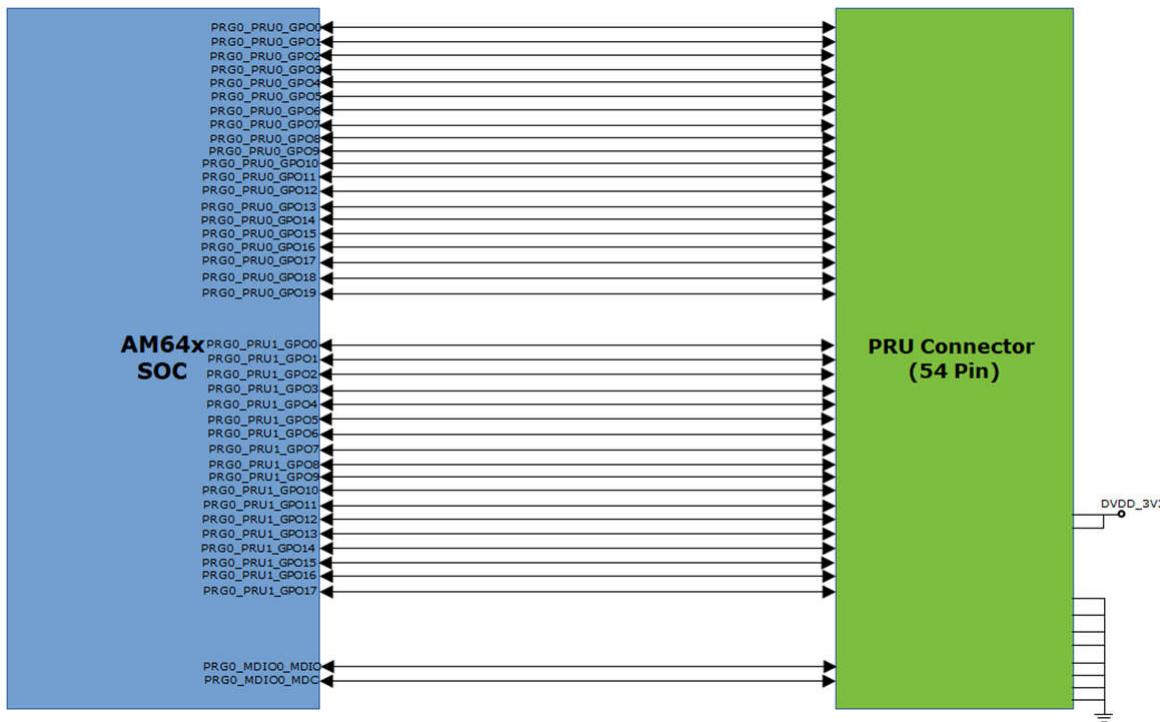

### 2.3.3.11 PRU 连接器

PRU 接头提供与 PRG0 接口的低速连接。PRG0 端口的 PRU\_ICSSG 信号 ( PRG0\_PRU0 和 PRG0\_PRU1 ) 端接在 PRU 扩展连接器上。PRU0 信号连接到 27x2 标准 0.1" 间隔 54 引脚连接器。连接器应包含 MDIO 控制信号 ( 2 引脚 ) 、 PRG0\_PRU0\_GPO [0: 19] 、 PRG0\_PRU1\_GPO [0: 17] 、 +3.3V PWR ( 2 引脚 ) 和接地基准 ( 5 引脚 ) , 以及连接至子卡的 DETECT 、 RESET 和 INT , 还有 SoC I2C0 线路 ( 2 引脚 ) 。 3.3V 时电流限值为 500 mA 。这可以通过使用负载开关 TPS22902YFPR 来实现。 SoC 可控制负载开关的启用。

从 PRU 连接器路由的信号在表 2-22 中列出。

表 2-22. PRU 连接器上 PRG0 信号的选择

| 引脚 | 网络名称            | 引脚 | 网络名称           |

|----|-----------------|----|----------------|

| 1  | VCC3V3_PRU      | 2  | DGND           |

| 3  | PRU_DETECT      | 4  | PRU_RESETz     |

| 5  | PRU_INTn        | 6  | SoC_I2C0_SCL   |

| 7  | PRG0_PRU0GPO16  | 8  | SoC_I2C0_SDA   |

| 9  | PRG0_MDIO0_MDC  | 10 | NC             |

| 11 | PRG0_MDIO0_MDIO | 12 | NC             |

| 13 | PRG0_PRU0GPO0   | 14 | PRG0_PRU0GPO1  |

| 15 | PRG0_PRU0GPO2   | 16 | PRG0_PRU0GPO3  |

| 17 | PRG0_PRU0GPO4   | 18 | PRG0_PRU0GPO5  |

| 19 | PRG0_PRU0GPO6   | 20 | PRG0_PRU0GPO7  |

| 21 | PRG0_PRU0GPO8   | 22 | PRG0_PRU0GPO9  |

| 23 | PRG0_PRU0GPO10  | 24 | PRG0_PRU0GPO11 |

| 25 | PRG0_PRU0GPO12  | 26 | PRG0_PRU0GPO13 |

| 27 | PRG0_PRU0GPO14  | 28 | PRG0_PRU0GPO15 |

| 29 | DGND            | 30 | PRG0_PRU0GPO17 |

| 31 | PRG0_PRU0GPO18  | 32 | PRG0_PRU0GPO19 |

| 33 | DGND            | 34 | DGND           |

| 35 | PRG0_PRU1GPO0   | 36 | PRG0_PRU1GPO1  |

| 37 | PRG0_PRU1GPO2   | 38 | PRG0_PRU1GPO3  |

| 39 | PRG0_PRU1GPO4   | 40 | PRG0_PRU1GPO5  |

| 41 | PRG0_PRU1GPO6   | 42 | PRG0_PRU1GPO7  |

| 43 | PRG0_PRU1GPO8   | 44 | PRG0_PRU1GPO9  |

| 45 | PRG0_PRU1GPO10  | 46 | PRG0_PRU1GPO11 |

| 47 | PRG0_PRU1GPO12  | 48 | PRG0_PRU1GPO13 |

| 49 | PRG0_PRU1GPO14  | 50 | PRG0_PRU1GPO15 |

| 51 | PRG0_PRU1GPO16  | 52 | PRG0_PRU1GPO17 |

| 53 | DGND            | 54 | VCC3V3_PRU     |

图 2-24. 54 引脚 PRU 连接器

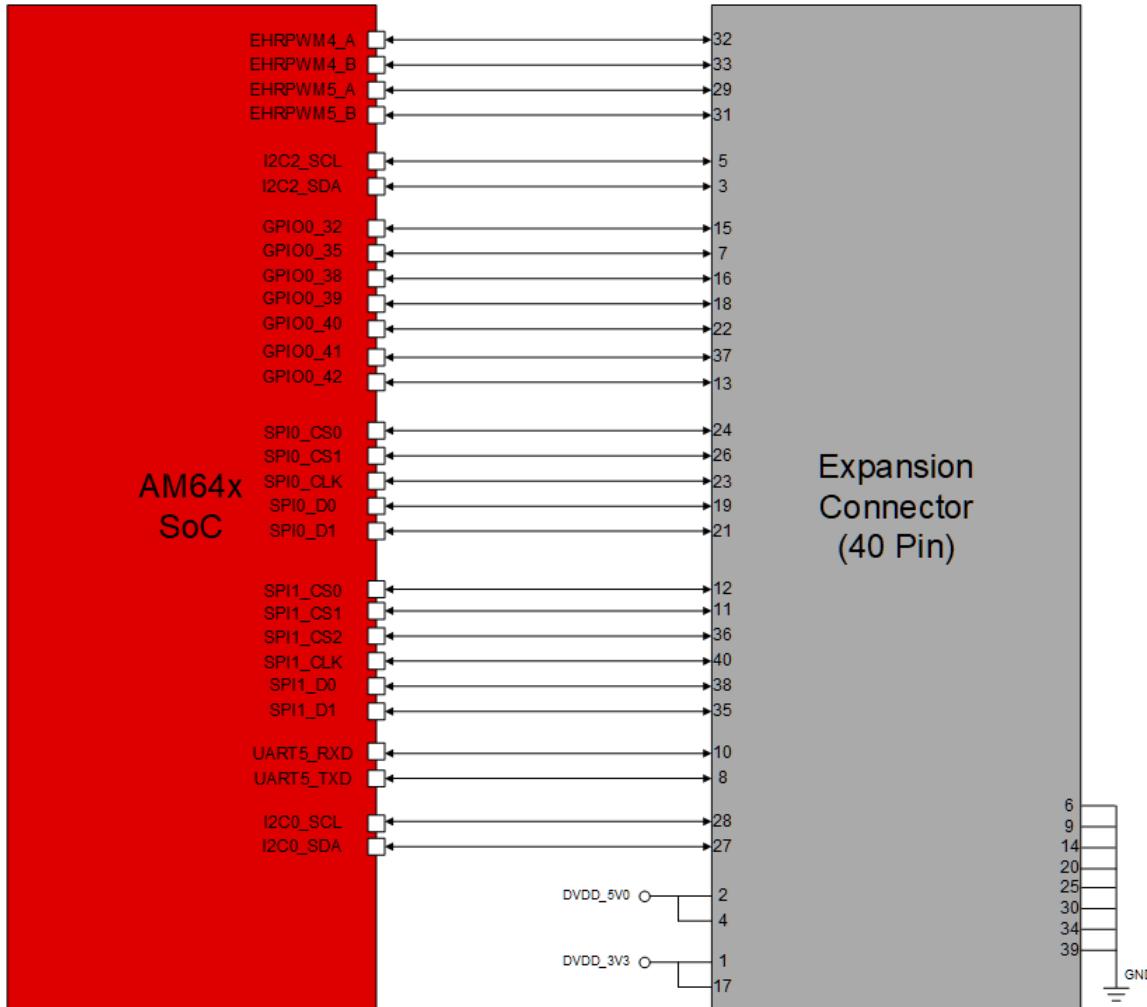

### 2.3.3.12 用户扩展连接器

此连接器与 Raspberry Pi®™ 4B 上的标准扩展连接器兼容，可与 HAT 板无缝连接。四个安装孔必须与连接器的方向一致，以便连接这些扩展板。从 SoC 连接到扩展头的信号包括：SPI (0)、SPI (1)、UART (5)、I2C (0)、I2C (2)、EHRPWM4\_A/B、EHRPWM5\_A/B、GPIO [32, 35, 38, 39, 40, 41, 42] 以及 5V、3.3V PWR 和 GND。每个 5V 和 3.3V 电源的电流分别限制为 155 mA 和 500 mA。这可以通过使用负载开关 TPS22902YFPR 来实现。IO 扩展器可控制负载开关的启用。从用户扩展连接器路由的信号已在表 2-23 中列出。

表 2-23. 40 引脚用户扩展连接器

| 引脚 | 网络名称           | 引脚 | 网络名称               |

|----|----------------|----|--------------------|

| 1  | VCC3V3_RPI     | 2  | VCC5V0_RPI         |

| 3  | RPI_I2C2_SDA   | 4  | VCC5V0_RPI         |

| 5  | RPI_I2C2_SCL   | 6  | DGND               |

| 7  | RPI_GPIO0_35   | 8  | SOC_MAIN_UART5_TXD |

| 9  | DGND           | 10 | SOC_MAIN_UART5_RXD |

| 11 | RPI_SPI1_CS1   | 12 | RPI_SPI1_CS0       |

| 13 | RPI_GPIO0_42   | 14 | DGND               |

| 15 | RPI_GPIO0_32   | 16 | RPI_GPIO0_38       |

| 17 | VCC3V3_RPI     | 18 | RPI_GPIO0_39       |

| 19 | RPI_SPI0_D0    | 20 | DGND               |

| 21 | RPI_SPI0_D1    | 22 | RPI_GPIO0_40       |

| 23 | RPI_SPI0_CLK   | 24 | RPI_SPI0_CS0       |

| 25 | DGND           | 26 | RPI_SPI0_CS1       |

| 27 | SoC_I2C0_SDA   | 28 | SoC_I2C0_SCL       |

| 29 | RPI_ETHRPWM5_A | 30 | DGND               |

| 31 | RPI_ETHRPWM5_B | 32 | RPI_ETHRPWM4_A     |

| 33 | RPI_ETHRPWM4_B | 34 | DGND               |

| 35 | RPI_SPI1_D1    | 36 | RPI_SPI1_CS2       |

表 2-23. 40 引脚用户扩展连接器 (续)

| 引脚 | 网络名称           | 引脚 | 网络名称         |

|----|----------------|----|--------------|

| 37 | RPI_GPIO0_41   | 38 | RPI_SPI1_D0  |

| 39 | RPI_HAT_DETECT | 40 | RPI_SPI1_CLK |

图 2-25. 40 引脚用户扩展连接器

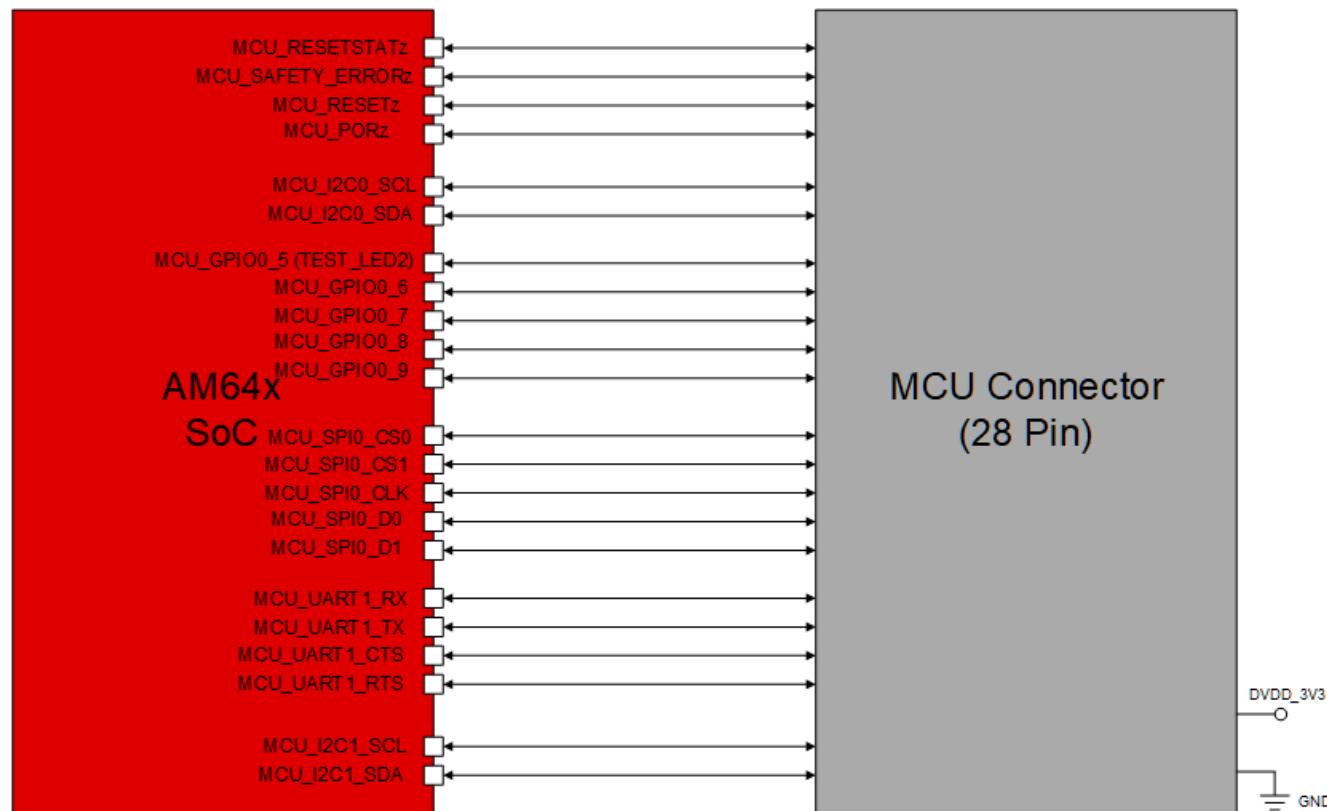

### 2.3.3.13 MCU 连接器

安全信号连接器是 14x2 标准 0.1” 间隔接头。MCU 连接器只包含连接到 MCU 的信号。18 种信号包含 MCU\_I2C0、MCU\_I2C1、MCU\_UART1 (具有流控制)、MCU\_SPI0 和 MCU\_SPI1 信号。连接器上提供的其他控制信号包括 CONN\_MCU\_RESETz、CONN\_MCU\_PORz、MCU\_RESETSTATz、MCU\_SAFETY\_ERRORz、与 MCU 和 GND 之间的 3.3V IO。MCU 连接器不包含板 ID 存储器接口。允许的电流限制是，3.3V 电源轨上为 100 mA。

表 2-24. 28 引脚 MCU 连接器

| 引脚 | 网络名称              | 引脚 | 网络名称                  |

|----|-------------------|----|-----------------------|

| 1  | VCC_3V3_SYS       | 2  | DGND                  |

| 3  | MCU_SPI0_CS1      | 4  | MCU_SPI0_D1           |

| 5  | MCU_GPIO0_8       | 6  | MCU_SPI0_D0           |

| 7  | DGND              | 8  | MCU_SPI0_CS0          |

| 9  | TEST_LED2         | 10 | MCU_GPIO0_6           |

| 11 | MCU_GPIO0_7       | 12 | MCU_UART1_CTS_3V3     |

| 13 | MCU_UART1_RX_3V3  | 14 | MCU_GPIO0_9           |

| 15 | DGND              | 16 | MCU_I2C1_SDA          |

| 17 | MCU_UART1_RTS_3V3 | 18 | MCU_SPI0_CLK          |

| 19 | MCU_UART1_TX_3V3  | 20 | DGND                  |

| 21 | MCU_I2C0_SDA      | 22 | MCU_I2C1_SCL          |

| 23 | MCU_RESETSTATz    | 24 | MCU_I2C0_SCL          |

| 25 | CONN_MCU_RESETz   | 26 | MCU_SAFETY_ERRORz_3V3 |

| 27 | DGND              | 28 | CONN_MCU_PORz         |

图 2-26. 28 引脚 MCU 连接器

### 2.3.3.14 中断

SK EVM 支持以下计时器和中断选项。

提供三种中断以对 MCU\_PORz、MCU\_RESETz 和 RESET\_REQz 进行复位。一个按钮开关连接到 MAIN 域和 MCU 域 GPIO 引脚，用于 GPIO 中断。

也可通过测试自动化接头应用热复位。

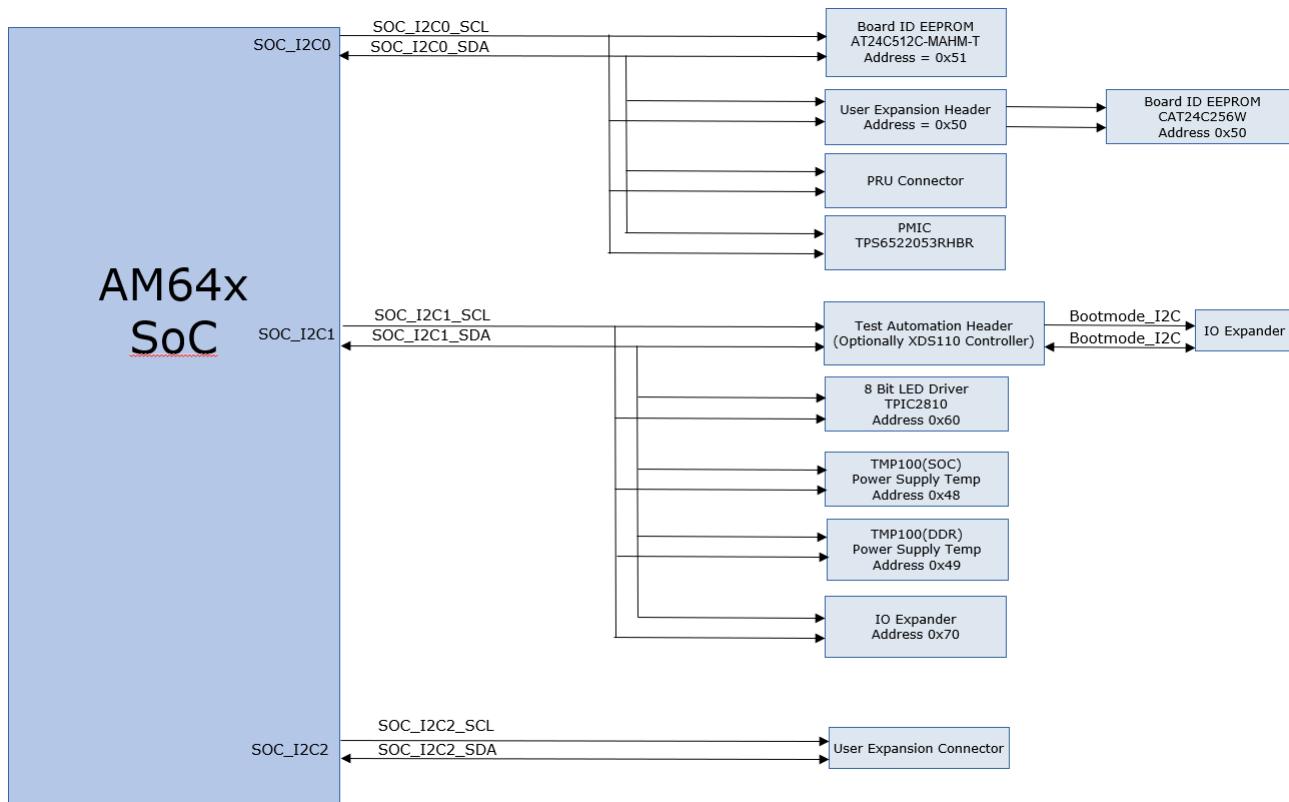

### 2.3.3.15 I2C 接口

SK EVM 板使用了三个 I2C 接口。

- SoC\_I2C0 接口：SoC I2C [0] 连接到板 ID EEPROM、一个 PMIC 和 R-Pi 扩展头。软件使用 I2C0 接口，通过板 ID 存储器器件 AT24C512C-MAHM-T 512Kb 串行 EEPROM ( 配置为响应地址 0x51 ) 识别 EVM。软件还使用 SKEVM 上的 I2C0 接口配置和控制一个 PMIC 器件。I2C0 还连接到 Ra-Pi 扩展头。

- SOC I2C (1) 接口：SoC I2C [1] 连接到 8 位 LED 驱动器、8 位 GPIO 扩展器、温度传感器和测试自动化接头。

- SOC I2C (2) 接口：将来自 SoC 的 I2C [2] 连接到 Ra-Pi 扩展头。

图 2-27 展示了 I2C 树。

图 2-27. I2C 接口

### 2.3.3.16 IO 扩展器 (GPIO)

AM64x SoC 中使用的 I/O 扩展器是一款基于 I2C 的 8 位 I/O 扩展器，用于子卡插件检测，以及为与其连接的各种外设器件生成复位和使能信号。AM64X SoC 的 I2C1 总线用于连接 I/O 扩展器，I/O 扩展器的地址为 0X70。下面是 IO 扩展器控制的信号列表。

**表 2-25. IO 扩展器引脚详细信息**

| 引脚编号 | 信号             | 方向 | 器件                  |

|------|----------------|----|---------------------|

| P0   | GPIO_CPSW2_RST | 输出 | CPSW PHY-2 ETHERNET |

| P1   | GPIO_CPSW1_RST | 输出 | CPSW PHY-1 ETHERNET |

| P2   | PRU_DETECT     | 输入 | PRU 连接器检测           |

| P3   | MMC1_SD_EN     | 输出 | SD 卡电源开关使能          |

| P4   | VPP_LDO_EN     | 输出 | SoC VPP 电压生成        |

| P5   | RPI_PS_3V3_En  | 输出 | 用户扩展连接器：3V3 电源开关使能  |

| P6   | RPI_PS_5V0_En  | 输出 | 用户扩展连接器：5V0 电源开关使能  |

| P7   | RPI_HAT_DETECT | 输入 | 用户扩展连接器：硬件附加电路板检测   |

### 3 硬件设计文件

原理图、BOM、PCB 布局、装配文件和 Gerber 文件等硬件设计文件可在下面的链接中找到。

[设计文件](#)

## 4 合规信息

### 4.1 法规遵从性

德州仪器 (TI) 特此声明，无线电设备“适用于 Sitara 处理器的 AM64x 入门套件”符合指令 2014/53/EU。

可在 [TI 网站](#) 上找到欧盟符合性声明全文。

#### 射频暴露信息

该器件已经过测试，符合适用的射频接触限制。该设备的安装和操作应始终确保与任何人都至少保持 20 厘米的距离。

#### EIRP 功率

WLAN 2.4GHz 频段中传输的最大射频功率为 19.5dBm。WLAN 5GHz 频段中传输的最大射频功率为 19.8dBm ( 约 5150MHz 至 5350MHz ) 和 18.9dBm ( 约 5470MHz 至 5725MHz ) 。

蓝牙中传输的最大射频功率为 13.9dBm，低功耗蓝牙 (BLE) 中传输的最大射频功率为 9.0dBm。

该器件仅限于在 5.15 - 5.35GHz 频段内的室内使用。以下是限制室内使用的国家/地区。

|    | AT | BE | BG | HR     | CY | CZ | DK |

|----|----|----|----|--------|----|----|----|

| EE | FI | FR | DE | EL     | HU | IE |    |

| IT | LV | LT | LU | MT     | NL | PL |    |

| PT | RO | SK | SI | ES     | SE | IS |    |

| LI | NO | CH | TR | UK(NI) |    |    |    |

#### 报废电子电气设备 (WEEE)

此符号表示，根据当地法律法规，产品或电池应当与生活垃圾分开处理。当此产品使用寿命已完结时，请将其送到地方当局指定的废物收集站。正确回收对应产品可以保护人类健康和环境。

## 5 其他信息

### 5.1 已知问题

本节介绍了每个 EVM 版本目前已知的问题，以及相应的权变措施。

**表 5-1. AM64 SK EVM 已知问题**

| 问题编号 | 问题标题                                                | 问题描述                                                                         |

|------|-----------------------------------------------------|------------------------------------------------------------------------------|

| 1    | LP8733x LDO0 和 LDO1 超出最大输出电容规范                      | 电源设计超出了推荐的电容值。                                                               |

| 2    | LP8733x 输出电压为 0.9V，超出 AM64x VDDR_CORE 最大电压规格 0.895V | 电源设计超出了 VDDR_CORE 最大电压规格。                                                    |

| 3    | WLAN 和 SDIO 器件使用                                    | 通常，MMC0 上的 WLAN 模块和 SDIO 器件需要注意布线长度，以满足 SDIO 器件的时序要求。MMC0 时序针对 eMMC 器件进行了优化。 |

| 4    | 在压力条件下的 LPDDR4 数据速率限制                               | 在 1600MT/s 的特定基准条件下可能导致错误。                                                   |

| 5    | UART 控制台上的垃圾字符                                      | 在某些电路板中，CP2105 和 XDS110 调试器的 UART 控制台中显示随机垃圾字符。                              |

| 6    | 测试断电信号悬空                                            | 测试自动化接头的 TEST POWERDOWN 信号上的 10k 上拉电阻缺失。                                     |

| 7    | uSD 卡引导无法正常工作                                       | uSD 引导功能不适用于某些品牌的 SD 卡。                                                      |

#### 5.1.1 问题 1 : LP8733x LDO0 和 LDO1 超出最大输出电容规范

受影响的 PCB 版本 : E1、E2、E3

严重程度 : 高

在入门套件中，LDO0 提供 VDDAR\_CORE ( 0.85V 内核电压域 )。4.7uF 的负载点电容器过度保守，可降低为 1uF，使 LDO0 观察到的总输出电容更符合 CLDO\_OUT 最高规格。

在入门套件中，由 LDO1 提供的 AM64x 1V8 模拟域和电容要求远远超出 LDO1 的 CLDO\_OUT 最高规格，主要原因是 VDDA\_1P8\_SERDES0 上的负载点电容器较大，为 22uF。TI 采用多管齐下的方法解决这个问题，未来将公布电容器最终推荐值。首先，LP8733xx CLDO\_OUT 最高规格过度保守，在数据表中将修改为更高的值。其次，进行了系统级仿真来评估 VDDA\_1P8\_SERDES0 上的实际去耦电容器要求。由于这项工作正在进行，TI 建议不要在生产系统中复制这种电源解决方案。

如果客户需要集成 PMIC 解决方案，德州仪器 (TI) 目前正在开发一款可满足 AM64x 处理器系列需求的 PMIC，并将在下一版本的 AM64x 入门套件中提供。

#### 5.1.2 问题 2 : LP8733x 输出电压为 0.9V，超出 AM64x VDDR\_CORE 最大电压规格 0.895V

受影响的 PCB 版本 : E1、E2、E3

严重程度 : 高

LP8733xx LDO0 输出电压为 0.9V，超出 AM64x VDDR\_CORE 最大电压规格 0.895V ( 标称理想值为 0.85V )。LDO0 没有 0.85V 的可编程选项，因此选择了 0.9V。

#### 5.1.3 问题 3 - MMC0 上的 SDIO 器件需要注意布线长度，以满足接口时序要求

受影响的 PCB 版本 : E1、E2

严重程度 : 信息

通常，MMC0 上的 WLAN 模块和 SDIO 器件需要注意布线长度，以满足 SDIO 器件的时序要求。MMC0 时序针对 eMMC 器件进行了优化。

**解决方案**：SD 可移除存储或 SDIO 器件使用 MMC1 接口，并在生产系统中使用 MMC0 上的 eMMC。

#### **5.1.4 问题 4 - 在压力条件下的 LPDDR4 数据速率限制**

受影响的 PCB 版本：E1、E2

严重程度：中

在开发流程的后期发现，在接口速率为 1600MT/s 的基准条件下，会出现 LPDDR4 错误。在扩展测试后下降到 1333MT/s，未出现错误。这仅限于 LPDDR4，不影响 DDR4 性能。仍在调查根本原因。

#### **5.1.5 问题 5 - 垃圾字符**

受影响的版本：E1、E2、E3

严重程度：信息

在某些电路板中，CP2105 和 XDS110 调试器的 UART 控制台中显示随机垃圾字符。

**解决方案**：已在修订版 E3A 中修复。

#### **5.1.6 问题 6 - 测试断电信号悬空**

受影响的版本：E1、E2、E3、E4

严重程度：中

测试自动化接头的 TEST POWERDOWN 信号上的 10k 上拉电阻缺失。

**解决方案**：已在修订版 A 中修复。

#### **5.1.7 问题 7 - uSD 引导无法正常工作**

受影响的版本：E1、E2、E3、E4

严重程度：高

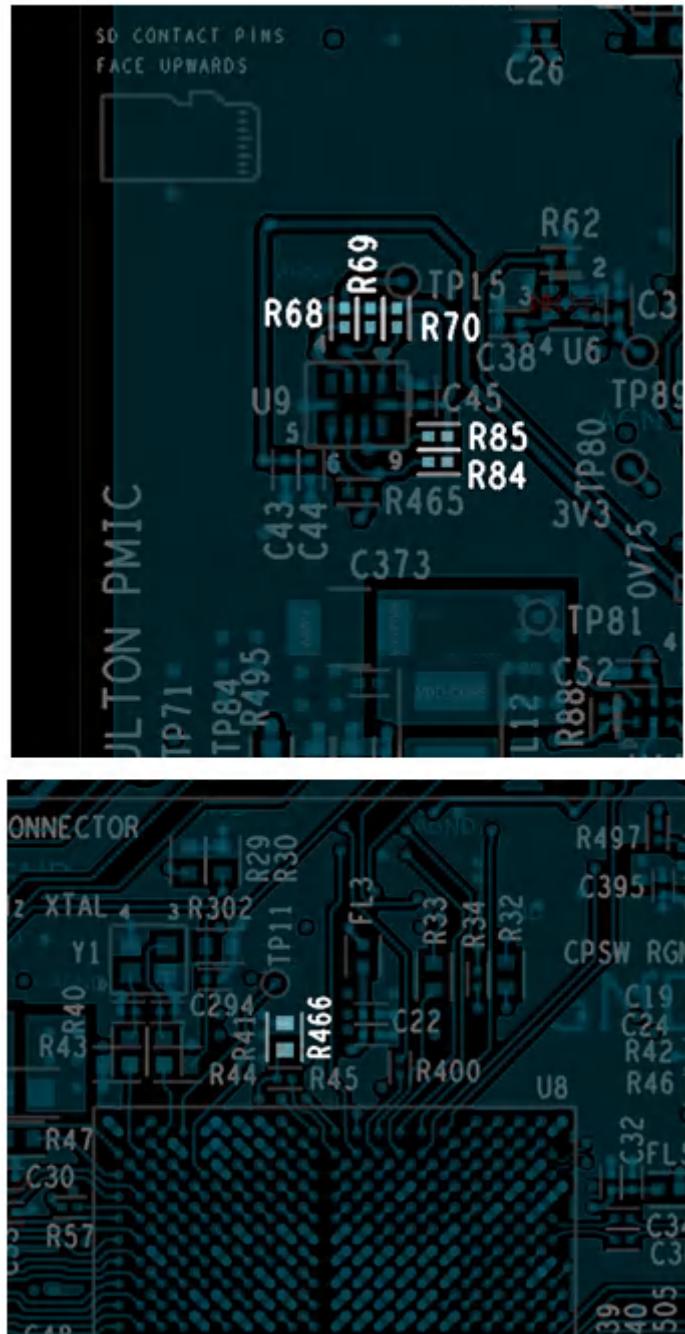

uSD 引导功能不适用于某些品牌的 SD 卡。该 EVM 未在 MMC1 接口上安装上拉电阻。这会导致某些 SD 卡出现边缘失效。

**解决方案**：在 EVM 顶部的 R68、R69、R70、R84、R85 和 R466 上安装 10K 电阻可解决该问题。

图 5-1. MMC1 原理图

图 5-2. MMC1 布局

商标

Sitara™ and Code Composer Studio™ are trademarks of Texas Instruments.

Wi-Fi™ is a trademark of Wi-Fi Alliance.

Rasberry Pi™ is a trademark of Raspberry Pi Ltd.

Linux® is a registered trademark of Linus Torvalds in the U.S. and other countries.

Arm® and are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

Cortex® is a registered trademark of tm.

蓝牙® is a registered trademark of Bluetooth SIG, Inc.

所有商标均为其各自所有者的财产。

术语 HDMI、HDMI 高清多媒体接口、HDMI 商业外观和 HDMI 标识是 HDMI Licensing Administrator, Inc. 的商标或注册商标。

## 6 修订历史记录

注：以前版本的页码可能与当前版本的页码不同

### Changes from OCTOBER 31, 2023 to DECEMBER 31, 2025 (from Revision B (October 2023) to Revision C (December 2025))

|                                                    | Page |

|----------------------------------------------------|------|

| • 添加了 HDMI 商标信息。 .....                             | 1    |

| • 更新了 <a href="#">已知问题汇总 ID 4</a> 受影响的版本并修复。 ..... | 5    |

| • 从受影响的版本中删除修订版 A。 .....                           | 46   |

## STANDARD TERMS FOR EVALUATION MODULES

1. *Delivery:* TI delivers TI evaluation boards, kits, or modules, including any accompanying demonstration software, components, and/or documentation which may be provided together or separately (collectively, an "EVM" or "EVMs") to the User ("User") in accordance with the terms set forth herein. User's acceptance of the EVM is expressly subject to the following terms.

- 1.1 EVMs are intended solely for product or software developers for use in a research and development setting to facilitate feasibility evaluation, experimentation, or scientific analysis of TI semiconductors products. EVMs have no direct function and are not finished products. EVMs shall not be directly or indirectly assembled as a part or subassembly in any finished product. For clarification, any software or software tools provided with the EVM ("Software") shall not be subject to the terms and conditions set forth herein but rather shall be subject to the applicable terms that accompany such Software

- 1.2 EVMs are not intended for consumer or household use. EVMs may not be sold, sublicensed, leased, rented, loaned, assigned, or otherwise distributed for commercial purposes by Users, in whole or in part, or used in any finished product or production system.

- 2 *Limited Warranty and Related Remedies/Disclaimers:*

- 2.1 These terms do not apply to Software. The warranty, if any, for Software is covered in the applicable Software License Agreement.

- 2.2 TI warrants that the TI EVM will conform to TI's published specifications for ninety (90) days after the date TI delivers such EVM to User. Notwithstanding the foregoing, TI shall not be liable for a nonconforming EVM if (a) the nonconformity was caused by neglect, misuse or mistreatment by an entity other than TI, including improper installation or testing, or for any EVMs that have been altered or modified in any way by an entity other than TI, (b) the nonconformity resulted from User's design, specifications or instructions for such EVMs or improper system design, or (c) User has not paid on time. Testing and other quality control techniques are used to the extent TI deems necessary. TI does not test all parameters of each EVM. User's claims against TI under this Section 2 are void if User fails to notify TI of any apparent defects in the EVMs within ten (10) business days after delivery, or of any hidden defects with ten (10) business days after the defect has been detected.

- 2.3 TI's sole liability shall be at its option to repair or replace EVMs that fail to conform to the warranty set forth above, or credit User's account for such EVM. TI's liability under this warranty shall be limited to EVMs that are returned during the warranty period to the address designated by TI and that are determined by TI not to conform to such warranty. If TI elects to repair or replace such EVM, TI shall have a reasonable time to repair such EVM or provide replacements. Repaired EVMs shall be warranted for the remainder of the original warranty period. Replaced EVMs shall be warranted for a new full ninety (90) day warranty period.

### **WARNING**

**Evaluation Kits are intended solely for use by technically qualified, professional electronics experts who are familiar with the dangers and application risks associated with handling electrical mechanical components, systems, and subsystems.**

**User shall operate the Evaluation Kit within TI's recommended guidelines and any applicable legal or environmental requirements as well as reasonable and customary safeguards. Failure to set up and/or operate the Evaluation Kit within TI's recommended guidelines may result in personal injury or death or property damage. Proper set up entails following TI's instructions for electrical ratings of interface circuits such as input, output and electrical loads.**

**NOTE:**

EXPOSURE TO ELECTROSTATIC DISCHARGE (ESD) MAY CAUSE DEGRADATION OR FAILURE OF THE EVALUATION KIT; TI RECOMMENDS STORAGE OF THE EVALUATION KIT IN A PROTECTIVE ESD BAG.

---

### 3 Regulatory Notices:

#### 3.1 United States

##### 3.1.1 Notice applicable to EVMs not FCC-Approved:

**FCC NOTICE:** This kit is designed to allow product developers to evaluate electronic components, circuitry, or software associated with the kit to determine whether to incorporate such items in a finished product and software developers to write software applications for use with the end product. This kit is not a finished product and when assembled may not be resold or otherwise marketed unless all required FCC equipment authorizations are first obtained. Operation is subject to the condition that this product not cause harmful interference to licensed radio stations and that this product accept harmful interference. Unless the assembled kit is designed to operate under part 15, part 18 or part 95 of this chapter, the operator of the kit must operate under the authority of an FCC license holder or must secure an experimental authorization under part 5 of this chapter.

##### 3.1.2 For EVMs annotated as FCC – FEDERAL COMMUNICATIONS COMMISSION Part 15 Compliant:

#### CAUTION

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

#### FCC Interference Statement for Class A EVM devices

*NOTE: This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.*

#### FCC Interference Statement for Class B EVM devices

*NOTE: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:*

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

#### 3.2 Canada

##### 3.2.1 For EVMs issued with an Industry Canada Certificate of Conformance to RSS-210 or RSS-247

#### Concerning EVMs Including Radio Transmitters:

This device complies with Industry Canada license-exempt RSSs. Operation is subject to the following two conditions:

(1) this device may not cause interference, and (2) this device must accept any interference, including interference that may cause undesired operation of the device.

#### Concernant les EVMs avec appareils radio:

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes: (1) l'appareil ne doit pas produire de brouillage, et (2) l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

#### Concerning EVMs Including Detachable Antennas:

Under Industry Canada regulations, this radio transmitter may only operate using an antenna of a type and maximum (or lesser) gain approved for the transmitter by Industry Canada. To reduce potential radio interference to other users, the antenna type and its gain should be so chosen that the equivalent isotropically radiated power (e.i.r.p.) is not more than that necessary for successful communication. This radio transmitter has been approved by Industry Canada to operate with the antenna types listed in the user guide with the maximum permissible gain and required antenna impedance for each antenna type indicated. Antenna types not included in this list, having a gain greater than the maximum gain indicated for that type, are strictly prohibited for use with this device.

#### Concernant les EVMs avec antennes détachables

Conformément à la réglementation d'Industrie Canada, le présent émetteur radio peut fonctionner avec une antenne d'un type et d'un gain maximal (ou inférieur) approuvé pour l'émetteur par Industrie Canada. Dans le but de réduire les risques de brouillage radioélectrique à l'intention des autres utilisateurs, il faut choisir le type d'antenne et son gain de sorte que la puissance isotope rayonnée équivalente (p.i.r.e.) ne dépasse pas l'intensité nécessaire à l'établissement d'une communication satisfaisante. Le présent émetteur radio a été approuvé par Industrie Canada pour fonctionner avec les types d'antenne énumérés dans le manuel d'usage et ayant un gain admissible maximal et l'impédance requise pour chaque type d'antenne. Les types d'antenne non inclus dans cette liste, ou dont le gain est supérieur au gain maximal indiqué, sont strictement interdits pour l'exploitation de l'émetteur

#### 3.3 Japan

3.3.1 *Notice for EVMs delivered in Japan:* Please see [http://www.tij.co.jp/lsts/ti\\_ja/general/eStore/notice\\_01.page](http://www.tij.co.jp/lsts/ti_ja/general/eStore/notice_01.page) 日本国内に輸入される評価用キット、ボードについては、次のところをご覧ください。

<https://www.ti.com/ja-jp/legal/notice-for-evaluation-kits-delivered-in-japan.html>

3.3.2 *Notice for Users of EVMs Considered "Radio Frequency Products" in Japan:* EVMs entering Japan may not be certified by TI as conforming to Technical Regulations of Radio Law of Japan.

If User uses EVMs in Japan, not certified to Technical Regulations of Radio Law of Japan, User is required to follow the instructions set forth by Radio Law of Japan, which includes, but is not limited to, the instructions below with respect to EVMs (which for the avoidance of doubt are stated strictly for convenience and should be verified by User):

1. Use EVMs in a shielded room or any other test facility as defined in the notification #173 issued by Ministry of Internal Affairs and Communications on March 28, 2006, based on Sub-section 1.1 of Article 6 of the Ministry's Rule for Enforcement of Radio Law of Japan,

2. Use EVMs only after User obtains the license of Test Radio Station as provided in Radio Law of Japan with respect to EVMs, or

3. Use of EVMs only after User obtains the Technical Regulations Conformity Certification as provided in Radio Law of Japan with respect to EVMs. Also, do not transfer EVMs, unless User gives the same notice above to the transferee. Please note that if User does not follow the instructions above, User will be subject to penalties of Radio Law of Japan.

【無線電波を送信する製品の開発キットをお使いになる際の注意事項】開発キットの中には技術基準適合証明を受けていないものがあります。技術適合証明を受けていないものご使用に際しては、電波法遵守のため、以下のいずれかの措置を取っていただく必要がありますのでご注意ください。

1. 電波法施行規則第6条第1項第1号に基づく平成18年3月28日総務省告示第173号で定められた電波暗室等の試験設備でご使用いただく。

2. 実験局の免許を取得後ご使用いただく。

3. 技術基準適合証明を取得後ご使用いただく。

なお、本製品は、上記の「ご使用にあたっての注意」を譲渡先、移転先に通知しない限り、譲渡、移転できないものとします。

上記を遵守頂けない場合は、電波法の罰則が適用される可能性があることをご留意ください。日本テキサス・インスツルメンツ株式会社

東京都新宿区西新宿 6 丁目 24 番 1 号

西新宿三井ビル

3.3.3 *Notice for EVMs for Power Line Communication:* Please see [http://www.tij.co.jp/lsts/ti\\_ja/general/eStore/notice\\_02.page](http://www.tij.co.jp/lsts/ti_ja/general/eStore/notice_02.page)

電力線搬送波通信についての開発キットをお使いになる際の注意事項については、次のところをご覧ください。<https://www.ti.com/ja-jp/legal/notice-for-evaluation-kits-for-power-line-communication.html>

#### 3.4 European Union

3.4.1 *For EVMs subject to EU Directive 2014/30/EU (Electromagnetic Compatibility Directive):*

This is a class A product intended for use in environments other than domestic environments that are connected to a low-voltage power-supply network that supplies buildings used for domestic purposes. In a domestic environment this product may cause radio interference in which case the user may be required to take adequate measures.

---

4 *EVM Use Restrictions and Warnings:*

- 4.1 EVMS ARE NOT FOR USE IN FUNCTIONAL SAFETY AND/OR SAFETY CRITICAL EVALUATIONS, INCLUDING BUT NOT LIMITED TO EVALUATIONS OF LIFE SUPPORT APPLICATIONS.

- 4.2 User must read and apply the user guide and other available documentation provided by TI regarding the EVM prior to handling or using the EVM, including without limitation any warning or restriction notices. The notices contain important safety information related to, for example, temperatures and voltages.

- 4.3 *Safety-Related Warnings and Restrictions:*

- 4.3.1 User shall operate the EVM within TI's recommended specifications and environmental considerations stated in the user guide, other available documentation provided by TI, and any other applicable requirements and employ reasonable and customary safeguards. Exceeding the specified performance ratings and specifications (including but not limited to input and output voltage, current, power, and environmental ranges) for the EVM may cause personal injury or death, or property damage. If there are questions concerning performance ratings and specifications, User should contact a TI field representative prior to connecting interface electronics including input power and intended loads. Any loads applied outside of the specified output range may also result in unintended and/or inaccurate operation and/or possible permanent damage to the EVM and/or interface electronics. Please consult the EVM user guide prior to connecting any load to the EVM output. If there is uncertainty as to the load specification, please contact a TI field representative. During normal operation, even with the inputs and outputs kept within the specified allowable ranges, some circuit components may have elevated case temperatures. These components include but are not limited to linear regulators, switching transistors, pass transistors, current sense resistors, and heat sinks, which can be identified using the information in the associated documentation. When working with the EVM, please be aware that the EVM may become very warm.

- 4.3.2 EVMs are intended solely for use by technically qualified, professional electronics experts who are familiar with the dangers and application risks associated with handling electrical mechanical components, systems, and subsystems. User assumes all responsibility and liability for proper and safe handling and use of the EVM by User or its employees, affiliates, contractors or designees. User assumes all responsibility and liability to ensure that any interfaces (electronic and/or mechanical) between the EVM and any human body are designed with suitable isolation and means to safely limit accessible leakage currents to minimize the risk of electrical shock hazard. User assumes all responsibility and liability for any improper or unsafe handling or use of the EVM by User or its employees, affiliates, contractors or designees.

- 4.4 User assumes all responsibility and liability to determine whether the EVM is subject to any applicable international, federal, state, or local laws and regulations related to User's handling and use of the EVM and, if applicable, User assumes all responsibility and liability for compliance in all respects with such laws and regulations. User assumes all responsibility and liability for proper disposal and recycling of the EVM consistent with all applicable international, federal, state, and local requirements.

5. *Accuracy of Information:* To the extent TI provides information on the availability and function of EVMs, TI attempts to be as accurate as possible. However, TI does not warrant the accuracy of EVM descriptions, EVM availability or other information on its websites as accurate, complete, reliable, current, or error-free.

6. *Disclaimers:*

- 6.1 EXCEPT AS SET FORTH ABOVE, EVMS AND ANY MATERIALS PROVIDED WITH THE EVM (INCLUDING, BUT NOT LIMITED TO, REFERENCE DESIGNS AND THE DESIGN OF THE EVM ITSELF) ARE PROVIDED "AS IS" AND "WITH ALL FAULTS." TI DISCLAIMS ALL OTHER WARRANTIES, EXPRESS OR IMPLIED, REGARDING SUCH ITEMS, INCLUDING BUT NOT LIMITED TO ANY EPIDEMIC FAILURE WARRANTY OR IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF ANY THIRD PARTY PATENTS, COPYRIGHTS, TRADE SECRETS OR OTHER INTELLECTUAL PROPERTY RIGHTS.

- 6.2 EXCEPT FOR THE LIMITED RIGHT TO USE THE EVM SET FORTH HEREIN, NOTHING IN THESE TERMS SHALL BE CONSTRUED AS GRANTING OR CONFERRING ANY RIGHTS BY LICENSE, PATENT, OR ANY OTHER INDUSTRIAL OR INTELLECTUAL PROPERTY RIGHT OF TI, ITS SUPPLIERS/LICENSENSORS OR ANY OTHER THIRD PARTY, TO USE THE EVM IN ANY FINISHED END-USER OR READY-TO-USE FINAL PRODUCT, OR FOR ANY INVENTION, DISCOVERY OR IMPROVEMENT, REGARDLESS OF WHEN MADE, CONCEIVED OR ACQUIRED.

7. *USER'S INDEMNITY OBLIGATIONS AND REPRESENTATIONS.* USER WILL DEFEND, INDEMNIFY AND HOLD TI, ITS LICENSORS AND THEIR REPRESENTATIVES HARMLESS FROM AND AGAINST ANY AND ALL CLAIMS, DAMAGES, LOSSES, EXPENSES, COSTS AND LIABILITIES (COLLECTIVELY, "CLAIMS") ARISING OUT OF OR IN CONNECTION WITH ANY HANDLING OR USE OF THE EVM THAT IS NOT IN ACCORDANCE WITH THESE TERMS. THIS OBLIGATION SHALL APPLY WHETHER CLAIMS ARISE UNDER STATUTE, REGULATION, OR THE LAW OF TORT, CONTRACT OR ANY OTHER LEGAL THEORY, AND EVEN IF THE EVM FAILS TO PERFORM AS DESCRIBED OR EXPECTED.

8. *Limitations on Damages and Liability:*

- 8.1 *General Limitations.* IN NO EVENT SHALL TI BE LIABLE FOR ANY SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL, OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF THESE TERMS OR THE USE OF THE EVMS, REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. EXCLUDED DAMAGES INCLUDE, BUT ARE NOT LIMITED TO, COST OF REMOVAL OR REINSTALLATION, ANCILLARY COSTS TO THE PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES, RETESTING, OUTSIDE COMPUTER TIME, LABOR COSTS, LOSS OF GOODWILL, LOSS OF PROFITS, LOSS OF SAVINGS, LOSS OF USE, LOSS OF DATA, OR BUSINESS INTERRUPTION. NO CLAIM, SUIT OR ACTION SHALL BE BROUGHT AGAINST TI MORE THAN TWELVE (12) MONTHS AFTER THE EVENT THAT GAVE RISE TO THE CAUSE OF ACTION HAS OCCURRED.

- 8.2 *Specific Limitations.* IN NO EVENT SHALL TI'S AGGREGATE LIABILITY FROM ANY USE OF AN EVM PROVIDED HEREUNDER, INCLUDING FROM ANY WARRANTY, INDEMNITY OR OTHER OBLIGATION ARISING OUT OF OR IN CONNECTION WITH THESE TERMS, EXCEED THE TOTAL AMOUNT PAID TO TI BY USER FOR THE PARTICULAR EVM(S) AT ISSUE DURING THE PRIOR TWELVE (12) MONTHS WITH RESPECT TO WHICH LOSSES OR DAMAGES ARE CLAIMED. THE EXISTENCE OF MORE THAN ONE CLAIM SHALL NOT ENLARGE OR EXTEND THIS LIMIT.

9. *Return Policy.* Except as otherwise provided, TI does not offer any refunds, returns, or exchanges. Furthermore, no return of EVM(s) will be accepted if the package has been opened and no return of the EVM(s) will be accepted if they are damaged or otherwise not in a resalable condition. If User feels it has been incorrectly charged for the EVM(s) it ordered or that delivery violates the applicable order, User should contact TI. All refunds will be made in full within thirty (30) working days from the return of the components(s), excluding any postage or packaging costs.

10. *Governing Law:* These terms and conditions shall be governed by and interpreted in accordance with the laws of the State of Texas, without reference to conflict-of-laws principles. User agrees that non-exclusive jurisdiction for any dispute arising out of or relating to these terms and conditions lies within courts located in the State of Texas and consents to venue in Dallas County, Texas. Notwithstanding the foregoing, any judgment may be enforced in any United States or foreign court, and TI may seek injunctive relief in any United States or foreign court.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2023, Texas Instruments Incorporated

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2026，德州仪器 (TI) 公司

最后更新日期：2025 年 10 月