ZHCSDR3C April 2015 – October 2017 LM43603-Q1

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Fixed Frequency Peak Current Mode Controlled Step-Down Regulator

- 7.3.2 Light Load Operation

- 7.3.3 Adjustable Output Voltage

- 7.3.4 Enable (EN)

- 7.3.5 VCC, UVLO, and BIAS

- 7.3.6 Soft-Start and Voltage Tracking (SS/TRK)

- 7.3.7 Switching Frequency (RT) and Synchronization (SYNC)

- 7.3.8 Minimum ON Time, Minimum OFF Time and Frequency Foldback at Dropout Conditions

- 7.3.9 Internal Compensation and CFF

- 7.3.10 Bootstrap Voltage (BOOT)

- 7.3.11 Power Good (PGOOD)

- 7.3.12 Overcurrent and Short-Circuit Protection

- 7.3.13 Thermal Shutdown

- 7.4 Device Functional Modes

-

8 Applications and Implementation

- 8.1 Application Information

- 8.2

Typical Applications

- 8.2.1 Design Requirements

- 8.2.2

Detailed Design Procedure

- 8.2.2.1 Custom Design With WEBENCH® Tools

- 8.2.2.2 Output Voltage Setpoint

- 8.2.2.3 Switching Frequency

- 8.2.2.4 Input Capacitors

- 8.2.2.5 Inductor Selection

- 8.2.2.6 Output Capacitor Selection

- 8.2.2.7 Feed-Forward Capacitor

- 8.2.2.8 Bootstrap Capacitors

- 8.2.2.9 VCC Capacitor

- 8.2.2.10 BIAS Capacitors

- 8.2.2.11 Soft-Start Capacitors

- 8.2.2.12 Undervoltage Lockout Setpoint

- 8.2.2.13 PGOOD

- 8.2.3 Application Performance Curves

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械、封装和可订购信息

1 特性

- 符合汽车应用要求 认证

- 具有符合 AEC-Q100 标准的下列结果:

- 器件温度 1 级:–40°C 至 +125°C 的工作结温范围

- 27µA 稳压静态电流

- 可在轻负载条件下实现高效率(DCM 和 PFM)

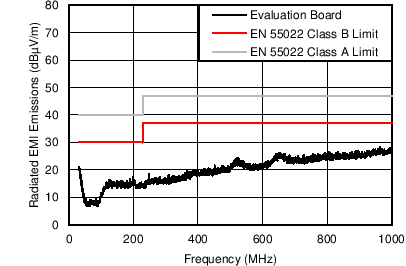

- 符合 EN55022/CISPR 22 电磁干扰 (EMI) 标准

- 集成同步整流

- 可调频率范围:200kHz 至 2.2MHz(默认值为 500kHz)

- 与外部时钟频率同步

- 内部补偿

- 与陶瓷、固态电解、钽和铝电容器等大多数组合搭配使用时均可保持稳定

- 电源正常标志

- 软启动至预偏置负载

- 内部软启动:4.1ms

- 可由外部电容器延长的软启动时间

- 输出电压跟踪功能

- 程序系统欠压闭锁 (UVLO) 精确使能

- 具有断续模式的输出短路保护

- 过热关断保护

- 使用 LM43603-Q1 并借助 WEBENCH® 电源设计器创建定制设计方案

3 说明

LM43603-Q1 稳压器是一款易于使用的同步降压直流/直流转换器,能够驱动高达 3A 的负载电流,输入电压范围为 3.5V 至 36V(最大绝对值 42V)。LM43603-Q1 以极小的解决方案尺寸提供优异的效率、输出精度和压降电压。扩展系列产品能够以引脚到引脚兼容封装提供 0.5A、1A 和 2A 负载电流选项。采用峰值电流模式控制来实现简单控制环路补偿和逐周期电流限制。可选 功能 包括可编程开关频率、同步、电源正常标志、精确使能、内部软启动、可扩展软启动和跟踪,可为各种 应用提供灵活且易于使用的平台应用中对通道损失进行线性补偿。轻载时的断续传导和自动频率调制可提升轻载效率。此系列只需要很少的外部组件,并且引脚排列可实现简单、最优的印刷电路板 (PCB) 布局布线。保护功能 采用了 包括热关断、VCC 欠压锁定、逐周期电流限制和输出短路保护。LM43603-Q1 器件采用 HTSSOP (PWP) 16 引脚引线式封装 (6.6mm × 5.1mm × 1.2mm)。LM43603A-Q1 版本针对 PFM 操作进行优化,推荐用于新设计。该器件与 LM4360x 和 LM4600x 系列实现了引脚对引脚兼容。

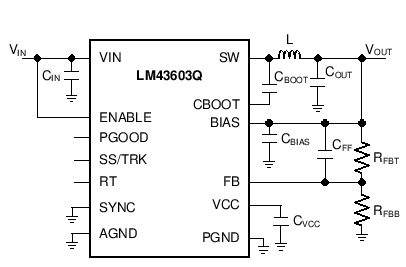

简化原理图

辐射发射图

12 VIN 到 3.3 VOUT,FS = 500kHz,IOUT = 3A