ZHCAAD9A April 2020 – June 2021 LM3668 , TPS63000 , TPS63000-Q1 , TPS63001 , TPS63002 , TPS63010 , TPS63011 , TPS63020 , TPS63020-Q1 , TPS63021 , TPS63024 , TPS630241 , TPS630242 , TPS630250 , TPS630251 , TPS630252 , TPS63027 , TPS63030 , TPS63031 , TPS63036 , TPS63050 , TPS63051 , TPS63060 , TPS63061 , TPS63070 , TPS63802 , TPS63805 , TPS63806 , TPS63810 , TPS63811 , TPS63900 , TPS63901

3 器件优化

图 3-1 所示为 TPS63070 典型应用的电路。本应用手册中使用了此电路。初始 PCB 布局概念是德州仪器 (TI) 针对已构建 PCB 建议的 Webench 布局。

请注意,Webench 布局并未针对卓越 EMI 性能进行优化,而是针对放置不同尺寸组件的能力进行了优化。

图 3-1 TPS63070 的典型应用

图 3-1 TPS63070 的典型应用Webench PCB 布局是一种双层方法。除电感器端口之外的所有平面都保留在顶层。底层由电感器端子及输入和输出平面组成。可对 Webench 布局进行优化以提高辐射性能,如下所示:

- 最大限度地减小热平面:对应于输入、输出、电感器和其他组件连接的网络的面积应在设计允许的范围内尽可能小。最大面积应分配给接地层。

- 将布线完全保留在一个层上:尽可能避免在布线中间的层之间交叉。此过程减少了过孔数量并降低了整体平面电感。

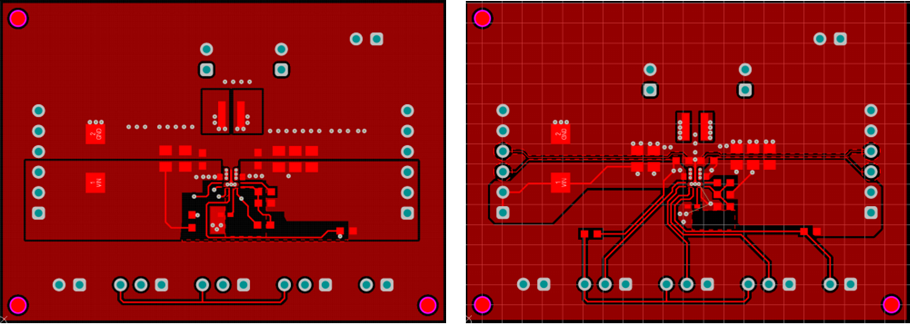

图 3-2 所示为 Webench 布局(左侧)和经过优化的布局(右侧)的顶层。它突出显示了极小的平面和缺乏串扰。

图 3-2 Webench 布局(左侧)和经过优化的布局(右侧)的顶层

图 3-2 Webench 布局(左侧)和经过优化的布局(右侧)的顶层图 3-3 所示为上述改进的优势。这两种测量方法之间的差异非常明显并且很容易看出。从数字角度而言,这种差异在严重受影响的频率下会高达 10dB。

图 3-3 Webench 布局和经过优化的布局的辐射 EMI 响应

图 3-3 Webench 布局和经过优化的布局的辐射 EMI 响应