SNAU260A October 2020 – February 2021 LMK5C33216

ADVANCE INFORMATION

- Trademarks

- 1Introduction

- 2EVM Quick Start

- 3EVM Configuration

-

4EVM Schematics

- 4.1 Power Supply Schematic

- 4.2 Power Distribution Schematic

- 4.3 LMK5C33216 and Input Reference Inputs IN0 to IN1 Schematic

- 4.4 Clock Outputs OUT0 to OUT3 Schematic

- 4.5 Clock Outputs OUT4 to OUT9 Schematic

- 4.6 Clock Outputs OUT10 to OUT15 Schematic

- 4.7 XO Schematic

- 4.8 Logic I/O Interfaces Schematic

- 4.9 USB2ANY Schematic

- 5EVM Bill of Materials

- 6Appendix A - TICS Pro LMK5C33216 Software

- 7Revision History

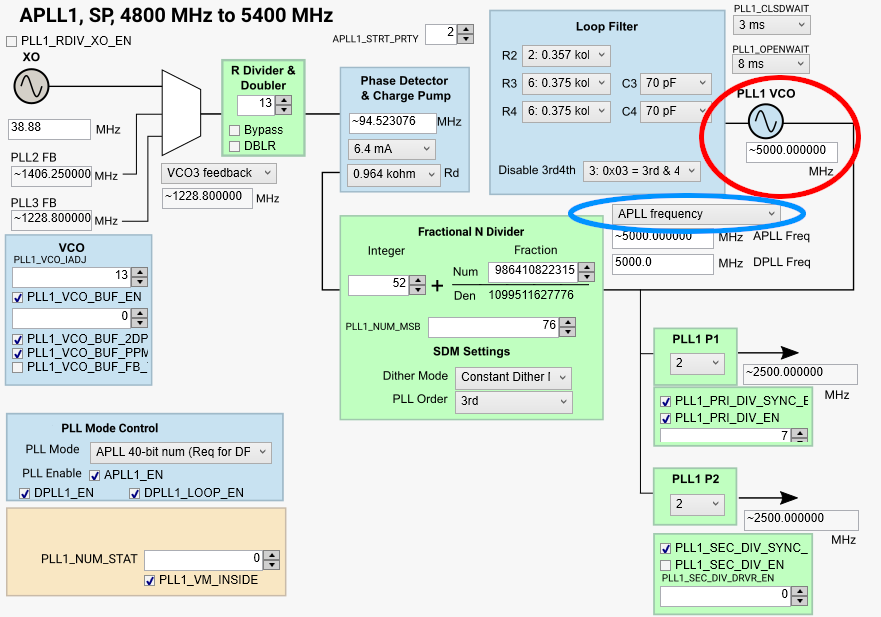

6.4 Using APLL1, 2, and 3 Pages

The APLL pages can be used to see detailed information on APLL behavior including the output dividers. It is possible to select between APLL frequency and DPLL frequency from this page to cascade to the output frequency boxes. By leaving APLL frequency (as shown in blue circle) selected, it is possible to type a VCO frequency into the PLL1 VCO frequency box (as shown in red circle) to have the fractional N value re-calculated.

When the DPLL is not used, the APLLs support an APLL only mode with a programmable 24-bit denominator. Support for this mode is currently not implemented in the TICS Pro software.

Figure 6-13 APLL1 Page

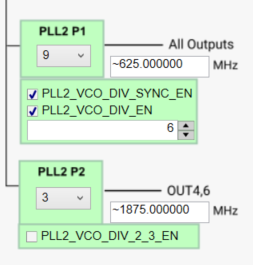

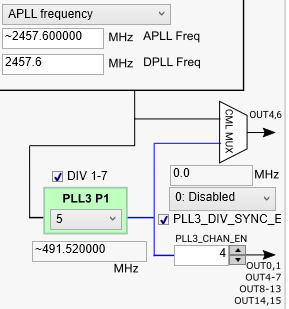

Figure 6-13 APLL1 PageFigure 6-14 below shows the post dividers for PLL2 which includes PLL2 P2 for high speed open collector CML output, and below right shows the post dividers for PLL3 which includes PLL3 P1 with a CML MUX for bypassing BAW frequency directly to CML outputs or to be used with the PLL3 P1 divider for other outputs.

Figure 6-14 PLL2 Post Divider

Figure 6-14 PLL2 Post Divider Figure 6-15 PLL3 Dividers

Figure 6-15 PLL3 Dividers