# 电力线通信模拟前端

查询样片: [AFE032](#)

## 特性

- 支持:

- CENELEC A, B, C, D 频带**

- ARIB STD-T84, FCC**

- FSK, SFSK 和 NB-OFDM**

- 符合:

- EN50065-1, -2, -3, -7**

- 美国联邦通信委员会 (FCC), 第 15 部分

- ARIB STD-T84**

- 标准:

- G3, PRIME, P1901.2, ITU-G.hnem**

- 可编程 Tx 低通滤波器和 Rx 带通滤波器

- 具有热保护和过流保护的集成型电力线驱动器

- 低功耗:

- 50mW** (接收器模式)

- 接收敏感度: **10 $\mu$ V<sub>RMS</sub>** (典型值)

- 四线制 **SPI™** 接口

- 3 个集成型零交叉检测器

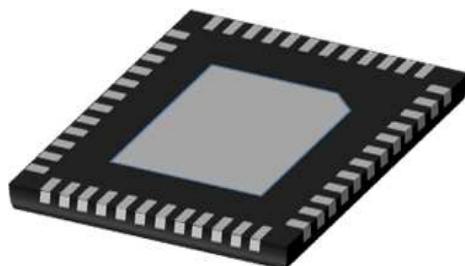

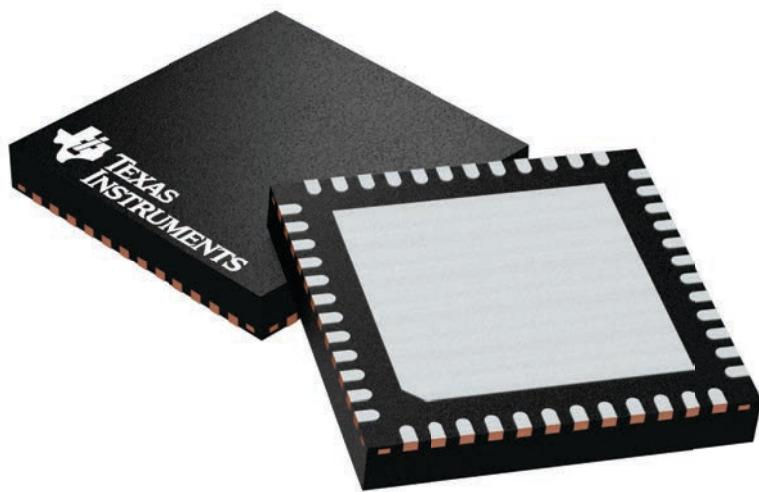

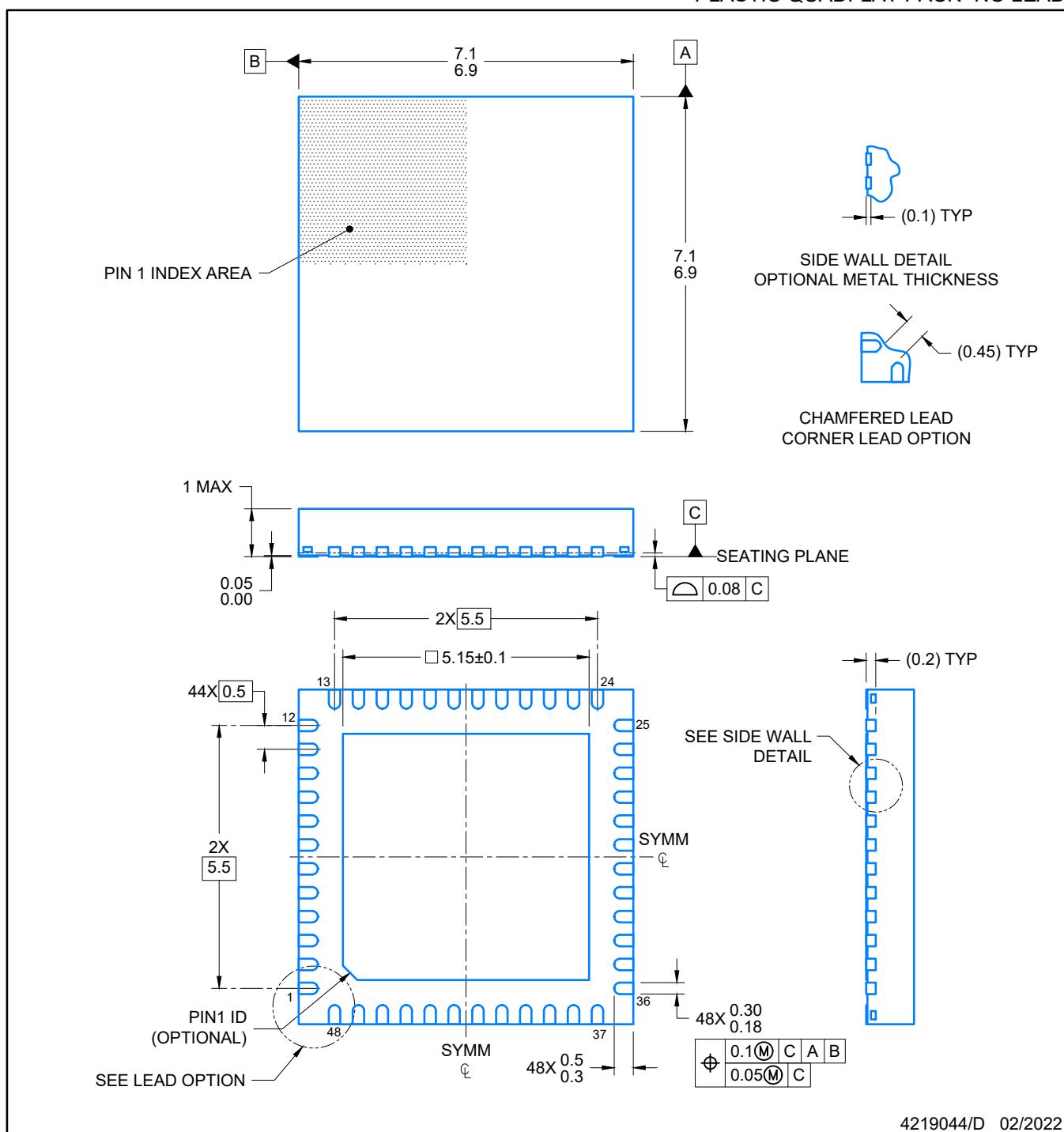

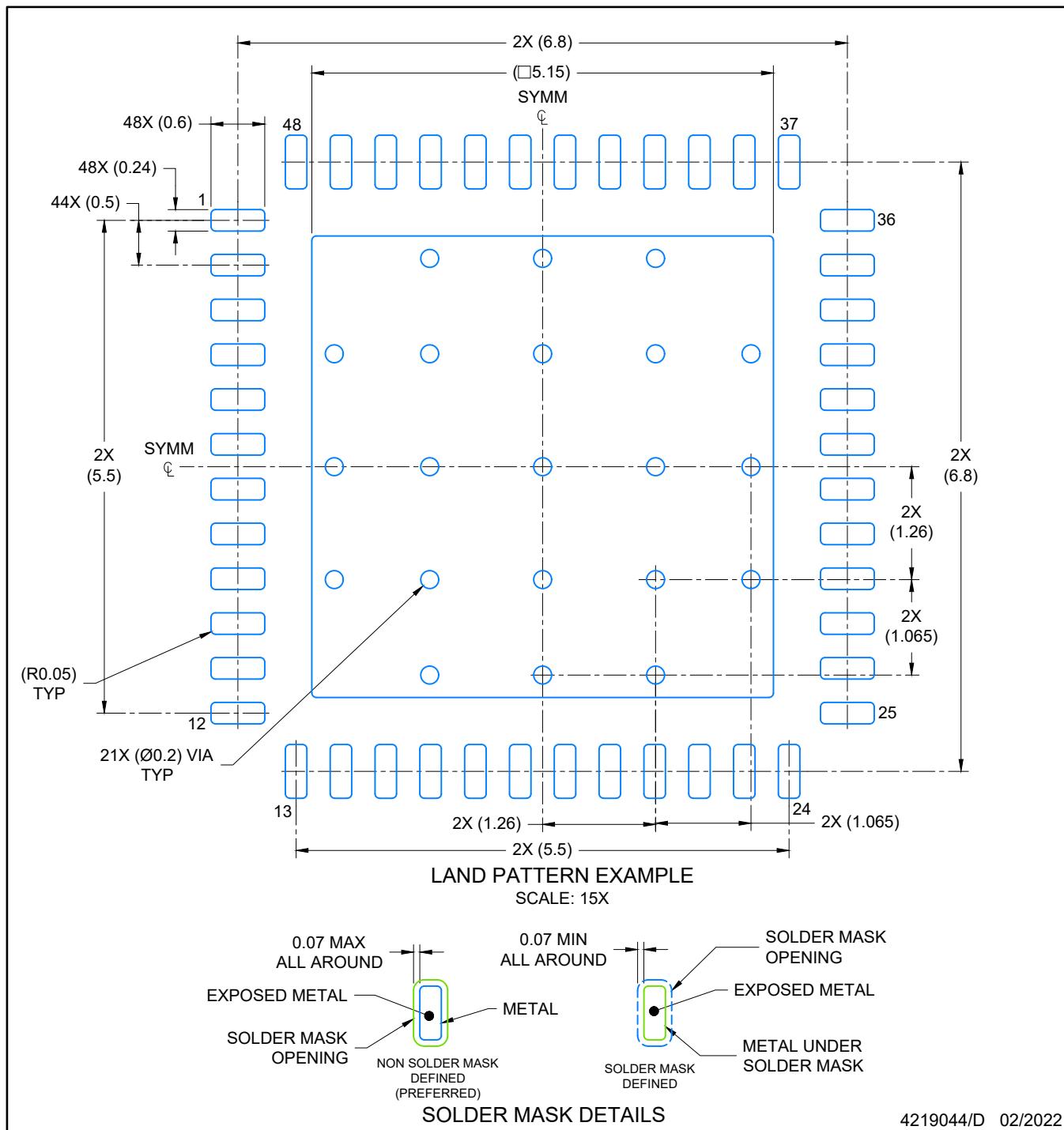

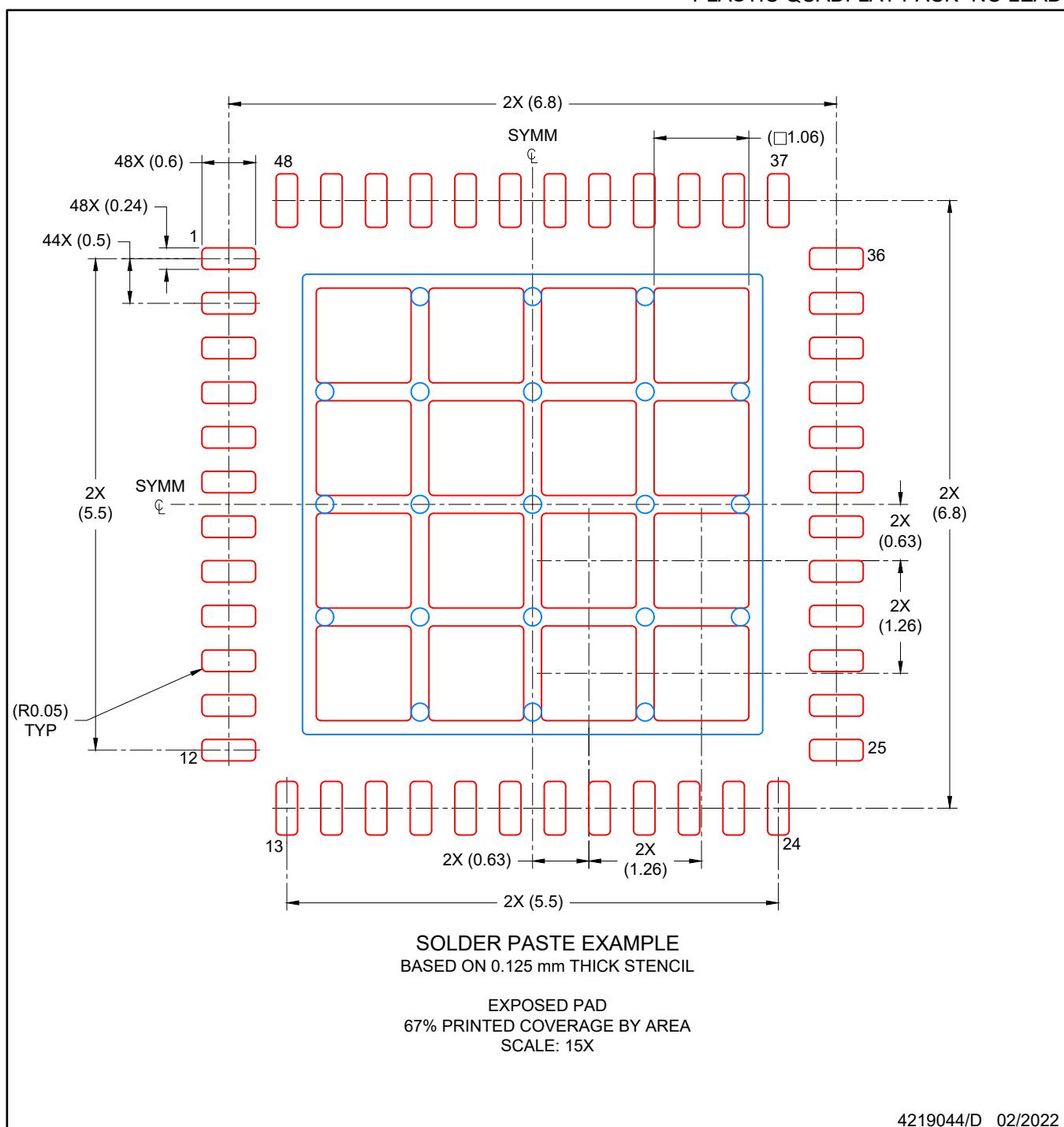

- 封装方式: **48 引脚四方扁平无引线 (QFN) PowerPAD™**

- 扩展温度范围:

- 40°C 至 +125°C**

## 应用范围

- 电子仪表

- 家庭局域网

- 照明

- 太阳能

- 电缆附线和电动汽车供电设备 (EVSE)

## 描述

AFE032 是一款低成本, 集成型, 电力线通信 (PLC), 模拟前端 (AFE) 器件, 此器件能够在一个数字信号处理器 (DSP) 或者微控制器控制下实现到电力线的变压器耦合连接。这款器件非常适合于将高达 1.9A 的高电流、低阻抗线路驱动进入电抗性负载。

此集成型接收器能够检测到低至 10 $\mu$ V<sub>RMS</sub> 的信号 (G3-FCC 模式), 并且能够支持宽范围增益选项以适应不同的输入信号情况。此单片集成电路在要求严格的电力线通信应用中提供高可靠性。

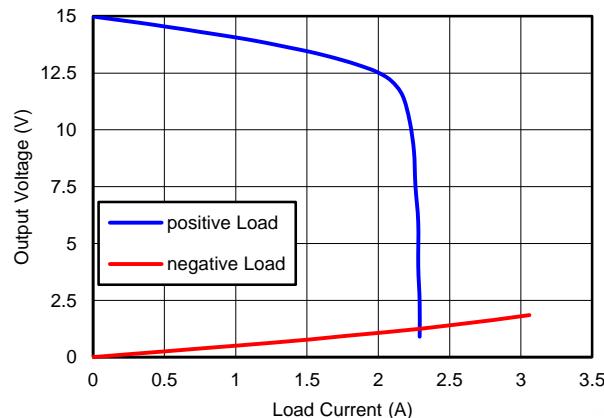

AFE032 传输功率放大器由电压范围在 7V 至 24V 的单电源供电。在负载电流为典型值时 ( $I_{OUT} = 1.5 A_{PEAK}$ ), 一个宽输出摆幅用一个额定 15V 的电源提供 12V<sub>PP</sub> 性能。

此器件在过热和短路情况下受到内部保护。此器件还提供一个可选电流限值。提供一个表示电流限制, 过热限制和过压的中断输出。还提供一个关断引脚, 并且可被用来将此器件快速置于最低功耗状态。为了通过串行外设接口 (SPI) 来优化功率耗散, 可以启用或禁用每个功能块。

AFE032 采用耐热增强型, 表面贴装, PowerPAD QFN-48 封装方式。额定工作扩展工业结温范围为 -40°C 至 +125°C。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

Illinois Capacitor is a trademark of Illinois Capacitor, Inc.

SPI is a trademark of Motorola Inc.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### ORDERING INFORMATION<sup>(1)</sup>

- (1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or visit the device product folder at [www.ti.com](http://www.ti.com).

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating free-air temperature range, unless otherwise noted.

|                         |                                      |                                 | VALUE                       | UNIT |

|-------------------------|--------------------------------------|---------------------------------|-----------------------------|------|

| PA_VS                   | Supply voltage (pins 44, 45)         |                                 | +26                         | V    |

| Signal input terminals  | Voltage <sup>(2)</sup>               | Pins 3, 4, 6, 7, 8, 10          | DGND – 0.4 to DVDD + 0.4    | V    |

|                         |                                      | Pins 13, 21, 28, 31, 32, 38, 39 | AGND – 0.4 to AVDD + 0.4    | V    |

|                         |                                      | Pins 18, 19                     | PA_GND – 0.4 to PA_VS + 0.4 | V    |

|                         |                                      | Pin 27                          | AVDD + 0.4 to 26            | V    |

|                         | Current <sup>(2)</sup>               | Pins 3, 4, 6, 7, 8, 10          | ±10                         | mA   |

|                         |                                      | Pins 13, 21, 28, 31, 32, 38, 39 | ±10                         | mA   |

|                         |                                      | Pins 18, 19                     | ±10                         | mA   |

|                         |                                      | Pin 35                          | ±10                         | mA   |

| Signal output terminals | Voltage                              | Pins 5, 9, 47, 48               | DGND – 0.4 to DVDD + 0.4    | V    |

|                         |                                      | Pins 14, 17, 20, 22, 33, 36, 37 | AGND – 0.4 to AVDD + 0.4    | V    |

|                         |                                      | Pins 42, 43                     | PA_GND – 0.4 to PA_VS + 0.4 | V    |

|                         | Current; short-circuit to GND        | Pins 5, 9, 47, 48               | Continuous                  |      |

|                         |                                      | Pins 14, 17, 20, 22, 33, 36, 37 | Continuous                  |      |

|                         |                                      | Pins 42, 43                     | Continuous                  |      |

| AVDD                    | Analog supply voltage (pins 11, 30)  |                                 | 5.5                         | V    |

| DVDD                    | Digital supply voltage               |                                 | 5.5                         | V    |

| T <sub>A</sub>          | Operating temperature <sup>(3)</sup> |                                 | –40 to +150                 | °C   |

| T <sub>stg</sub>        | Storage temperature                  |                                 | –55 to +150                 | °C   |

| T <sub>J</sub>          | Junction temperature                 |                                 | +150                        | °C   |

| ESD                     | Electrostatic discharge ratings      | Human body model (HBM)          | 3000                        | V    |

|                         |                                      | Machine model (MM)              | 200                         | V    |

|                         |                                      | Charged device model (CDM)      | 500                         | V    |

- (1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.4 V beyond the supply rails should be current limited to 10 mA or less.

- (3) The device automatically goes to shutdown above +165°C.

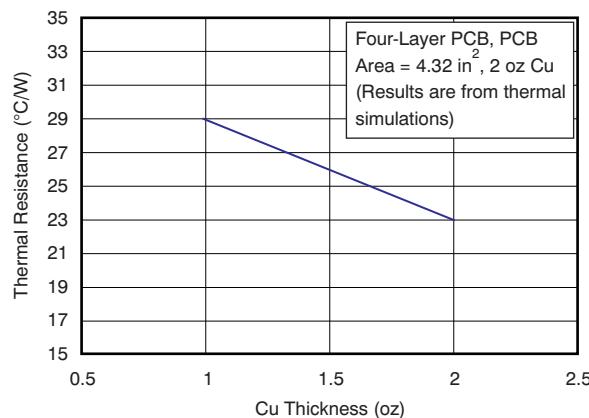

### THERMAL INFORMATION

| THERMAL METRIC <sup>(1)</sup> |                                              | AFE032    | UNITS |

|-------------------------------|----------------------------------------------|-----------|-------|

|                               |                                              | RGZ (QFN) |       |

|                               |                                              | 48 PINS   |       |

| θ <sub>JA</sub>               | Junction-to-ambient thermal resistance       | 22.5      | °C/W  |

| θ <sub>JCtop</sub>            | Junction-to-case (top) thermal resistance    | 12.1      |       |

| θ <sub>JB</sub>               | Junction-to-board thermal resistance         | 7.5       |       |

| Ψ <sub>JT</sub>               | Junction-to-top characterization parameter   | 2.0       |       |

| Ψ <sub>JB</sub>               | Junction-to-board characterization parameter | 5.4       |       |

| θ <sub>JCbot</sub>            | Junction-to-case (bottom) thermal resistance | 1.7       |       |

- (1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, [SPRA953](http://www.ti.com).

**ELECTRICAL CHARACTERISTICS: Transmitter**

At  $T_{CASE} = +25^\circ\text{C}$ ,  $V_{PAVS} = 15 \text{ V}$ , and  $V_{AVDD} = V_{DVDD} = 3.3 \text{ V}$ , unless otherwise noted.

| PARAMETER                                      | TEST CONDITIONS                                                                                                | MIN                                     | TYP                                    | MAX  | UNIT                       |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------|------|----------------------------|

| <b>DAC</b>                                     |                                                                                                                |                                         |                                        |      |                            |

| Resolution                                     | 12-bit DAC, internal $V_{REF} = 0.7 \text{ V}$                                                                 | 165                                     | 171                                    | 176  | $\mu\text{V}$              |

| DR Data rate <sup>(1)</sup>                    | DAC pin high, 12-bit word                                                                                      |                                         | 4.8                                    | 5.2  | MSPS                       |

| $G_E$ Gain error                               | Full-scale range, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$                                            | -2%                                     | $\pm 0.5\%$                            | 2%   |                            |

| <b>DAC OUTPUT</b>                              |                                                                                                                |                                         |                                        |      |                            |

| $R_O$ Output resistance                        | $G = 1$ , $f = 100 \text{ kHz}$                                                                                | 1                                       |                                        |      | $\text{k}\Omega$           |

| <b>TX_PGA INPUT</b>                            |                                                                                                                |                                         |                                        |      |                            |

| Input voltage range                            |                                                                                                                | $(AGND + 0.15) / \text{gain}$           | $(AVDD - 0.15) / \text{gain}$          |      | V                          |

| $R_I$ Input resistance                         | $G = 1.15 \text{ V/V}$                                                                                         | 52                                      |                                        |      | $\text{k}\Omega$           |

|                                                | $G = 2.3 \text{ V/V}$                                                                                          | 34                                      |                                        |      | $\text{k}\Omega$           |

|                                                | $G = 3.25 \text{ V/V}$                                                                                         | 26                                      |                                        |      | $\text{k}\Omega$           |

|                                                | $G = 4.6 \text{ V/V}$                                                                                          | 20                                      |                                        |      | $\text{k}\Omega$           |

| G Gain                                         |                                                                                                                | 1.15, 2.3, 3.25, 4.6 <sup>(2)</sup>     |                                        |      | V/V                        |

| $G_E$ Gain error                               | Includes DAC, programmable filter, and TX_PGA for all gains, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | -2%                                     | $\pm 0.1\%$                            | 2%   |                            |

| Gain error drift                               | Includes DAC, programmable filter, and TX_PGA for all gains, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | -10                                     | $\pm 3$                                | +10  | ppm/ $^\circ\text{C}$      |

| <b>TX_PGA FREQUENCY RESPONSE</b>               |                                                                                                                |                                         |                                        |      |                            |

| BW Bandwidth <sup>(3)</sup>                    | $C_L = 20 \text{ pF}$ , $G = 1.15 \text{ V/V}$ , $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$             | 30                                      |                                        |      | MHz                        |

|                                                | $C_L = 20 \text{ pF}$ , $G = 2.3 \text{ V/V}$ , $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$              | 21.5                                    |                                        |      | MHz                        |

|                                                | $C_L = 20 \text{ pF}$ , $G = 3.25 \text{ V/V}$ , $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$             | 17.5                                    |                                        |      | MHz                        |

|                                                | $C_L = 20 \text{ pF}$ , $G = 4.6 \text{ V/V}$ , $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$              | 15.5                                    |                                        |      | MHz                        |

| <b>TX PATH TRANSMITTER NOISE<sup>(4)</sup></b> |                                                                                                                |                                         |                                        |      |                            |

| Integrated noise at PA output <sup>(5)</sup>   | CEN-A                                                                                                          | 35 kHz to 95 kHz                        | 370                                    |      | $\mu\text{V}_{\text{RMS}}$ |

|                                                | CEN-B                                                                                                          | 95 kHz to 125 kHz                       | 220                                    |      | $\mu\text{V}_{\text{RMS}}$ |

|                                                | CEN-C                                                                                                          | 125 kHz to 140 kHz                      | 160                                    |      | $\mu\text{V}_{\text{RMS}}$ |

|                                                | CEN-D                                                                                                          | 140 kHz to 148 kHz                      | 98                                     |      | $\mu\text{V}_{\text{RMS}}$ |

|                                                | ARIB STD-T84                                                                                                   | 35 kHz to 420 kHz                       | 640                                    |      | $\mu\text{V}_{\text{RMS}}$ |

|                                                | FCC-LOW                                                                                                        | 35 kHz to 125 kHz                       | 384                                    |      | $\mu\text{V}_{\text{RMS}}$ |

|                                                | G3-FCC                                                                                                         | 150 kHz to 490 kHz                      | 565                                    |      | $\mu\text{V}_{\text{RMS}}$ |

| <b>POWER AMPLIFIER (PA) INPUT</b>              |                                                                                                                |                                         |                                        |      |                            |

| Input voltage range                            | For linear operation                                                                                           | $(PA_{\text{GND}} + 0.4) / \text{gain}$ | $(PA_{\text{VS}} - 0.4) / \text{gain}$ |      | V                          |

| Input impedance                                |                                                                                                                | 17                                      |                                        |      | $\text{k}\Omega$           |

| <b>PA FREQUENCY RESPONSE</b>                   |                                                                                                                |                                         |                                        |      |                            |

| BW Bandwidth                                   | $I_{\text{LOAD}} = 0 \text{ mA}$                                                                               | 3.4                                     | 3.82                                   | 4.23 | MHz                        |

| SR Slew rate                                   | $PA_{\text{VS}} = 24 \text{ V}$ , 20-V step                                                                    |                                         | 75                                     |      | $\text{V}/\mu\text{s}$     |

| Full-power bandwidth                           | $PA_{\text{VS}} = 24 \text{ V}$ , $V_{\text{OUT}} = 20 \text{ V}_{\text{PP}}$                                  |                                         | 1                                      |      | MHz                        |

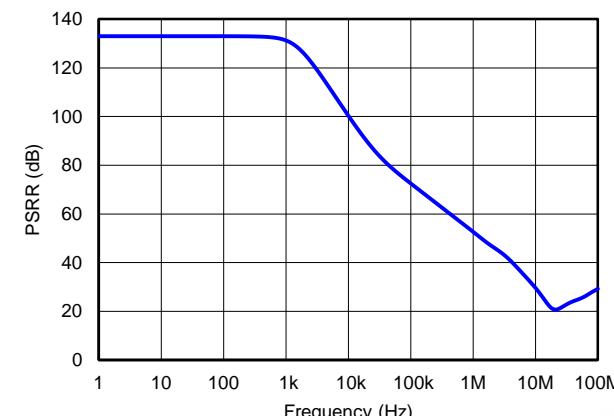

| PSRR Power-supply rejection ratio              | RTI, dc to $f = 50 \text{ kHz}$                                                                                | 80                                      | 94                                     |      | dB                         |

- (1) Refer to the [Application Information](#) section.

- (2) This parameter is from DAC\_OUT to TX\_F\_OUT. This parameter includes the LPF gain error and is the dc gain. Adding LPF causes some loss of gain flatness.

- (3) This parameter is internal to the device. Bandwidth is designed and simulated over corners to ensure a low-distortion PGA in the application.

- (4) Includes the DAC, programmable filter, TX\_PGA, and PA noise-reducing capacitor = 1 nF from DAC\_NRF to ground, PA\_NRF to ground, and TX\_RF\_NRF to ground.

- (5) Includes the DAC, TX\_PGA (gain = 4.6), LPF, and PA.

## ELECTRICAL CHARACTERISTICS: Transmitter (continued)

At  $T_{CASE} = +25^\circ\text{C}$ ,  $V_{PAVS} = 15\text{ V}$ , and  $V_{AVDD} = V_{DVDD} = 3.3\text{ V}$ , unless otherwise noted.

| PARAMETER                        |                                     | TEST CONDITIONS                                                      | MIN                                                     | TYP                 | MAX  | UNIT                                 |  |

|----------------------------------|-------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------|---------------------|------|--------------------------------------|--|

| <b>PA OUTPUT</b>                 |                                     |                                                                      |                                                         |                     |      |                                      |  |

| $V_O$                            | Voltage output swing                | $I_O = 200\text{-mA sourcing, 1-ms pulse}$                           |                                                         |                     | 0.5  | V                                    |  |

|                                  |                                     | $I_O = 1.5\text{-A sourcing, 1-ms pulse}$                            |                                                         |                     | 2.25 | V                                    |  |

|                                  | From PA_GND                         | $I_O = 200\text{ mA sinking, 1-ms pulse}$                            |                                                         |                     | 0.5  | V                                    |  |

|                                  |                                     | $I_O = 1.5\text{-A sinking, 1-ms pulse}$                             |                                                         |                     | 1.5  | V                                    |  |

| Maximum continuous current, dc   |                                     | Pin 26 connected to ground, $\text{REG\_PA\_CURRENT\_CFG}[5:4] = 11$ |                                                         | 1.9                 |      | A                                    |  |

| Output resistance                |                                     | $I_O = 1.9\text{ A, } f = 500\text{ kHz}$                            |                                                         | 0.1                 |      | $\Omega$                             |  |

| PA disabled output impedance     |                                     | $f = 100\text{ kHz, PA_NRF enabled}$                                 |                                                         | 130 $\parallel$ 105 |      | $\text{k}\Omega \parallel \text{pF}$ |  |

| Output current limit             | Resistor-selectable                 | $R_{SET}$ connected from pin 26 to ground                            | See the <a href="#">Application Information</a> section |                     |      |                                      |  |

|                                  | Digitally-selectable <sup>(6)</sup> | Pin 26 connected to ground, $\text{REG\_PA\_CURRENT\_CFG}[5:4] = 00$ |                                                         | 1.25                |      | A                                    |  |

|                                  |                                     | Pin 26 connected to ground, $\text{REG\_PA\_CURRENT\_CFG}[5:4] = 01$ |                                                         | 1.8                 |      | A                                    |  |

|                                  |                                     | Pin 26 connected to ground, $\text{REG\_PA\_CURRENT\_CFG}[5:4] = 10$ |                                                         | 2.5                 |      | A                                    |  |

|                                  |                                     | Pin 26 connected to ground, $\text{REG\_PA\_CURRENT\_CFG}[5:4] = 11$ |                                                         | 3.0                 |      | A                                    |  |

| <b>PA THERMAL SHUTDOWN</b>       |                                     |                                                                      |                                                         |                     |      |                                      |  |

| Junction temperature at shutdown |                                     |                                                                      |                                                         | +165                |      | $^\circ\text{C}$                     |  |

| Hysteresis                       |                                     |                                                                      |                                                         | +15                 |      | $^\circ\text{C}$                     |  |

| Return to normal operation       |                                     |                                                                      |                                                         | +150                |      | $^\circ\text{C}$                     |  |

| <b>PA TSENSE DIODE</b>           |                                     |                                                                      |                                                         |                     |      |                                      |  |

| $\eta$                           | Diode ideality factor               |                                                                      |                                                         | 1.03                |      |                                      |  |

| <b>PA GAIN</b>                   |                                     |                                                                      |                                                         |                     |      |                                      |  |

| G                                | Nominal gain                        | PA_OUT / PA_IN                                                       |                                                         | 7.4 <sup>(7)</sup>  |      | V/V                                  |  |

| $G_E$                            | Gain error                          | $T_J = -40^\circ\text{C to } +125^\circ\text{C}$                     |                                                         | -2%                 | 0.1% | 2%                                   |  |

| Gain error drift                 |                                     | $T_J = -40^\circ\text{C to } +125^\circ\text{C}$                     |                                                         | $\pm 5$             |      | ppm/ $^\circ\text{C}$                |  |

(6) Refer to the [Application Information](#) section.

(7) This gain reflects a direct measurement on the PA block by itself. The gain in the signal chain composed by Tx PGA, Tx Filter and PA equals the Tx PGA gain multiplied by 7 V/V (where 7 V/V is the gain of the PA block when its input is capacitively coupled to the Tx Filter output). Refer to the [Power Amplifier Block](#) section for more information.

## ELECTRICAL CHARACTERISTICS: Programmable Filter

At  $T_{CASE} = +25^\circ\text{C}$ ,  $V_{PAVS} = 15 \text{ V}$ , and  $V_{AVDD} = V_{DVDD} = 3.3 \text{ V}$ , unless otherwise noted.

| PARAMETER                                         |                              | TEST CONDITIONS                                                               | MIN | TYP               | MAX | UNIT             |

|---------------------------------------------------|------------------------------|-------------------------------------------------------------------------------|-----|-------------------|-----|------------------|

| <b>LOW-PASS FILTER (LPF)</b>                      |                              |                                                                               |     |                   |     |                  |

| Cutoff frequencies in Tx mode <sup>(1)</sup>      | CEN-A                        | 1-dB gain flatness, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$         | 94  | 102               | 110 | kHz              |

|                                                   | CEN-B, CEN-C, CEN-D, FCC-LOW | 1-dB gain flatness, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$         | 148 | 160               | 172 | kHz              |

|                                                   | ARIB STD-T84                 | 1-dB gain flatness, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$         | 405 | 435               | 475 | kHz              |

|                                                   | G3-FCC                       | 1-dB gain flatness, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$         | 470 | 505               | 540 | kHz              |

| Transition time                                   | Rx to Tx                     | PA_NRF, TX_RX_NRF, and DAC, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$ |     | 80 <sup>(2)</sup> |     | μs               |

|                                                   | Tx to Rx                     | NRF enabled, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$                |     | 30                |     | μs               |

| <b>LPF OUTPUT</b>                                 |                              |                                                                               |     |                   |     |                  |

| $R_O$                                             | Output impedance             | $f = 100 \text{ kHz}$                                                         |     | 1                 |     | $\text{k}\Omega$ |

| <b>HIGH-PASS FILTER (HPF)</b>                     |                              |                                                                               |     |                   |     |                  |

| CEN-A, CEN-B, CEN-C, CEN-D, ARIB STD-T84, FCC-LOW |                              | 1-dB gain flatness, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$         | 30  | 35                | 40  | kHz              |

| G3-FCC                                            |                              | 1-dB gain flatness, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$         | 120 | 132               | 152 | kHz              |

| Transition time                                   | Rx to Tx                     | PA_NRF, TX_RX_NRF, and DAC, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$ |     | 30                |     | μs               |

|                                                   | Tx to Rx                     | NRF enabled, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$                |     | 80 <sup>(2)</sup> |     | μs               |

| <b>HPF OUTPUT</b>                                 |                              |                                                                               |     |                   |     |                  |

| $R_O$                                             | Output impedance             | $f = 100 \text{ kHz}$                                                         |     | 1                 |     | $\text{k}\Omega$ |

(1) These cutoff frequencies are only valid when the filter is used as a low-pass filter. Refer to the [Register Map](#) section in the [Application Information](#) for register settings.

(2) See the [Application Information](#) section for the start-up procedure.

**ELECTRICAL CHARACTERISTICS: Receiver**At  $T_{CASE} = +25^\circ\text{C}$ ,  $V_{PAVS} = 15 \text{ V}$ , and  $V_{AVDD} = V_{DVDD} = 3.3 \text{ V}$ , unless otherwise noted.

| PARAMETER                         |                     | TEST CONDITIONS                                                  | MIN                                  | TYP                           | MAX | UNIT                  |

|-----------------------------------|---------------------|------------------------------------------------------------------|--------------------------------------|-------------------------------|-----|-----------------------|

| <b>RX_PGA1 INPUT</b>              |                     |                                                                  |                                      |                               |     |                       |

| $R_I$                             | Input voltage range | For linear operation                                             | $(A_{GND} + 0.15) / \text{gain}$     | $(AVDD - 0.15) / \text{gain}$ |     | V                     |

|                                   |                     | $G = 0.125 \text{ V/V}$                                          | 111.1                                |                               |     | $\text{k}\Omega$      |

|                                   |                     | $G = 0.25 \text{ V/V}$                                           | 100                                  |                               |     | $\text{k}\Omega$      |

|                                   |                     | $G = 0.5 \text{ V/V}$                                            | 133                                  |                               |     | $\text{k}\Omega$      |

|                                   |                     | $G = 1 \text{ V/V}$                                              | 100                                  |                               |     | $\text{k}\Omega$      |

|                                   |                     | $G = 2 \text{ V/V}$                                              | 66                                   |                               |     | $\text{k}\Omega$      |

|                                   |                     | $G = 4 \text{ V/V}$                                              | 40                                   |                               |     | $\text{k}\Omega$      |

|                                   |                     | $G = 8 \text{ V/V}$                                              | 22                                   |                               |     | $\text{k}\Omega$      |

|                                   |                     | $G = 16 \text{ V/V}$                                             | 12                                   |                               |     | $\text{k}\Omega$      |

|                                   |                     | $G = 32 \text{ V/V}$                                             | 6                                    |                               |     | $\text{k}\Omega$      |

| <b>RX_PGA1 GAIN</b>               |                     |                                                                  |                                      |                               |     |                       |

| $G_E$                             | DC gain             |                                                                  | 0.125, 0.25, 0.5, 1, 2, 4, 8, 16, 32 |                               |     | V/V                   |

|                                   | Gain error          | For all gains, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | -5%                                  |                               | 5%  |                       |

| Gain error drift                  |                     | $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$                |                                      | $\pm 100$                     |     | ppm/ $^\circ\text{C}$ |

| <b>RX_PGA1 FREQUENCY RESPONSE</b> |                     |                                                                  |                                      |                               |     |                       |

| $BW$                              | Bandwidth           | $C_L = 20 \text{ pF}, G = 0.125 \text{ V/V}$                     | 47                                   |                               |     | MHz                   |

|                                   |                     | $C_L = 20 \text{ pF}, G = 0.25 \text{ V/V}$                      | 18                                   |                               |     | MHz                   |

|                                   |                     | $C_L = 20 \text{ pF}, G = 0.5 \text{ V/V}$                       | 6                                    |                               |     | MHz                   |

|                                   |                     | $C_L = 20 \text{ pF}, G = 1 \text{ V/V}$                         | 4                                    |                               |     | MHz                   |

|                                   |                     | $C_L = 20 \text{ pF}, G = 2 \text{ V/V}$                         | 3                                    |                               |     | MHz                   |

|                                   |                     | $C_L = 20 \text{ pF}, G = 4 \text{ V/V}$                         | 2.5                                  |                               |     | MHz                   |

|                                   |                     | $C_L = 20 \text{ pF}, G = 8 \text{ V/V}$                         | 2.1                                  |                               |     | MHz                   |

|                                   |                     | $C_L = 20 \text{ pF}, G = 16 \text{ V/V}$                        | 1.85                                 |                               |     | MHz                   |

|                                   |                     | $C_L = 20 \text{ pF}, G = 32 \text{ V/V}$                        | 1.55                                 |                               |     | MHz                   |

| <b>RX_PGA2 INPUT</b>              |                     |                                                                  |                                      |                               |     |                       |

| $R_I$                             | Input voltage range | For linear operation                                             | $(A_{GND} + 0.15) / \text{gain}$     | $(AVDD - 0.15) / \text{gain}$ |     | V                     |

|                                   |                     | $G = 1 \text{ V/V}$                                              | 54                                   |                               |     | $\text{k}\Omega$      |

|                                   |                     | $G = 4 \text{ V/V}$                                              | 21                                   |                               |     | $\text{k}\Omega$      |

|                                   |                     | $G = 16 \text{ V/V}$                                             | 5.5                                  |                               |     | $\text{k}\Omega$      |

**ELECTRICAL CHARACTERISTICS: Receiver (continued)**

At  $T_{CASE} = +25^\circ\text{C}$ ,  $V_{PAVS} = 15 \text{ V}$ , and  $V_{AVDD} = V_{DVDD} = 3.3 \text{ V}$ , unless otherwise noted.

| PARAMETER                                |                  | TEST CONDITIONS                                                  | MIN      | TYP       | MAX | UNIT                       |  |

|------------------------------------------|------------------|------------------------------------------------------------------|----------|-----------|-----|----------------------------|--|

| <b>Rx_PGA2 GAIN</b>                      |                  |                                                                  |          |           |     |                            |  |

| G                                        | Gain             |                                                                  | 1, 4, 16 |           |     | V/V                        |  |

| $G_E$                                    | Gain error       | For all gains, $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$ | -2%      | 2%        |     |                            |  |

|                                          | Gain error drift | $T_J = -40^\circ\text{C}$ to $+125^\circ\text{C}$                |          | $\pm 100$ |     | ppm/ $^\circ\text{C}$      |  |

| <b>RX_PGA2 FREQUENCY RESPONSE</b>        |                  |                                                                  |          |           |     |                            |  |

| BW                                       | Bandwidth        | $C_L = 20 \text{ pF}$ , $G = 1 \text{ V/V}$                      | 6.73     |           |     | MHz                        |  |

|                                          |                  | $C_L = 20 \text{ pF}$ , $G = 4 \text{ V/V}$                      | 5        |           |     | MHz                        |  |

|                                          |                  | $C_L = 20 \text{ pF}$ , $G = 16 \text{ V/V}$                     | 3        |           |     | MHz                        |  |

| <b>RX_PGA2 OUTPUT</b>                    |                  |                                                                  |          |           |     |                            |  |

| Output resistance                        |                  | $G = 1$ , $f = 100 \text{ kHz}$                                  | 1        |           |     | $\text{k}\Omega$           |  |

| <b>RX PATH SENSITIVITY<sup>(1)</sup></b> |                  |                                                                  |          |           |     |                            |  |

| Input-referred integrated noise          | CEN-A            | 35 kHz to 95 kHz                                                 | 10       |           |     | $\mu\text{V}_{\text{RMS}}$ |  |

|                                          | CEN-B            | 95 kHz to 125 kHz                                                | 5        |           |     | $\mu\text{V}_{\text{RMS}}$ |  |

|                                          | CEN-C            | 125 kHz to 140 kHz                                               | 3        |           |     | $\mu\text{V}_{\text{RMS}}$ |  |

|                                          | CEN-D            | 140 kHz to 148 kHz                                               | 2        |           |     | $\mu\text{V}_{\text{RMS}}$ |  |

|                                          | ARIB STD-T84     | 35 kHz to 400 kHz                                                | 12       |           |     | $\mu\text{V}_{\text{RMS}}$ |  |

|                                          | FCC-LOW          | 35 kHz to 125 kHz                                                | 11       |           |     | $\mu\text{V}_{\text{RMS}}$ |  |

|                                          | G3-FCC           | 150 kHz to 490 kHz                                               | 10       |           |     | $\mu\text{V}_{\text{RMS}}$ |  |

(1) Noise-reducing capacitor = 1 nF from TX\_RX\_NRF to ground, RX\_PGA1 = 32, and RX\_PGA2 = 1.

**ELECTRICAL CHARACTERISTICS: Noise-Reducing Filters**

At  $T_{CASE} = +25^\circ\text{C}$ ,  $V_{PAVS} = 15 \text{ V}$ , and  $V_{AVDD} = V_{DVDD} = 3.3 \text{ V}$ , unless otherwise noted.

| PARAMETER        |                   | TEST CONDITIONS                                          | MIN              | TYP | MAX | UNIT             |

|------------------|-------------------|----------------------------------------------------------|------------------|-----|-----|------------------|

| <b>PA_NRF</b>    |                   |                                                          |                  |     |     |                  |

|                  | Bias voltage      |                                                          | $V_{PAVS} / 2$   |     |     | V                |

| $R_{OUT}$        | Output resistance |                                                          | 4                |     |     | $\text{k}\Omega$ |

| $t_{ON}$         | Turn-on time      | Noise-reducing capacitor = 1 nF from PA_NRF to ground    | 250              |     |     | ms               |

| $t_{OFF}$        | Turn-off time     |                                                          | 10               |     |     | $\mu\text{s}$    |

| <b>TX_RX_NRF</b> |                   |                                                          |                  |     |     |                  |

|                  | Bias voltage      |                                                          | $V_{AVDD} / 2$   |     |     | V                |

| $R_{OUT}$        | Output resistance |                                                          | 1                |     |     | $\text{k}\Omega$ |

| $t_{ON}$         | Turn-on time      | Noise-reducing capacitor = 1 nF from TX_RX_NRF to ground | 10               |     |     | $\mu\text{s}$    |

| $t_{OFF}$        | Turn-off time     |                                                          | 10               |     |     | $\mu\text{s}$    |

| <b>DAC_NRF</b>   |                   |                                                          |                  |     |     |                  |

|                  | Bias voltage      |                                                          | $V_{AVDD} / 4.7$ |     |     | V                |

| $R_{OUT}$        | Output resistance |                                                          | 1                |     |     | $\text{k}\Omega$ |

| $t_{ON}$         | Turn-on time      | Noise-reducing capacitor = 1 nF from DAC_NRF to ground   | 10               |     |     | $\mu\text{s}$    |

| $t_{OFF}$        | Turn-off time     |                                                          | 10               |     |     | $\mu\text{s}$    |

## ELECTRICAL CHARACTERISTICS: Digital

At  $T_{CASE} = +25^\circ\text{C}$ ,  $V_{PAVS} = 15 \text{ V}$ , and  $V_{AVDD} = V_{DVDD} = 3.3 \text{ V}$ , unless otherwise noted.

| PARAMETER                                           | TEST CONDITIONS                     |                                     | MIN                                      | TYP       | MAX           | UNIT          |  |  |  |  |  |

|-----------------------------------------------------|-------------------------------------|-------------------------------------|------------------------------------------|-----------|---------------|---------------|--|--|--|--|--|

| <b>DIGITAL INPUTS (SCLK, DI, CS, SD, DAC, XCLK)</b> |                                     |                                     |                                          |           |               |               |  |  |  |  |  |

| Leakage input current                               | 0 V $\leq V_{IN} \leq DVDD$         |                                     | -1                                       | 0.01      | 1             | $\mu\text{A}$ |  |  |  |  |  |

| $V_{IH}$                                            | High-level input voltage            |                                     | $0.7 \times DVDD$                        |           | V             |               |  |  |  |  |  |

| $V_{IL}$                                            | Low-level input voltage             |                                     | $0.3 \times DVDD$                        |           | V             |               |  |  |  |  |  |

| SD pin function (active high)                       | SD pin high                         | SD $> 0.7 \times DVDD$              | Device in shutdown                       |           |               |               |  |  |  |  |  |

|                                                     | SD pin low                          | SD $< 0.3 \times DVDD$              | Device in normal operation               |           |               |               |  |  |  |  |  |

| DAC pin function (active high)                      | DAC pin high                        | DAC $> 0.7 \times DVDD$             | SPI access to DAC registers              |           |               |               |  |  |  |  |  |

|                                                     | DAC pin low                         | DAC $< 0.3 \times DVDD$             | SPI access to command and data registers |           |               |               |  |  |  |  |  |

| XCLK frequency range                                | XCLK jitter $< 180 \text{ ps}$      |                                     | 5                                        | 40        |               | MHz           |  |  |  |  |  |

| <b>DIGITAL OUTPUTS (DO, ZC_OUT)</b>                 |                                     |                                     |                                          |           |               |               |  |  |  |  |  |

| $V_{OH}$                                            | High-level output voltage           | $I_{OH} = 3 \text{ mA}$             | DVDD – 0.4                               | DVDD      |               | V             |  |  |  |  |  |

| $V_{OL}$                                            | Low-level output voltage            | $I_{OL} = -3 \text{ mA}$            | GND                                      | GND + 0.4 |               | V             |  |  |  |  |  |

| <b>DIGITAL OUTPUTS (INT, TX_FLAG, RX_FLAG)</b>      |                                     |                                     |                                          |           |               |               |  |  |  |  |  |

| $I_{OH}$                                            | High-level output current           | $V_{OH} = 3.3 \text{ V}$            | 1                                        |           | $\mu\text{A}$ |               |  |  |  |  |  |

| $V_{OL}$                                            | Low-level output voltage            | $I_{OL} = 4 \text{ mA}$             | 0.4                                      |           | V             |               |  |  |  |  |  |

| $I_{OL}$                                            | Low-level output current            | $V_{OL} = 400 \text{ mV}$           | 4                                        | mA        |               |               |  |  |  |  |  |

| INT pin (active low, open-drain)                    | INT pin high                        | INT sink high $< 1 \mu\text{A}$     | Normal operation                         |           |               |               |  |  |  |  |  |

|                                                     | INT pin low                         | INT $< 0.4 \text{ V}$               | Interrupt has occurred                   |           |               |               |  |  |  |  |  |

| TX_FLAG (active low, open-drain)                    | TX_FLAG pin high                    | TX_FLAG sink high $< 1 \mu\text{A}$ | Tx block disabled                        |           |               |               |  |  |  |  |  |

|                                                     | TX_FLAG pin low                     | TX_FLAG $< 0.4 \text{ V}$           | Tx block ready                           |           |               |               |  |  |  |  |  |

| RX_FLAG (active low, open-drain)                    | RX_FLAG pin high                    | RX_FLAG sink high $< 1 \mu\text{A}$ | Rx block disabled                        |           |               |               |  |  |  |  |  |

|                                                     | RX_FLAG pin low                     | RX_FLAG $< 0.4 \text{ V}$           | Rx block ready                           |           |               |               |  |  |  |  |  |

| <b>GAIN TIMING</b>                                  |                                     |                                     |                                          |           |               |               |  |  |  |  |  |

| Gain select time                                    |                                     |                                     | 0.2                                      |           | $\mu\text{s}$ |               |  |  |  |  |  |

| <b>SHUTDOWN MODE TIMING</b>                         |                                     |                                     |                                          |           |               |               |  |  |  |  |  |

| Enable time                                         | SD pin transitions from high to low |                                     | 3                                        | ms        |               |               |  |  |  |  |  |

| Disable time                                        | SD pin transitions from low to high |                                     | 2                                        | ms        |               |               |  |  |  |  |  |

| <b>POR TIMING</b>                                   |                                     |                                     |                                          |           |               |               |  |  |  |  |  |

| Power-on reset power-up time                        | $DVDD \geq 2 \text{ V}$             |                                     | 3                                        | ms        |               |               |  |  |  |  |  |

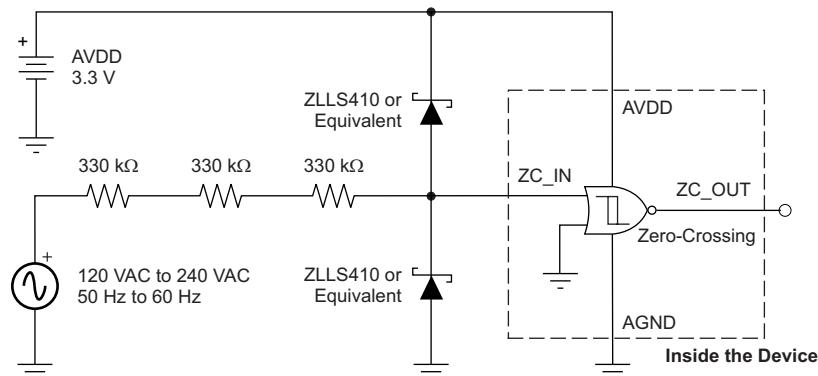

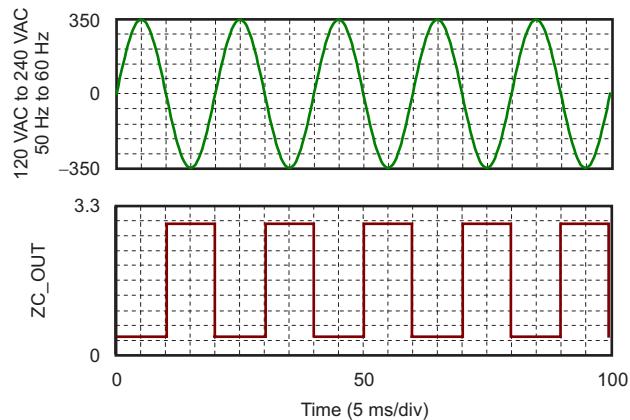

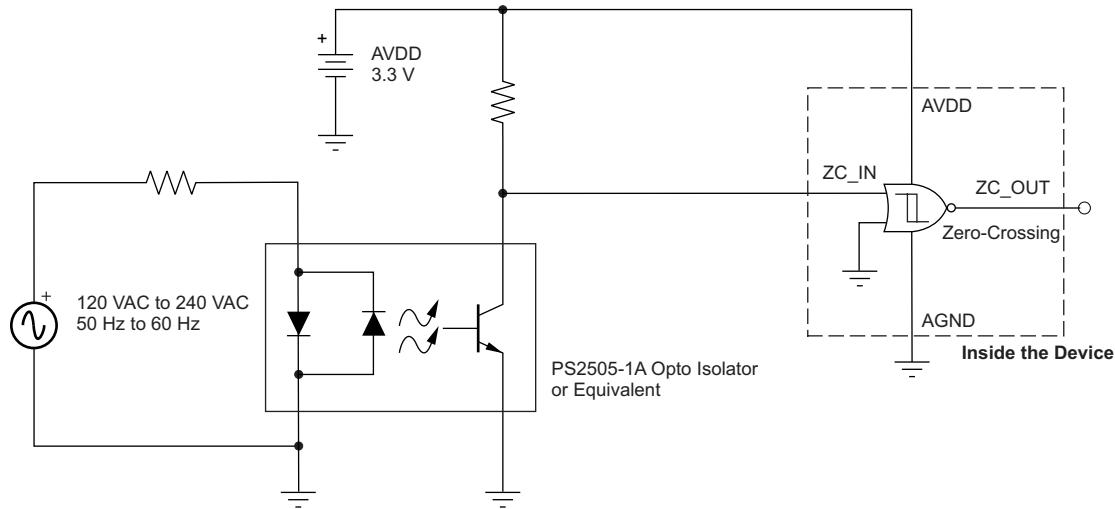

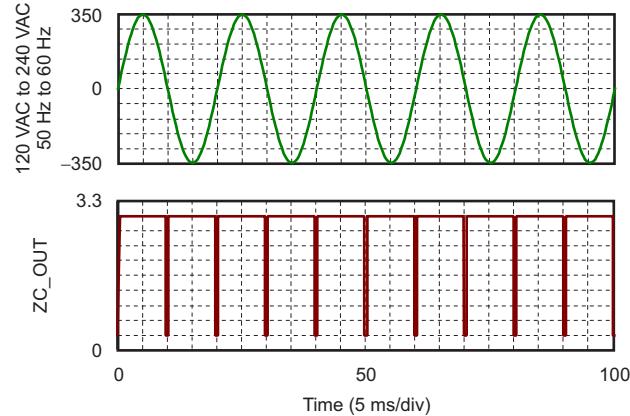

## ELECTRICAL CHARACTERISTICS: Zero-Crossing Detector

At  $T_{CASE} = +25^\circ\text{C}$ ,  $V_{PAVS} = 15 \text{ V}$ , and  $V_{AVDD} = V_{DVDD} = 3.3 \text{ V}$ , unless otherwise noted.

| PARAMETER           | TEST CONDITIONS                                                              | MIN  | TYP | MAX  | UNIT             |

|---------------------|------------------------------------------------------------------------------|------|-----|------|------------------|

| Input voltage range |                                                                              | AGND |     | AVDD | V                |

| Input current range |                                                                              | -10  |     | 10   | mA               |

| $R_{IN}$            | $\text{AGND} \leq V_{IN} \leq \text{AVDD}$                                   |      | 2   |      | $\text{M}\Omega$ |

| $C_{IN}$            | Input capacitance                                                            |      | 4   |      | pF               |

| Rising threshold    |                                                                              | 0.45 | 0.9 | 1.35 | V                |

| Falling threshold   |                                                                              | 0.25 | 0.5 | 0.75 | V                |

| Hysteresis          |                                                                              | 0.2  | 0.4 | 0.6  | V                |

| Jitter              | 50 Hz and 60 Hz, 240 $\text{V}_{\text{RMS}}$ and 120 $\text{V}_{\text{RMS}}$ |      | 10  |      | ns               |

## ELECTRICAL CHARACTERISTICS: Power Supply

At  $T_{CASE} = +25^\circ\text{C}$ ,  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ ,  $V_{PAVS} = 15 \text{ V}$ , and  $V_{AVDD} = V_{DVDD} = 3.3 \text{ V}$ , unless otherwise noted.

| PARAMETER                             | TEST CONDITIONS | MIN                                                                            | TYP | MAX | UNIT |               |

|---------------------------------------|-----------------|--------------------------------------------------------------------------------|-----|-----|------|---------------|

| <b>OPERATING SUPPLY RANGE</b>         |                 |                                                                                |     |     |      |               |

| PA_VS                                 | Power amplifier | 7                                                                              | 15  | 24  | V    |               |

| DVDD                                  | Digital supply  |                                                                                | 3.3 |     | V    |               |

| AVDD                                  | Analog supply   |                                                                                | 3.3 |     | V    |               |

| <b>QUIESCENT CURRENT (SD pin low)</b> |                 |                                                                                |     |     |      |               |

| IQ <sub>PA_VS</sub>                   | Power amplifier | $I_O = 0 \text{ V}$ , PA = on <sup>(1)</sup> ,<br>REG_PA_CURRENT_CFG[7:6] = 00 | 40  | 48  | 56   | mA            |

|                                       |                 | $I_O = 0 \text{ V}$ , PA = on <sup>(1)</sup> ,<br>REG_PA_CURRENT_CFG[7:6] = 01 | 68  | 78  | 88   | mA            |

|                                       |                 | $I_O = 0 \text{ V}$ , PA = on <sup>(1)</sup> ,<br>REG_PA_CURRENT_CFG[7:6] = 10 | 84  | 96  | 108  | mA            |

|                                       |                 | $I_O = 0 \text{ V}$ , PA = on <sup>(1)</sup> ,<br>REG_PA_CURRENT_CFG[7:6] = 11 | 10  | 17  | 24   | mA            |

| IQ <sub>DVDD</sub>                    | Digital supply  | Tx configuration <sup>(2)</sup>                                                | 1.5 | 2.5 | 3.5  | mA            |

|                                       |                 | Rx configuration <sup>(3)</sup>                                                | 1.1 | 2.1 | 3.1  | mA            |

|                                       |                 | All blocks disabled <sup>(4)</sup>                                             |     | 330 | 450  | $\mu\text{A}$ |

| IQ <sub>AVDD</sub>                    | Analog supply   | Tx configuration <sup>(3)</sup>                                                | 8   | 11  | 14   | mA            |

|                                       |                 | Rx configuration <sup>(4)</sup>                                                | 9   | 13  | 17   | mA            |

|                                       |                 | All blocks disabled <sup>(4)</sup>                                             |     | 25  | 100  | $\mu\text{A}$ |

| <b>SHUTDOWN</b>                       |                 |                                                                                |     |     |      |               |

| SD <sub>PA_VS</sub>                   | Power amplifier | SD pin high                                                                    |     | 40  | 150  | $\mu\text{A}$ |

| SD <sub>DVDD</sub>                    | Digital supply  | SD pin high                                                                    |     | 330 | 400  | $\mu\text{A}$ |

| SD <sub>AVDD</sub>                    | Analog supply   | SD pin high                                                                    |     | 25  | 50   | $\mu\text{A}$ |

- (1) PA and PA output enabled.

- (2) The DAC, TX\_PGA, low-pass filter, PA, PA\_NRF, TX\_RX\_NRF, and DAC\_NRF blocks are enabled in the Tx configuration. All other blocks are disabled.

- (3) The RX\_PGA1, high-pass filter, low-pass filter, RX\_PGA2, and TX\_RX\_NRF blocks are enabled in the Rx configuration. All other blocks are disabled.

- (4) All internal blocks disabled, SD pin low.

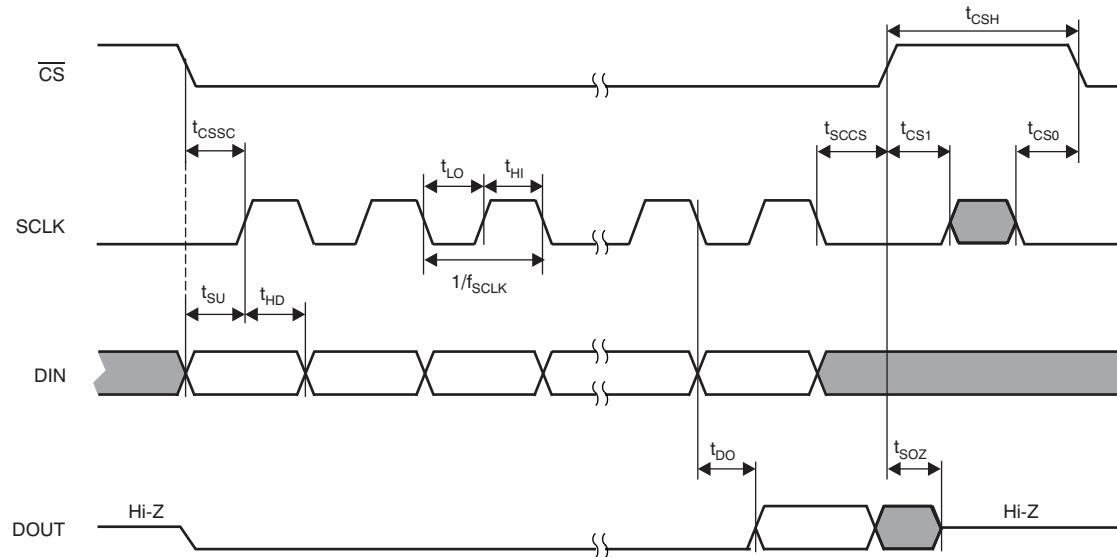

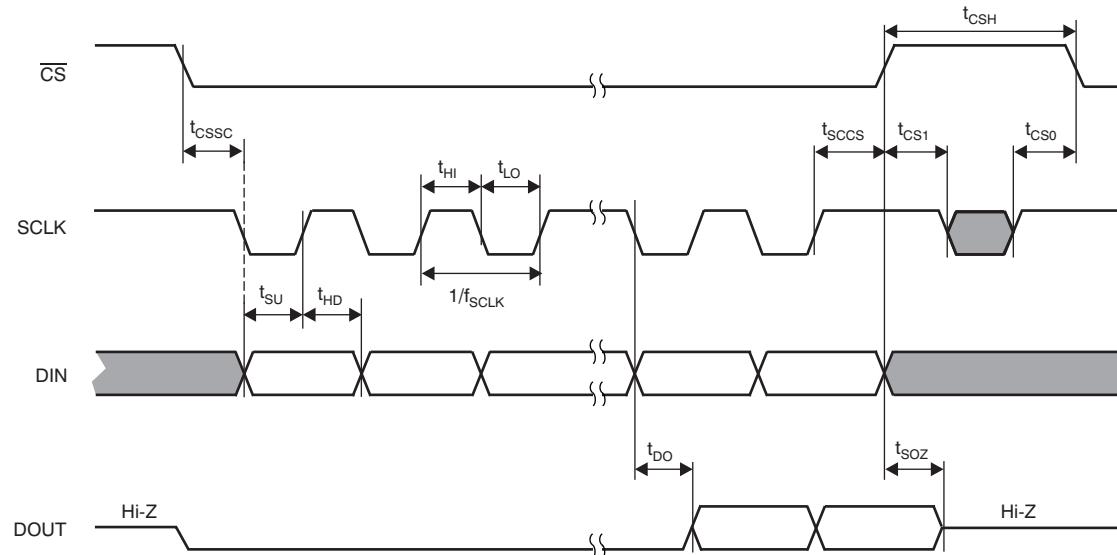

## SPI TIMING REQUIREMENTS

| PARAMETER         | MIN  | TYP | MAX | UNIT                          |

|-------------------|------|-----|-----|-------------------------------|

| Input capacitance |      | 1   |     | pF                            |

| $t_{RFI}$         |      |     | 2   | ns                            |

| $t_{RFO}$         |      |     | 10  | ns                            |

| $t_{CSH}$         | 10   |     |     | DAC_CLK cycles <sup>(1)</sup> |

| $t_{CS0}$         | 10   |     |     | ns                            |

| $t_{CSSC}$        | 10   |     |     | ns                            |

| $f_{SCLK}$        |      | 20  | 30  | MHz                           |

| $t_{HI}$          | 16.7 | 25  |     | ns                            |

| $t_{LO}$          | 16.7 | 25  |     | ns                            |

| $t_{SCCS}$        | 10   |     |     | ns                            |

| $t_{CS1}$         | 10   |     |     | ns                            |

| $t_{SU}$          | 5    |     |     | ns                            |

| $t_{HD}$          | 5    |     |     | ns                            |

| $t_{DO}$          |      |     | 16  | ns                            |

| $t_{SOZ}$         |      |     | 20  | ns                            |

- (1)  $\overline{CS}$  pin must remain high for at least ten DAC\_CLK cycles after a write operation and must remain high for at least five DAC\_CLK cycles after a read operation.

## TIMING DIAGRAMS

**Figure 1. SPI Mode 0,0**

**Figure 2. SPI Mode 1,1**

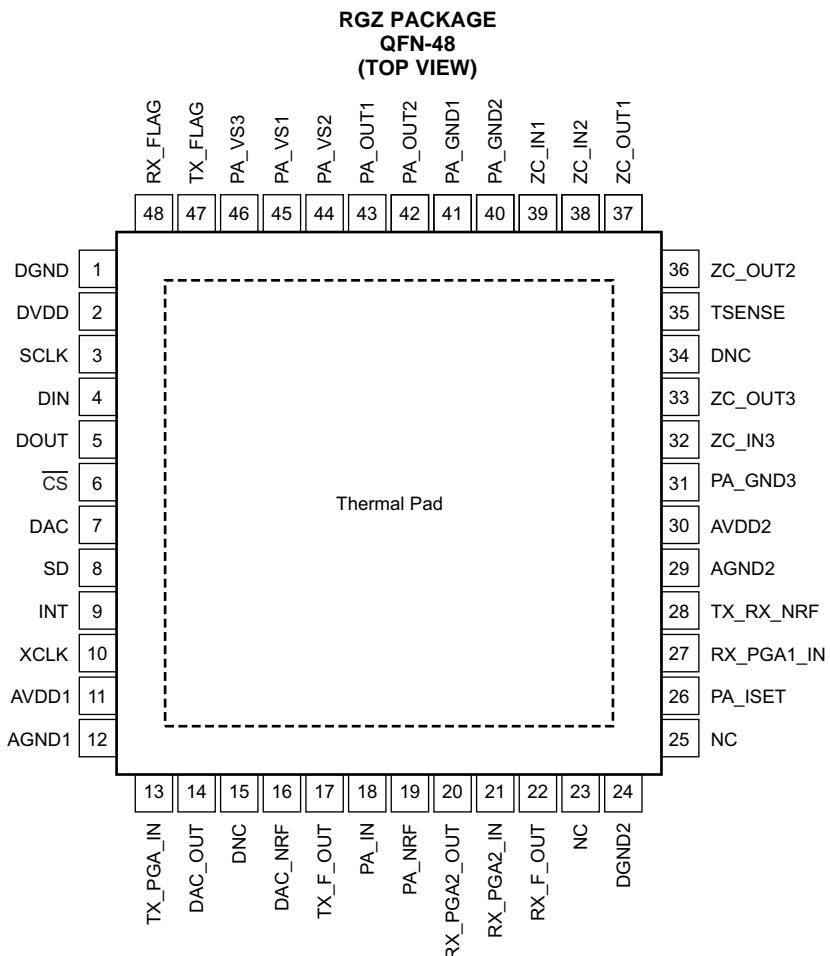

## PIN CONFIGURATION

NOTE: Connect exposed thermal pad to ground.

**PIN DESCRIPTIONS**

| NAME        | PIN NO. | DESCRIPTION                                                                                           |

|-------------|---------|-------------------------------------------------------------------------------------------------------|

| AGND1       | 12      | Analog ground                                                                                         |

| AGND2       | 29      | Analog ground                                                                                         |

| AVDD1       | 11      | Analog supply                                                                                         |

| AVDD2       | 30      | Analog supply                                                                                         |

| CS          | 6       | SPI digital chip-select input                                                                         |

| DAC         | 7       | DAC mode select digital input                                                                         |

| DAC_OUT     | 14      | DAC analog output                                                                                     |

| DAC_NRF     | 16      | DAC noise-reducing filter analog input                                                                |

| DGND        | 1       | Digital ground                                                                                        |

| DGND2       | 24      | Digital ground                                                                                        |

| DIN         | 4       | SPI digital input                                                                                     |

| DNC         | 15, 34  | Do not connect                                                                                        |

| DOUT        | 5       | SPI digital output (push or pull)                                                                     |

| DVDD        | 2       | Digital supply                                                                                        |

| INT         | 9       | Interrupt on undervoltage, undercurrent, or thermal overload (digital output, open-drain, active low) |

| NC          | 23, 25  | No internal connection (connect to GND or leave unconnected)                                          |

| PA_GND1     | 41      | Power amplifier ground                                                                                |

| PA_GND2     | 40      | Power amplifier ground (connect to PA_GND1, pin 41)                                                   |

| PA_GND3     | 31      | Power amplifier ground (connect to PA_GND1, pin 41)                                                   |

| PA_IN       | 18      | Power amplifier analog input                                                                          |

| PA_ISET     | 26      | Power amplifier current-limit adjust pin (left open if not used)                                      |

| PA_NRF      | 19      | Power amplifier noise-reducing filter analog input                                                    |

| PA_OUT1     | 43      | Power amplifier output                                                                                |

| PA_OUT2     | 42      | Power amplifier output (connect to PA_OUT1, pin 43)                                                   |

| PA_VS1      | 45      | Power amplifier supply                                                                                |

| PA_VS2      | 44      | Power amplifier supply (connect to PA_VS1, pin 45)                                                    |

| PA_VS3      | 46      | Power amplifier supply (connect to PA_VS1, pin 45)                                                    |

| RX_F_OUT    | 22      | Receiver filter analog output                                                                         |

| RX_FLAG     | 48      | Receiver ready flag (digital output, open-drain, active low)                                          |

| RX_PGA1_IN  | 27      | Receiver PGA1 analog input                                                                            |

| RX_PGA2_IN  | 21      | Receiver PGA2 analog input                                                                            |

| RX_PGA2_OUT | 20      | Receiver PGA2 analog output                                                                           |

| SCLK        | 3       | SPI serial clock input                                                                                |

| SD          | 8       | System shutdown digital input (active high)                                                           |

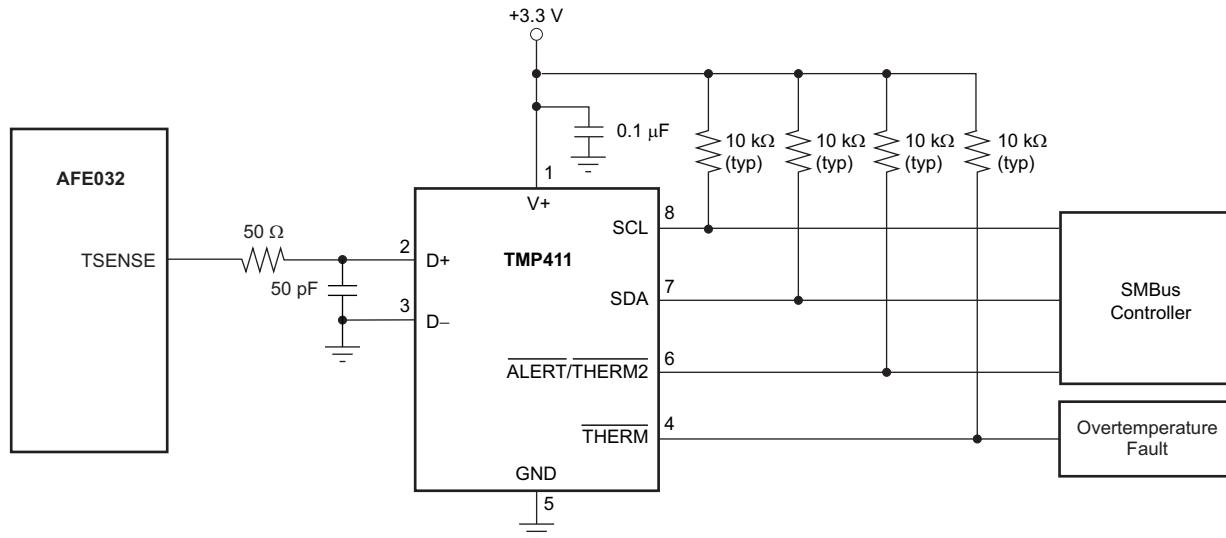

| TSENSE      | 35      | Analog temperature sensing diode (anode)                                                              |

| TX_F_OUT    | 17      | Transmit filter analog output                                                                         |

| TX_FLAG     | 47      | Transmitter ready flag (digital output, open-drain, active low)                                       |

| TX_PGA_IN   | 13      | Transmitter PGA analog input                                                                          |

| TX_RX_NRF   | 28      | Transmitter and receiver noise-reducing filter analog input                                           |

| XCLK        | 10      | DAC clock digital input                                                                               |

| ZC_IN1      | 39      | Zero-crossing detector 1, analog input                                                                |

| ZC_IN2      | 38      | Zero-crossing detector 2, analog input                                                                |

| ZC_IN3      | 32      | Zero-crossing detector 3, analog input                                                                |

| ZC_OUT1     | 37      | Zero-crossing detector 1, digital output (push or pull)                                               |

| ZC_OUT2     | 36      | Zero-crossing detector 2, digital output (push or pull)                                               |

| ZC_OUT3     | 33      | Zero-crossing detector 3, digital output (push or pull)                                               |

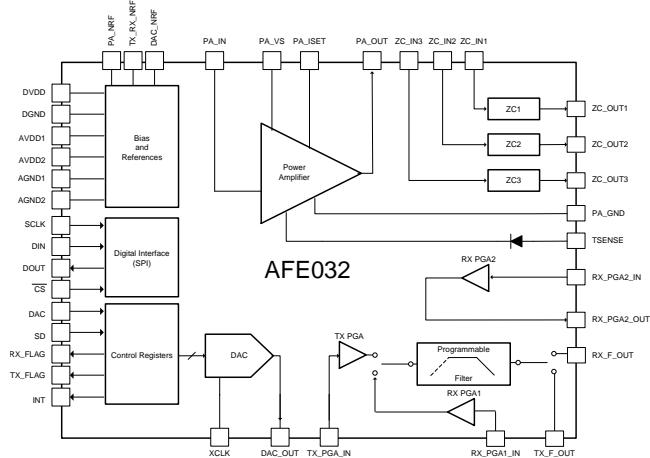

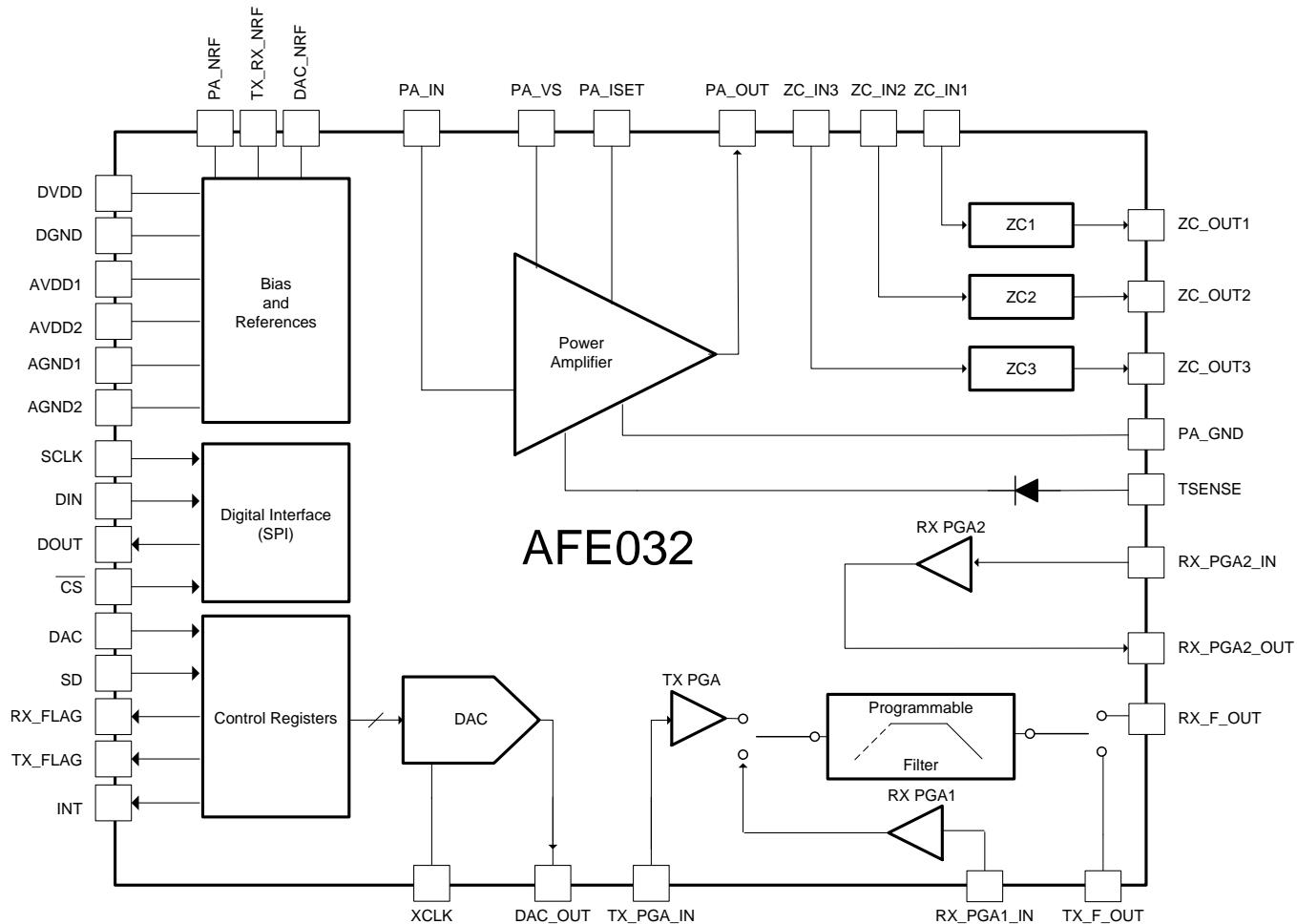

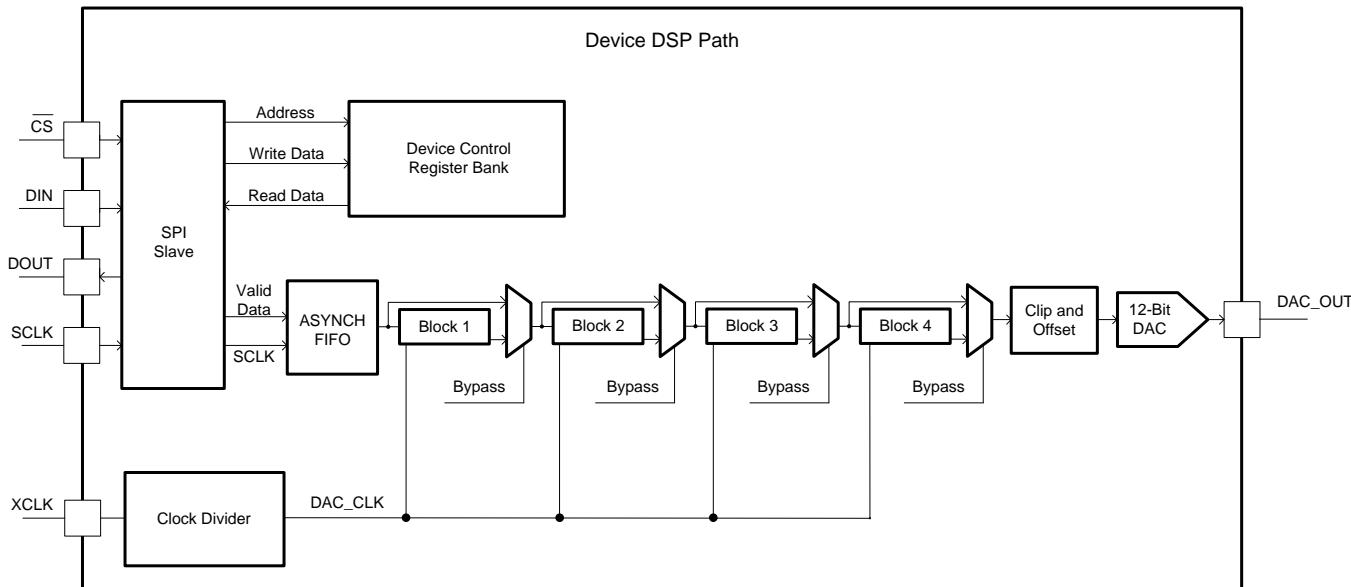

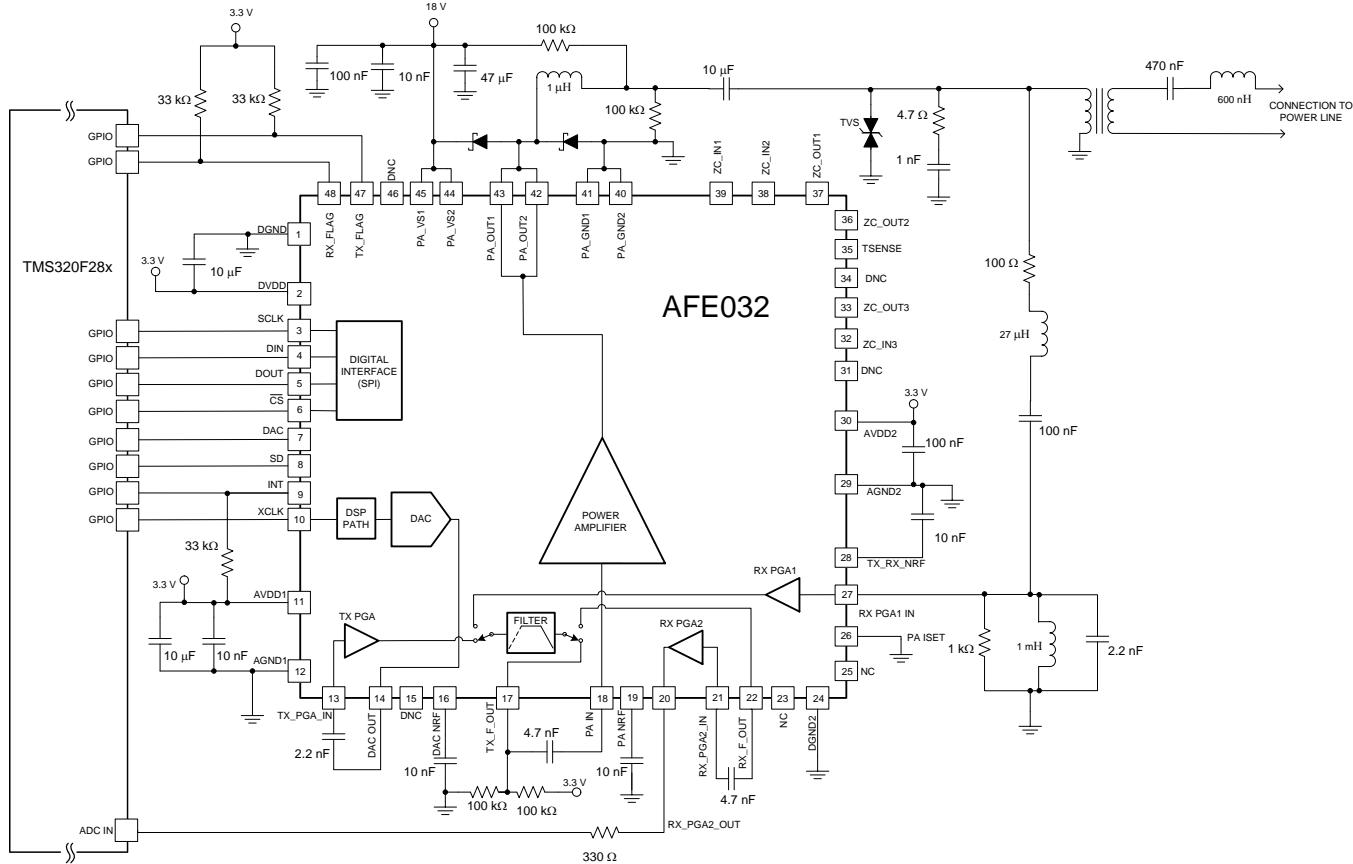

## FUNCTIONAL BLOCK DIAGRAM

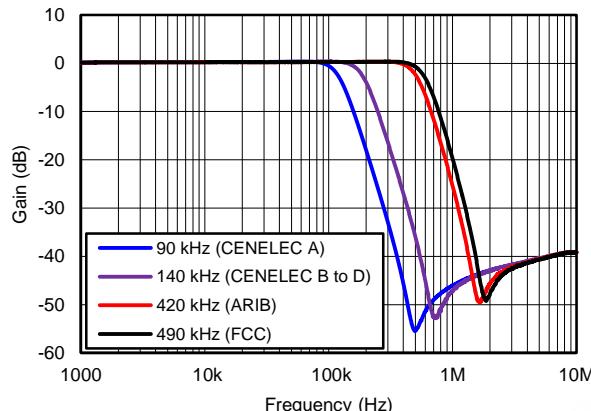

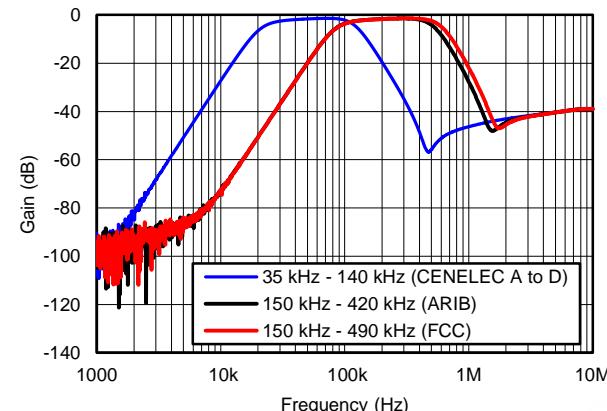

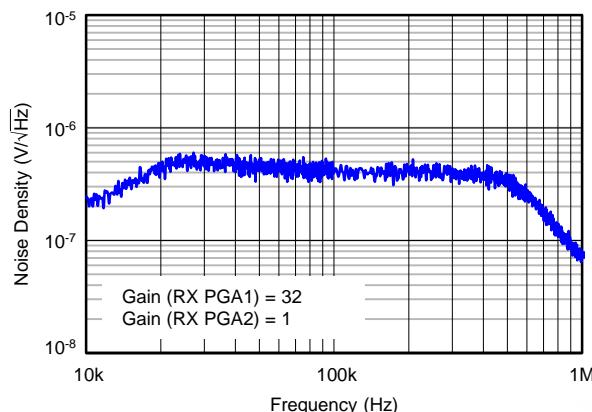

## TYPICAL CHARACTERISTICS

At  $T_J = +25^\circ\text{C}$ ,  $V_{PA\text{ V}_S} = 15\text{ V}$ , and  $V_{AVDD} = V_{DVDD} = 3.3\text{ V}$ , unless otherwise noted.

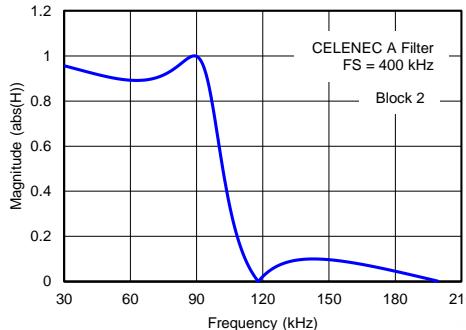

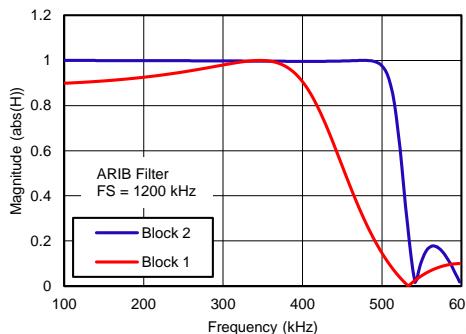

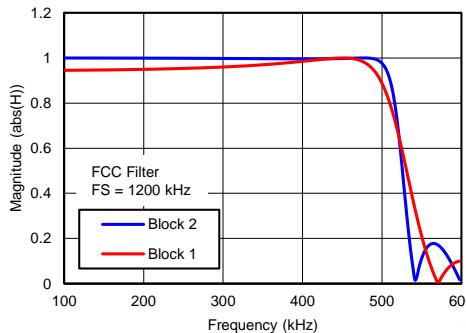

**Figure 3. Tx, Rx LOW-PASS FILTER GAIN vs FREQUENCY**

**Figure 4. Rx BAND-PASS FILTER GAIN vs FREQUENCY**

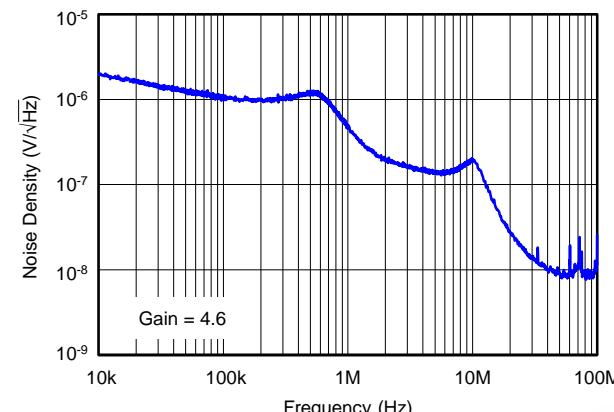

**Figure 5. Rx PATH NOISE DENSITY**

**Figure 6. Tx PATH NOISE DENSITY**

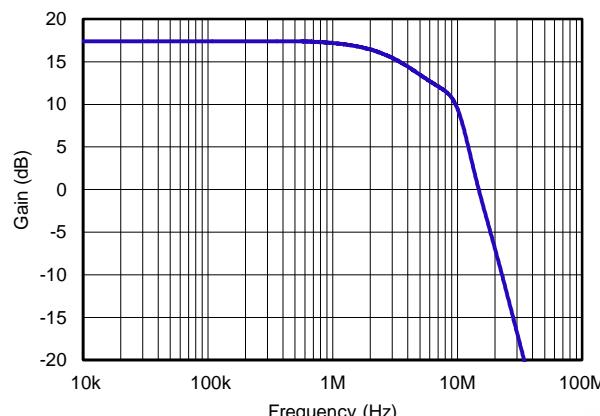

**Figure 7. PA GAIN vs FREQUENCY**

**Figure 8. PA PSRR vs FREQUENCY**

### TYPICAL CHARACTERISTICS (continued)

At  $T_J = +25^\circ\text{C}$ ,  $V_{PA\,V\,S} = 15\text{ V}$ , and  $V_{AVDD} = V_{DVDD} = 3.3\text{ V}$ , unless otherwise noted.

Figure 9. PA OUTPUT vs OUTPUT LOAD

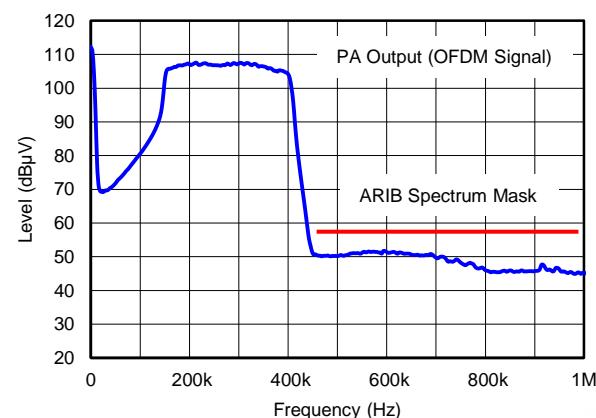

Figure 10. ARIB CONDUCTED EMISSIONS

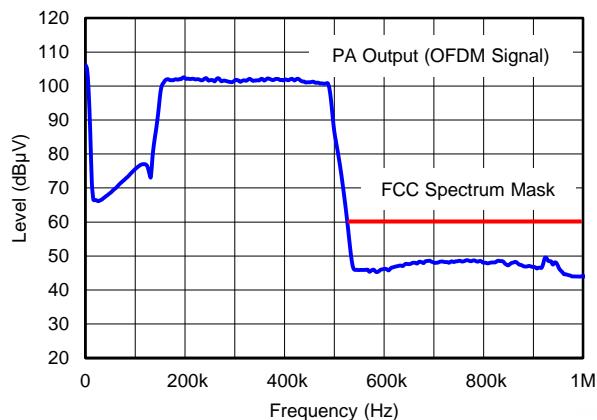

Figure 11. FCC CONDUCTED EMISSIONS

## APPLICATION INFORMATION

### GENERAL DESCRIPTION

The AFE032 is an integrated, power-line communication, analog front-end device that functions in conjunction with a microcontroller. The device conditions data generated in a microcontroller and transmits such data onto power lines through a line-coupling circuit.

The device includes several primary functional blocks:

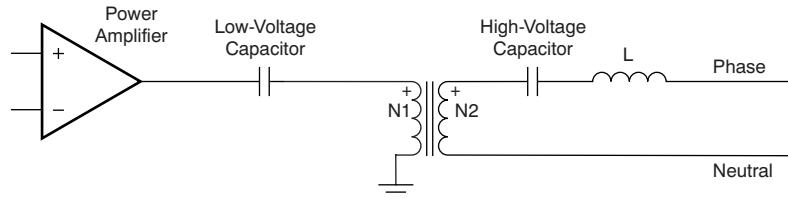

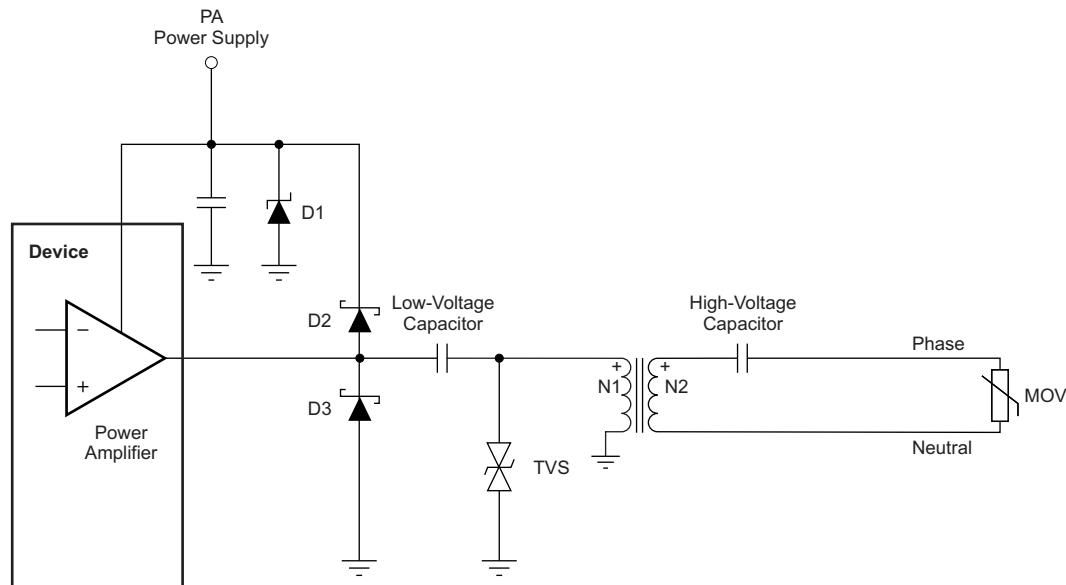

- A power amplifier (PA) transmits data onto power lines through a line-coupling circuit.

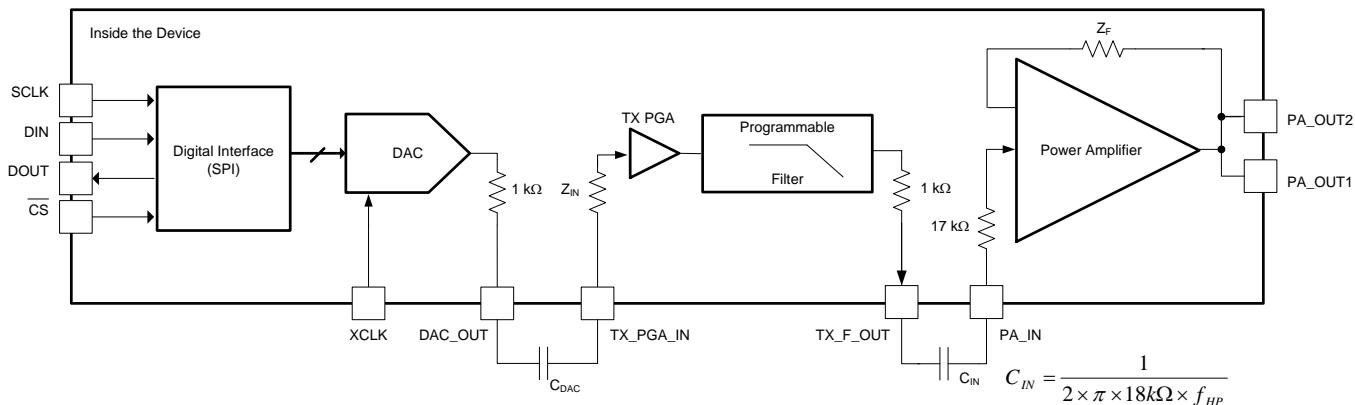

- The transmit path (Tx) consists of a high-precision, digital-to-analog converter (DAC), programmable amplifier (TX\_PGA), and low-pass filter (LPF).

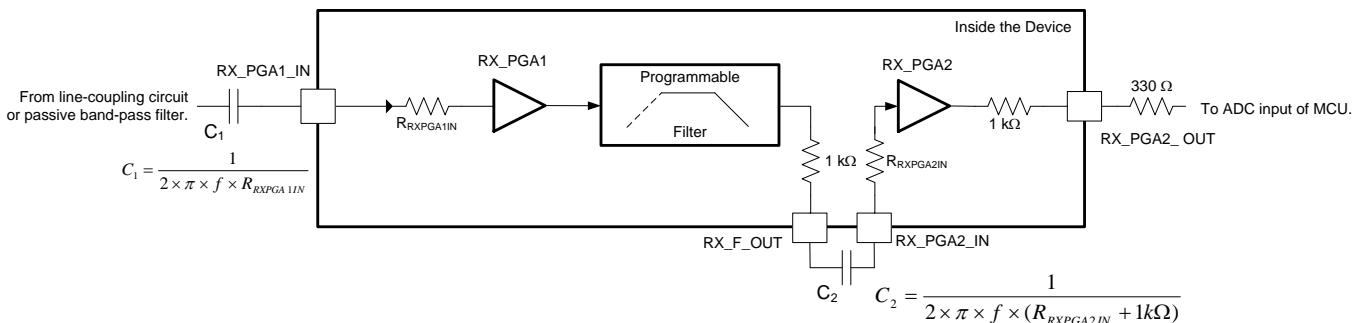

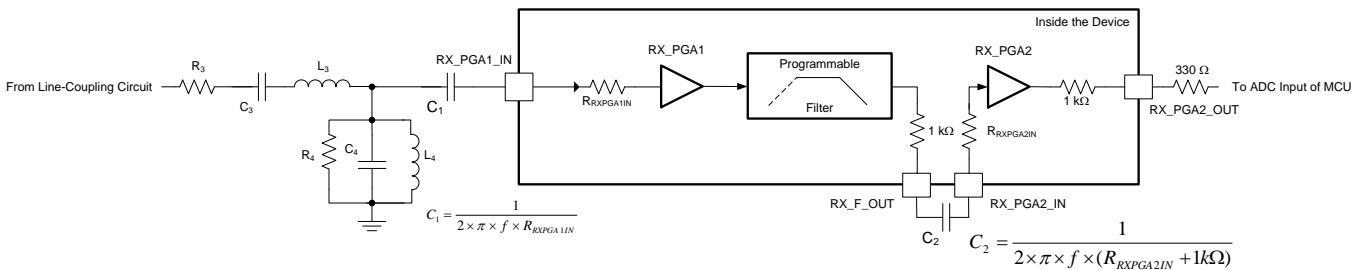

- The receive path (Rx) consists of two programmable amplifiers (RX\_PGA1 and RX\_PAG2) and a band-pass filter [(an LPF and a high-pass filter (HPF)].

### BLOCK DESCRIPTIONS

#### Power Amplifier Block

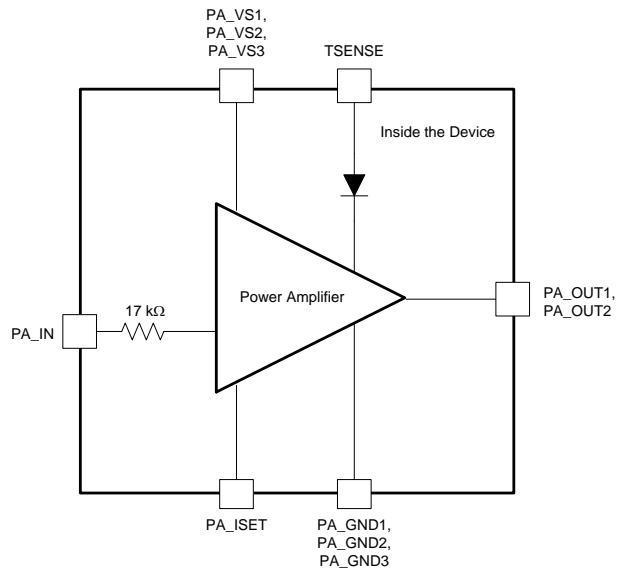

The power amplifier (PA) block consists of a high slew rate, high-voltage, and high-current operational amplifier. The PA is configured with an inverting gain of 7 V/V, has a low-pass filter response, and maintains excellent linearity and low distortion throughout its bandwidth. The PA is specified to operate from 7 V to 24 V and can deliver up to  $\pm 1.9$  A of continuous output current over the specified junction temperature range of  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ . The PA block is shown in [Figure 12](#).

**Figure 12. PA Block Equivalent Circuit**

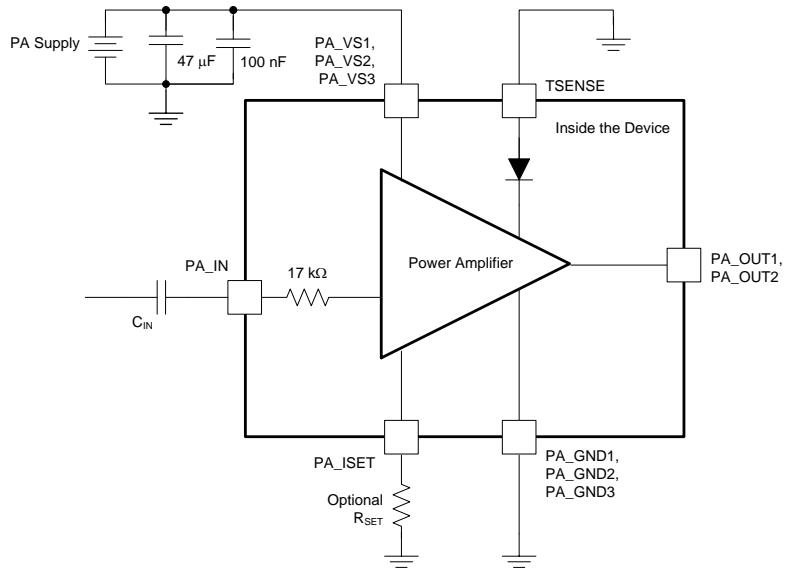

Connecting the PA in a typical power line communication (PLC) application requires few additional components. Figure 13 shows the typical connections to the PA block.

Figure 13. Typical Connections to the PA

The external capacitor ( $C_{IN}$ ) introduces a single-pole, high-pass characteristic to the PA transfer function. The  $C_{IN}$  and PA combination has a band-pass response because of the inherent low-pass transfer function from the PA. The value of the high-pass cutoff frequency is determined by  $C_{IN}$  reacting with the input resistance of the PA circuit, and can be determined by [Equation 1](#):

$$C_{IN} = \frac{1}{2 \times \pi \times 18 \text{ k}\Omega \times f_{HP}}$$

where:

- $C_{IN}$  = external input capacitor and

- $f_{HP}$  = desired high-pass cutoff frequency. (1)

For example, setting  $C_{IN}$  to 3.3 nF results in a high-pass cutoff frequency of 2.9 kHz. The voltage rating for  $C_{IN}$  should be determined to withstand operation up to the PA power-supply voltage.

When the transmitter is not in use, the output can be disabled and placed in a high-impedance state by following the procedure outlined in the [Power Amplifier Enable Sequence](#) section.

Refer to the [Initialization Sequence](#) and [Power Amplifier Enable Sequence](#) sections for details on the proper sequence when enabling the power amplifier.

### PA Current Limiting

The PA\_ISET pin (pin 26) provides a resistor-programmable output current limit for the PA block. Equation 2 determines the value of the external  $R_{SET}$  resistor attached to this pin.

$$I_{LIM} = \frac{1.2 \text{ V} \times 16.320 \text{ k}\Omega}{R_{INT} + R_{SET}}$$

where:

- $R_{SET}$  = the value of the external resistor connected between pin 26 and ground,

- $R_{INT}$  = the value of the internal resistor as programmed by the SPI interface in Table 18 (bits 4 and 5), and

- $I_{lim}$  = the value of the desired current limit for the PA. (2)

$R_{INT}$  bit setting for bits 4 and 5 in Table 18 are listed in Table 1.

**Table 1.  $R_{INT}$  Bit Settings**

| BIT SETTING | $R_{INT}$ VALUE |

|-------------|-----------------|

| 00          | 17 k $\Omega$   |

| 01          | 11 k $\Omega$   |

| 10          | 8 k $\Omega$    |

| 11          | 1.2 k $\Omega$  |

Note that there is a 30% tolerance on the  $I_{lim}$  value given by Equation 2.

### Tx Block

The Tx block consists of the Tx PGA and Tx filter.

The Tx PGA is a low-noise, high-performance, programmable gain amplifier. In DAC mode [where the DAC pin, pin 7, is a logic '1' and Tx enable (bit 4 in the REG\_RX/TX\_CTL register) is a logic '1'], the Tx PGA operates as the internal digital-to-analog converter (DAC) output buffer with programmable gain. The Tx PGA gain is programmed through the serial interface. The Tx PGA gain settings are 1.15 V/V, 2.3 V/V, 3.25 V/V, and 4.6 V/V. Gain is selectable via the TX\_PGA gain pins (bits 2 to 0 in the REG\_RX/TX\_CTL register).

The Tx filter is a unity-gain, fourth-order, low-pass filter. The Tx filter cutoff frequency is selectable between the CENELEC (bands A, B, C, or D), ARIB, or FCC modes. The LPF band select bits (bits 6 to 4 in the REG\_HPF/LPF\_CFG register) determine the cutoff frequency.

When in DAC mode, the device accepts serial data from the microprocessor and writes that data to the internal DAC registers.

Proper connections for the Tx signal path for DAC mode operation are shown in Figure 14.

(1) For the capacitor value of  $C_{IN}$ ,  $f_{HP}$  is the desired lower cutoff frequency and 17 k $\Omega$  is the PA input resistance.

**Figure 14. Recommended Tx Signal Chain Connections**

The capacitors listed in [Figure 14](#) should be rated to withstand the full AVDD power-supply voltage for  $C_{DAC}$  and  $PA_{VS}$  for  $C_{IN}$ .

### Rx Block

The Rx block consists of the Rx PGA1, Rx filter, and Rx PGA2. Both Rx PGA1 and Rx PGA2 are high-performance programmable gain amplifiers that can be configured through the SPI interface.

Rx PGA1 can operate as either an attenuator or in gain. The Rx PGA1 gain steps are 0.125 V/V, 0.25 V/V, 0.5 V/V, 1 V/V, 2 V/V, 4 V/V, 8 V/V, 16 V/V, and 32 V/V. Gains are selectable with the RX\_PGA1 gain bits (bits 7 to 4 in the REG\_RXPGA\_CFG register). Configuring the Rx PGA1 as an attenuator (at gains less than 1 V/V) is useful for applications where large interference signals are present within the signal band. Attenuating the large interference allows these signals to pass through the analog Rx signal chain without causing an overload; the interference signal can then be processed and removed within the microprocessor as necessary. Similarly, if a transmitter is located close to the receiver, gains less than 1 V/V may be needed.

The Rx PGA2 gain steps are 1 V/V, 4 V/V, and 16 V/V. Gains are selectable through the RX\_PGA2 gain bits (bits 3 to 1 in the REG\_RXPGA\_CFG register).

The Rx filter is a very low-noise, unity-gain, fourth-order, low-pass or band-pass filter. The Rx filter cutoff frequency is selectable between the CENELEC (bands A, B, C, or D), ARIB, or FCC modes. The LPF band select bits (bits 6 to 4 of the REG\_HPF/LPF\_REG register) determine the cutoff frequency for the LPF. The HPF band select bits (bits 1 and 2 of the REG\_HPF/LPF\_REG register) set up the cutoff frequency of the HPF.

Recommended connections for the Rx signal chain are shown in [Figure 15](#).

(1) For capacitor value  $C_1$ ,  $f$  is the desired lower cutoff frequency and  $R_{RXPGA1IN}$  is the input resistance of RX\_PGA1.

(2) For capacitor value  $C_2$ ,  $f$  is the desired lower cutoff frequency and  $R_{RXPGA2IN}$  is the input resistance of RX\_PGA2.

**Figure 15. Recommended Connections for Rx Signal Chain**

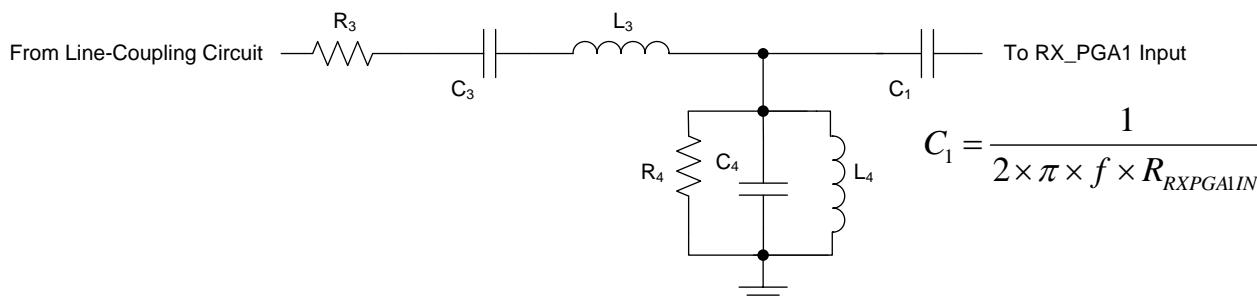

[Figure 16](#) shows, a fourth-order, passive band-pass filter that is optional but recommended for applications with high performance needs. The external passive band-pass filter removes unwanted, out-of-band signals from the signal path, and it prevents such signals from reaching the active internal filters within the device.

(1) For capacitor value  $C_1$ ,  $f$  is the desired lower cutoff frequency and  $R_{RXPGA1IN}$  is the input resistance of RX\_PGA1.

**Figure 16. Passive Band-Pass Rx Filter**

The following steps can be used to quickly design the passive pass-band filter. (Note that these steps produce an approximate result.)

1. Choose the filter characteristic impedance,  $Z_C$ :

- For a -6-db passband attenuation:  $R_3 = R_4 = Z_C$ .

- For a 0-db passband attenuation:  $R_4 = Z_C$ ,  $R_3 = 10 \times Z_C$ .

2. Calculate values for  $C_3$ ,  $C_4$ ,  $L_3$ , and  $L_4$  using the following equations:

$$C_3 = \frac{1}{2 \times \pi \times f_3 \times Z_C}$$

$$C_4 = \frac{1}{2 \times \pi \times f_4 \times Z_C}$$

$$L_3 = \frac{Z_C}{2 \times \pi \times f_3}$$

$$L_4 = \frac{Z_C}{2 \times \pi \times f_4}$$

[Table 2](#) and [Table 3](#) show standard values for common applications.

**Table 2. Recommended Component Values for Fourth-Order Passive Band-Pass Filters (0-dB Pass-Band Attenuation)**

| FREQUENCY BAND  | FREQUENCY RANGE (kHz) | CHARACTERISTIC IMPEDANCE | R3    | R4 (kΩ) | C3 (nF) | C4 (nF) | L3 (μH) | L4 (μH) |

|-----------------|-----------------------|--------------------------|-------|---------|---------|---------|---------|---------|

| CENELEC A       | 35 to 95              | 1 kΩ                     | 1 kΩ  | 10      | 4.7     | 1.5     | 1500    | 4700    |

| CENELEC B, C, D | 95 to 150             | 1 kΩ                     | 1 kΩ  | 10      | 1.7     | 1       | 1200    | 1500    |

| SFSK            | 63 to 74              | 1 kΩ                     | 1 kΩ  | 10      | 2.7     | 2.2     | 2200    | 2200    |

| FCC and ARIB    | 15 to 600             | 100 Ω                    | 100 Ω | 1       | 100     | 2.2     | 27      | 1000    |

**Table 3. Recommended Component Values for Fourth-Order Passive Band-Pass Filters (-6-dB Pass-Band Attenuation)**

| FREQUENCY BAND  | FREQUENCY RANGE (kHz) | CHARACTERISTIC IMPEDANCE | R3    | R4    | C3 (nF) | C4 (nF) | L3 (μH) | L4 (μH) |

|-----------------|-----------------------|--------------------------|-------|-------|---------|---------|---------|---------|

| CENELEC A       | 35 to 95              | 1 kΩ                     | 1 kΩ  | 1 kΩ  | 4.7     | 1.5     | 1500    | 4700    |

| CENELEC B, C, D | 95 to 150             | 1 kΩ                     | 1 kΩ  | 1 kΩ  | 1.7     | 1       | 1200    | 1500    |

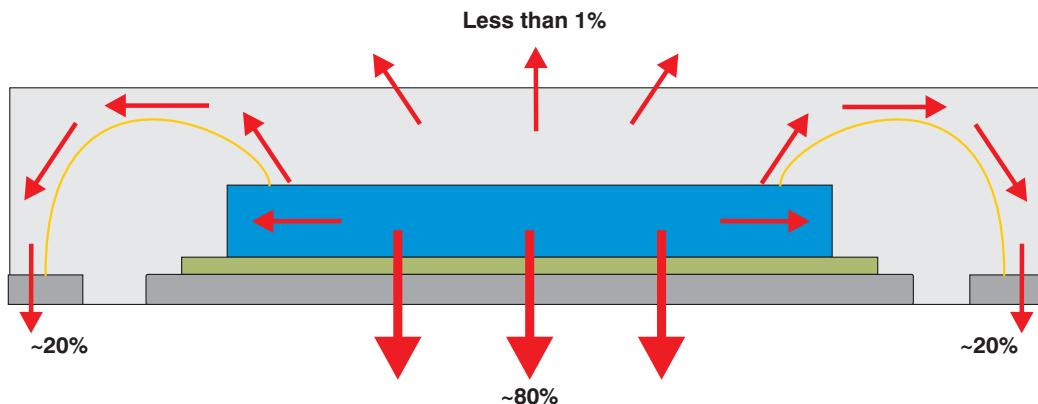

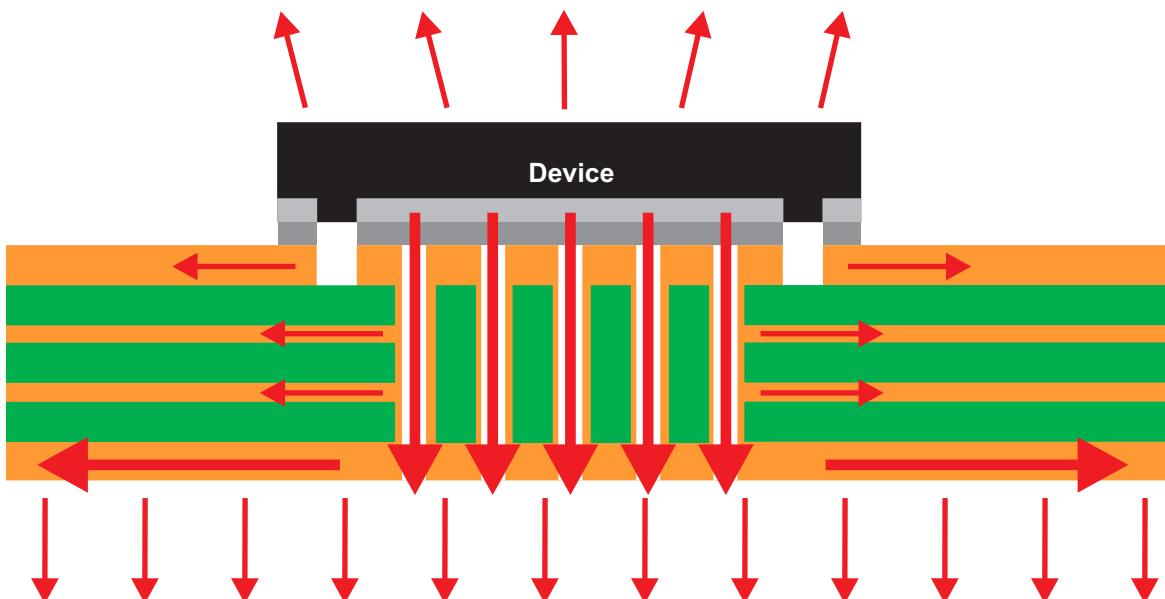

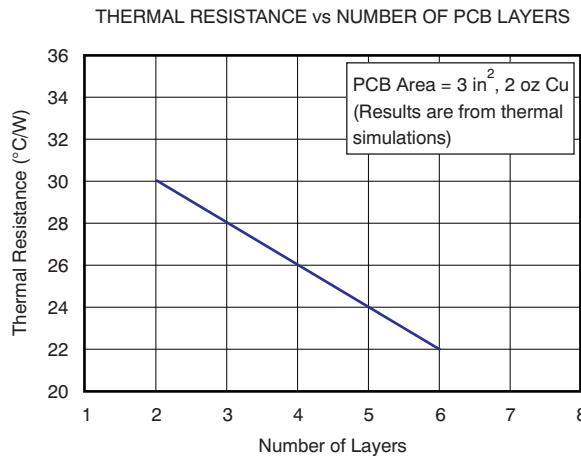

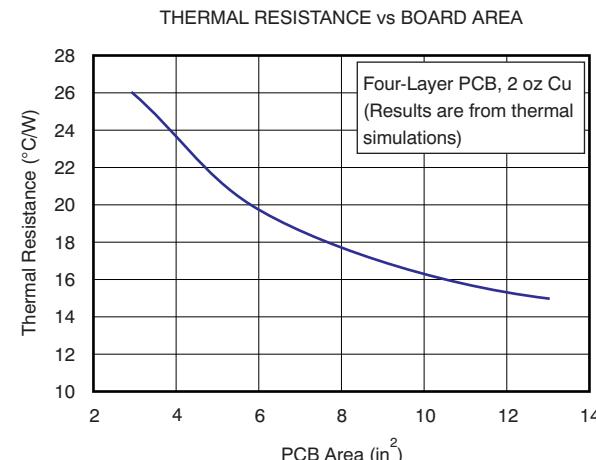

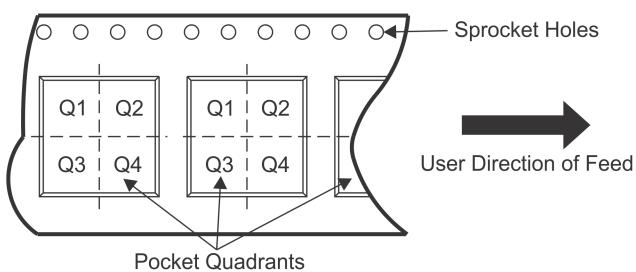

| SFSK            | 63 to 74              | 1 kΩ                     | 1 kΩ  | 1 kΩ  | 2.7     | 2.2     | 2200    | 2200    |