ZHCSQN6 May 2022 ADC3644

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics - Power Consumption

- 6.6 Electrical Characteristics - DC Specifications

- 6.7 Electrical Characteristics - AC Specifications

- 6.8 Timing Requirements

- 6.9 Typical Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application Information Disclaimer

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

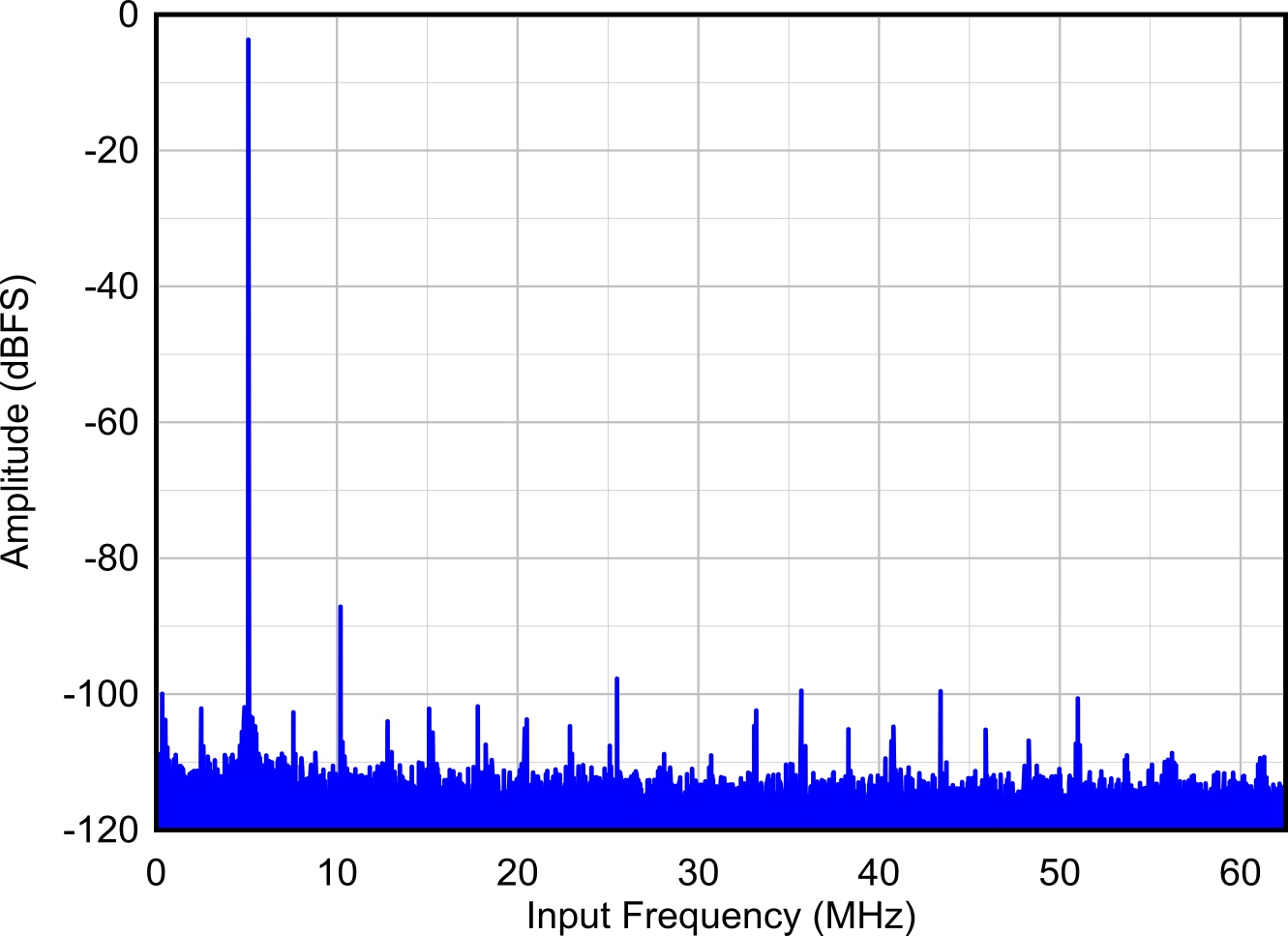

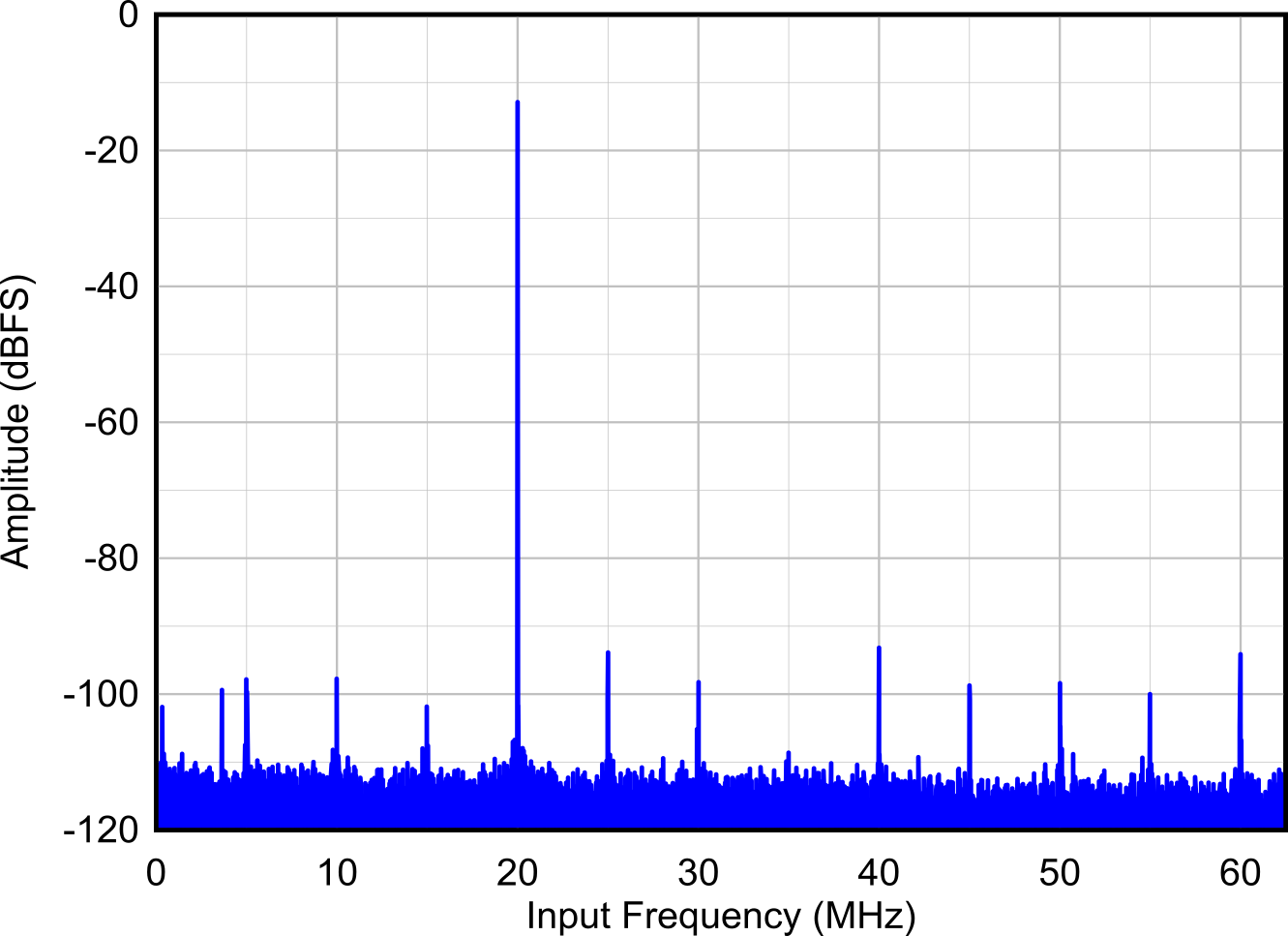

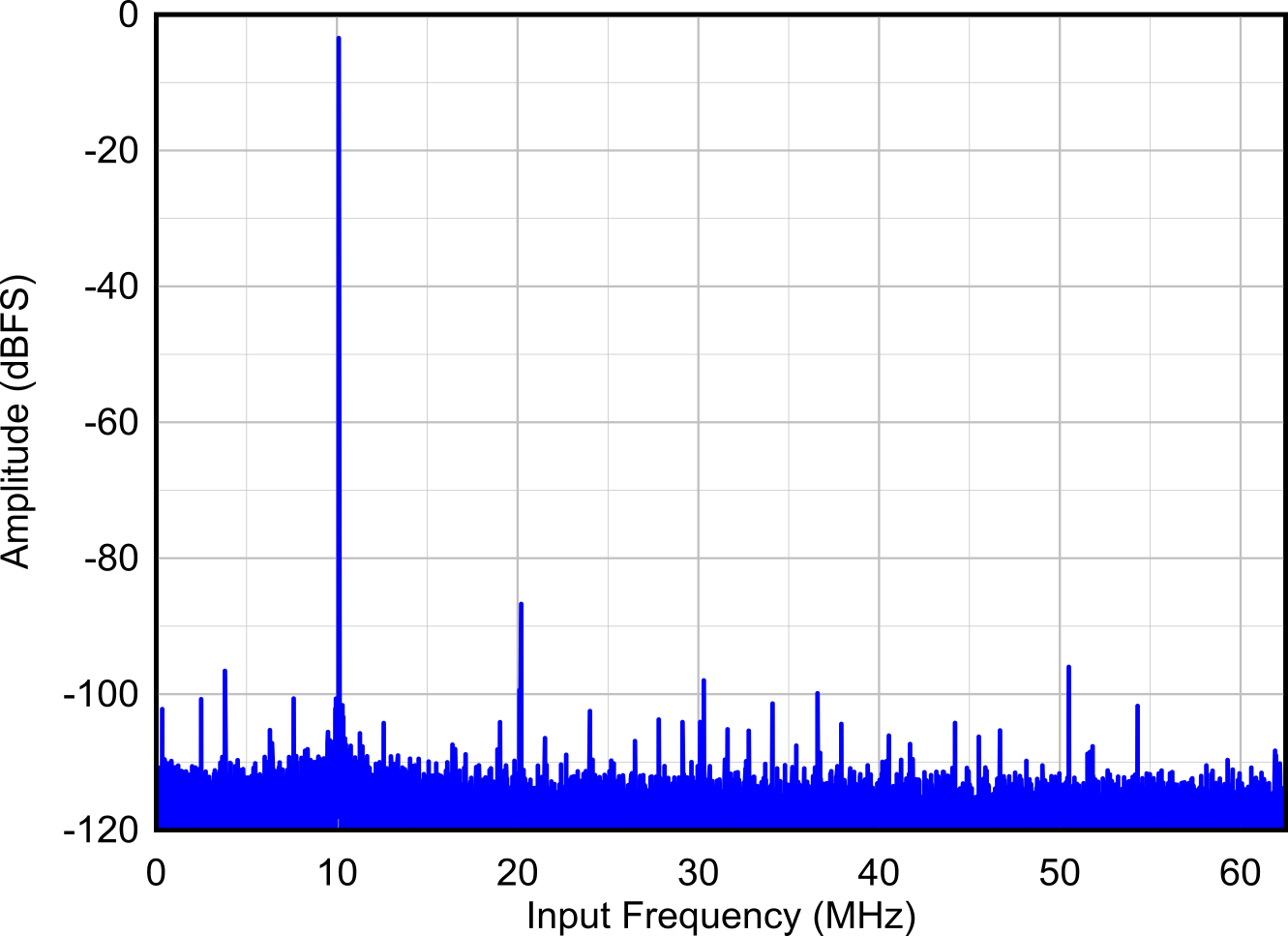

9.1.3 Application Curves

The following FFT plots show the performance of THS4541 driving the ADC3644 operated at 125 MSPS with a full-scale input at -1 dBFS. The FFT spectrum also shows the response of the low pass filter located between the THS4541 and the glitch filter with a 30 MHz corner frequency.

| AIN = - 1 dBFS, SNR = 73.2 dBFS, SFDR = 84 dBFS |

| AIN = - 10 dBFS, SNR = 73.5 dBFS, SFDR = 90 dBFS |

| AIN = - 1 dBFS, SNR = 73 dBFS, SFDR = 84 dBFS |