# High Volume Power Supply design meets collaboration

[High side bias challenges and solutions in half bridge gate drivers] [Ritesh Oza]

## What will I get out of this session?

• Purpose:

Understand various challenges associated with high side bias design in half bridge gate driver circuits. The presentation will also propose solutions to those challenges.

- Part numbers mentioned:

- UCC27282, UCC27201/11/12

- LM510x

- Reference designs mentioned:

- TIDM-AUTO-DC-LED-LIGHTING

- Relevant End Equipment's:

- Telecom power supplies

- Automotive Headlights

- Drones, Motor Drives, etc....

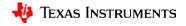

Ways to generate high side bias for half-bridge circuit?

- A) Bootstrap

- B) Gate Driver Transformer

- C) Windings off of the flyback

- D) Buck conversion from the input/output

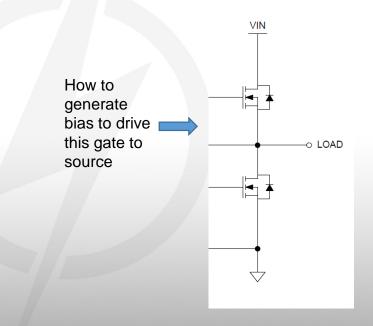

Bootstrap supply charging/discharging operation

Bootstrap supply charging/discharging operation

Key parts/components of bootstrap supply/bias?

- A) Bootstrap Diode

- B) Bootstrap Capacitor

- C) Charging/Discharging Element

- D) Supply Capacitor

#### Key influencers in bootstrap supply design

- Gate charge of the MOSFET to be driven

- Bias voltage

- Allowed ripple and discharge during switching

- Switching frequency

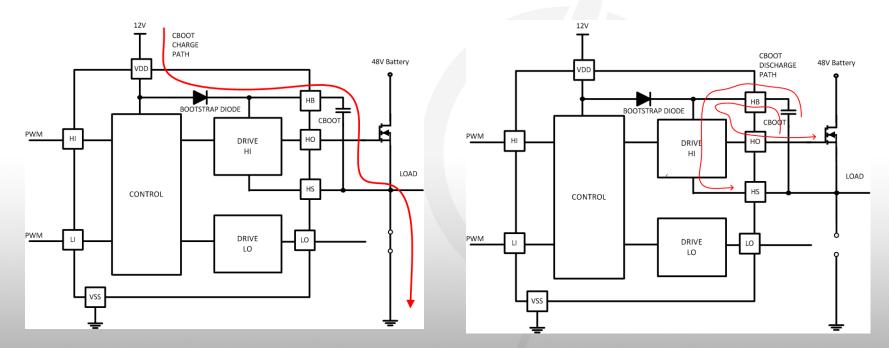

- Maximum high-side pulse width

- Minimum low-side pulse width

#### Basic bootstrap capacitor design equations

$\Delta V_{\text{HB}} = V_{\text{DD}} - V_{\text{DH}} - V_{\text{HBL}}$

where

- $V_{DD}$  = Supply voltage of the gate drive IC

- V<sub>DH</sub> = Bootstrap diode forward voltage drop

- $V_{HBL} = V_{HBRmax} V_{HBH}$ , HB falling threshold

$$Q_{\mathsf{Total}} = Q_{\mathsf{G}} + \mathsf{I}_{\mathsf{HBS}} \times \frac{\mathsf{D}_{\mathsf{Max}}}{f_{\mathsf{SW}}} + \frac{\mathsf{I}_{\mathsf{HB}}}{f_{\mathsf{SW}}}$$

where

- Q<sub>G</sub> = Total MOSFET gate charge

- I<sub>HBS</sub> = HB to VSS Leakage current

- D<sub>Max</sub> = Converter maximum duty cycle

- I<sub>HB</sub> = HB Quiescent current

#### Absolute Minimum Value of Bootstrap Capacitor

$$C_{\text{Boot}} = \frac{Q_{\text{Total}}}{\Delta V_{\text{HB}}}$$

## Effect of value of bootstrap capacitor

- Ripple voltage

- Diode peak current

- Operating voltage range

- Value of gate to source resistance

- Operating range of duty cycle

- Switching frequency

- Low side minimum pulse width

#### No high frequency filter capacitor on HB

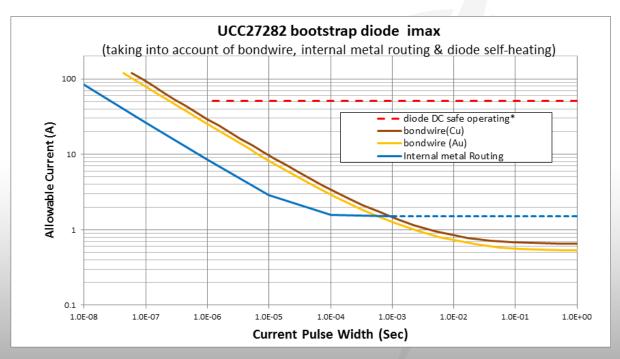

Factors affecting boot diode peak forward current capability

- Diode dynamic impedance

- Value of bootstrap capacitor

- Voltage needed to be charged

- Charging pulse width

- Rds(on) of the charging MOSFET

- Any other series impedance

- Not a datasheet parameter

- Can be modeled and simulated

$$Vpk = C \frac{dV}{dt}$$

$$pk = \frac{dV}{Rdynamic}$$

#### Simulation of Boot diode peak forward current capability

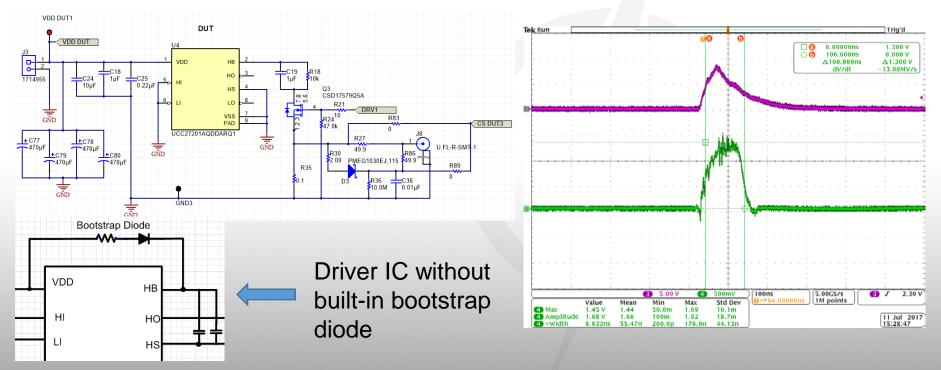

#### Bench testing of boot diode peak forward current capability

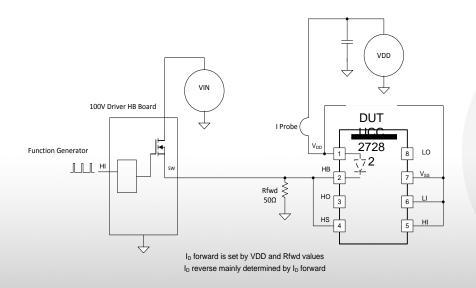

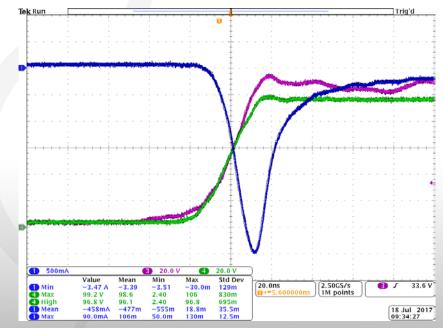

Factors affecting boot diode peak reverse current capability

- Diode forward current

- Diode reverse bias voltage

- Bootstrap capacitor value

- Not a datasheet parameter

- Not easy to simulate at IC level

Bench testing of Boot diode peak reverse current capability

Solution: Clamp LO minimum pulse width or place external Schottkey diode

🔱 Texas Instruments

Effect of frequency, pulse width, UVLO delay, & temperature

- High switching frequency -> Low value bootstrap capacitor

- Low switching frequency -> High value bootstrap capacitor

- Very High switching frequency -> External Schottkey bootstrap diode option

- High switching frequency -> Additional low profile, low value, high frequency bypass bootstrap capacitor

- Temperature

- UVLO Delay

- Gate to source resistor and other external leakage path from HS to VSS

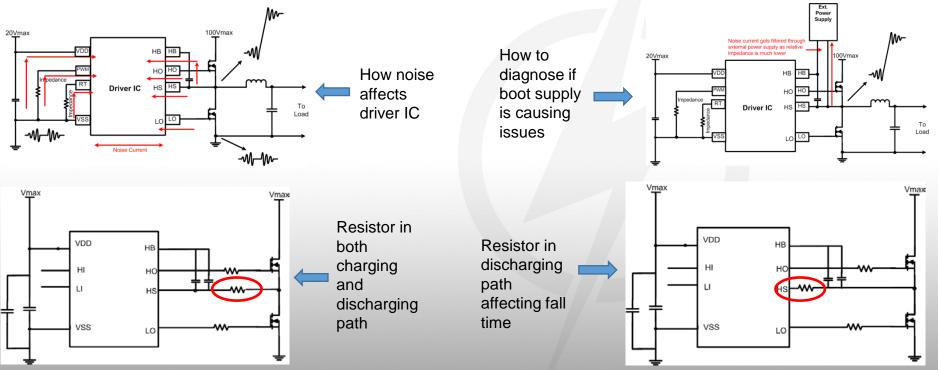

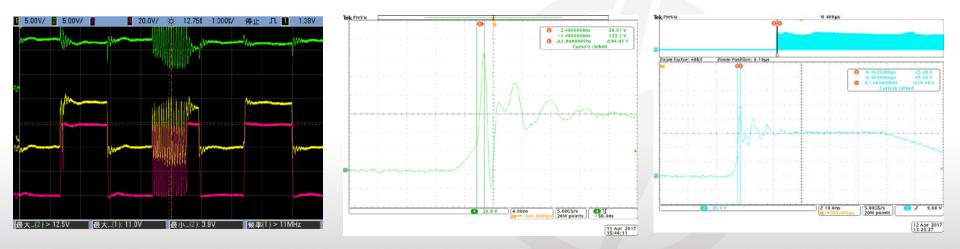

#### Effect of switch Node slew rate and noise

#### Effect of switch node slew rate and solution

CH1=HO-HS, CH2=HB-HS, CH4=HS

High dV/dt on HS pin, 90V/ns, Cb=0.1uF

High dV/dt on HS pin, 90V/ns, Cb=22nF

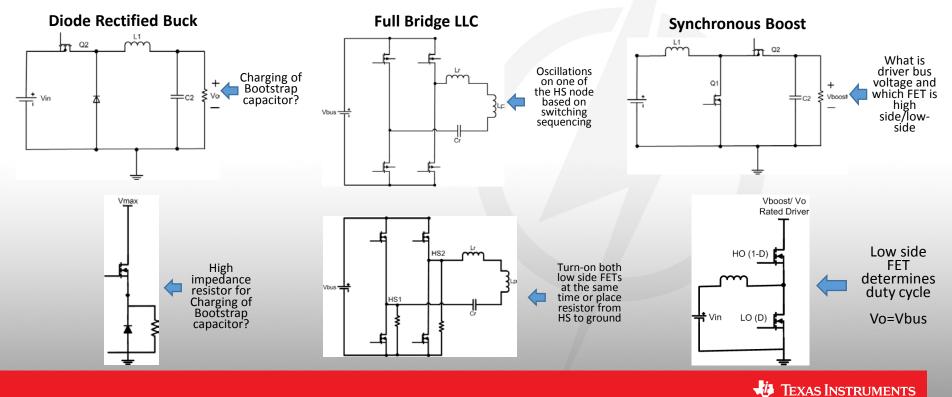

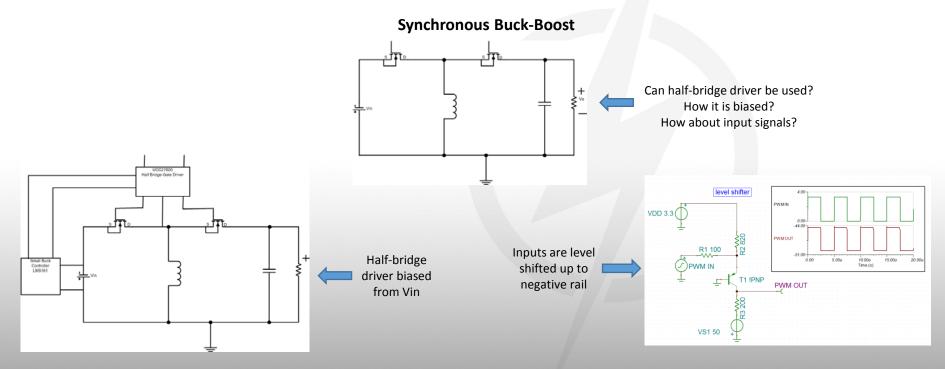

Bridge driver and boot supply challenges with topologies

Bridge driver and boot supply challenges with topologies

#### Summary

- There are multiple variables as well as multiple operating conditions that need to be considered while designing a bootstrap supply around half-bridge gate driver.

- Bootstrap diode characteristics such as peak forward and reverse current, play an important role in reliable operation of the bootstrap diode and also HB driver.

- Optimum bootstrap capacitor need to be selected based on overall system operation.

- Switching frequency and pulse width has impact on bootstrap bias design

- Topology and switching pattern also need to be considered while selecting half bridge driver as well as designing bootstrap bias supply

- Thank you

- Ritesh Oza

- Systems Engineer

- r-oza@ti.com

© Copyright 2017 Texas Instruments Incorporated. All rights reserved.

This material is provided strictly "as-is," for informational purposes only, and without any warranty. Use of this material is subject to TI's **Terms of Use**, viewable at TI.com