# TLV40x1EVM

The TLV40x1 devices are MicroPower, high-accuracy comparators with an internal 0.2V or 1.2V reference and propagation delay of 450ns. The comparators are available in an ultra-small, WCSP package measuring 0.73 mm  $\times$  0.73 mm. The TLV40x1EVM is intended to make it easier to evaluate or to integrate the device in the user's prototype system.

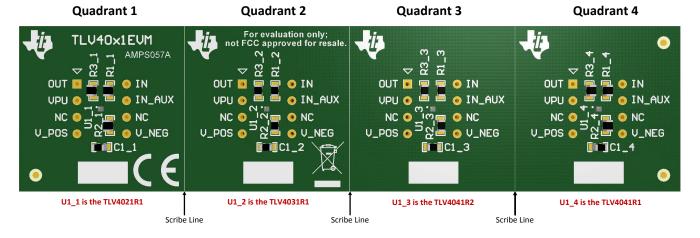

The EVM is comprised of four identical layouts (quadrants) where a different TLV40x1 device can be installed. For user flexibility, each quadrant can be conveniently detached from the other quadrants by flexing the EVM at the provided scribe lines. The shipped EVM has the TVL4021R1, TLV4031R1, TLV4041R2, and TLV4041R1 installed in quadrants (I to IV) respectively.

The EVM board provides mounting holes which are compatible to an industry standard DIP package. A 8-pin DIP socket, common 0.1 inch pin headers, or wires can be installed depending on the user's integration requirement.

Figure 1. TLV40x1EVM Board Top View

#### Contents

| 1 | TLV40x1EVM Block Diagram                                      |

|---|---------------------------------------------------------------|

|   | How to Use the TLV40x1EVM for Evaluation or System Prototypes |

|   | 2.1 Usage Example                                             |

|   | TI V40x1EVM Schematic                                         |

#### 1 TLV40x1EVM Block Diagram

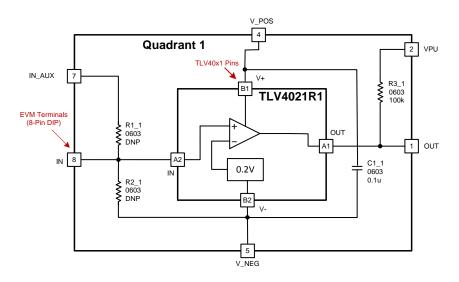

The block diagram for each Quadrant is identical with each Quadrant having a different TLV40x1 device populated. For example, Quadrant 1 is populated with the TLV4021R1, Quadrant 2 is populated with the TLV4031R1, Quadrant 3 is populated with the TLV4041R2. and Quadrant 4 is populated with the TLV4041R1. See *Table 2* for a description of each TLV40x1 family member.

Figure 2. Block Diagram

Table 1. TLV40x1 and EVM "Quadrant" Board Signals

| TL40x1     | DEVICE      | TLV40x1EVM DIP HOLES |               |

|------------|-------------|----------------------|---------------|

| PIN NUMBER | SIGNAL NAME | PIN NUMBER           | SIGNAL NAME   |

| A1         | OUT         | 1                    | OUT           |

| B1         | V+          | 4                    | V_POS         |

| B2         | V-          | 5                    | V_NEG         |

| A2         | IN          | 8                    | IN            |

|            |             | 7                    | IN_AUX        |

|            |             | 2                    | VPU           |

|            |             | 3, 6                 | No Connection |

Table 2. TLV40x1 Truth Table

| DEVICE                 | REFERENCE<br>VOLTAGE | INPUT<br>CONFIGURATION | OUTPUT<br>TOPOLOGY |

|------------------------|----------------------|------------------------|--------------------|

| TLV4021R2<br>TLV4021R1 | 0.2V<br>1.2V         | Non-Inverting          | Open-Drain         |

| TLV4031R2<br>TLV4031R1 | 0.2V<br>1.2V         | Inverting              | Open-Drain         |

| TLV4041R2<br>TLV4041R1 | 0.2V<br>1.2V         | Non-Inverting          | Push-Pull          |

| TLV4051R2<br>TLV4051R1 | 0.2V<br>1.2V         | Inverting              | Push-Pull          |

#### 2 How to Use the TLV40x1EVM for Evaluation or System Prototypes

The TLV40x1EVM quadrant is assembled with the TLV40x1 device, a 0.1  $\mu$ F ceramic capacitor (in 0603 package), and a 100 k $\Omega$  pull-up resistor (only for Quadrants I & II). If the application needs to scale down the input voltage to a lower value, a pair of resistors R1 and R2 can be installed by the user. In this case, connect the voltage to be monitored to IN\_AUX (DIP PIN 7) instead of IN (DIP PIN 8).

Depending on the user's setup or requirement, a standard 8-pin DIP socket or 0.1-inch pin headers may be installed. Users may also solder wires directly to the DIP holes.

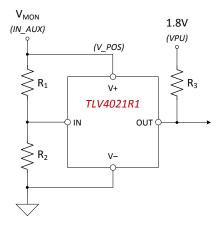

#### 2.1 Usage Example

Figure 3 shows a typical use case of TLV4021R1 as an undervoltage monitor. Resistors R1 and R2 need to be installed on the EVM and the voltage to be monitored is applied to IN\_AUX (DIP PIN 7). The configuration detects an undervoltage condition when the input voltage at IN\_AUX drops below 2 V. The output pull-up resistor R3 is connected to a 1.8 V supply through VPU (DIP PIN2). The example assumes that the logic device that is connected to the output of the comparator operates at 1.8 V.

Figure 3. Usage Example

Listed below is the equation for deriving values for R1 and R2. For more details on this application, please refer to the Applications Section of the TLV4021 datasheet

$$R_1 = \frac{(V_{TH} - V_{IT-})}{V_{IT-}} \times R_2 \tag{1}$$

TLV40x1EVM Schematic www.ti.com

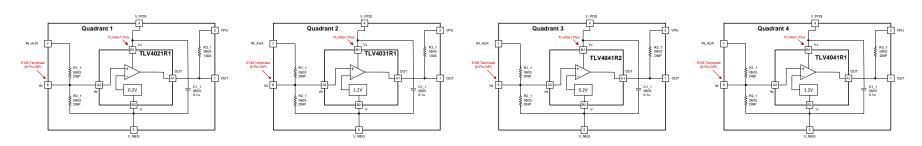

### 3 TLV40x1EVM Schematic

Figure 4. TLV40x1EVM Schematic

www.ti.com Revision History

## **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Original (September 2019) to A Revision

Page

• Changed the BOM for the EVM. All 4 Quadrants are now populated with different devices from the TLV40x1 family..... 2

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated