*Application Note*

# 对直流频段进行采样：设计用于高速 ADC 的直流耦合放大器前端

Rob Reeder

## 摘要

有时，使用高速射频转换器在该直流区域进行下采样感觉像是一项神秘任务，但实际上要简单得多。许多高速转换器的数据表实际上并未表示可以进行直流采样，因为大多数高速和射频转换器的数据表性能规格都以 10MHz 为起点，该值接近于直流但却并非真正的直流。这里的难题是高速通常意味着交流耦合。转换器数据表可能仍保留了一些直流规格，因为其中许多规格都是在使用过程中被弃用或者只是被忽略，更有甚者，它们变得更加模糊而无法解释。当 ADC 的重点市场或应用是 K 频段直接采样时，谁还会想对 DC 频段进行采样？本文摒弃了这类想法，并提供了分步指南，使下一次直流耦合高速信号链设计尝试富有成效！

## 内容

|                        |    |

|------------------------|----|

| 1 简介                   | 2  |

| 2 查找合适的放大器             | 3  |

| 3 了解 ADC 及类型           | 4  |

| 4 同时模拟 FDA 和 ADC 以避免缺陷 | 6  |

| 5 实现直流耦合福音的五个步骤        | 8  |

| 6 总结                   | 15 |

| 7 参考资料                 | 15 |

## 商标

所有商标均为其各自所有者的财产。

## 1 简介

在许多情况下，设计人员需要使用高速转换器实现两个功能：以更高速度采样（涵盖射频频率区域中某些部分的兆采样或千兆采样）以及直流采样。直流频段也可以为设计人员提供一些有用的信息。这可以是传感器电平或高频脉冲波形上的直流值，其中该脉冲内的直流电平为系统提供了一些有用信息，以做出更高级别的决策。

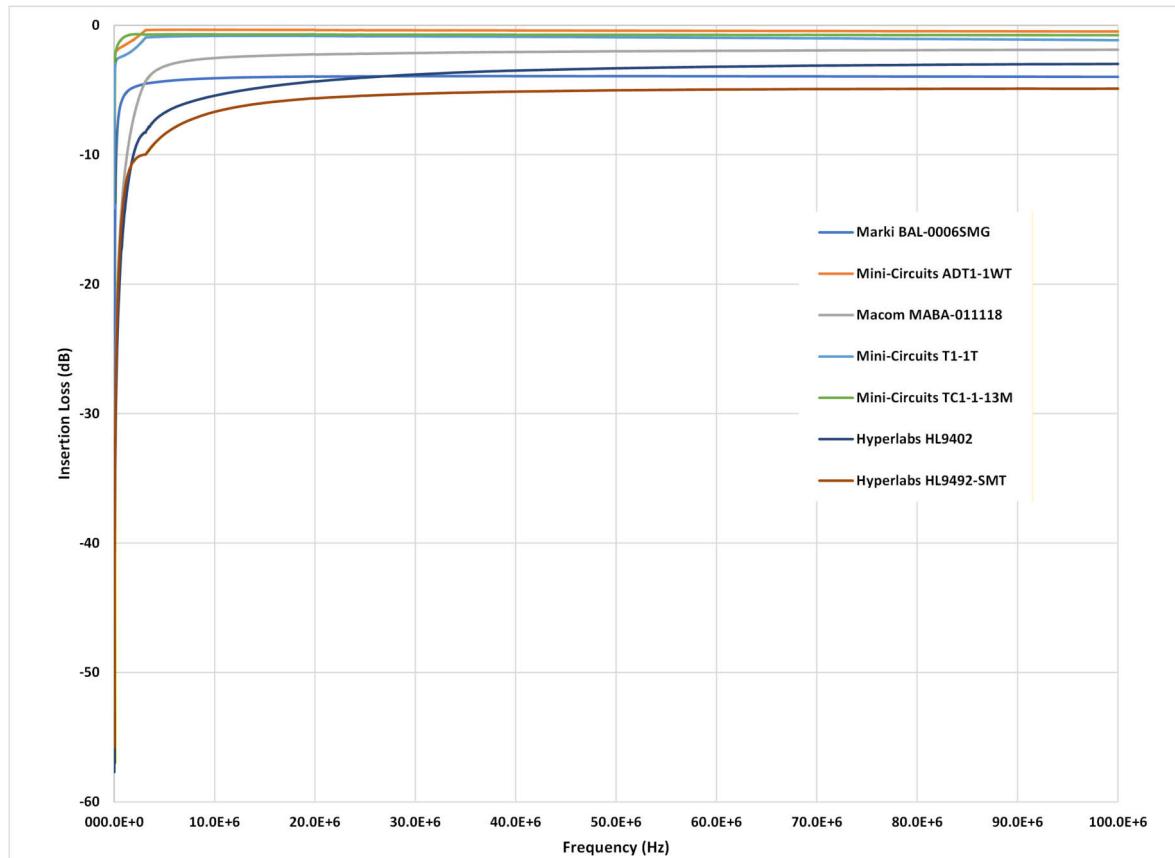

如果需要直流耦合，这通常意味着设计人员无法在设计中使用变压器或平衡-非平衡变压器前端，这种拓扑很常用且设计简便。一些平衡-非平衡变压器和变压器可以具有低频范围，可以低至非常低的 kHz 范围，但是，使用平衡-非平衡变压器或变压器对真直流进行采样恰恰是不行的。请参阅图 1-1，快速了解一些变压器和平衡-非平衡变压器的低端频率响应，在当今市场上可以低至 9kHz 范围（测试设备受限）。

图 1-1. 变压器和平衡-非平衡变压器的低端频率响应

在 9kHz（用于测量这些平衡-非平衡变压器的 S21 响应的 VNA 的测试设备限制）下，平衡-非平衡变压器的许多低端响应都在 -10 至 -50dB 或更高的衰减范围内。因此，如果用户计划对真直流进行采样，这未必是实用设计。

这种情况通常会强制设计人员使用放大器耦合到 ADC 并保持该直流值。通常会使用 FDA（即全差分放大器）来保持该直流值并将其传送到 ADC 以进行采样，但是放大器确实存在一些注意事项。首先，ADC 不能仅与任何 FDA 配合使用从而实现直流耦合。以下是放大器数据表中需要检查的一些内容，以确保 ADC 可以正常工作：

1. 放大器的输出级可实现直流耦合。

2. 放大器电源的合规范围足够大。

3. 放大器输入或输出共模范围足够大，这通常与第二点有关。

接下来，设计人员还可以使用单端信号链，然后将信号链连接到 FDA。如果是这种情况，接下来要检查 FDA 是否可以针对单端 (SE) 输入和差分 (DIFF) 输出进行配置。有时，FDA 只允许差分输入和差分输出信号配置。

如果 FDA 数据表中未显示这类信息，请联系厂家供应商并核实。

## 2 查找合适的放大器

既然，我们知道用户打算使用 FDA 进行直流耦合连接，接下来本文将探讨上面提到的一些细节。

首先，检查放大器的输出级。除非数据表中没有明确指出输出级无法进行直流耦合，否则请查看数据表的应用部分，确认输出级是否具有一些上拉或下拉扼流圈。如果有，FDA 很可能具有集电极开路输出级，并且低端对几个 kHz 频率（而不是直流）进行有限的响应。

其次，检查 FDA 的合规区。这意味着什么？这意味着几个因素间存在着些许关联。检查 ADC 所需的模拟输入共模电压 (VCM)；该电压通常在 ADC 数据表的模拟输入规格表中。它通常在规格表中注明为 VCM。ADC 上还可以有一个 VCM 引脚，让用户可以将该节点连接回模拟输入端，以保持共模电压稳定。这是 ADC 的 VCM 引脚，也可用于将 FDA 的输出驱动至特定的输出共模电压或 FDA 上的 VOCM 引脚电压。最终，ADC 的模拟输入共模电压需合规并支持 FDA 的相同 VOCM 电压范围。该信息通常可以在 FDA 数据表的规格表中找到。

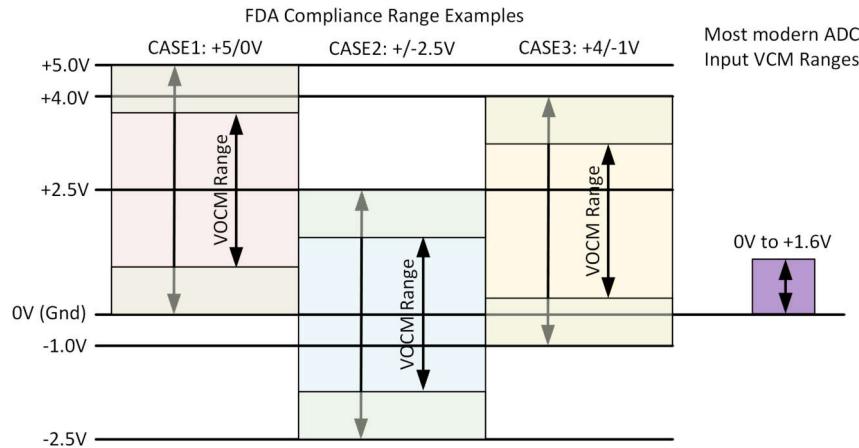

通常，VOCM 范围与电源电压范围或放大器使用的电源相关。有些 FDA 只有单电源，有些甚至可具有双电源功能。这类双电源放大器肯定更加灵活。原因是，通常当该引脚未专门使用电压驱动时，FDA 的输出共模电压或 VOCM 会悬空至电源电压的一半。例如，0 至 5V FDA 具有 2.5V VOCM，0 至 3.3V FDA 具有 1.65V VOCM。现在，对于双电源 FDA，灵活性也取决于电源的范围。例如，您可以使用 LMH5401 FDA。该 FDA 具有 5V 合规范围，但具有双电源选项。这使得该放大器能够在 5V VCC 和 0V VSS（接地）或者 2.5V VCC 和 -2.5V VSS 范围中运行，或者两者之间的任何范围运行，例如 4V VCC 和 -1V VSS。只要两个电源域的总和处于 5V 合规范围内或更小。有关上述合规范围示例，请参阅图 2-1。

图 2-1. LMH5401 合规范围示例与当前 ADC VCM 范围间的关系

请注意，放大器的 VOCM 范围在放大器的电压合规范围内，这样就可以通过放大器管理各种信号电平。

### 3 了解 ADC 及类型

ADC 的模拟输入共模规格同 ADC 的架构类型直接相关。大多数高速 RF 转换器分成两组。它们具有直接连接到模拟输入引脚的内部缓冲级，或者没有内部缓冲器，模拟输入引脚直接连接到内部采样开关，否则称为非缓冲输入。如果转换器进行缓冲，则模拟输入为自偏置输入，并且 VCM 通常为模拟电源的一半加上一个二极管压降，即  $AVDD/2+0.7V$ 。而非缓冲转换器没有内部缓冲器，需要 ADC 的模拟输入引脚由 VCM 引脚偏置，该引脚必须连接到模拟前端电路或由连接的 FDA 偏置。通常，非缓冲 ADC 需要模拟输入引脚的共模电压来停止模拟电源，即  $AVDD/2$ 。

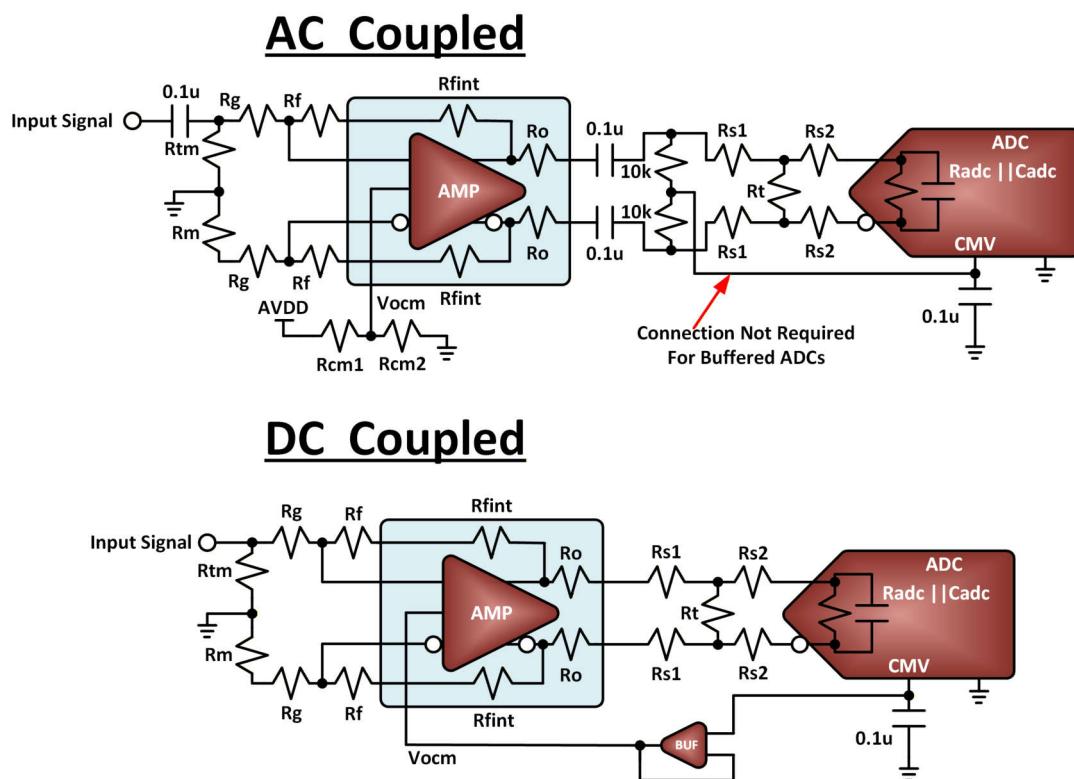

两种类型 ADC 之间的主要区别在于，缓冲转换器是自偏置的，这意味着模拟输入悬空至  $AVDD/2+0.7V$ ，而非缓冲转换器需要一点帮助。模拟输入需要在每个模拟输入引脚上进行 VCM 连接，以适当地偏置这些输入。有多种方法可以在模拟输入前端实现此连接，务必遵循数据表建议的评估板方法，以实现最佳实践。请参阅图 3-1，了解缓冲与非缓冲 ADC 类型以及 FDA 的交流与直流耦合连接之间的一些一般差异。

图 3-1. 缓冲与非缓冲以及交流与直流耦合前端的模拟输入 ADC 连接

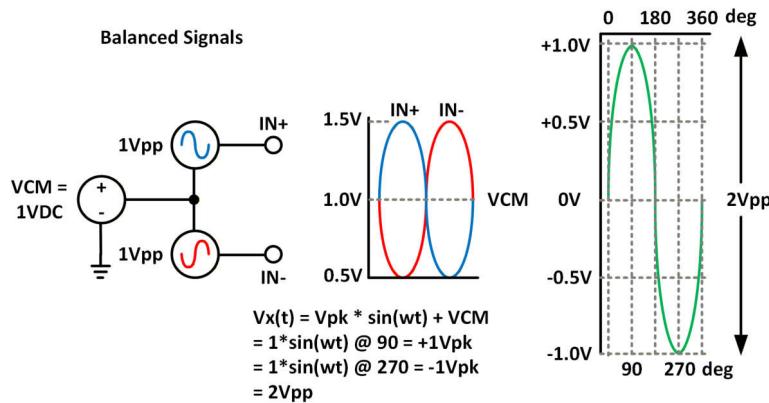

许多高速 ADC 和 DAC 都在 65nm 以及更小的工艺节点上进行设计和开发。这意味着 ADC 的电源节点变得越来越小，例如 +1.1V AVDD 甚至更低。这会强制模拟输入共模范围处于亚伏或更低范围内。例如，当今市场上的许多 ADC 的 VCM 范围为 +0.95V 或更小。这意味着 FDA 还必须具有允许的 VOCM 输出范围，以便放大器和 ADC 能够正常工作。有关 ADC 在 1V 共模电压附近的差分输入信号的示例，请参阅图 3-2。

图 3-2. ADC 差分输入信号示例。

请注意，转换器的模拟输入 VCM 很重要，需要外部输入网络前端来满足要求，例如，FDA 或其他方面，转换器存在性能问题。

通过差分划分信号摆幅，该接口使用户能够在转换器的输入满量程范围内保持更高的电压电平（即一个、两个甚至 3Vpp）；因此，模拟输入的差分特性让容纳更小过程节点成为可能。有关更多信息，请参阅 1。

## 4 同时模拟 FDA 和 ADC 以避免缺陷

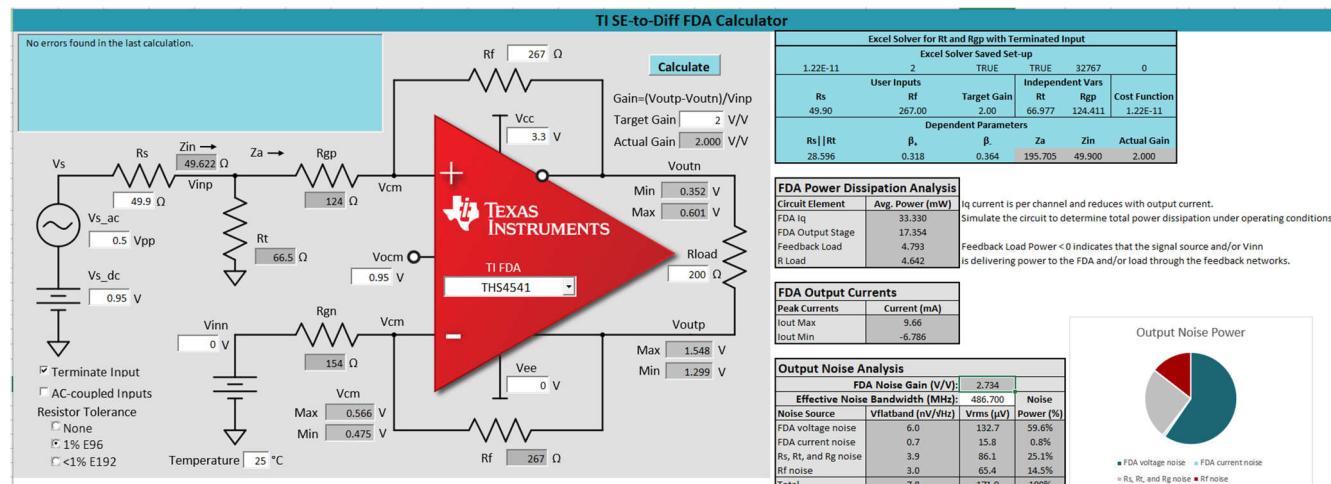

做出 FDA 和 ADC 选型决策后，最好进行功能仿真，以确保 VOCM 和电源满足设计的适当合规范围。为了快速简单地完成此操作，只需在 [TI.com](http://TI.com) 上下载 FDA 计算器，而无需像数据表中所述那样进行所有数学运算。请参阅参考资料 9。

在此 FDA 计算器工具中，选择 TI.com 上提供的大多数 FDA，以了解此 FDA 是否满足特定的 VCM 合规范围，从而满足 FDA 和 ADC 功能的要求。

要详细了解该特定计算器, 请参阅图 4-1。该工具支持差分输入和差分输出配置, 以及 SE 输入至差分输出配置。

图 4-1. 使用 THS4541 的 FDA 计算器示例，SE 输入至差分输出（如图所示）

最后要说明一些要点，尤其是在 **FDA** 配置了单端输入和差分输出的情况下。请再次注意图 4-1。请注意，两个 **FDA** 输入端接不同的电阻值，以便特意达到不平衡。这是为了在此配置中强制共模电流达到平衡。因此，放大器的信号输入端需要额外的 **Rt** 值，并且 **Rgp** 和 **Rgn** 的值略微不相等，以便在仅使用一个输入时帮助平衡该阻抗。如果操作不正确，这些共模电流不会抵消，并且输出端的电压不一定相等。以下是该良好电路发生故障时可能出现的情况。请参阅图 4-2

图 4-2. FDA 的输出共模电压在 P 和 N 输出之间不平衡，导致 ADC 模拟输入信号采集出现偏移

在上图中我们可以看到，这种不平衡迫使输入信号从中标度偏离中心。因此，输入在可以成为满量程输入之前，在一个方向或另一个方向上升高并超出 ADC 的合规范围。这会导致 ADC 出现削波或超范围，只是因为 VCM 合规范围不在中心。因此，转换器似乎存在增益和/或偏移误差，并降低到要采集的总体测量值。设计人员可能会发现转换器过早削波，并且输入信号无法达到满量程。

为了避免这种错误，只需在数据表中浏览建议的示例公式，找到 SE 转差分信号的方法，或者在 [TI.com](http://TI.com) 上使用这个方便的计算器，如图 4-1 中所示。否则，这实际上会在 FDA 的输出端和 ADC 的输入端之间产生关于 VCM 的激烈竞争。两个器件之间的这些直流共模值不完全匹配。因此，这两个器件将开始相互“争斗”，并且总是达成某种妥协以满足彼此的直流需求。无论谁胜出，电路都不正常，FDA/ADC 组合无法在频谱中正确表示自己，如图 4-3 中所示。

图 4-3. HSDCPro 输出频谱由于共模平衡不良被削波

请注意远离 ADC 的 VREF 引脚或查看数据表。大多数具有此类注释的引脚都不具备提供 VCM 偏置的能力，除非通过放大器跟随器配置在外部对它们进行缓冲。请注意，VREF 引脚设置转换器内所有的内部基准偏置。这也是转换器满量程输入的函数。如果 VREF 引脚使用不当（例如负载过大），转换器的输入满量程范围可能会意外偏移，这也会导致图 4-3 和图 4-2 所示的情况。因此，系统的总动态范围会受到限制。总之，如果可能，不要使用 VREF 引脚。

## 5 实现直流耦合福音的五个步骤

现在，我们已经回顾了有关直流耦合的要点并对其有了整体了解，我们还回顾了放大器和 ADC 的详细信息，以便正确设计直流耦合接收器。我们来看一个简单的真实直流耦合示例，确保我们可以演示如何运用从上述要点中学到的全部知识。

- 从以下要求开始，假设用户希望进行直流耦合并使用 FDA，以下是开始设计时必须预先考虑的一些参数：

ADC 采样率：40MSPS

接收器 ( FDA 和 ADC ) 带宽 (BW)：直流至第一奈奎斯特 (20MHz)

接收器 ( FDA 和 ADC ) 通带平坦度：超过通带 + 1dB。

接收器 ( FDA 和 ADC ) SNR/SFDR：75dBc/85dBc ( 最小值 - 3dBFS )

FDA 最大输入信号驱动：10MHz 时为 0dBm ( 或更小 )

### 备注

该要求假设 FDA 必须为小输入信号幅值提供 2V/V 或更高的增益，以便实现 ADC 的满量程。

FDA 配置：输入 = 单端、输出 = 差分

有关上述要求的更多信息和更深入的解释，请参阅 [揭秘射频转换器前端的实用奥秘](#)。

- 在查看 TI 最新 FDA 和 ADC 产品清单并对电子表格进行大量分析和权衡后，本例选择了 THS4541 和 ADC3543。按理说，此步骤非常简单。关键在于，不要忘记在查看符合要求的 FDA 和 ADC 的全部信息时，该步骤可能会相当耗费精力。TI 建议为 FDA 和 ADC 创建电子表格，突出显示上述所有相关规格。详情请参考 [图 5-1](#)。

| FDA | Part Number | Power (mW) | Supplies (V) | SFDR (dBFS)@10MHz | Noise (nV/sqrt(Hz)) | BW (MHz) | VCOM Range (V) | NF(dB)               | Slew Rate (V/uSec) | Road (ohms)           |                        |

|-----|-------------|------------|--------------|-------------------|---------------------|----------|----------------|----------------------|--------------------|-----------------------|------------------------|

| 1   | LMH5401     | 275        | 5/Dual       | 94                | 1.25                | 6200     | +/-1.4         | 9.6                  | 17500              | 200                   |                        |

| 2   | THS4541     | 48.5       | 5/Dual       | 90                | 2.2                 | 850      | +/-2.3         | 12                   | 1500               | 500                   |                        |

| 3   | THS4532     | 5          | 5/Dual       | 30                | 10                  | 27       | +/-2.4         | NA                   | 220                | 2000                  |                        |

| 4   | THS4535     | 25         | 5/Dual       | 30                | 3.6                 | 80       | +1.4/-2.1      | NA                   | 47                 | 1000                  |                        |

| 5   | LMH6554     | 260        | 5/Dual       | 102               | 0.9                 | 2500     | +/-1.25        | 7.7                  | 6200               | 200                   |                        |

| ADC | Part Number | Power (mW) | Supplies (V) | SFDR (dBFS)@10MHz | SNR (dBFS)@10MHz    | BW (MHz) | VCM (V)        | Sampling Rate (MSPS) | Resolution (Bits)  | Input Fullscale (Vpp) | Digital Interface Type |

| 1   | ADC3563     | 77         | 1.8          | 94                | 81.9                | 230      | 0.95           | 65                   | 16                 | 3.2                   | Serial LVDS            |

| 2   | ADS1412     | 105        | 1.8          | 87.5              | 71.1                | 400      | 0.95           | 65                   | 14                 | 2                     | Parallel CMOS          |

| 3   | ADC3543     | 35         | 1.8          | 88                | 79                  | 230      | 0.95           | 65                   | 14                 | 2.25                  | Parallel CMOS          |

| 4   | ADS5560     | 250        | 3.3          | 89                | 84                  | 300      | 1.5            | 40                   | 16                 | 3.56                  | Parallel CMOS          |

| 5   | ADS6142     | 285        | 3.3          | 96                | 74.7                | 450      | 1.5            | 65                   | 14                 | 2                     | Parallel CMOS          |

图 5-1. FDA 和 ADC 电子表格权衡分析。

- 在做出 FDA 和 ADC 选型决策后，最好分别使用上述电子表格或 FDA 和 ADC 数据表来确定它们的共模电压是否兼容。如图 4-1 中所示，FDA 针对 SE 输入和差分输出进行了配置，只需使用 3.3V 电源即可满足 ADC 模拟输入的 +0.95V 共模电压需求。请注意，也可以通过上一步电子表格中 FDA 和 ADC 的选型决策来完成此步骤。这一步可以作为一种不错的复查。

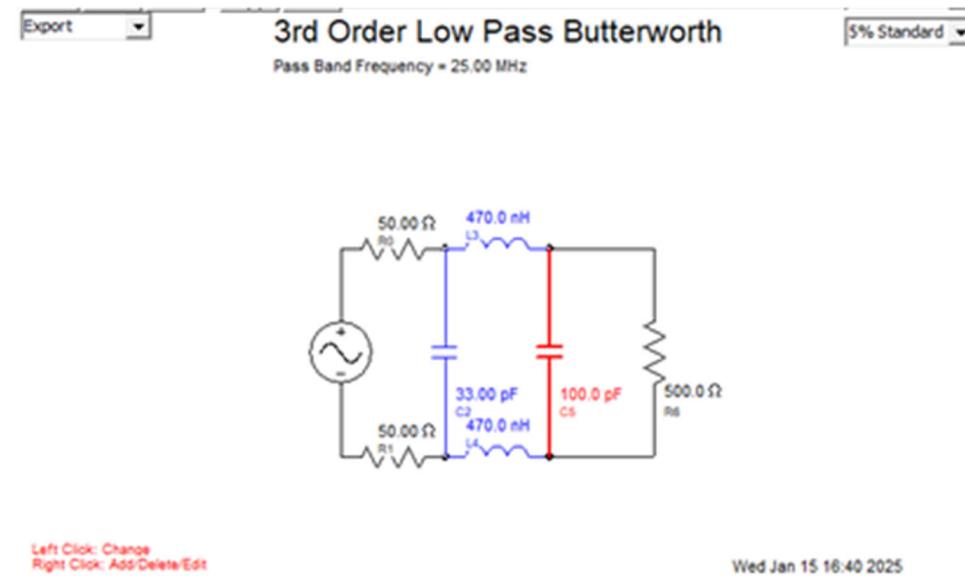

- 接下来，最好在 FDA 的输出端和 ADC 的输入端之间设计一个抗混叠滤波器 (AAF)。这将有助于将上面提到的带宽要求降低到 20MHz，并减轻混叠回基带的任何额外噪声，从而进一步降低 ADC 的信噪比 (SNR) 性能要求。请记住，放大器是有源器件，它本身具有噪声并且会增加 ADC 通带区域内的噪声。有关对于 FDA 噪声及其如何叠加到整个接收器信号链的更多理解（例如，降级、SNR），请参阅 4 和 6。

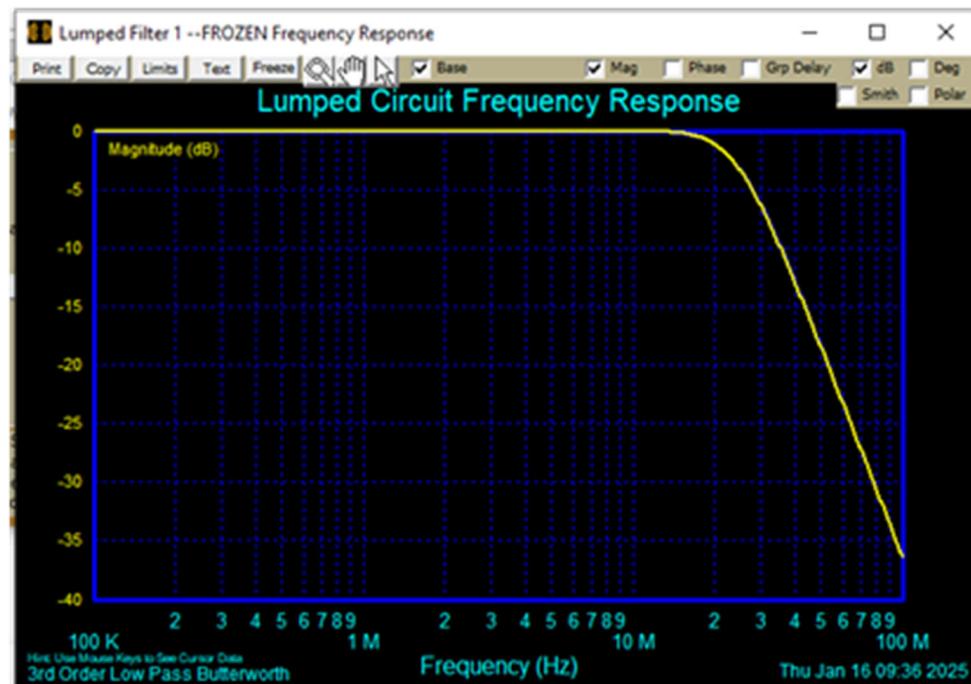

使用 Ansys 的简单滤波器解决方案工具或类似工具，可以为设计提供一个良好的起点。请分别参阅图 5-2 和图 5-3。此处，将一个简单的三阶低通巴特沃斯滤波器设计为 25MHz。滤波器截止频率采用超额设计，这是考虑到在 PCB 上使用实际值时将发生的一些损耗。有关如何在 FDA 和 ADC 之间正确设计 AAF 的更多详细信息，请参阅 2。此处，我们要更深入探讨针对此 FDA 和 ADC 接口使用每个元件时的所有细微差别。

图 5-2. 25MHz 差分 AAF 设计 — 原理图

图 5-3. 25MHz 差分 AAF 设计 — BW/插入损耗仿真

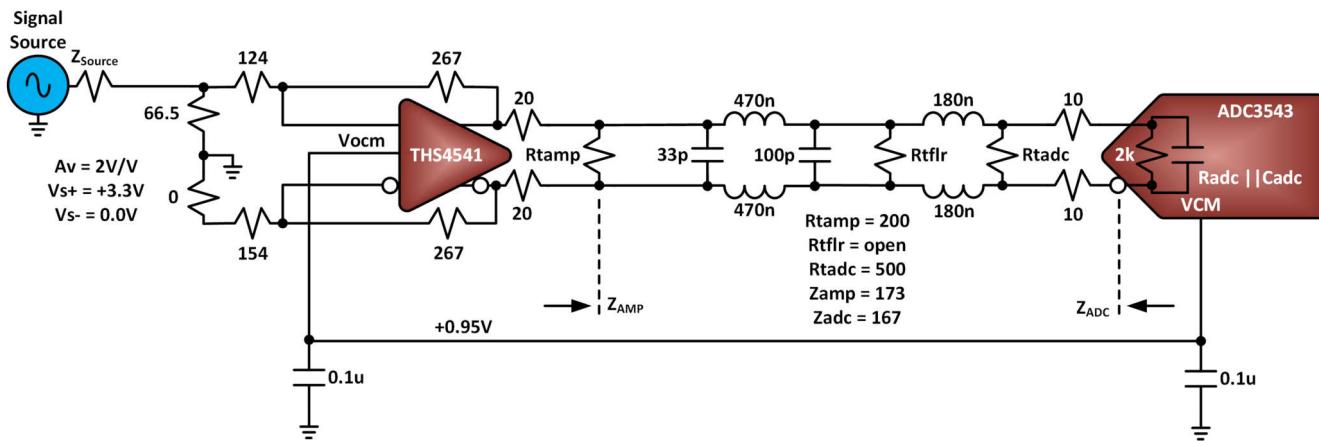

5. 根据 [图 5-4](#)，在实验室中构建接收器设计并按照 [步骤 1](#) 中概述的所有要求开始累积一些测试测量值。在该用例中，本示例使用 THS4541 FDA 和 ADC3543 评估模块测试板（或 EVM），它们通常提供几个方便的修改选项以实现此类设计。不包含焊铁。

图 5-4. 真实直流耦合设计示例方框图

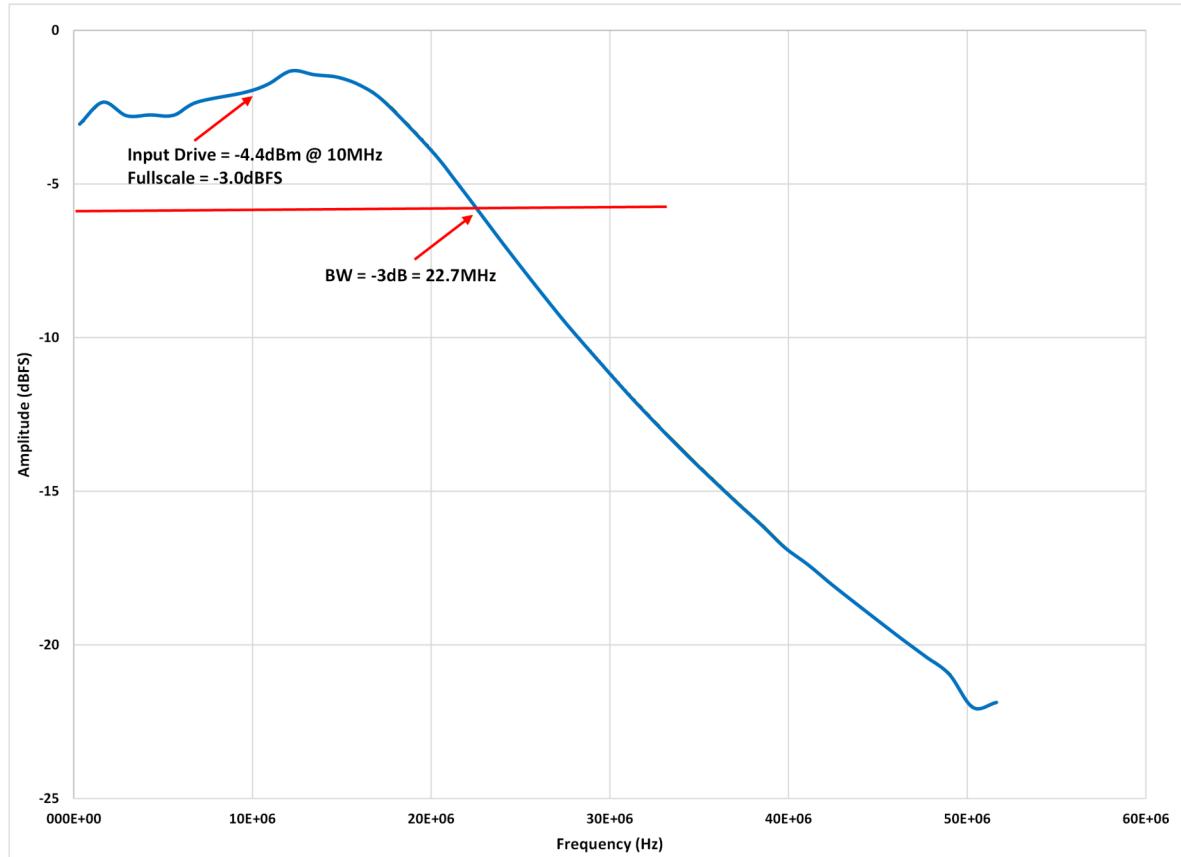

我们需要完成并验证的第一个次测量值是信号链系列的通带平坦度。在图 5-5 中，根据在放大器输出端和 ADC 输入端之间实现的 AAF 设计，显示的通带平坦度约为 23MHz 带宽。作为基准点，放大器的输入端只需要使用  $-4.4\text{dB}$  即可在 10MHz 达到  $-3\text{dBFS}$  信号。这样，用户能够了解系统参数设置的所需 BW 范围内的正向或反向增益或损耗。有关如何正确测量通带平坦度的更多信息，请参阅 8

图 5-5. 测量的带宽、通带平坦度和输入驱动

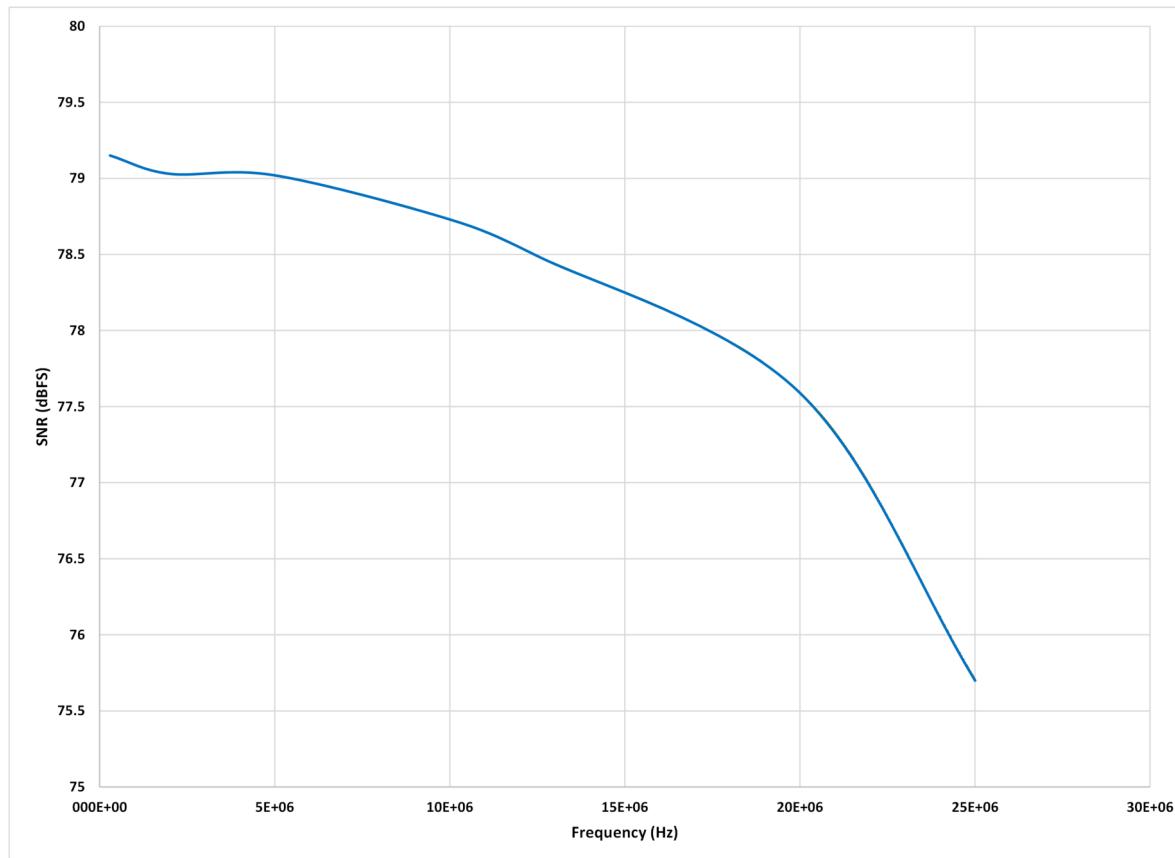

验证通带平坦度带宽 (BW) 后，下一步是在应用带宽范围内完成一些交流性能扫描。这样可以深入了解性能如何动态保持，从而验证 ADC 是否仍满足应用的所有其他性能要求。请分别参阅图 5-6 和图 5-7。

图 5-6. 测得的 SNR 扫描与模拟输入频率间的关系

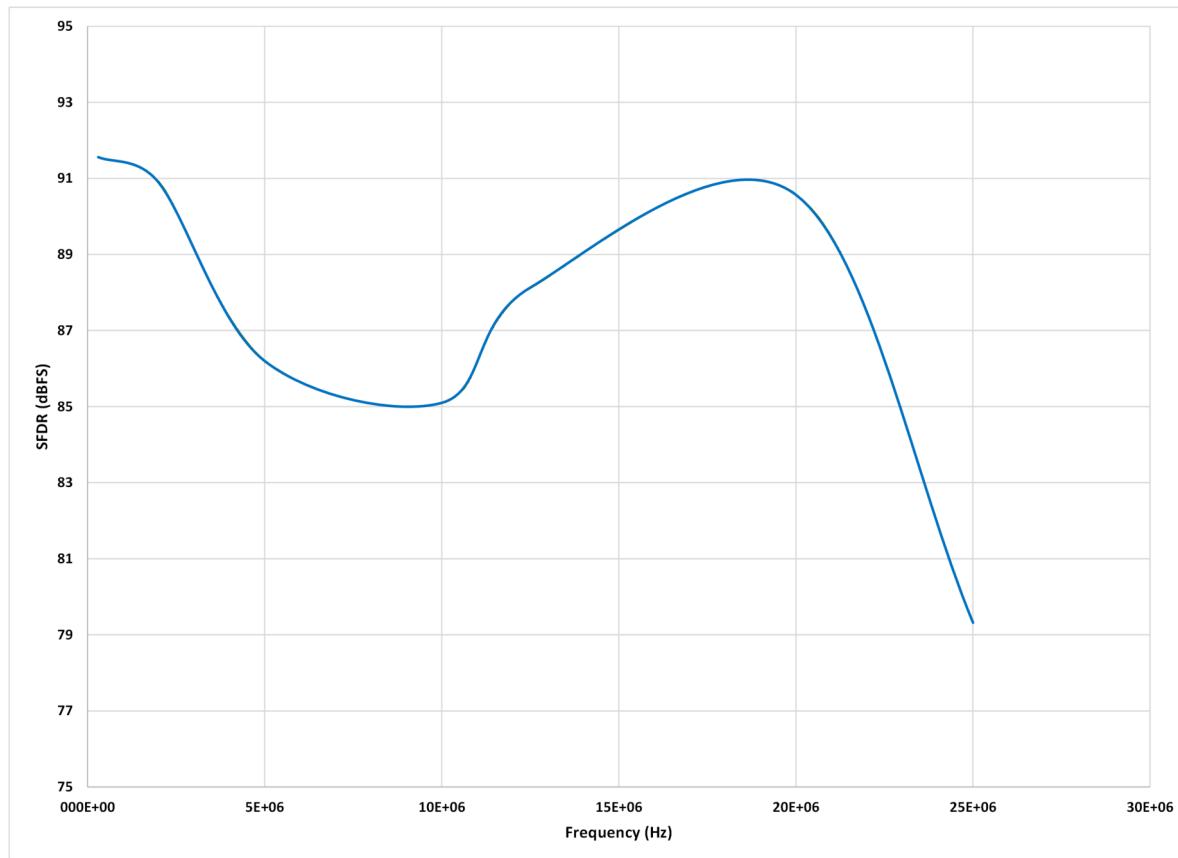

图 5-7. 测得的 SFDR 扫描与模拟输入频率间的关系

如图所示，测得带宽内的 SNR 和 SFDR 性能分别为 79dBFS 至 75dBFS 和 92dBFS 至 79dBFS。所有测量都在近直流和 300kHz 至 25MHz 进行，在 -3dBFS 时总共使用 10 个频率点以得出该曲线。

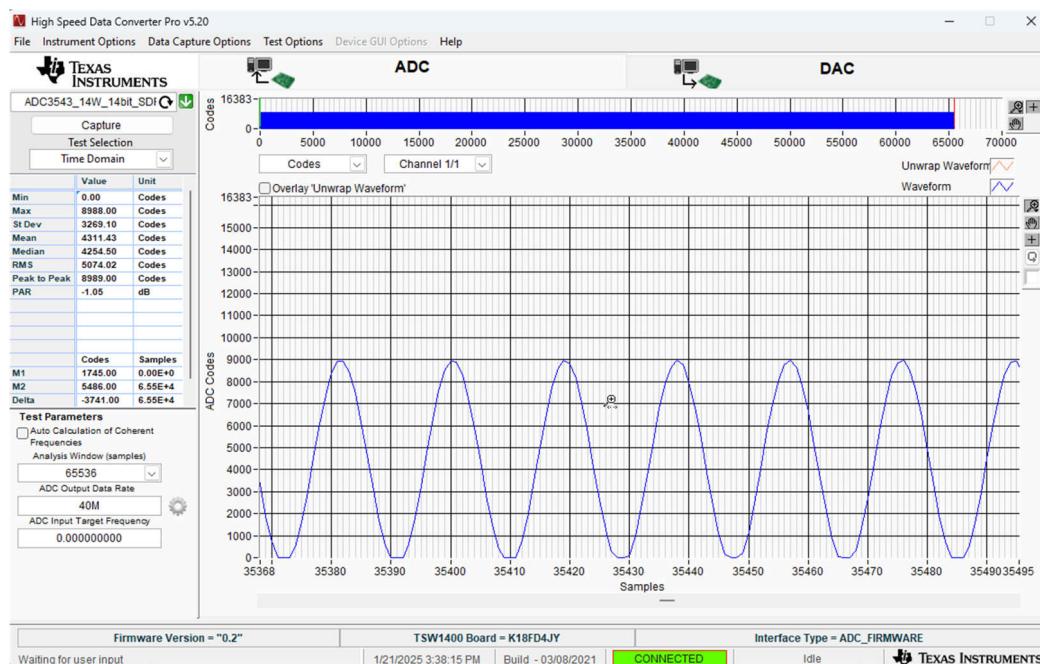

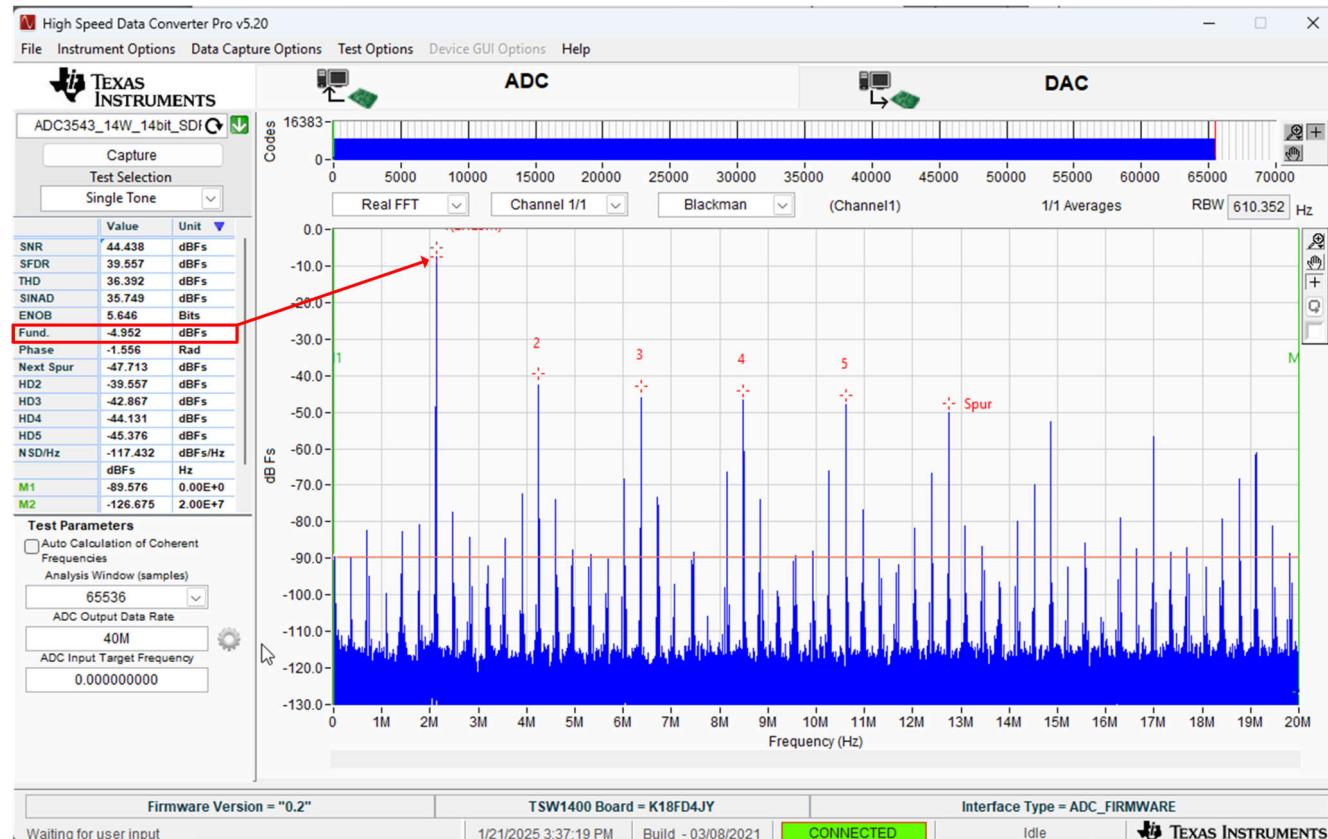

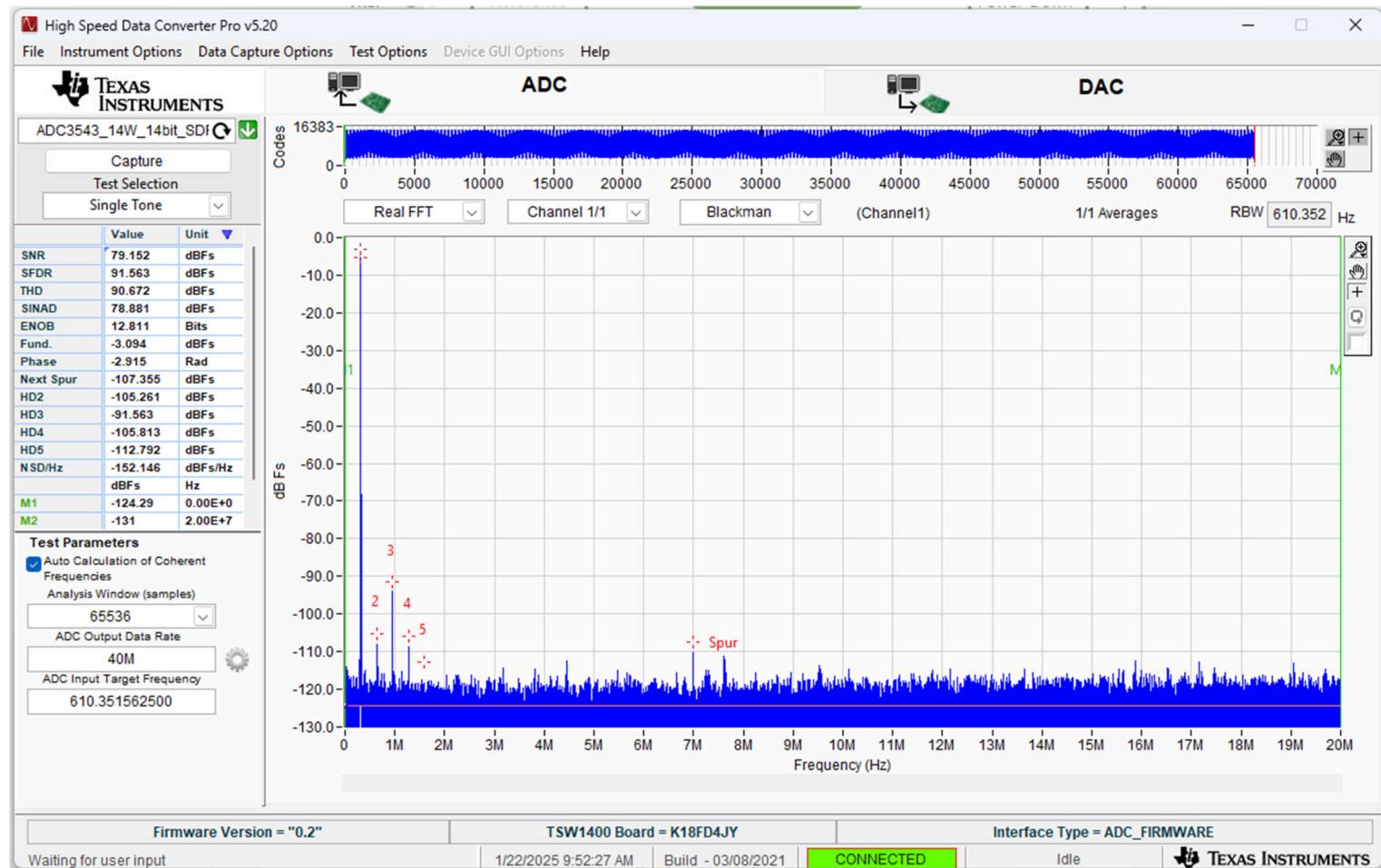

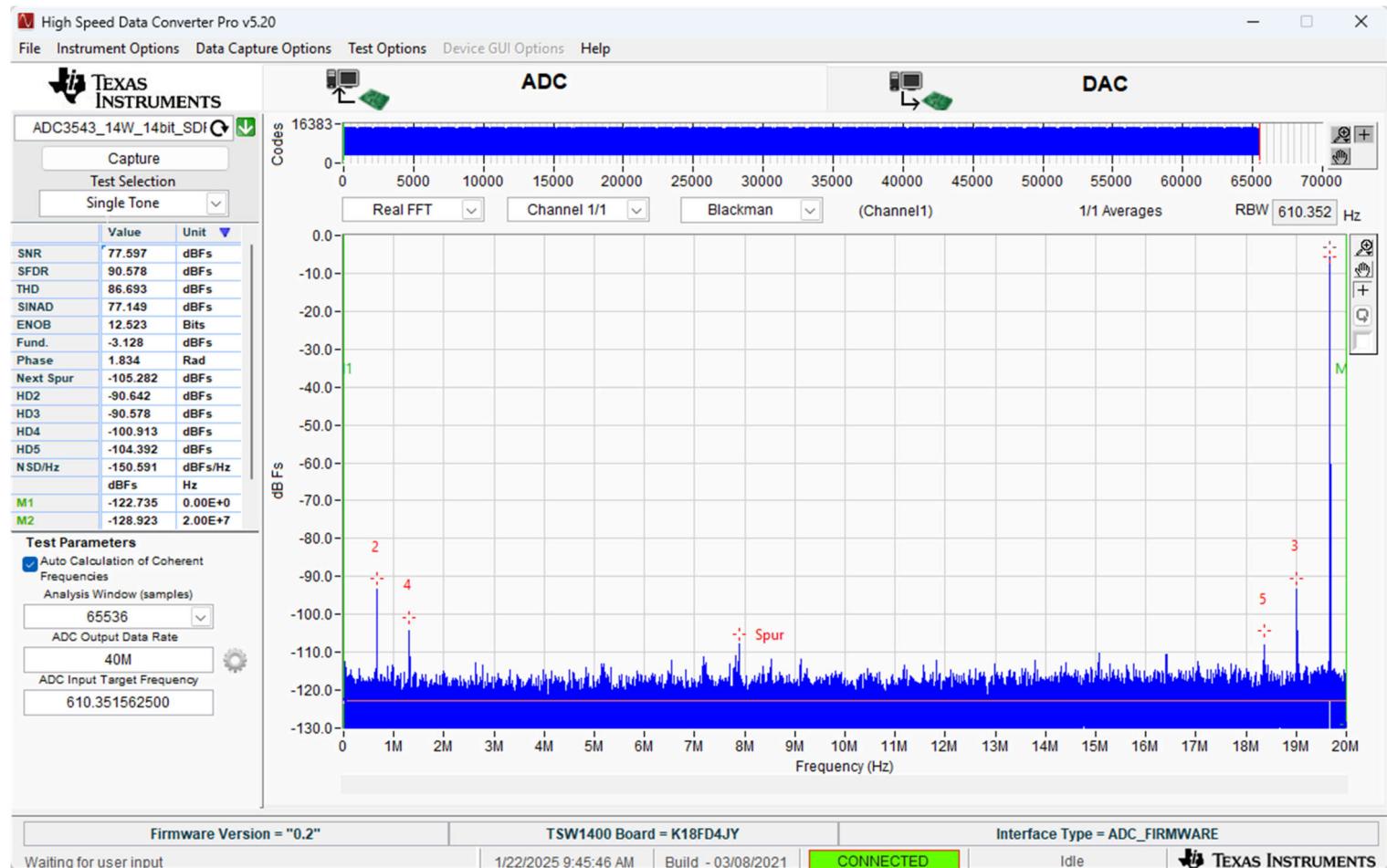

为了显示直流耦合 FDA 和 ADC 信号链组合的频谱纯度，使用 TI 的 HSDC Pro 数据采集软件，分别在图 5-9 和图 5-8 中展示了一些 FFT。图中显示了近直流、300kHz 和 20.3MHz 模拟输入音调。每个 FFT 交流性能测量值都完全符合前面规定的要求。

图 5-8. 测得的 FFT 性能：近直流，Fin = 300kHz

图 5-9. 测得的 FFT 性能 :  $F_{in} = 20.3\text{MHz}$

可以看出，遵循这个简单的五步过程，用户的下一个高速直流耦合信号链设计就可以取得成功。预先确定信号链要求，创建一个简单的电子表格来帮助进行器件比较，然后仅使用有现货的现成 EVM，以便在两个元件尚未布置到同一个电路板上时将信号链设计剪切粘贴在一起。通过一些标准的实验室测量，用户只需评估整体设计功能，即可开始将最终设计转换为客户电路板或系统设计。

## 6 总结

本文档说明了如何快速轻松地开发 FDA 和 ADC 之间的正确直流耦合前端，只要避免上述缺陷即可。首先，需要理解直流耦合必须使用放大器。在这种类应用场景中，不能使用平衡-非平衡变压器和变压器。另外请注意，放大器会向整个接收器信号链增加噪声，因此必须在两个器件之间采用 AAF，以尽可能降低输出频谱中的噪声。进行检查，以确保所选放大器和 ADC 直流兼容，并且共模电压均在两个器件的正常工作范围内。这对于直流耦合设计的成功至关重要。使用方便的 DA DIFF 计算器电子表格和互联网上提供的其他工具是一个良好的开端，可以确保每个器件处于其他器件的合规范围内。最后，使用 5 步过程来指导直流耦合前端设计开发，否则下一个接收器信号链可能会过早削波或根本无法达到 ADC 的满量程，从而严重破坏动态范围。

## 7 参考资料

1. 德州仪器 (TI), [揭示射频转换器模拟输入的满量程推断方法](#), 应用手册。

2. 德州仪器 (TI), [抗混叠滤波器设计技术如何改进有源射频转换器前端](#), 模拟设计期刊。

3. 电子设计, [实现放大器与 ADC 之间的共模收敛](#), 网页。

4. 电子设计, [ADC 信号链中的噪声注意事项](#), 网页。

5. 德州仪器 (TI), [揭秘射频转换器前端的实用奥秘](#)研讨会。

6. 德州仪器 (TI), [比较有源和无源高速/射频模数转换器前端](#), 应用手册。

7. 德州仪器 (TI), [在高速转换器中的奈奎斯特孔附近采样](#), 应用手册。

8. 德州仪器 (TI), [高速模数转换器通带平坦度解析](#), 应用手册。

9. 德州仪器 (TI), [DIFFAMPGAINCALC 计算工具](#), 计算工具。

10. 德州仪器 (TI), [HSDCPro 数据采集软件](#), 软件。

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2026，德州仪器 (TI) 公司

最后更新日期：2025 年 10 月