*Application Note*

# 使用极少的 **CLB** 资源实现三相三电平逆变器延迟保护

Aki Li

## 摘要

三电平逆变器拓扑已广泛应用于大功率应用中，但其需要特殊的保护控制方案，许多用户曾尝试通过昂贵的外部电路来实现。本应用报告讨论了如何使用极少的可配置逻辑块 (CLB) 资源来实现三相三电平逆变器的保护逻辑。

## 内容

|                 |   |

|-----------------|---|

| 1 简介            | 2 |

| 2 设计概述          | 3 |

| 3 CLB 实现方案      | 4 |

| 3.1 CLB 输入选择    | 4 |

| 3.2 计数器和 FSM 配置 | 5 |

| 3.3 CLB 输出      | 6 |

| 4 EPWM 配置       | 7 |

| 4.1 测试结果        | 8 |

| 5 总结            | 9 |

| 6 参考资料          | 9 |

## 商标

所有商标均为其各自所有者的财产。

## 1 简介

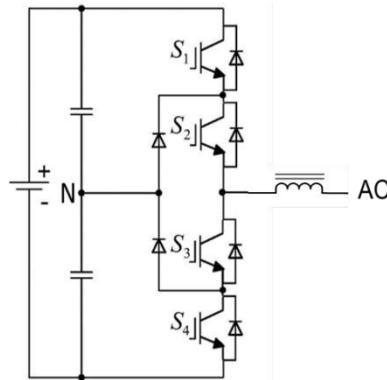

图 1-1 展示了一种典型的单相三电平 I 型逆变器，即中性点钳位 (NPC) 逆变器。该单相 NPC 逆变器包括 4 个串联的 FET ( 例如 IGBT )，其中 S1 和 S4 称为外部开关，S2 和 S3 称为内部开关。

图 1-1. 单相三电平 I 型逆变器

考虑到并网时正负周期之间的差异，表 1-1 列出了正常工作时四个 FET 的常规开关状态。

表 1-1. 正常运行时的常规开关状态

| 交流周期 | 开关状态 |      |      |      |

|------|------|------|------|------|

|      | S1   | S2   | S3   | S4   |

| 正    | 备用开关 | 保持开启 | 备用开关 | 保持关闭 |

| 负    | 保持关闭 | 备用开关 | 保持开启 | 备用开关 |

有多种事件 ( 如过流、热过载等 ) 会触发快速关断以保护半导体器件和系统。与两电平逆变器中立即同时关断所有 FET 不同，在三电平逆变器中，必须确保遵循正确的关断顺序：先关断外部开关 ( S1 或 S4 )，经过特定延迟后再关断内部开关 ( S2 或 S3 )；而在恢复过程中则需首先导通内部开关。长期以来，这种延迟保护需求一直是许多 UPS 或光伏逆变器客户面临的一大挑战。由于使用软件算法的延迟过大而无法提供及时保护，部分客户不得不采用外部硬件电路 ( 如 FPGA 或 CPLD ) 来实现该保护逻辑，这增加了系统成本与开发工作量。

为了应对这一挑战，先前的应用报告《[使用 CLB 实现三电平逆变器延迟保护](#)》提出了一种单芯片设计方案，利用 C2000 器件的可配置逻辑块 (CLB) 来设计 PWM 信号的额外延迟保护逻辑。但在从单相逆变器扩展至三相时，大多数 C2000 器件没有足够的 CLB 单元，因此提出了占用额外 GPIO 的额外权变措施。

另一篇应用报告《[使用 4 类 EPWM 实现三电平逆变器延迟保护](#)》提出了一种利用现有 EPWM 功能的创造性配置，但扩展至三相逆变器时仍需占用更多 EPWM 模块，这对需要大量 EPWM 模块的大功率系统而言不可取。

此外，这两篇报告均假设故障事件仅通过硬件 ( GPIO 或内部比较器输出 ) 反映，而实际应用中故障事件可能来自多种来源，包括手动关断命令。业界期待一种对故障事件限制更少、灵活性更高的设计方案。

本应用报告讨论了如何优化 CLB 逻辑，以使用更少的 CLB 资源实现相同性能。该升级方案还能简化软件设计，用户可保留原有的故障响应操作，而不受不同故障事件影响。采用升级设计方案后，任何至少具备三个 CLB 单元的 C2000 器件 ( 包括 F2838xD/S、F28379D/S、F28076、F28004xC、F28003x 和 F28P55X ) 均可用于三相三电平逆变器系统。

## 2 设计概述

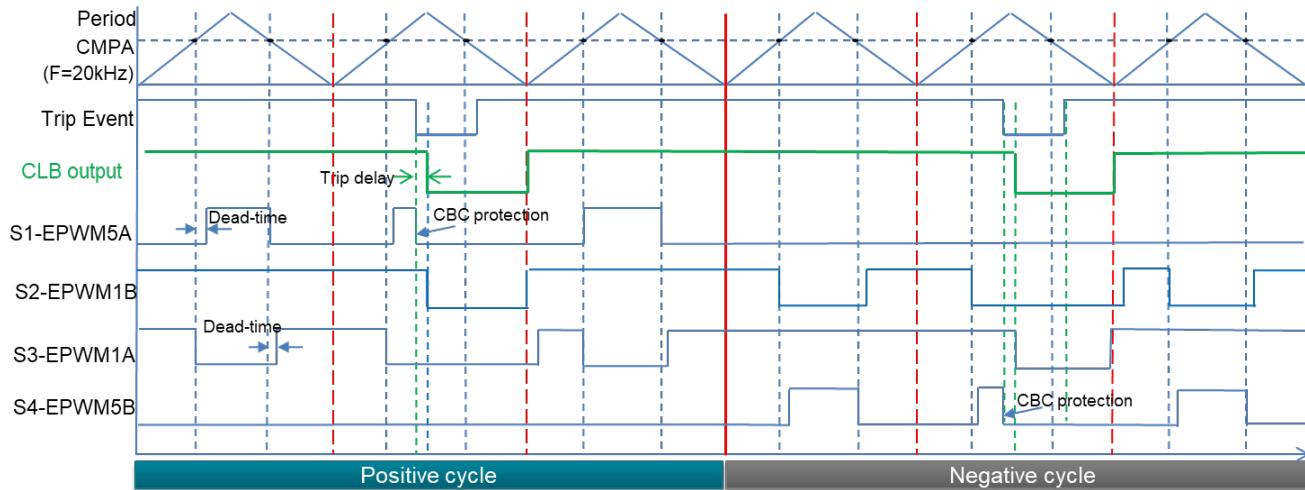

图 2-1 展示了在单相的正周期和负周期运行期间，结合使用 CLB 的预期 EPWM 保护行为。CLB 输出图看起来与先前的应用报告类似，但其生成和利用 CLB 输出的方式有所不同。

图 2-1. 结合使用 CLB 的预期 EPWM 保护逻辑

表 2-1 列出了每个相位的 EPWM 模块和 CLB 单元分配。由于在大多数 C2000 器件中，受 CLB 外设信号复用关系限制，仅 EPWM1 至 EPWM4 的输出可替换为相应的 CLB 输出，因此将 EPWM1、2 和 3 分别用于三个相位的内部开关。

表 2-1. EPWM 模块和 CLB 单元的分配

| 开关  | 阶段 1   | 阶段 2   | 阶段 3   |

|-----|--------|--------|--------|

| S1  | EPWM5A | EPWM6A | EPWM7A |

| S2  | EPWM1B | EPWM2B | EPWM3B |

| S3  | EPWM1A | EPWM2A | EPWM3A |

| S4  | EPWM5B | EPWM6B | EPWM7B |

| CLB | CLB1   | CLB2   | CLB3   |

### 3 CLB 实现方案

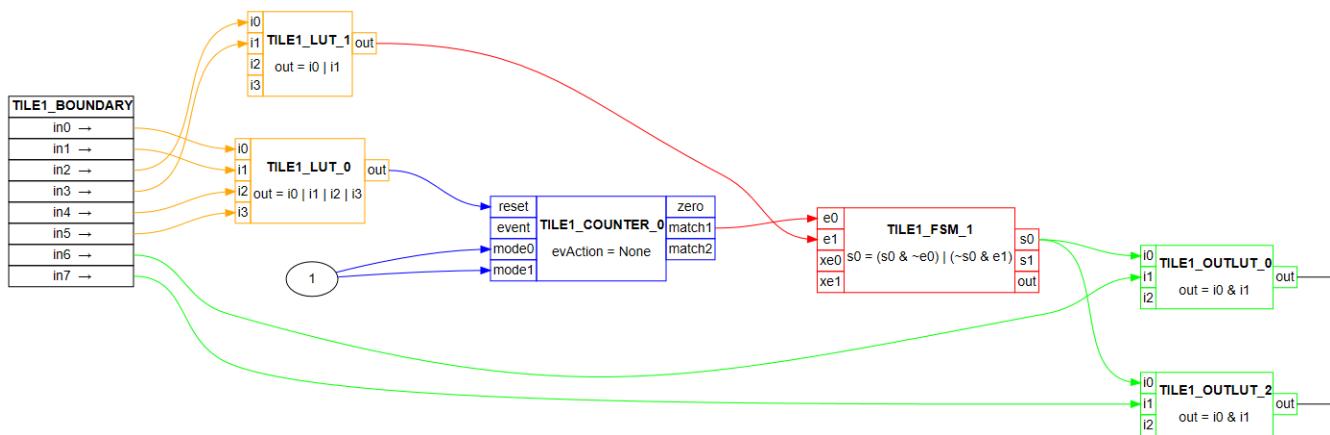

图 3-1 展示了每个相位的完整 CLB 方框图。

#### CLB Tile Configuration

图 3-1. 完整 CLB 方框图

#### 3.1 CLB 输入选择

该设计总共需要 8 路 CLB 输入，包括表 3-1 中所示的输入信号（以相位 1 为例）。

表 3-1. CLB 输入信号选择

| in0       | in1       | in2                | in3                | in4       | in5       | in6          | in7          |

|-----------|-----------|--------------------|--------------------|-----------|-----------|--------------|--------------|

| S2-EPWM1B | S3-EPWM1A | S2-EPWM1B<br>(上升沿) | S3-EPWM1A<br>(上升沿) | S1-EPWM5A | S4-EPWM5B | S3 EPWM1A_DB | S2 EPWM1B_DB |

该设计保留了所有 EPWM 模块的传统保护响应机制，即无论是单次触发还是逐周期配置，只要被任何硬件故障事件或手动关断（如软件强制跳闸）激活，所有 PWM 输出信号都将立即关断。

### 3.2 计数器和 FSM 配置

计数器块用于实现自定义延迟。使用一个额外的 LUT\_0 将所有 4 个 PWM 输出信号通过“或”逻辑相组合，然后将 LUT\_0 的输出设计为 Counter\_0 的复位输入。同时将模式 0 和模式 1 均设置为 1，这意味着只有当所有 PWM 输出信号关断后，Counter\_0 才开始计数。MATCH1 设置为预期的延迟值。

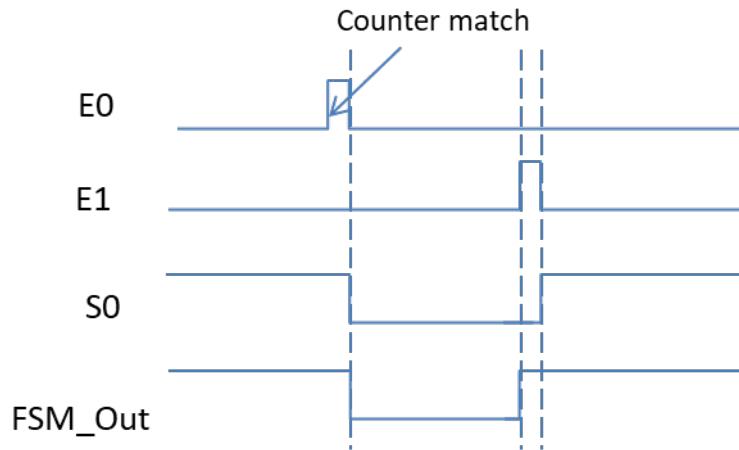

状态机通过 FSM 块实现，如图 3-2 所示。通过两路输入识别 S0 的状态，S0 在 E0 处下降，在 E1 处上升。E0 指 Counter\_0 match1 事件，而 E1 来自 LUT\_1 的输出，它组合了两个内部开关 PWM 信号 ( PWM1A 和 PWM1B ) 的上升沿，这意味着当任一内部 PWM 信号导通时，CLB 输出就会恢复到高电平状态。据此可建立 S0 状态的卡诺图，如表 3-2 所示

图 3-2. FSM 块中的状态机

表 3-2. FSM S0 卡诺图

| S0 E0E1 | 00 | 01 | 11 | 10 |

|---------|----|----|----|----|

| 0       | 0  | 1  | 1  | 0  |

| 1       | 1  | 1  | 0  | 0  |

根据卡诺图，可以推导出 S0 的 FSM 公式为

$$S0 = (S0 \& \sim E0) | (\sim S0 \& E1)$$

### 3.3 CLB 输出

CLB 输出的精妙之处在于能够用 CLB 生成的信号覆盖原始外设信号。在该设计中，输出 LUT 通过“与”逻辑将 FSM\_S0 状态与原始 EPWM1A/B 死区输出相组合。选择 LUT\_0 和 LUT\_2 输出，以启用“与”逻辑输出作为最终的 EPWM1A/EPWM1B 输出，如图 3-3 所示。

**Table 32-4. CLB Output Signal Multiplexer Table**

| CLB Output | CLB OUTLUT     | CLB1 Destination | CLB2 Destination | CLB3 Destination | CLB4 Destination |

|------------|----------------|------------------|------------------|------------------|------------------|

| 0          | <b>OUTLUT0</b> | <b>EPWM1A</b>    | EPWM2A           | EPWM3A           | EPWM4A           |

| 1          | OUTLUT1        | EPWM1A_OE        | EPWM2A_OE        | EPWM3A_OE        | EPWM4A_OE        |

| 2          | <b>OUTLUT2</b> | <b>EPWM1B</b>    | EPWM2B           | EPWM3B           | EPWM4B           |

| 3          | OUTLUT3        | EPWM1B_OE        | EPWM2B_OE        | EPWM3B_OE        | EPWM4B_OE        |

| 4          | OUTLUT4        | EPWM1A_AQ        | EPWM2A_AQ        | EPWM3A_AQ        | EPWM4A_AQ        |

| 5          | OUTLUT5        | EPWM1B_AQ        | EPWM2B_AQ        | EPWM3B_AQ        | EPWM4B_AQ        |

| 6          | OUTLUT6        | EPWM1A_DB        | EPWM2A_DB        | EPWM3A_DB        | EPWM4A_DB        |

| 7          | OUTLUT7        | EPWM1B_DB        | EPWM2B_DB        | EPWM3B_DB        | EPWM4B_DB        |

图 3-3. CLB 输出和外设信号多路复用器表

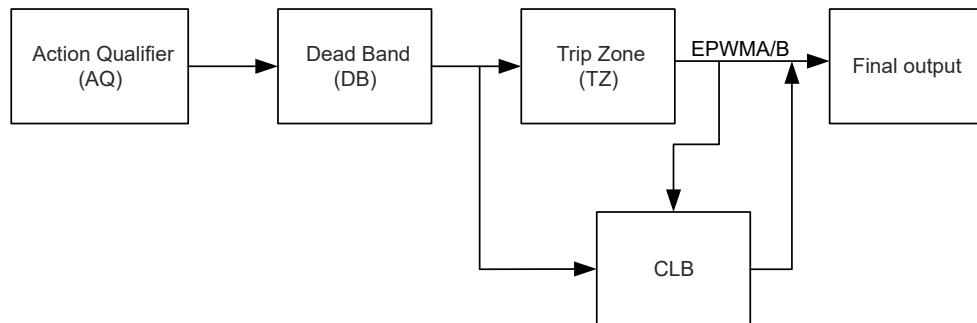

图 3-4 展示了 EPWM 子模块信号与 CLB 逻辑之间的关系。

图 3-4. EPWM 子模块信号与 CLB 逻辑之间的关系

## 4 EPWM 配置

表 4-1 列出了正周期和负周期的不同 EPWM 设置。与传统 EPWM 配置使用死区子模块生成同一 EPWM 模块的两路互补 PWM 输出不同，该设计通过两个 EPWM 模块的反相动作限定器动作来验证互补行为。由于两个 EPWM 模块共享相同的 CMPA 值，可以使用链接寄存器 EPWMXLINK 来确保两个 EPWM 模块的 CMPA 值始终保持同步更新。

并网的逆变器必须在正负周期内均能正常控制。利用当前的 EPWM 配置，在过零点期间，使用死区子模块中的 DBCTL[OUT\_MODE] 寄存器来交换 EPWMxA 和 EPWMxB 输出非常简单。

表 4-1. 正负周期的 EPWM 设置

| EPWM 信号   | 正周期的基本设置                  | 负周期                   |

|-----------|---------------------------|-----------------------|

| S1-EPWM5A | ↑ CAU<br>↓ CAD<br>启用上升沿延迟 | 交换 EPWMxA 和 EPWMxB 输出 |

| S2-EPWM1B | 强制高电平                     |                       |

| S3-EPWM1A | ↑ CAD<br>↓ CAU<br>启用上升沿延迟 |                       |

| S4-EPWM5B | 强制低电平                     |                       |

以下代码显示了交换 EPWM 输出的示例。

```

if(positive_cycle==1)

{

//Default setting is for positive cycle

EPWM_SetDeadBandOutputSwapMode(EPWM1_BASE, EPWM_DB_OUTPUT_A, false);

EPWM_SetDeadBandOutputSwapMode(EPWM1_BASE, EPWM_DB_OUTPUT_B, false);

EPWM_SetDeadBandOutputSwapMode(EPWM5_BASE, EPWM_DB_OUTPUT_A, false);

EPWM_SetDeadBandOutputSwapMode(EPWM5_BASE, EPWM_DB_OUTPUT_B, false);

}

else

{

// for negative cycle

EPWM_SetDeadBandOutputSwapMode(EPWM1_BASE, EPWM_DB_OUTPUT_A, true);

EPWM_SetDeadBandOutputSwapMode(EPWM1_BASE, EPWM_DB_OUTPUT_B, true);

EPWM_SetDeadBandOutputSwapMode(EPWM5_BASE, EPWM_DB_OUTPUT_A, true);

EPWM_SetDeadBandOutputSwapMode(EPWM5_BASE, EPWM_DB_OUTPUT_B, true);

}

```

## 4.1 测试结果

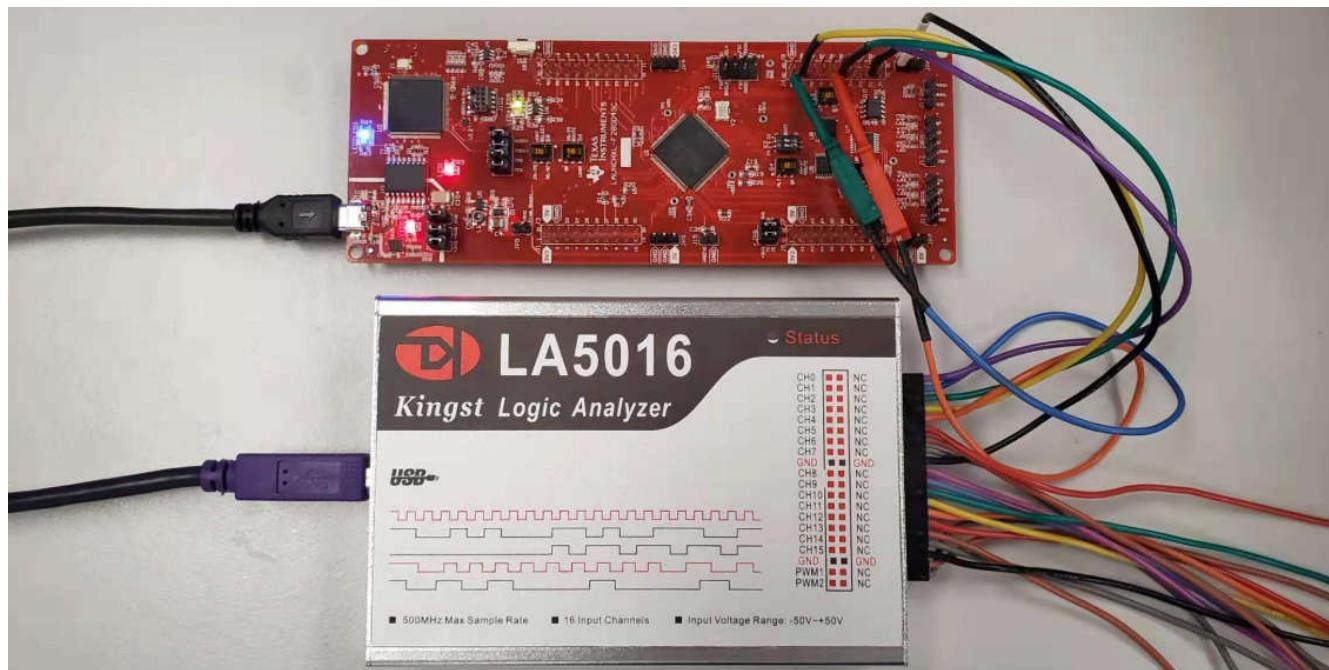

该设计已通过 LaunchPad **LAUNCHXL-F280039C** 和 Kingst Logic Analyzer 验证，如图 4-1 所示。

图 4-1. 测试平台设置

图 4-2 展示了正周期内的测试结果。当故障事件发生时，EPWM5A 立即启动 CBC 保护，而 EPWM1B 则在测得  $2.098 \mu\text{s}$  的延迟后变为低电平 (CLB 中设置为  $2 \mu\text{s}$ )。由于 CLB 硬件逻辑电路固有的延迟，实际延迟时间略大于定义值。图 4-3 展示了负周期内的故障事件，延迟保护逻辑同样按预期工作。

图 4-2. 正周期内故障低电平有效

图 4-3. 负周期内故障低电平有效

## 5 总结

本应用报告介绍了一种升级设计方案，旨在以极少的 **CLB** 资源实现三相逆变器的延迟保护功能。同时，该设计可简化软件实现，降低每个交流周期过零点期间的软件开销。该设计已在实际应用中得到验证并采用。

## 6 参考资料

1. 德州仪器 (TI)，[使用 CLB 实现三电平逆变器延迟保护](#)，应用手册。

2. 德州仪器 (TI)，[使用 4 类 EPWM 实现三电平逆变器延迟保护](#)，应用手册。

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2026，德州仪器 (TI) 公司

最后更新日期：2025 年 10 月