## Design Guide: TIDA-060031

# 适用于 Hi-Fi 应用中高级音频的精密 DAC 参考设计

## 说明

DAC11001 音频参考设计是采用 DAC11001A 和 DAC11001B 的独特而全面的音频设计。DAC11001 是一种 20 位低噪声超高性能精密 R-2R 数模转换器 (DAC)。 $\Delta-\Sigma$  类型调制器是音频应用中最常用的 DAC。由于针对特定音频要求存在额外设计注意事项，基于精密 R-2R 的 DAC 通常不用于音频应用。此参考设计展示了高保真音频应用中用于动态信号生成的精密 R-2R DAC 的优势和局限性。

## 资源

|             |       |

|-------------|-------|

| TIDA-060031 | 设计文件夹 |

| DAC11001A   | 产品文件夹 |

| DAC11001B   | 产品文件夹 |

| OPA1656     | 产品文件夹 |

| OPA1622     | 产品文件夹 |

## 特性

- 用于音频生成的 20 位精密 R-2R DAC

- $2.1V_{RMS}$  线路电平输出，总谐波失真加噪声 (THD+N) 为 108dB

- 低噪声输出缓冲器

- 高带宽基准缓冲器

- USB 和 TOSLINK® 光输入

- I2S 至串行外设接口 (SPI) 转换

## 应用

- AV 接收器

- 流媒体播放器

- 条形音箱

- 汽车音响主机

请咨询我司 TI E2E™ 支持专家

## 1 系统说明

### 1.1 主要系统规格

表 1-1. 主要系统规格

| 参数     | DAC11001A            | DAC11001B            | 详细信息                    |

|--------|----------------------|----------------------|-------------------------|

| THD+N  | 108dB                | 111dB                | <a href="#">节 3.3.2</a> |

| 动态范围   | 119dB                | 119dB                | <a href="#">节 3.3.4</a> |

| SNR    | 121dB                | 121dB                | <a href="#">节 3.3.6</a> |

| 闲置时的噪音 | 1.9μVRMS             | 1.9μVRMS             | <a href="#">节 3.3.6</a> |

| 线性输出振幅 | 2.1V <sub>RMS</sub>  | 2.1V <sub>RMS</sub>  | <a href="#">节 3.3.6</a> |

| 耳机输出振幅 | 480mV <sub>RMS</sub> | 480mV <sub>RMS</sub> | <a href="#">节 3.3.2</a> |

## 2 系统概述

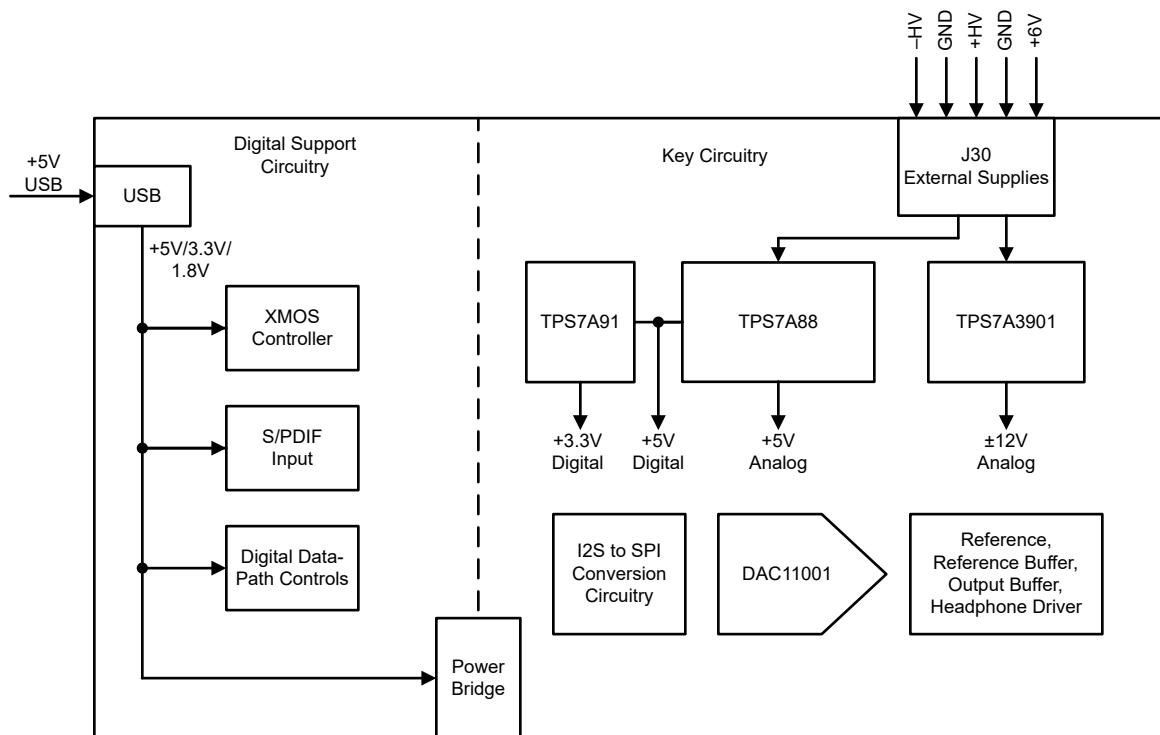

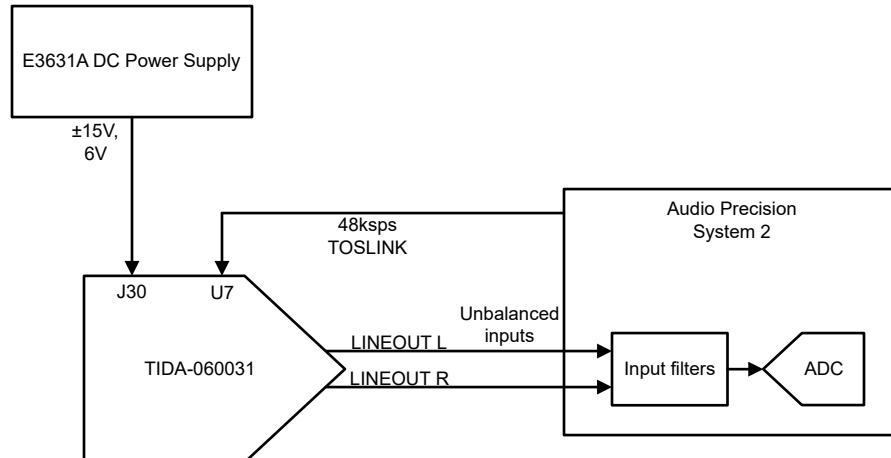

### 2.1 方框图

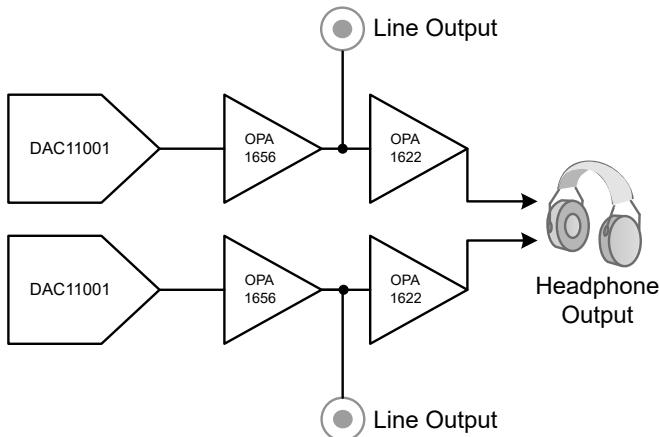

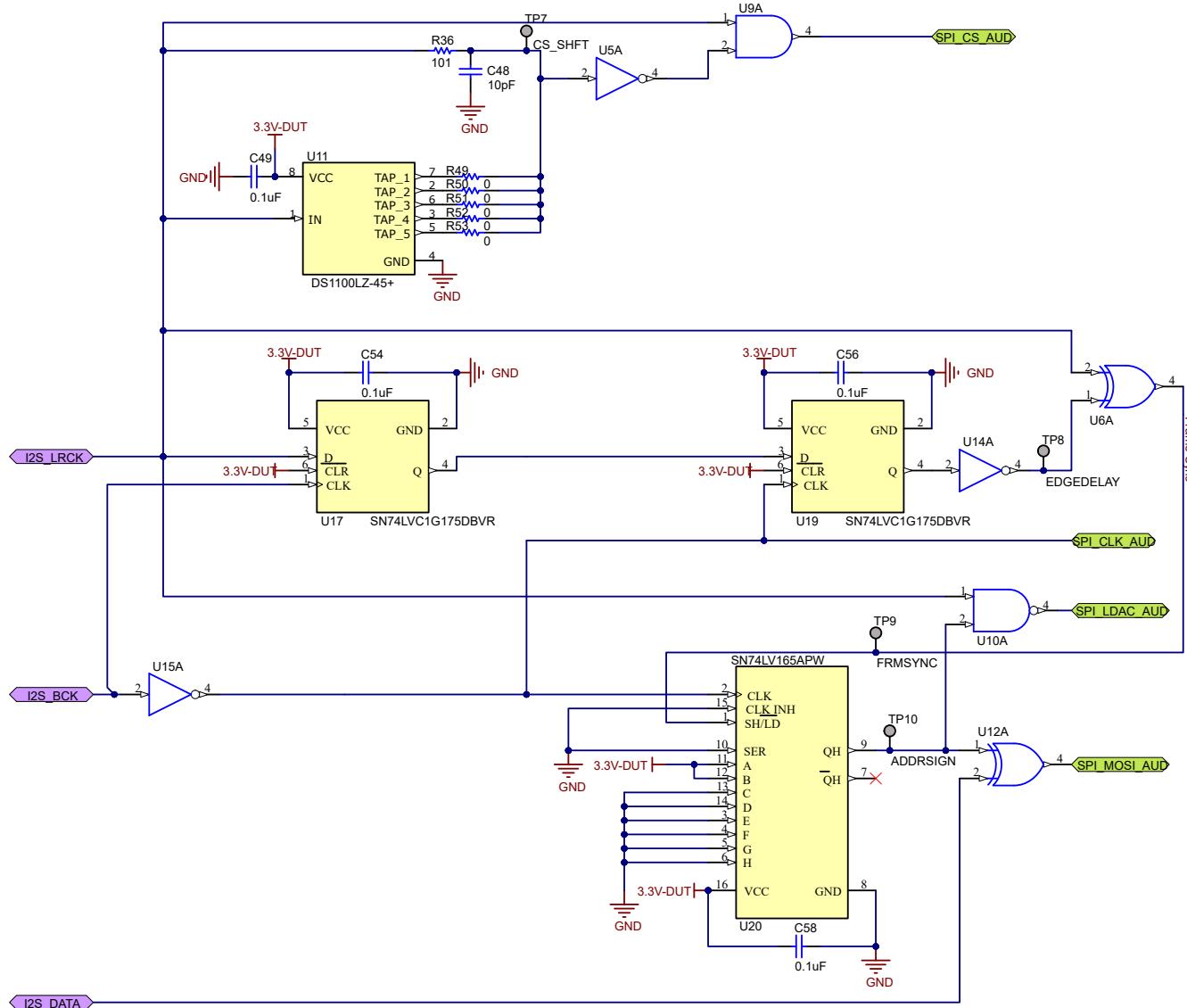

图 2-1. TIDA-060031 方框图

### 2.2 设计注意事项

#### 2.2.1 音频 DAC 和精密 DAC 之间的差异

市面上有多种类型的数模转换器 (DAC)，其中包括通用电压输出 DAC、音频 DAC 等高度专用 DAC 以及 DAC11001A 之类高精度 DAC。适合这些 DAC 的架构有多种。大多数 DAC 使用精密电阻器架构，例如串阻分压器或 R-2R 电阻梯。更专业的 DAC 采用高频开关架构，例如脉宽调制器 (PWM) 或  $\Delta$ -Σ 调制器。

早期的音频 DAC 主要采用 R-2R 梯，但随着数字工艺的改进，多段式  $\Delta$ -Σ 架构开始在大多数产品中取代 R-2R 设计。

这两种架构都有积极和消极的方面。例如，R-2R 电阻梯需要在设计中集成非常精密的电阻器，这会增加成本。此外，大多数电阻梯型设计都存在代码对代码相关误差（例如毛刺），这些误差会影响交流性能。

$\Delta$ -Σ 设计集成了多种形式的误差平均，可减少误差的影响，从而减少对精密模拟元件的需求。然而，这些 DAC 需要更高频率的主时钟来驱动过采样电路。该时钟在较高频率下会产生噪声，而 R-2R 架构具有平坦的噪声曲线。

实际上，在音频 DAC 应用中使用精密 DAC 可能会带来一些困难。首先，精密 DAC 要求低噪声和精确的基准电压。其次，精密 DAC 缺乏数字功能，例如通过过零检测实现音量衰减。最后，精密 DAC 不接受标准 I2S 输入。这意味着必须在设计中添加一些数字逻辑，以将 I2S 转换为 SPI。

此参考设计比较了 DAC11001A 和 DAC11001B 的性能。与 DAC11001A 相比，DAC11001B 在更高的频率下具有更出色的 THD+N 性能。节 2.4.1 [输出毛刺](#) 中介绍了该电路及其优点和限制。

## 2.2.2 右对齐 I2S 到菊花链 SPI 转换

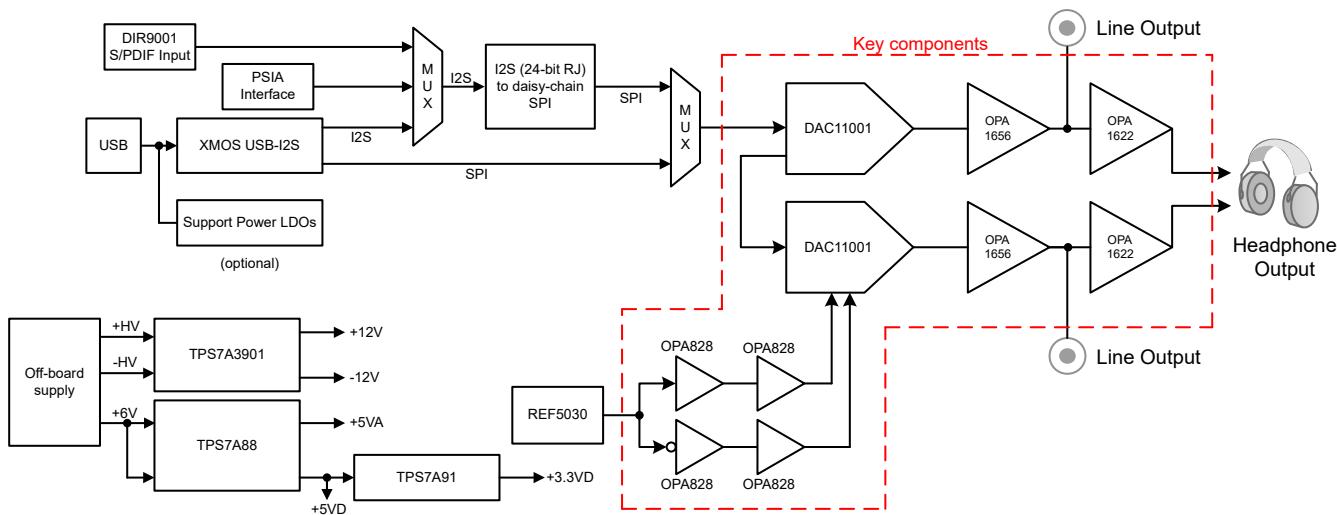

音频器件主要使用集成电路间音频 (I2S) 协议进行通信。I2S 具有位时钟 (BCLK)、左右时钟 (LRCLK) 和数据线。为便于使用，TIDA-060031 采用板载数字逻辑将 24 位、右对齐的 I2S 输入转换为双帧菊花链式 SPI 输出。DAC 设置为菊花链配置。该输出由两个 DAC11001 器件锁存。图 2-2 显示了与所需 SPI 输出重叠的 I2S 输入。

图 2-2. I2S 到菊花链 SPI

在创建 I2S 转 SPI 数字逻辑时，需要克服一些关键设计挑战。

- SPI 时钟与 I2S 时钟相比反转。

- I2S 帧中的 8 个最高有效位不用考虑，而 DAC11001 要求该位是 DAC 地址 0x01。这通过 8 位并行负载移位寄存器 SN74LV165APW 实现。

- DAC11001 的四个最低有效位 (LSB) 不用考虑。这不是大问题，因为 24 位数据在 I2S 中很常见，因此不需要移位。

- LRCK 为 50% 占空比信号，而 DAC11001 需要一条低电平有效芯片选择线路。LRCLK 会延迟并反转，然后与原始 LRCLK 进行“与”运算，以产生 DAC11001 所需的 CS 高脉冲。

- 必须生成 LDAC 信号以使 DAC 同时锁存数据。

- I2S 中的数据值是有符号 24 位整数，而 DAC11001A 需要无符号整数。这意味着必须反转数据值的最高有效位。

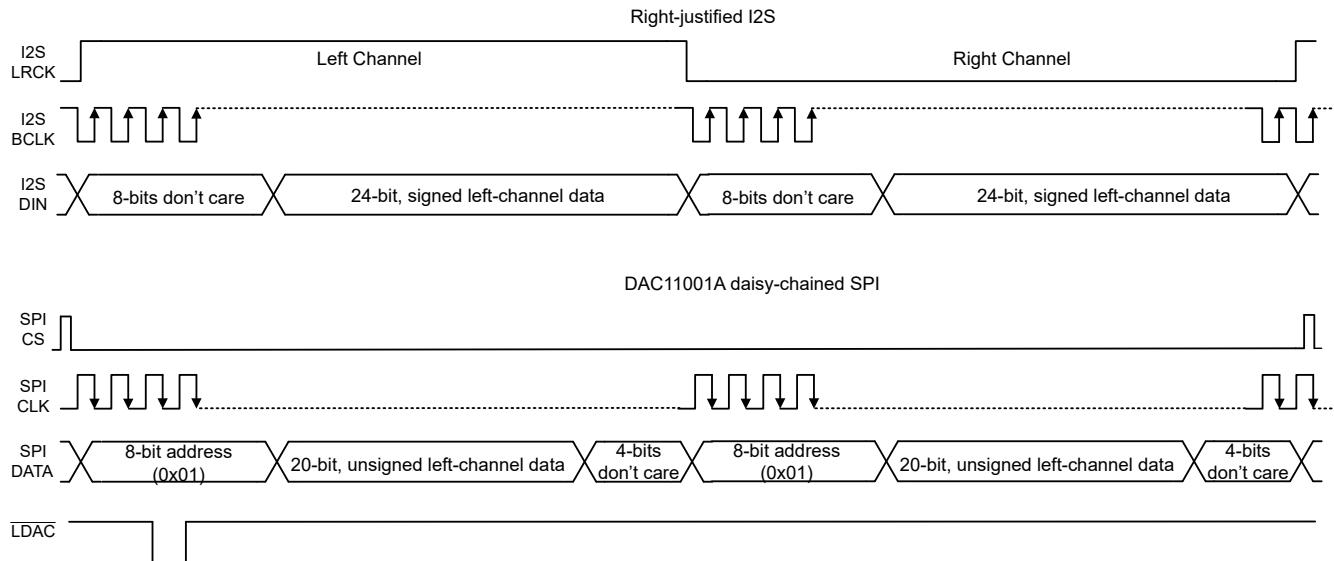

TIDA-060031 使用 图 2-3 中所示的逻辑实现了 I2S 到 SPI 转换。

图 2-3. I2S 到 SPI 转换的数字逻辑

## 2.3 重点产品

### 2.3.1 DAC11001

20 位 DAC11001 是一款高精度、低噪声、电压输出、单通道数模转换器。DAC11001 根据设计具有单调性，并可在所有输出范围内提供出色的线性度。

非缓冲电压输出可提供低噪声性能 ( $7\text{nV}/\sqrt{\text{Hz}}$ ) 和快速稳定时间 ( $1\mu\text{s}$ )，因此这款器件非常适合低噪声、快速控制环路和波形生成应用。DAC11001 兼具增强型抗尖峰脉冲电路以及独立于代码的超低干扰 ( $1\text{nV}\cdot\text{s}$ )，可实现干净的波形斜升和超低总谐波失真 (THD)。

DAC11001 器件包含上电复位电路，因此 DAC 上电时使用寄存器中的已知值。使用外部基准，可以实现  $V_{REFPF}$  到  $V_{REFNF}$  的 DAC 输出，包括非对称输出范围。

DAC11001 配有一个以高达 50MHz 的时钟速率运行的多功能 4 线制串行接口。DAC11001 的额定工业温度范围为  $-40^{\circ}\text{C}$  至  $+125^{\circ}\text{C}$ 。

### 2.3.2 OPA1656

OPA1656 是一种 Burr-Brown™ 运算放大器，专为音频和工业应用而设计，在这些应用中保持信号保真度至关重要。FET 输入架构可达到  $2.9\text{nV}/\sqrt{\text{Hz}}$  的低电压噪声密度和  $6\text{fA}/\sqrt{\text{Hz}}$  低电流噪声密度，能够在各种电路内将噪声降到超低。OPA1656 采用高带宽和高开环增益设计，在 20kHz 时可实现 0.000035% (-129dB) 的低失真，并可在整个音频带宽内提高音频信号保真度。该器件还具有出色的输出电流驱动功能，在  $2\text{k}\Omega$  负载下提供 250mV 电源电压范围内的轨到轨输出摆幅，并且可以提供 100mA 输出电流。

OPA1656 可在  $\pm 2.25\text{V}$  至  $\pm 18\text{V}$  的超宽电源电压范围内工作，也可在仅为 3.9mA 的电源电流 (4.5V 至 36V) 下工作，从而满足许多类型的音频产品的电源限制。额定温度范围为 -40°C 至 +125°C。该器件采用 8 引脚 SOIC 封装。

### 2.3.3 OPA1622

OPA1622 双路双极输入 SoundPlus™ 音频运算放大器的噪声密度极低，仅为  $2.8\text{nV}/\sqrt{\text{Hz}}$ ；在 1kHz 频率下，驱动  $32\Omega$  负载且输出功率为 100mW 时，可获得 -119.2dB 的超低 THD+N。OPA1622 具有极高的交流 PSRR 和 CMRR 规格，可消除电源噪声，因此 OPA1622 非常适合便携式音频应用。该器件还具有 +145mA / -130mA 的高输出驱动能力。

OPA1622 可在  $\pm 2\text{V}$  至  $\pm 18\text{V}$  的非常宽的电源电压范围内运行，每通道电源电流仅为 2.6mA。OPA1622 运算放大器的单位增益稳定，在宽范围负载条件下可保持出色的动态性能。OPA1622 具备关断模式，允许放大器从正常工作切换到通常低于 5μA 的待机电流。这种关断功能专门设计用于消除切换到或退出关断模式时的咔嗒声和砰砰声。

OPA1622 采用独特的内部布局，即便在过驱或过载时也可以实现最低串扰且通道间零交互。该器件的额定工作温度范围为 -40°C 至 +125°C。

### 2.3.4 OPA2828

OPA828 和 OPA2828 (OPAx828) JFET 输入运算放大器是 OPA627 和 OPA827 的下一代产品，兼具高速度、高直流精度和高交流性能。这些运算放大器可提供低失调电压、低温漂、低偏置电流和低噪声，噪声仅为  $60\text{nV}_{\text{RMS}}$  0.1Hz 至 10Hz。OPAx828 在  $\pm 4\text{V}$  至  $\pm 18\text{V}$  的宽电源电压范围内工作，每通道电源电流仅为 5.5mA (典型值)。

凭借各种交流特性，包括 45MHz 增益带宽积 (GBW)、 $150\text{V}/\mu\text{s}$  的压摆率和精密直流特性，OPAx828 系列非常适合用于各种系统。其中包括高速和高分辨率数据采集系统 (例如 16 位和 18 位混合信号系统)、跨阻 (I/V 转换) 放大器、滤波器、精密 ±10V 前端和高阻抗传感器接口应用。

OPAx828 采用 8 引脚 SOIC 封装和热增强型 8 引脚 HVSSOP PowerPAD™ 集成电路封装。

## 2.4 系统设计原理

### 2.4.1 输出干扰

毛刺是影响 THD 性能的一个主要因素。因此，高保真音频性能要求尽可能减少毛刺。R-2R DAC 中诱发毛刺的主要因素来自 R-2R 开关网络。

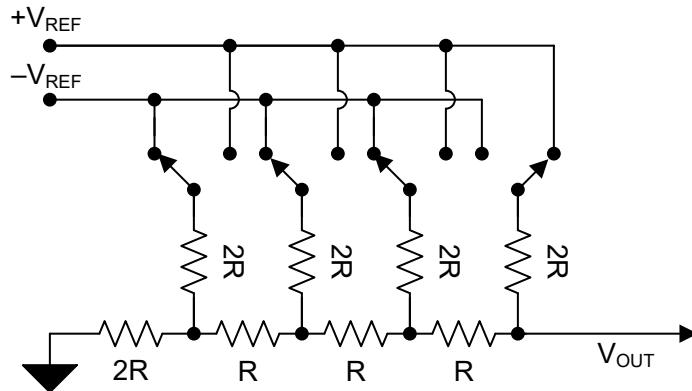

通常，R-2R DAC 架构的每个分辨率位都由两个电阻器 ( $R$  和  $2R$ ) 以及一个将电阻器对连接到 DAC 正基准或负基准电压的开关组成。图 2-4 展示了简化示例。这种架构充当二进制加权分压器。当相对位为高电平时，开关将 R-2R 对连接到正基准。当该位为低电平时，开关对连接到负基准。

图 2-4. R-2R 开关架构

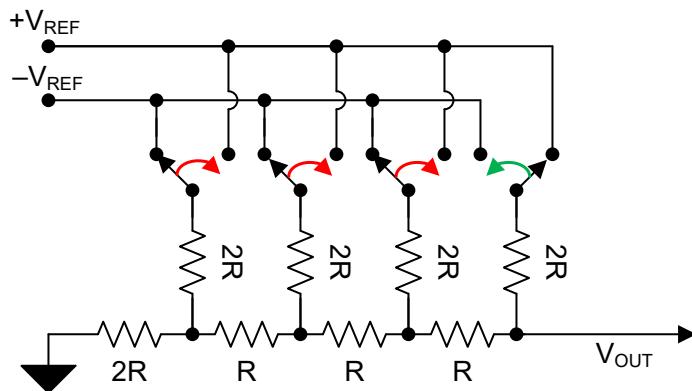

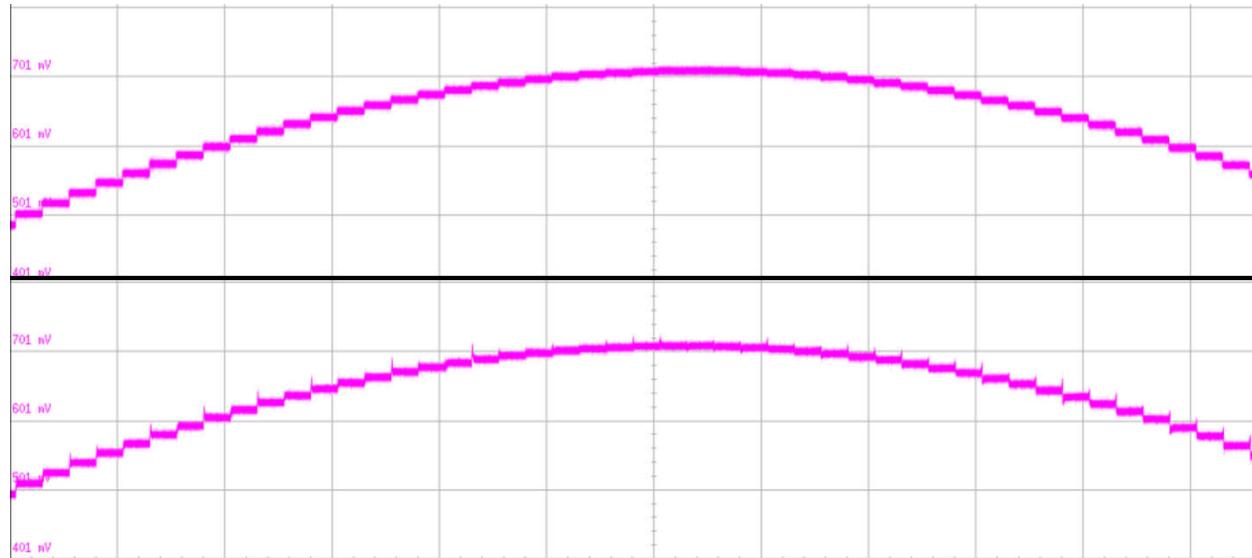

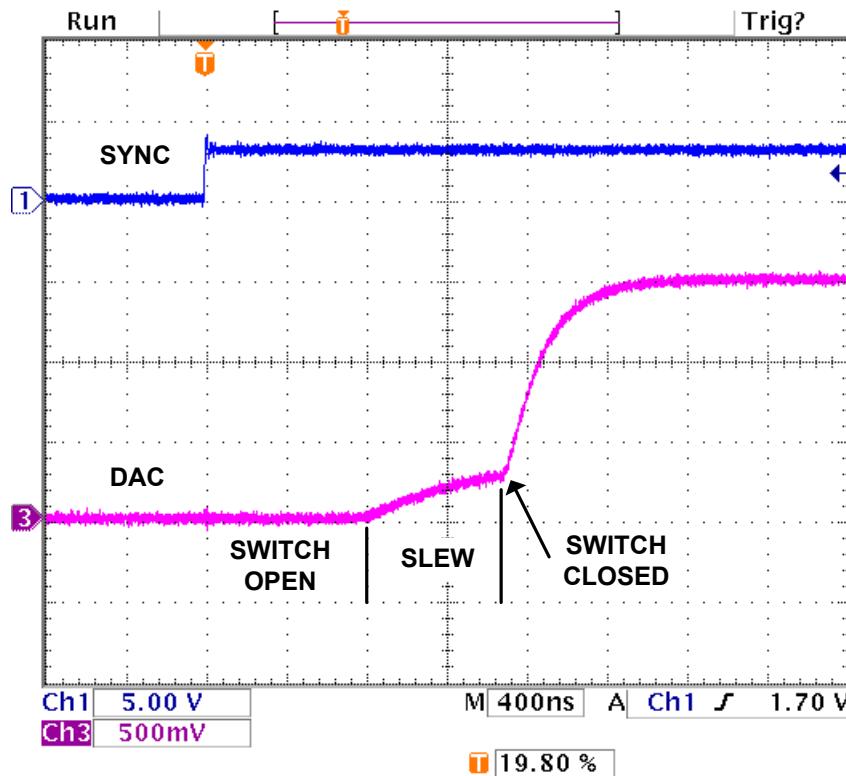

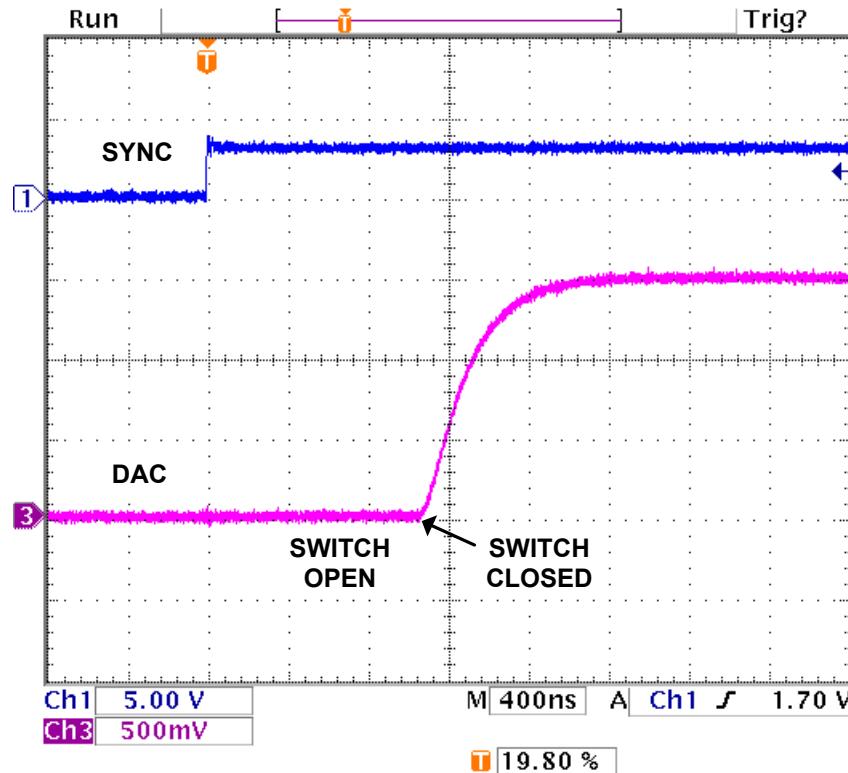

DAC 毛刺定义为与 DAC 的代码转换产生的过冲或下冲相关的能量。即使在仅转换一个代码时也会产生这种毛刺。毛刺能量是 R-2R 开关电荷注入的结果。在 R-2R DAC 中，由于每个开关代表一个位，因此代码更新毛刺很大。代码间毛刺取决于在代码转换期间电阻梯中变化的开关数量。更多的独立位变化会产生更高的毛刺。在 20 位器件中，最严重的代码间毛刺出现在 0xFFFF 和 0x80000 的中幅度代码转换处。此外，R-2R 电阻梯通常需要使用电容较大的开关。更高的电容会增加每个开关的电荷注入。大多数 R-2R DAC 具有双瓣毛刺输出，当 DAC 输出增大时，输出从较小的过冲变成较大的下冲。这种过冲和下冲是 R-2R 开关打开和闭合的特性。图 2-5 展示了一个双瓣毛刺示例。随着高阶谐波的增加或非谐波频率下的额外杂散，可在输出频谱中检测到与代码相关的毛刺能量。

图 2-5. R-2R 开关中标度代码转换

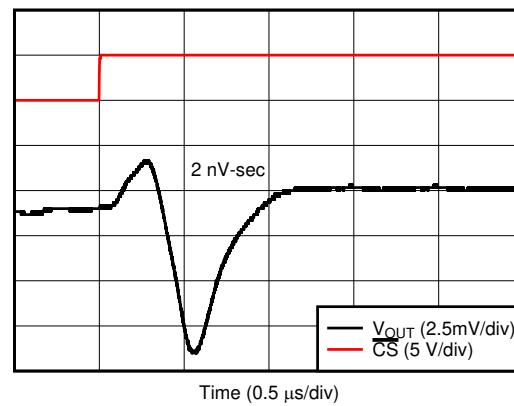

图 2-6. R-2R 输出毛刺

D035

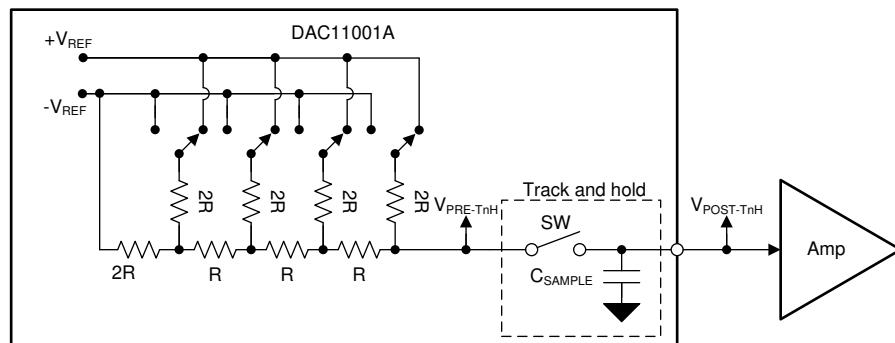

DAC11001 器件具有复杂的高性能跟踪保持 ( $T_{nH}$ ) 电路，可减少该器件中使用的 20 位 R-2R 电阻梯产生的代码间毛刺影响。图 2-7 展示了该电路。该电路在 R-2R 电阻梯的输出端有一个开关和一个采样电容器。当 DAC 代码更新时，跟踪保持开关会在 R-2R 电阻梯发生变化之前断开。采样电容器在初始电压下保持电压稳定，显示为  $V_{POST-T_{nH}}$ 。在 R-2R 电阻梯完成更新后，跟踪保持开关将闭合，从而更新输出电压。跟踪保持电路能够显著降低

DAC 变化时的毛刺，但代价是 DAC 更新速率会受到影响。图 2-8 显示了跟踪保持启用和禁用情况下输出毛刺的比较情况。

图 2-7. DAC11001 跟踪保持图

图 2-8. DAC11001 跟踪保持启用与禁用

通过在电路开启和关闭的情况下以 192kSPS 的采样速率使用 1kHz 音调测量 THD+N，来测试 TnH 电路的有效性。当 TnH 电路接通时，THD+N 测量值为  $-107\text{dB}$ 。当该电路关闭时，THD+N 测量值为  $-73\text{dB}$ 。这个差异为  $34\text{dB}$ ，或者性能下降约 50 倍。

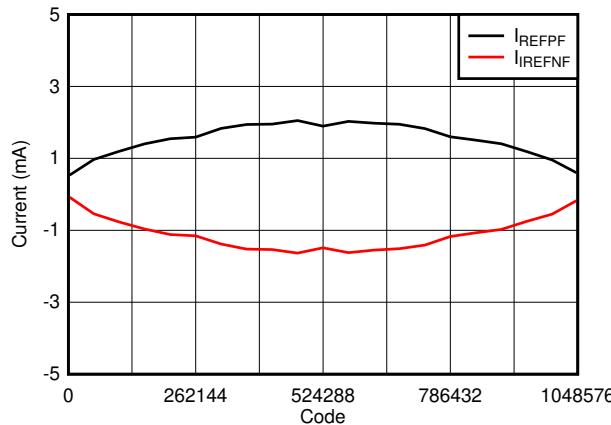

此外，只要 R-2R 开关改变位置，基准输入阻抗就会变化。图 2-9 显示了代码间变化对基准的影响。这种突然的阻抗变化会以压降的形式导致基准出现小毛刺脉冲。虽然跟踪保持电路有助于缓解该干扰，但基准必须在跟踪保持开关断开之前稳定下来。需要快速稳定的基准缓冲器来尽可能地减少来自基准的毛刺。

图 2-9. 基准电流与 DAC 代码间的关系

#### 2.4.2 精密 DAC 中的采样速率相关性

较高的采样速率可通过减少量化噪声来降低 DAC 输出失真。与高速 DAC 和音频 DAC 不同，精密 DAC 的采样速率较低，通常小于 1MSPS。精密 DAC 存在一个阈值，在该点采样速率受到输出稳定时间限制。输出缓冲器必须能够在每次 DAC 代码更新期间稳定下来，以防止输出信号失真。

具有跟踪保持电路的器件在高采样速率方面存在额外的障碍。跟踪保持电路在每次 DAC 更新后都有一定的时间使开关保持断开。如果采样速率超过跟踪保持采样周期，则输出失真。

$\Delta-\Sigma$  设计具有其他形式的误差平均功能，因此这些 DAC 没有这种跟踪保持限制。

#### 2.4.3 系统噪声

在噪声敏感型应用中，目标是尽可能减少 DAC 噪声，从而获得更佳性能。在设计具有非缓冲 R-2R 精密 DAC 的系统时，需要考虑多种噪声源。主要的噪声源包括电源、DAC 基准、基准缓冲器、DAC 输出放大器和 DAC R-2R 电阻器网络。有意地选择元件有助于降低噪声。

电源噪声可能会对系统噪声性能产生不利影响。电源噪声可通过输入滤波器以及去耦和旁路电容器来抑制。去耦电容器可降低电压骤降的影响。旁路电容器充当低通滤波器，以减少电源高频噪声的影响。选择高电源抑制比(PSRR)性能的器件还有助于降低高噪声电源的影响。交流 PSRR 是指器件抑制电源噪声和振荡的能力。表 2-1 显示了参考设计中选择的器件以及数据表中的 PSRR 值。

表 2-1. 参考设计器件的 PSRR

| 器件       | PSRR (1kHz) |

|----------|-------------|

| DAC11001 | 95dB        |

| REF5030  | 130dB       |

| TPS7A39  | 69dB        |

| TPS7A88  | 70dB        |

| TPS7A90  | 60dB        |

基准噪声对 DAC THD+N 性能有直接影响，因为来自基准的任何噪声都会馈送到 DAC 输出。通过选择具有良好噪声性能的基准，可以更大限度地降低基准噪声。某些参考器件（例如 REF5030）具有专用的修整引脚或噪声引脚，可用于改进噪声性能。其他降噪方法包括添加低通滤波器和选择低噪声输出缓冲器。用于基准的缓冲器必须解决快速稳定的需求问题，如输出毛刺部分所述。在快速稳定和低噪声之间找出折衷方案代表了理想的方法。

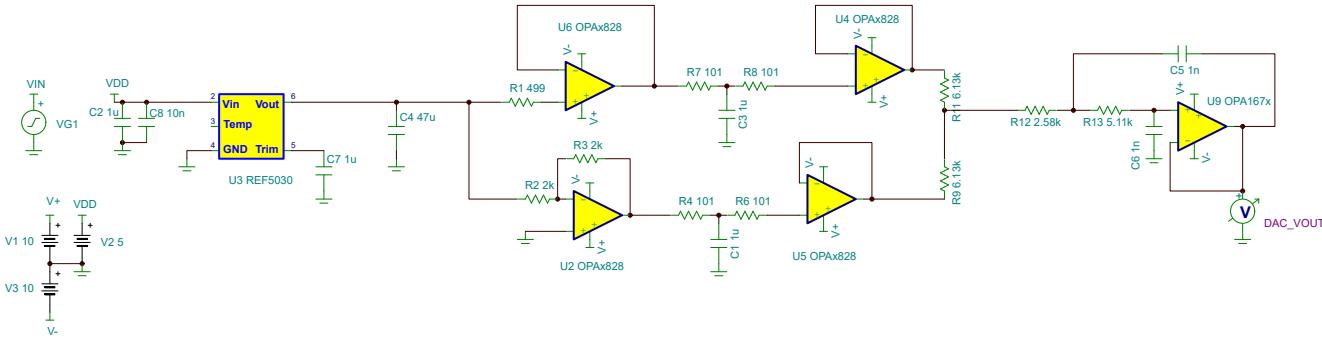

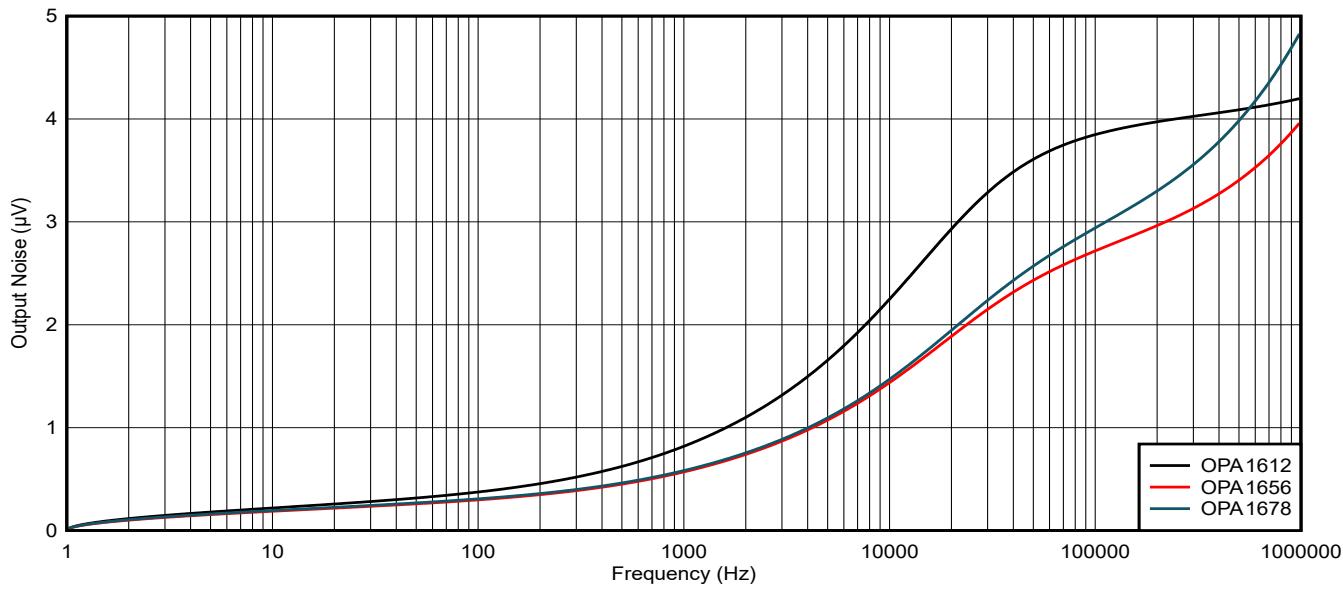

由于 R-2R 电阻器网络，DAC11001 等非缓冲 R-2R DAC 通常具有更高的输出阻抗。选择输出缓冲器时，较高的 DAC 输出阻抗会使电流噪声比电压噪声更受关注。表 2-2 显示了不同运算放大器输入架构的噪声性能。具有双极

输入的运算放大器的电压噪声非常低，但电流噪声较高。OPA1656 等 CMOS 运算放大器倾向于实现低电流噪声，但代价是电压噪声略高。图 2-10 显示了在 TINA-TI™ 中创建的噪声仿真，用于比较连接到高阻抗输出的不同运算放大器。图 2-11 显示了这种噪声仿真的结果。两个 CMOS 运算放大器的性能优于双极 OPA1612。使用 R-2R DAC，由于电流噪声降低，CMOS 运算放大器可实现更好的整体噪声性能。

表 2-2. 运算放大器噪声比较

| 运算放大器   | 输入级  | 1kHz 时的电压噪声               | 1kHz 时的电流噪声                |

|---------|------|---------------------------|----------------------------|

| OPA1612 | 双极   | 1.1nV/ $\sqrt{\text{Hz}}$ | 1700fA/ $\sqrt{\text{Hz}}$ |

| OPA1656 | CMOS | 4.3nV/ $\sqrt{\text{Hz}}$ | 6fA/ $\sqrt{\text{Hz}}$    |

| OPA1678 | CMOS | 4.5nV/ $\sqrt{\text{Hz}}$ | 3fA/ $\sqrt{\text{Hz}}$    |

图 2-10. TINA-TI™ 噪声仿真

图 2-11. 运算放大器噪声仿真比较

#### 2.4.4 DAC11001A 与 DAC11001B 的比较

DAC11001B 是 DAC11001A 的增强版本。这些增强功能包括较低的积分非线性 (INL) 以及改善的跟踪保持电路 (TnH)。

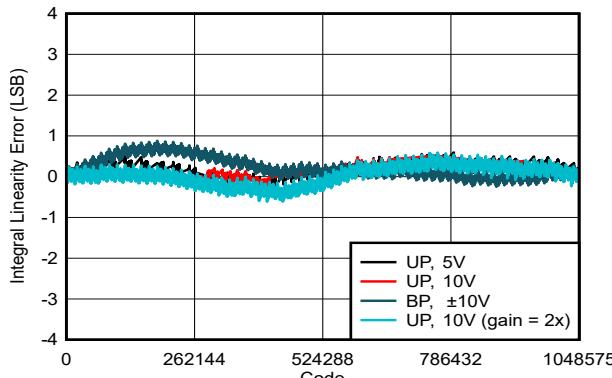

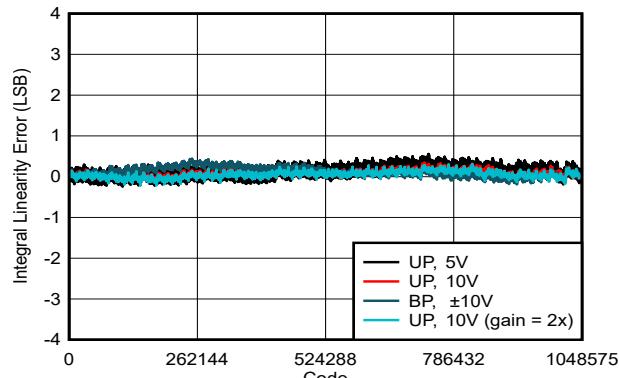

INL 也称为相对精度，用于测量实际 DAC 输出与每个代码的预期理论输出之间的差异。该参数通常以最低有效位 (LSB) 表示。从数学角度来看，INL 是先前代码每个单独代码间误差的总和。DAC11001A 的最大误差为 4LSB，这意味着单个代码与最佳输出可能相差最多四个 LSB，不包括偏移和增益误差。DAC11001B 的最大误差为 1LSB，可提供明显更准确的输出。图 2-12 和 图 2-13 显示了两个数据表中的 INL 比较。

图 2-12. DAC11001A INL

图 2-13. DAC11001B INL

DAC11001A 和 DAC11001B 都实现了跟踪保持子电路，以降低代码间毛刺的影响。如 [输出毛刺](#) 部分所述，在通过开关进行 DAC 更新期间，TnH 电路会将输出与 R-2R 电阻梯分开。该开关为互补的 PMOS 或 NMOS 结构。当开关上的电压高于某个阈值时，这些 MOSFET 会转化为寄生二极管。在 DAC11001A 中，图 2-14 显示了当差分电压大于约 1V 时，TnH 会导致输出压摆。DAC11001B 上的这种限制得到了改进，如图 2-15 所示。

图 2-14. DAC11001A 跟踪保持电压馈通

图 2-15. DAC11001B 跟踪保持无电压馈通

此 TnH 问题通过输出失真直接影响 THD+N。三个参数会影响 DAC11001A TnH 电路：采样速率、输出振幅和音调频率。低采样速率会增加输出更新之间的时间，有可能导致 DAC 更新之间的电压阶跃更大。较大的 DAC 输出范围会直接增加电压变化幅度。在恒定采样速率下，增加音调频率可能会导致输出需要更大的电压变化。可以通过在其他参数中提供足够的余量来解决任何这些参数的影响。例如，如果采样速率足够高，高输出范围就不太可能导致问题。

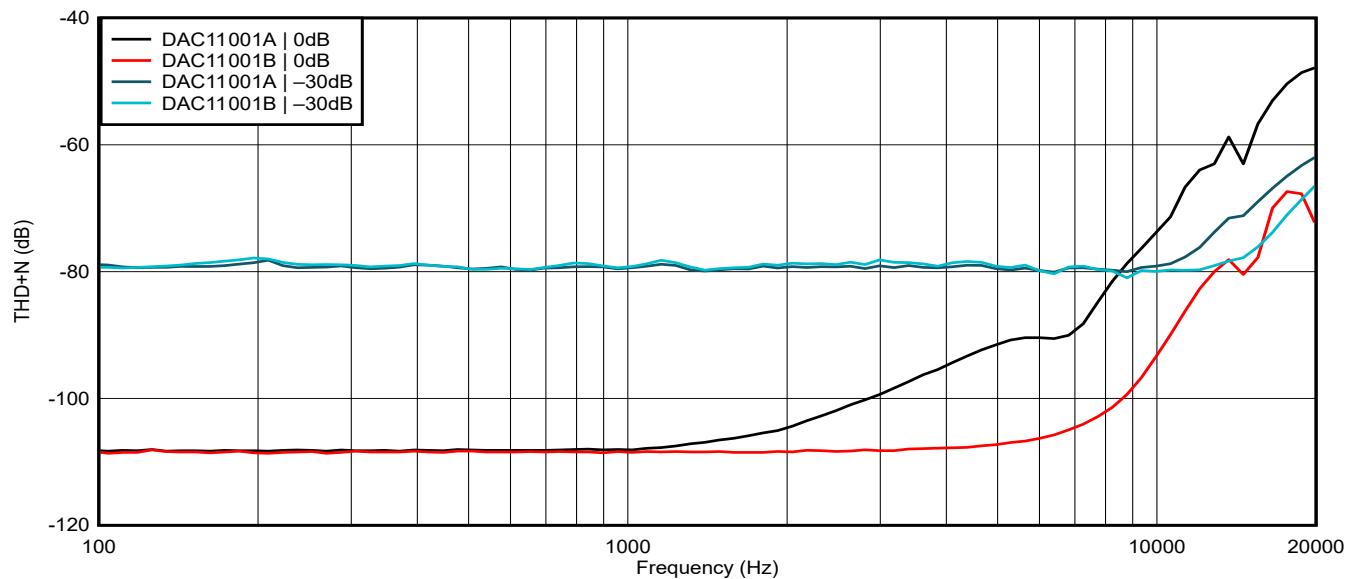

图 2-16 显示了这些不同的参数如何在整个频谱范围内影响 DAC11001A 和 DAC11001B 的 THD+N。该图比较了两个 DAC 的 0dB 和 -30dB 振幅。参考设计的 0dB 输出范围为  $\pm 3V$ 。所有四个数据集均以 192kSPS 的恒定采样速率测量。在 0dB 下，DAC11001A 在 1kHz 时开始在 THD+N 中降低。随着频率增加，电压变化幅度随着更新而增加，这会导致跟踪保持电路产生更多失真。由于 TnH 电路得到改进，直到 5kHz 后 DAC11001B 才开始降低。在 -30dB DAC 中，THD+N 测量值直到 10kHz 才会下降。较低的振幅会降低电压更新变化的最大幅度，进而防止额外的 TnH 失真。虽然 TnH 电路不会产生失真，但在 -30dB 振幅下，总体 THD+N 测量结果更差，因为 DAC 输出振幅更接近本底噪声。

图 2-16. 跟踪保持电路比较

### 3 硬件、软件、测试要求和测试结果

#### 3.1 硬件要求

##### 3.1.1 需要外部电源

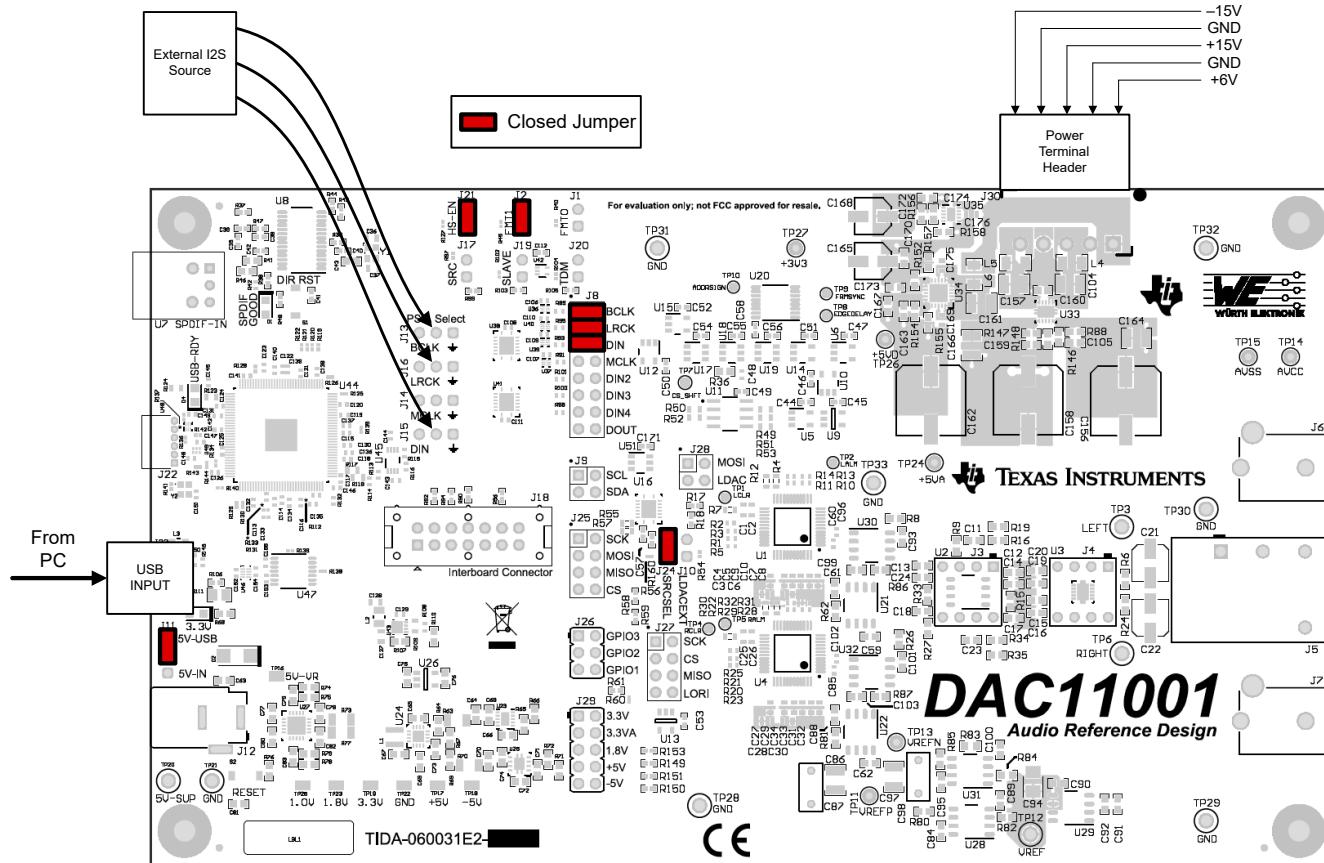

TIDA-060031 需要两个电源。该设计的左侧主要配备用于数字输入和 USB 接口的支持电路。图 3-1 显示该电路可由 USB 输入供电，或通过电源桥由外部电源供电。

电路板的右侧具有关键模拟电路，特别是 DAC、DAC 基准和基准缓冲器以及 DAC 输出缓冲器。该侧还有一些数字控制电路，用于管理 SPI 数据路径以及将传入的 RJ I2S 数据转换为菊花链式 SPI 格式。电路板的这一侧需要外部电源。

图 3-1. 电源配置

图 3-1 显示了 TIDA-060031 设计的电源输入。端子块 J30 用于关键电路的外部电源。表 3-1 显示了 J30 定义。

表 3-1. 电源输入

| J30 引脚 | 说明                                               | 值和限制                     |

|--------|--------------------------------------------------|--------------------------|

| J30.1  | 低压电源 +6V。该电源用于关键电路的 5V 模拟电源、5V 数字电源 和 3.3V 数字电源。 | +6V 输入，300mA 限制          |

| J30.2  | 接地                                               | 接地                       |

| J30.3  | 正高压电源输入。这用于关键电路的 +12V 电源。                        | +12.5 至 +15V，200mA 限制    |

| J30.4  | 接地                                               | 接地                       |

| J30.5  | 负高压电源输入。这用于关键电路的 -12V 电源。                        | - 12.5V 至 - 15V，200mA 限制 |

如果未使用 USB 输入（I2S 由 S/PDIF 输入提供或直接连接到该设计），则不需要 USB 电源。关键电路侧的 +3.3V 电源可用于为电路板左侧的最小支持电路供电。这可通过在电源电桥（J29，位置 1-2）上连接 3.3V 电源来实现。

##### 3.1.2 跳线定义

表 3-2 详细介绍了跳线定义。

表 3-2. 跳线定义

| 跳线    | 名称                    | 说明                                                                                                                                                                  |

|-------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J1、J2 | S/PDIF 格式选择           | FMT1 短路、FMT0 短路：16 位，MSB 在前，右对齐<br>FMT1 短路，FMT0 开路：24 位，MSB 在前，右对齐。默认，这是 TIDA-060031 唯一支持的格式。<br>FMT1 开路，FMT0 短路：24 位 MSB 在前，左对齐<br>FMT1 开路，FMT0 开路：24 位，MSB 在前，I2S |

| J10   | 外部 LDAC 选型            | 短路：LDAC 短接至地线。<br>开路：LDAC 上拉至高达 3.3V。                                                                                                                               |

| J11   | USB 电源选择              | 短接 1-2 (5V-IN)：J12 用作电路板左侧的 +5V 输入。<br>短接 2-3 (5V-USB)：建议使用 USB 输入为电路板左侧供电。                                                                                         |

| J13   | BCLK 选择               | 短接 2-3：选择 USB 或 S/PDIF BCLK 输入作为 I2S 源。<br>与 1-2 的外部连接：引脚 1 为接地。这允许将外部 I2S BCLK 源（例如 PSIA）连接到 EVM。                                                                  |

| J14   | MCLK 选择               | 短接 2-3：选择 USB 或 S/PDIF MCLK 输入作为 I2S 源。TIDA-060031 上不需要这样，因为未使用 MCLK 信号。<br>与 1-2 的外部连接：引脚 1 为接地。这允许将外部 I2S 源（例如 PSIA）连接到 EVM。                                      |

| J15   | DIN 选择                | 短接 2-3：选择 USB 或 S/PDIF DIN 输入作为 I2S 源。<br>与 1-2 的外部连接：引脚 1 为接地。这允许将外部 I2S DIN 源（例如 PSIA）连接到 EVM。                                                                    |

| J16   | LRCK 选择               | 短接 2-3：选择 USB 或 S/PDIF LRCK 输入作为 I2S 源。<br>与 1-2 的外部连接：引脚 1 为接地。这允许将外部 I2S LRCK 源（例如 PSIA）连接到 EVM。                                                                  |

| J17   | DIR9001 (S/PDIF) 输入选择 | 短路：将 DIR9001 输入连接到 I2S 数据路径。<br>开路：将 USB I2S 源连接到 I2S 数据路径。                                                                                                         |

| J19   | I2S 目标选择              | 在 TIDA-060031 上不受支持，保持断开。                                                                                                                                           |

| J20   | I2S TDM 模式选择          | 在 TIDA-060031 上不受支持，保持断开。                                                                                                                                           |

| J21   | XMOS 高速 USB           | 短路：允许将 TIDA-060031 检测为 USB2.0 器件并支持 192kHz 采样速率。                                                                                                                    |

| J22   | JTAG 输入               | 此接头允许 JTAG 输入。                                                                                                                                                      |

| J24   | SPI 源选择               | 短路：I2S 到 SPI 转换电路的 SPI 输出连接到 DAC11001A 器件。<br>开路：来自 SPI 输入桥 (J25) 的 SPI 输入连接到 DAC11001A 器件。                                                                         |

表 3-3. 输入和输出连接器

| 跳线  | 名称      | 说明                    |

|-----|---------|-----------------------|

| J5  | 耳机输出    | 耳机输出。组合了左右 DAC 输出。    |

| J6  | 左侧留声机插孔 | 左侧线路输出。               |

| J7  | 右侧留声机插孔 | 右侧线路输出。               |

| J12 | 5V 数字输入 | 数字侧的 5V 直流电源插孔。       |

| J23 | USB 输入  | USB 输入。如果不需要，请保持插头拔出。 |

表 3-4. I2S、SPI、GPO 和电源桥

| 跳线  | 名称      | 说明                                                              |

|-----|---------|-----------------------------------------------------------------|

| J8  | I2S 连接桥 | 此连接允许将 I2S 输入连接到 DAC 和支持电路。TIDA-060031 参考设计仅需要 LRCK、BCLK 和 DIN。 |

| J9  | I2C 连接桥 | TIDA-060031 参考设计不使用 I2C。                                        |

| J18 | I2S 至接地 | 该接头将 I2S 信号接地。这些连接可保留为未组装。                                      |

**表 3-4. I2S、SPI、GPO 和电源桥 (续)**

| 跳线  | 名称              | 说明                                                                                                                            |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------|

| J25 | SPI 连接桥         | 这种连接允许 XMOS 控制器生成 SPI 以配置 DAC11001A 器件。默认情况下，该参考设计不需要进行配置。需要专用软件来运行 SPI。默认情况下，这些连接可保留为未组装。                                    |

| J26 | GPO 连接桥         | 这种连接允许 XMOS 控制器设置几条与 SPI 配合使用的控制线路。默认情况下，这些可保留为未组装。                                                                           |

| J27 | SPI 输入          | 如果改用 SPI，则可使用此连接绕过 I2S 电路。                                                                                                    |

| J28 | PICO-LDAC 至 GND | 该连接将 SPI PICO 和 LDAC 短接至地线。                                                                                                   |

| J29 | 电源连接桥           | 该连接允许在参考设计和 USB 控制器之间共享电源。默认情况下，该连接可以保留为未组装。可以在 J29.1-2 (3.3V) 上放置一根跳线，为电路板左侧的 3.3V 电路供电。如果使用外部或 S/PDIF 输入这会很有用，因为不需要 USB 输入。 |

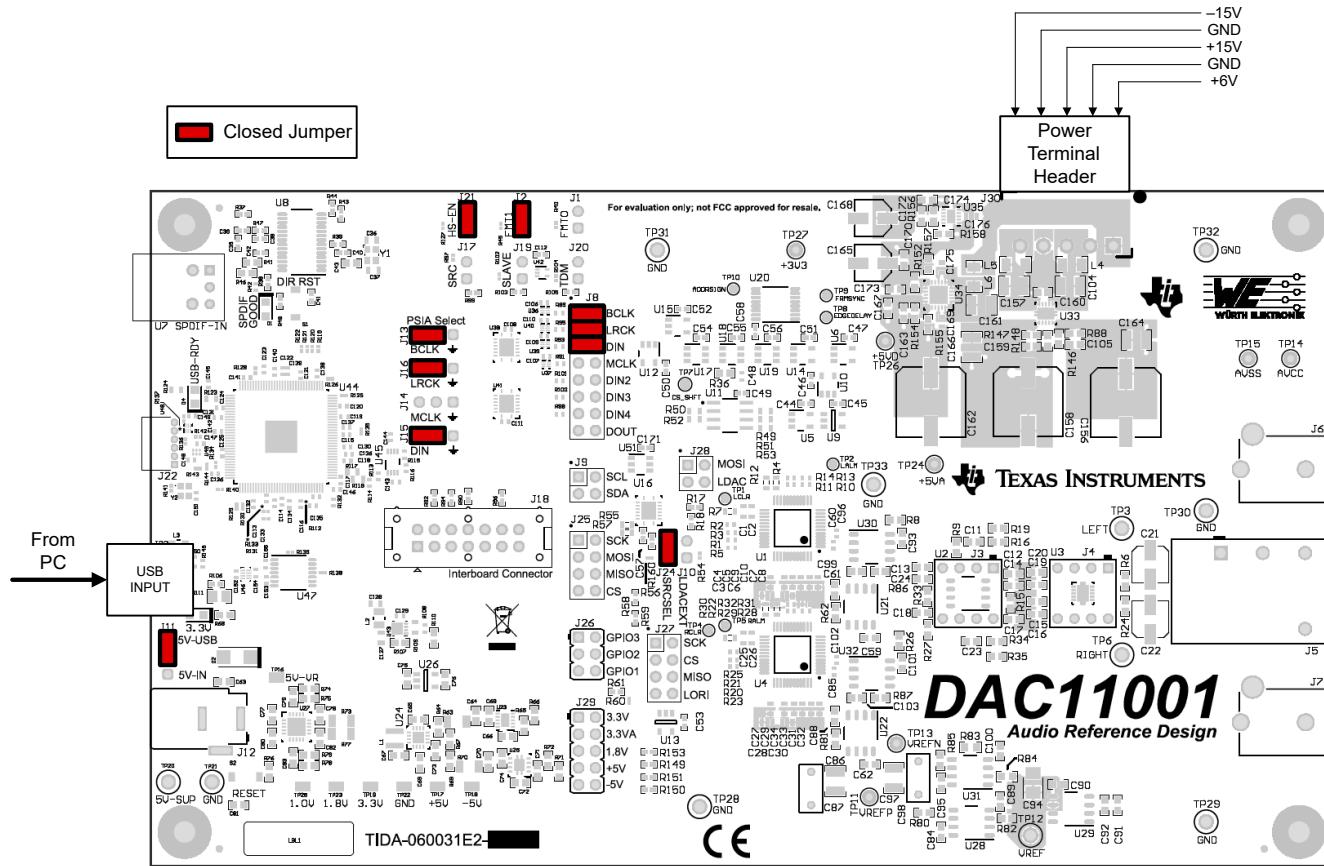

### 3.1.3 选择 I2S 源

本节介绍了可与 TIDA-060031 参考设计一起使用的各种输入配置。

#### 3.1.3.1 USB I2S 源

评估 DAC11001A 音频性能的最简单方法是使用 USB 输入。图 3-2 展示了用于选择 USB 的跳线配置。

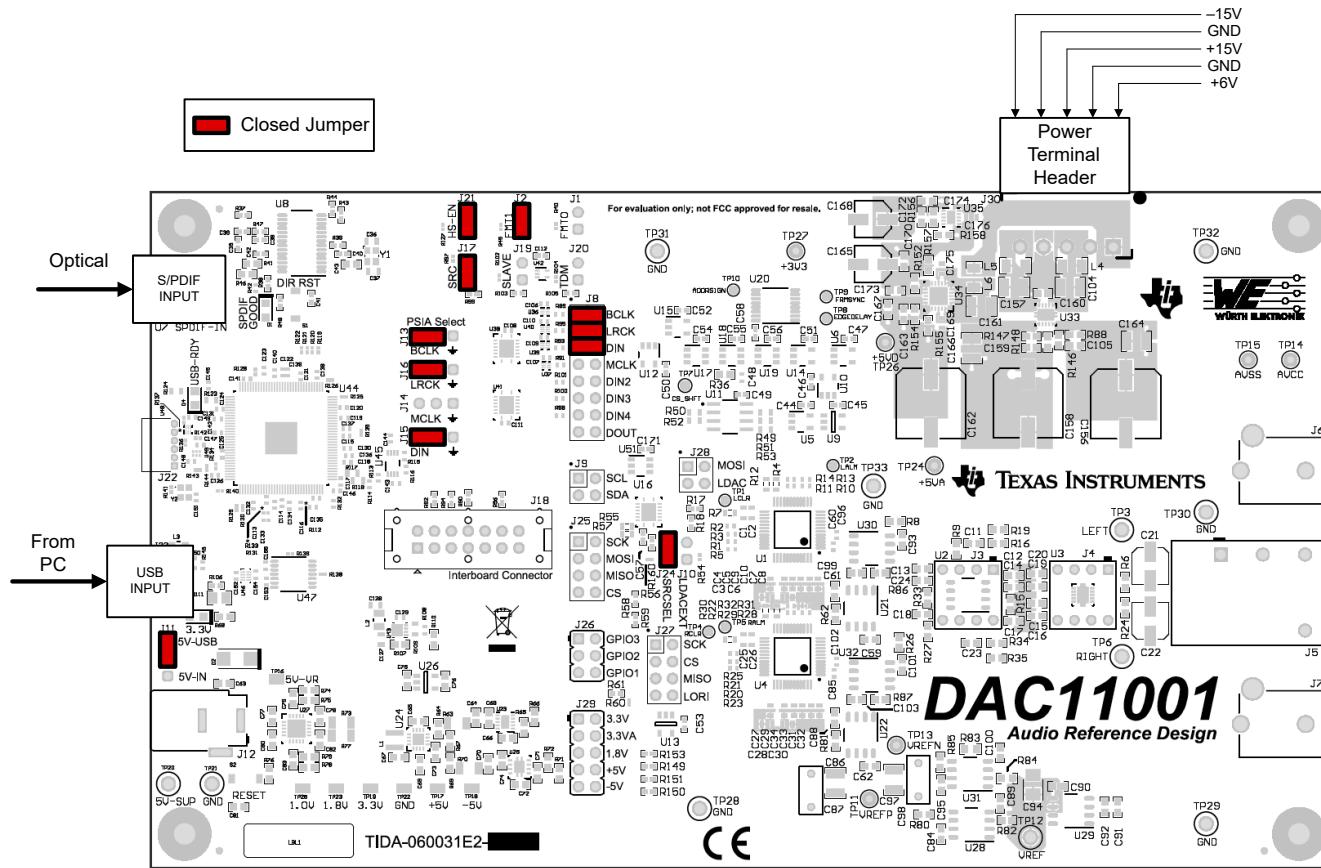

### 3.1.3.2 SPDIF I2S 源

图 3-3 显示了在 TIDA-060031 参考设计中使用光学 SPDIF 输入作为音频源的跳线配置。这仅支持 48kSPS 输入。

### 3.1.3.3 外部 PSIA I2S 源

可以使用 PSIA 输入接头 J13-J16 为 TIDA-060031 提供外部 I2S 输入。为此，移除 J13-J16 上的跳线并将 I2S 输入连接到 1-2 位置的接头。该接头上的引脚 1 接地，以实现更干净的数字连接。I2S 输入必须配置为 24 位右对齐模式。

图 3-4. 外部 I2S 输入配置

## 3.2 软件要求

TIDA-060031 参考设计不需要任何控制软件。USB 接口需要驱动程序。安装驱动程序的最简单方法是安装 PurePath™ Console 软件。

### 3.2.1 安装 XMOS USB 2.0 驱动程序

可以通过以下登录页面请求访问 PurePath Console 软件：[PurePath Console](#)。获得访问权限后，请从 [ti.com/securereresources](http://ti.com/securereresources) 下载该软件。

成功安装驱动程序后，PC 会将 TIDA-060031 检测为 *TUSBAudio Eval UAC2.0 (BB04)*。

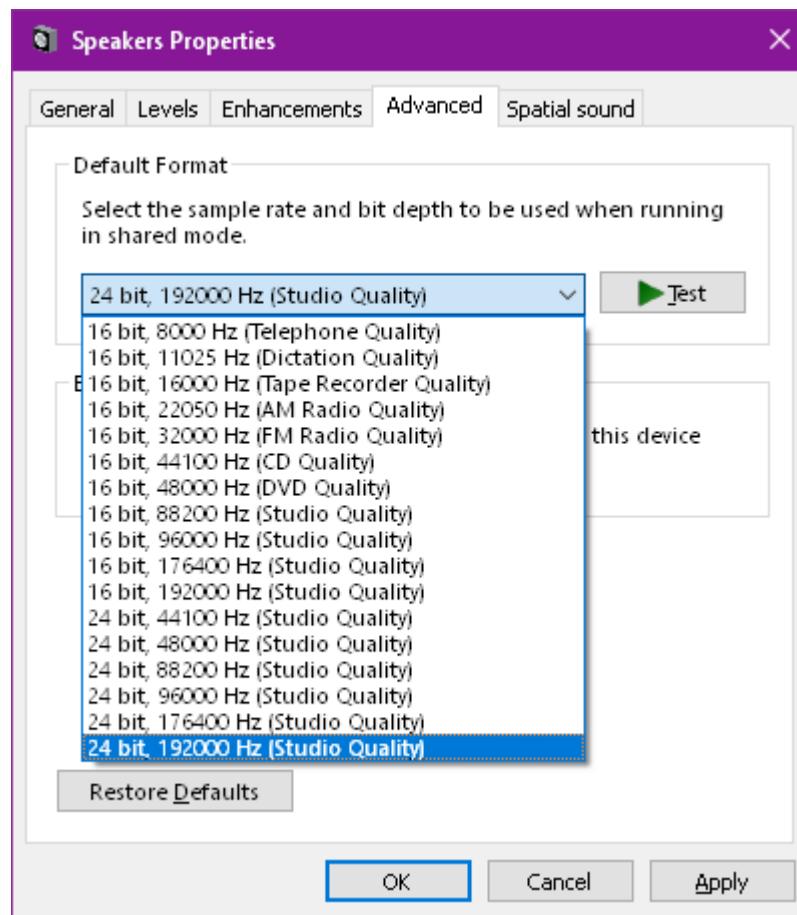

### 3.2.2 设置 USB 采样速率

USB 输入的采样速率由 PC 设置中音频器件的采样速率设置决定。访问器件属性以设置采样速率。图 3-5 显示了使用 24 位 190000Hz 进行测试。Microsoft® Windows® 要求在更改速率后重新启动播放音频源的任何软件。

图 3-5. 用于选择采样速率的 Speaker Properties ( 扬声器属性 ) 菜单

### 3.3 测试和结果

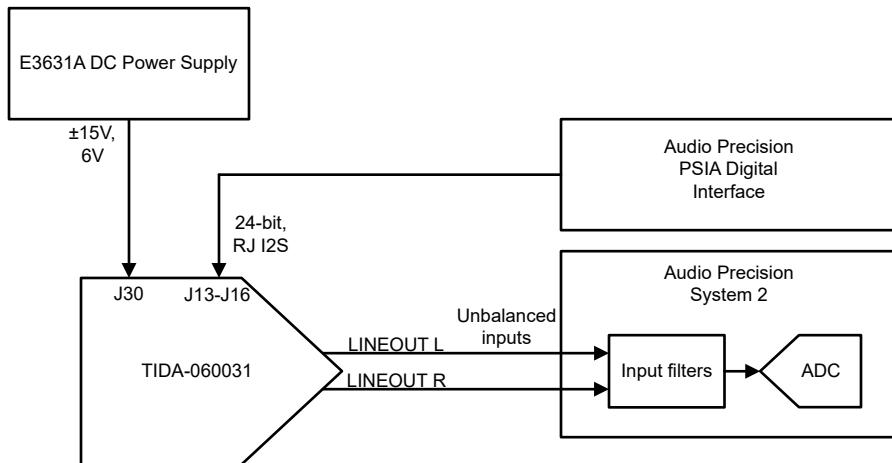

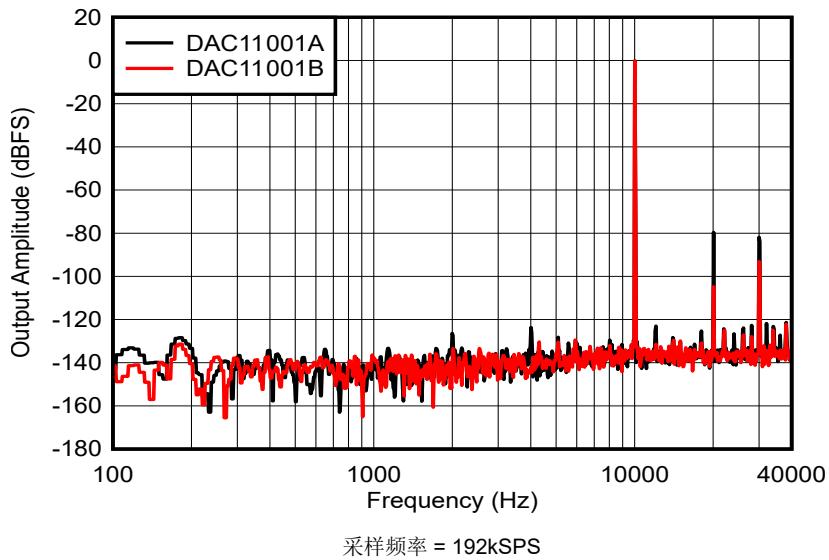

#### 3.3.1 测量总谐波失真和噪声

使用 Audio Precision System 2 (AP2) 测量 THD+N。AP2 配有外部 I2S 源，配置为 24 位数据，采用右对齐输出模式。I2S 信号连接到 TIDA-060031 设计中的 I2S 输入连接器 J13-J16。

图 3-6. THD+N 测量设置

表 3-5. THD+N 输入滤波器

| 采样速率    | 滤波器                          |

|---------|------------------------------|

| 48kSPS  | 22Hz 高通滤波器、20kHz AES17 低通滤波器 |

| 96kSPS  | 22Hz 高通滤波器、40kHz AES17 低通滤波器 |

| 192kSPS | 22Hz 高通滤波器、40kHz AES17 低通滤波器 |

#### 3.3.2 THD 和 THD+N 结果

表 3-6 和 表 3-7 展示了各种振幅、音调和采样速率下的 THD+N 测量结果。

表 3-6. DAC11001A THD+N 测量结果

| 输入振幅     | 音调频率  | 采样速率   |        |         |

|----------|-------|--------|--------|---------|

|          |       | 48kSPS | 96kSPS | 192kSPS |

| 0dBFS    | 1kHz  | -107dB | -107dB | -108dB  |

|          | 2kHz  | -94dB  | -101dB | -106dB  |

|          | 5kHz  | -56dB  | -74dB  | -92dB   |

|          | 10kHz | -49dB  | -45dB  | -73dB   |

| - 60dBFS | 1kHz  | -55dB  | -51dB  | -50dB   |

|          | 2kHz  | -54dB  | -50dB  | -49dB   |

|          | 5kHz  | -56dB  | -50dB  | -49dB   |

|          | 10kHz | -57dB  | -50dB  | -50dB   |

表 3-7. DAC11001B THD+N 测量结果

| 输入振幅  | 音调频率  | 采样速率   |        |         |

|-------|-------|--------|--------|---------|

|       |       | 48kSPS | 96kSPS | 192kSPS |

| 0dBFS | 1kHz  | -111dB | -108dB | -108dB  |

|       | 2kHz  | -110dB | -108dB | -108dB  |

|       | 5kHz  | -75dB  | -97dB  | -106dB  |

|       | 10kHz | -47dB  | -69dB  | -92dB   |

表 3-7. DAC11001B THD+N 测量结果 (续)

| 输入振幅    | 音调频率  | 采样速率   |        |         |

|---------|-------|--------|--------|---------|

|         |       | 48kSPS | 96kSPS | 192kSPS |

| -60dBFS | 1kHz  | -55dB  | -51dB  | -50dB   |

|         | 2kHz  | -53dB  | -50dB  | -49dB   |

|         | 5kHz  | -55dB  | -50dB  | -40dB   |

|         | 10kHz | -57dB  | -50dB  | -50dB   |

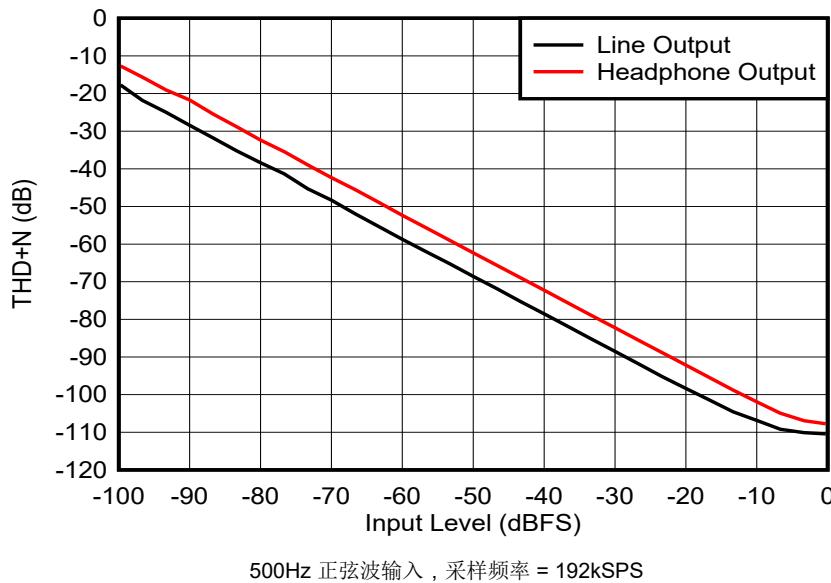

图 3-7 展示了 THD+N 随着输入电平幅度的增加而改善。这是因为当噪声水平保持不变时，DAC 输出的幅度会增加。THD+N 值的线性下降表明，THD+N 主要由噪声决定。耳机振幅比线路振幅低约 12dB，这反映在稍差的 THD+N 结果中。

图 3-7. 线路和耳机输出 THD+N 与输入电平间的关系

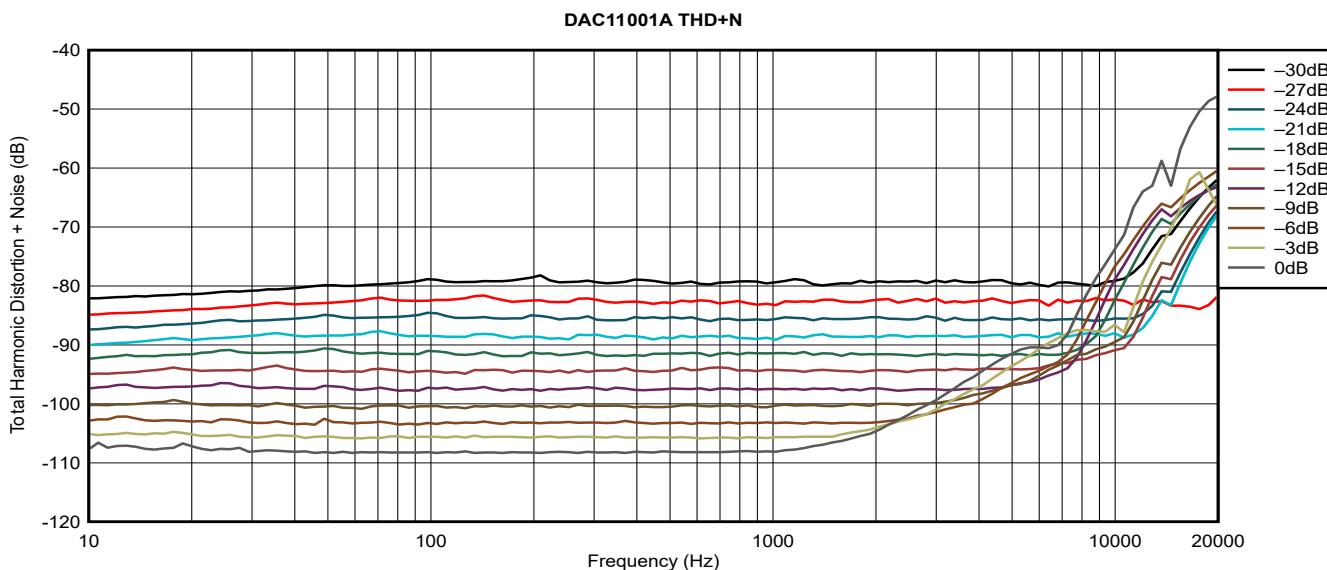

图 3-8 中所示的行为展示了与 DAC11001A 相比，DAC11001B 跟踪保持设计的性能得到增强。DAC11001B 在更高的频率下保持更平坦的 THD+N 曲线。

图 3-8. 线路输出 THD+N 与频率和振幅间的关系

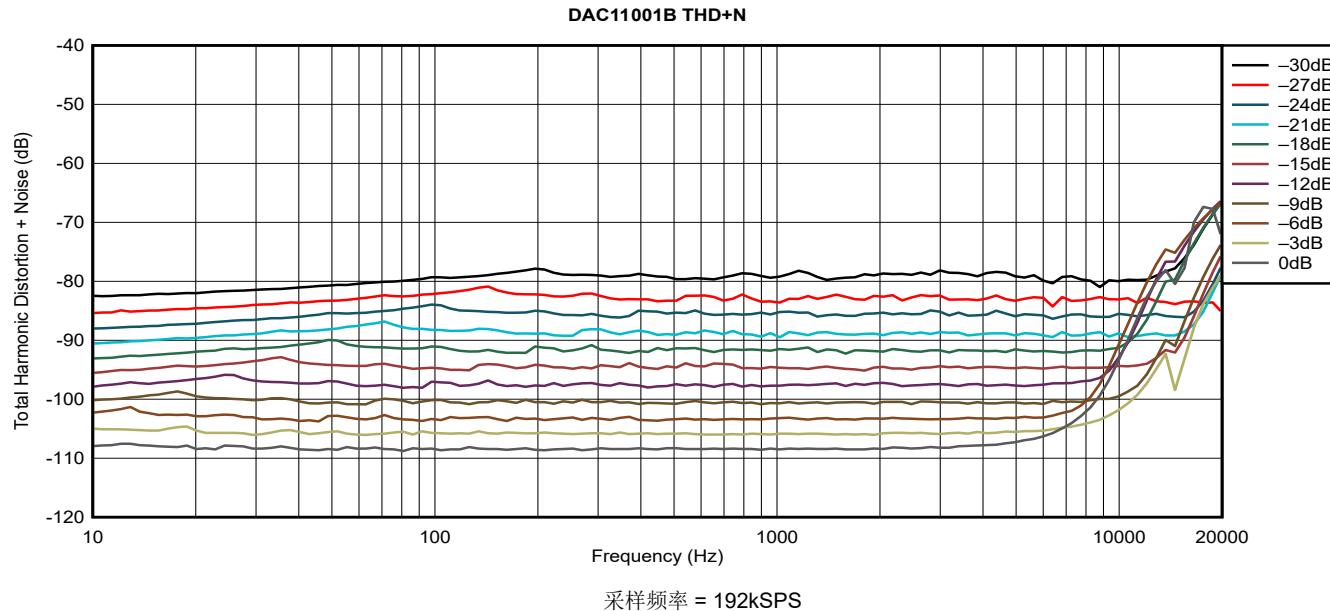

图 3-9 显示了 DAC11001 在 10k 音调下的噪声和谐波性能。

图 3-9. 10kHz 正弦波下的可闻范围 FFT

### 3.3.3 测量动态范围

图 3-10. 动态范围测量设置

表 3-8. 动态范围输入滤波器

| 采样速率    | 滤波器                               |

|---------|-----------------------------------|

| 48kSPS  | 22Hz 高通滤波器、20kHz AES17 低通滤波器，A 加权 |

| 96kSPS  | 22Hz 高通滤波器、40kHz AES17 低通滤波器，A 加权 |

| 192kSPS | 22Hz 高通滤波器、40kHz AES17 低通滤波器，A 加权 |

### 3.3.4 动态范围结果

表 3-9 显示了 DAC11001 的动态范围。

表 3-9. 动态范围测量结果

| 输入振幅     | 音调频率  | 采样速率                      |                           |                           |

|----------|-------|---------------------------|---------------------------|---------------------------|

|          |       | 48kSPS                    | 96kSPS                    | 192kSPS                   |

| - 60dBFS | 1kHz  | - 117dB ( THD+N : -57dB ) | - 117dB ( THD+N : -57dB ) | - 115dB ( THD+N : -55dB ) |

|          | 2kHz  | - 118dB ( THD+N : -58dB ) | - 117dB ( THD+N : -57dB ) | - 115dB ( THD+N : -55dB ) |

|          | 10kHz | - 113dB ( THD+N : -53dB ) | - 118dB ( THD+N : -58dB ) | - 119dB ( THD+N : -59dB ) |

### 3.3.5 测量信噪比

图 3-11 显示了 SNR 测量设置。

图 3-11. SNR 测量设置

**表 3-10. SNR 输入滤波器**

| 采样速率    | 滤波器                               |

|---------|-----------------------------------|

| 48kSPS  | 22Hz 高通滤波器、20kHz AES17 低通滤波器，A 加权 |

| 96kSPS  | 22Hz 高通滤波器、40kHz AES17 低通滤波器，A 加权 |

| 192kSPS | 22Hz 高通滤波器、40kHz AES17 低通滤波器，A 加权 |

**3.3.6 SNR 结果**

表 3-11 和 表 3-12 展示了 DAC11001A 和 DAC11001B 的 SNR 结果。一些噪声由数字发送器产生，因而导致 SNR 略差。数字发送器关闭时的 SNR 如表 3-13 所示。

**表 3-11. DAC11001A 信噪比测量**

| 输入振幅       | 音调频率 | 采样速率                   |                        |                       |

|------------|------|------------------------|------------------------|-----------------------|

|            |      | 48kSPS                 | 96kSPS                 | 192kSPS               |

| 100% 满量程   | 1kHz | 2.115V <sub>RMS</sub>  | 2.112V <sub>RMS</sub>  | 2.112V <sub>RMS</sub> |

| 0% 满量程，无抖动 | 不适用  | 1.893μV <sub>RMS</sub> | 2.038μV <sub>RMS</sub> | 2.29μV <sub>RMS</sub> |

| SNR 计算值    |      | 120.9dB                | 120.3dB                | 119.3dB               |

**表 3-12. DAC11001B 信噪比测量**

| 输入振幅       | 音调频率 | 采样速率                   |                        |                        |

|------------|------|------------------------|------------------------|------------------------|

|            |      | 48kSPS                 | 96kSPS                 | 192kSPS                |

| 100% 满量程   | 1kHz | 2.115V <sub>RMS</sub>  | 2.112V <sub>RMS</sub>  | 2.112V <sub>RMS</sub>  |

| 0% 满量程，无抖动 | 不适用  | 1.858μV <sub>RMS</sub> | 2.039μV <sub>RMS</sub> | 2.325μV <sub>RMS</sub> |

| SNR 计算值    |      | 121.1dB                | 120.3dB                | 119.2dB                |

**表 3-13. DAC11001 信噪比 ( 无数字 )**

| 输入振幅        | 音调频率 | 结果                     |

|-------------|------|------------------------|

| 100% 满量程    | 1kHz | 2.115V <sub>RMS</sub>  |

| 0% 满量程，无 TX | 不适用  | 1.732μV <sub>RMS</sub> |

| SNR 计算值     |      | 121.7dB                |

## 4 设计文件

### 4.1 原理图

要下载原理图，请参阅 [TIDA-060031](#) 中的设计文件。

### 4.2 物料清单

要下载物料清单 (BOM)，请参阅 [TIDA-060031](#) 中的设计文件。

### 4.3 PCB 布局建议

#### 4.3.1 布局图

要下载板层图，请参阅 [TIDA-060031](#) 中的设计文件。

### 4.4 Altium 工程

要下载 Altium Designer® 工程文件，请参阅 [TIDA-060031](#) 中的设计文件。

### 4.5 Gerber 文件

要下载 Gerber 文件，请参阅 [TIDA-060031](#) 的设计文件。

### 4.6 装配图

要下载装配图，请参阅 [TIDA-060031](#) 中的设计文件。

## 5 相关文档

- 德州仪器 (TI) , [DACx1001 20 位、18 位和 16 位低噪声、超低谐波失真、快速趋稳、高电压输出数模转换器 \(DAC\) 数据表](#)

- 德州仪器 (TI) , [DAC11001B 20 位低噪声、超低谐波失真、快速趋稳、高电压输出数模转换器 \(DAC\) 数据表](#)

- 德州仪器 (TI) , [《了解音频电路中的运算放大器噪声 \(应用报告\)》](#)

- 德州仪器 (TI) , [《使用基准电压进行设计的提示和技巧 \(电子书\)》](#)

### 5.1 支持资源

[TI E2E™ 中文支持论坛](#)是工程师的重要参考资料，可直接从专家处获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题，获得所需的快速设计帮助。

链接的内容由各个贡献者“按原样”提供。这些内容并不构成 TI 技术规范，并且不一定反映 TI 的观点；请参阅 TI 的[使用条款](#)。

### 5.2 商标

TI E2E™, Burr-Brown™, SoundPlus™, PowerPAD™, TINA-TI™, and PurePath™, and are trademarks of Texas Instruments.

TOSLINK® is a registered trademark of Toshiba Electronics Devices and Storage Corporation.

Microsoft® and Windows® are registered trademarks of Microsoft Corporation.

Altium Designer® is a registered trademark of Altium LLC or its affiliated companies.

所有商标均为其各自所有者的财产。

## 6 作者简介

**PAUL FROST** (集团技术员工团队成员) 是精密数模转换器团队的应用和验证经理。他获得了亚利桑那大学的计算机工程学士学位。

**ERIN BOWRIE** 是精密数模转换器团队的应用工程师。他们获得了圣克拉拉大学的电气工程学士学位。

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#))、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025 , 德州仪器 (TI) 公司

最后更新日期 : 2025 年 10 月