## 摘要

本文档介绍了 TDP1204 EVM 的使用和配置方式，并提供了有关系统硬件实现的建议。这些建议仅用作指南，设计人员应负责考虑所有系统特性和要求。工程师应参考数据表了解器件运行、端子描述等技术细节。

---

## 内容

|                           |   |

|---------------------------|---|

| <b>1 概述</b>               | 2 |

| 1.1 什么是 TDP1204 EVM ?     | 2 |

| 1.2 TDP1204 EVM 中包含哪些元件 ? | 2 |

| 1.3 EVM 看起来是什么样子的 ?       | 2 |

| <b>2 硬件配置</b>             | 3 |

| 2.1 电源                    | 3 |

| 2.2 启用或复位                 | 3 |

| 2.3 配置跳线                  | 3 |

| 2.4 Rx EQ 配置              | 4 |

| 2.5 HPD 监控选项              | 5 |

| 2.6 本地 I2C 访问             | 5 |

| <b>3 快速入门指南</b>           | 5 |

| <b>4 原理图</b>              | 6 |

## 商标

所有商标均为其各自所有者的财产。

## 1 概述

### 1.1 什么是 TDP1204 EVM ?

TDP1204 EVM 是为帮助客户评估带有 HDMI 接口的 TDP1204 视频应用而开发的 PCB。该 EVM 还可用作硬件参考设计来实现 TDP1204。客户申请获取有关 TDP1204 元件布线或布置规则的 PCB 设计说明后，我们立即提供 PCB 设计或布局文件。

### 1.2 TDP1204 EVM 中包含哪些元件 ?

该 EVM 的主要元件如下 :

- TDP1204 更强

- 标准 HDMI 源连接器 ( 插座 )

- 标准 HDMI 接收器连接器 ( 插座 )

- 直流电源稳压器

- 用于连接外部 I2C 主机的 I2C 编程接口

- USB 接口

- 用于配置各种 TDP1204 特性的接头

### 1.3 EVM 看起来是什么样子的 ?

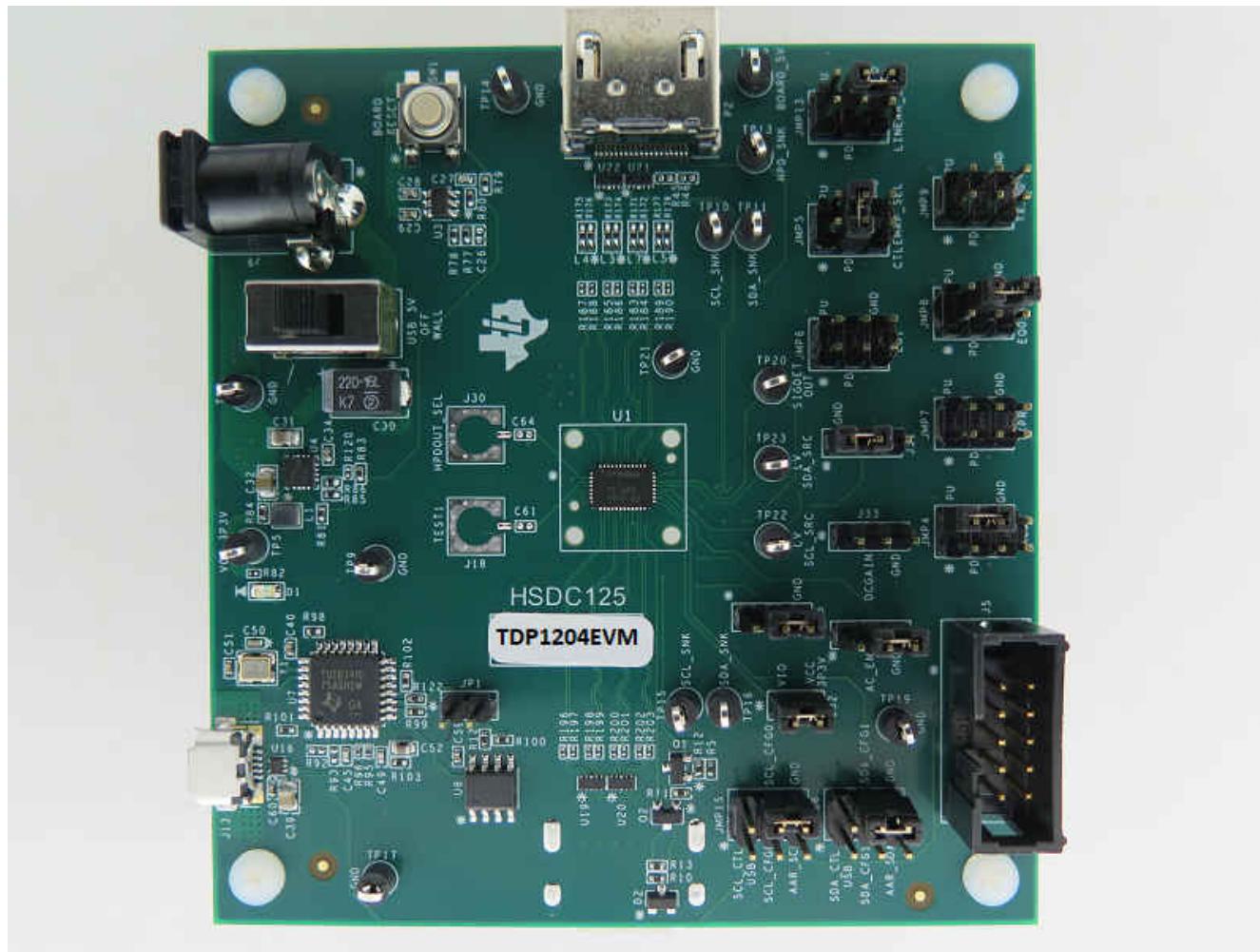

图 1-1. EVM 电路板

## 2 硬件配置

### 2.1 电源

EVM 上提供了一个直流桶形插孔 (J9) , 可连接 5V 壁式电源适配器。直流桶形插孔 (CUI Inc. PJ-202AH) 的内径为 2.1mm , 外径为 5.5mm。+5V 电源的尖端必须为正极。满足上述要求且电流至少为 1.5A 的 +5V 电源可用于为 TDP1204 EVM 供电。当 SW2 设置到位置 1 时 , 为 EVM 供电。

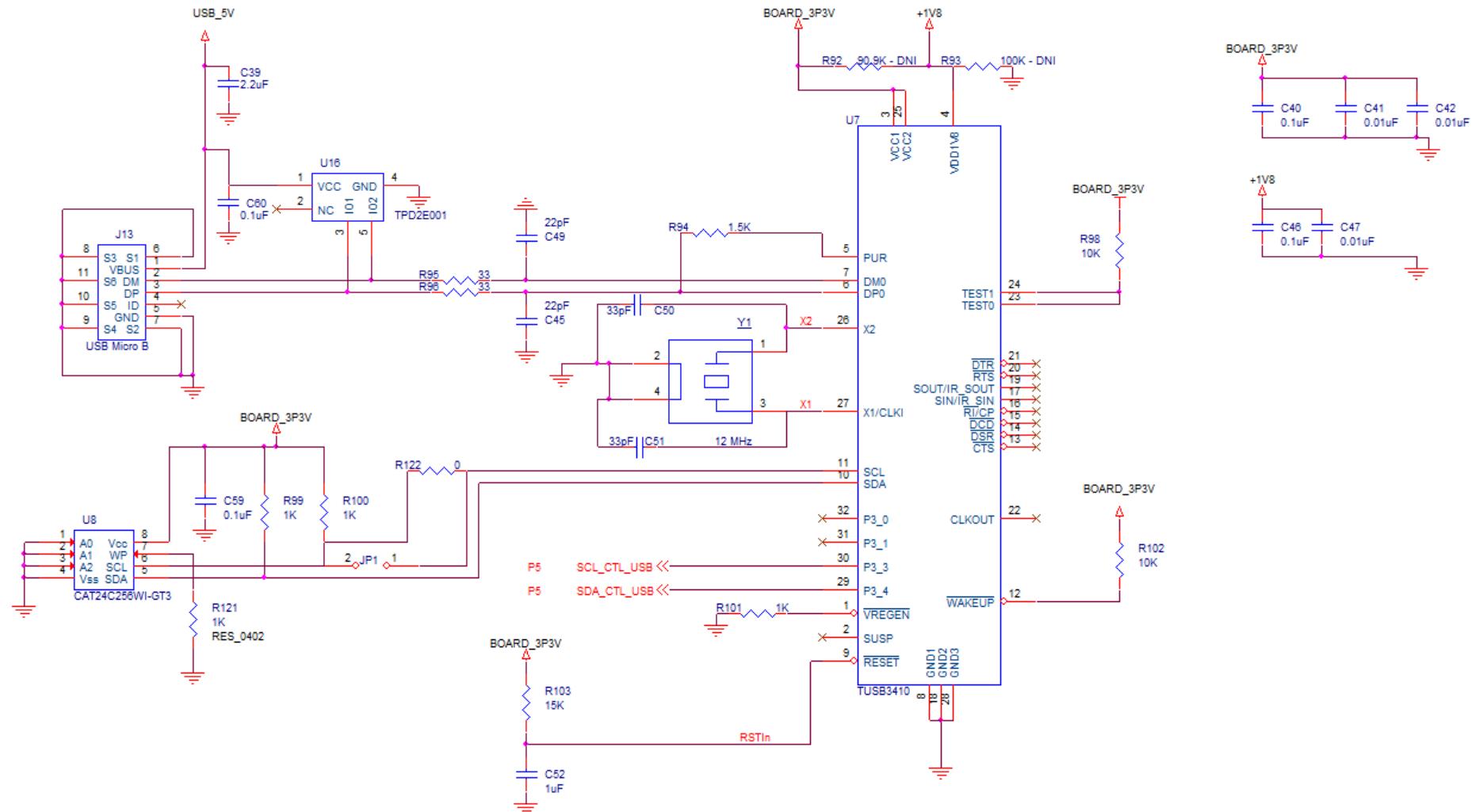

或者 , 也可以使用 USB Micro 电缆将主机连接到 J13 USB Micro B 连接器 , 并将 SW2 设置到位置 3。

---

#### 备注

将 VBUS 电压和桶形插孔的电压限制为不超过 6V。

---

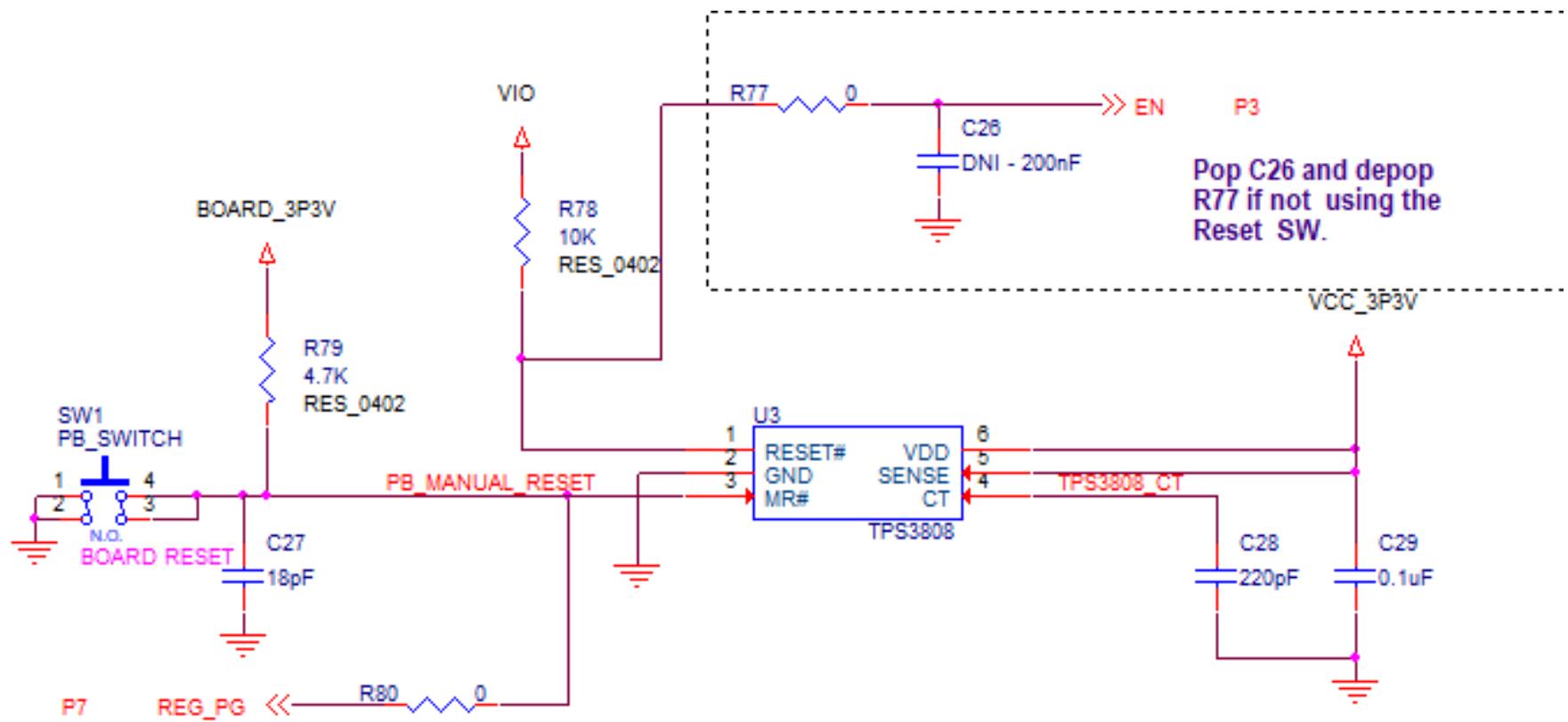

### 2.2 启用或复位

有三个器件启用或复位选项与 EVM 配合使用。

1. 监控器电路选项。这是 EVM 上的默认配置。使能 (EN) 信号保持低电平 , 直到 3.3V 稳压器的电源正常 (REG\_PG) 信号达到稳定的高电压电平 , 然后释放高电平。

2. RC 时序选项。C26 外部电容器和内部电阻器用于控制器件上电后的 EN 引脚斜坡时间。默认情况下 , C26 是 DNI ( 不安装选项 )。需要安装 C26 并且需要卸载 R77 , 才能启用该选项。

3. 外部控制选项。提供了一个按钮 (SW1) 来手动控制 EN 引脚。

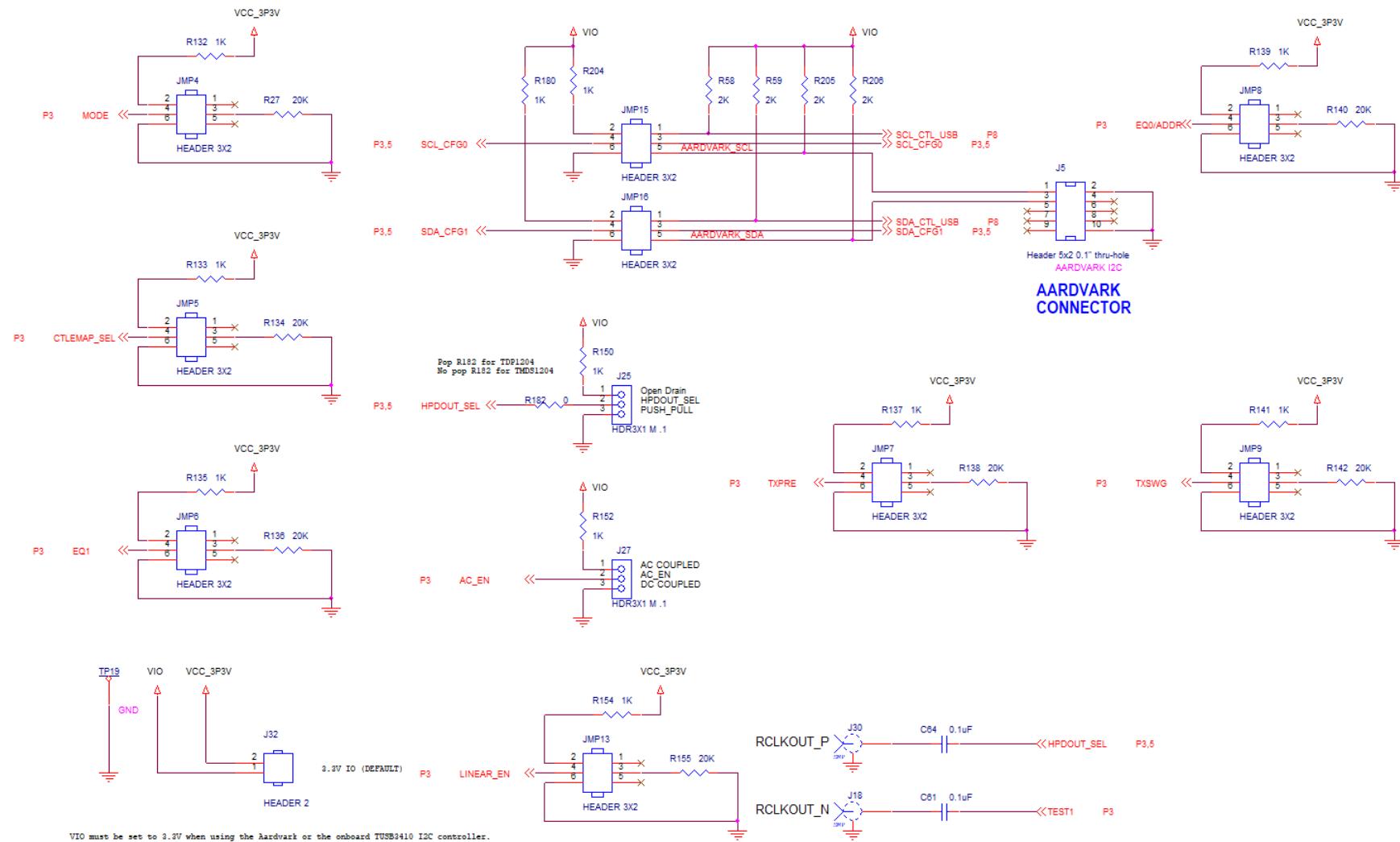

### 2.3 配置跳线

EVM 上提供了多个跳线 , 用于配置 TDP1204 和探测点。

以下是用于配置 TDP1204 的 4 电平跳线列表 : JMP4、JMP5、JMP6、JMP7、JMP8、JMP9 和 JMP13。表 2-1 中详细说明了在不同电平之间选择的跳线位置。

---

#### 备注

在 EN 引脚的上升沿之后对 4 电平引脚进行采样。因此 , 在 EN 引脚从低电平切换到高电平之前 , 不会改变任何 4 电平引脚的状态。

---

表 2-1. 4 电平配置跳线设置

| 跳线位置      | 4 电平状态 |

|-----------|--------|

| 将 4 短接至 6 | 0      |

| 将 3 短接至 4 | R      |

| 开路        | F      |

| 将 2 短接至 4 | 1      |

表 2-2. 跳线

| 跳线    | 默认位置      | 说明                                                                                                              |

|-------|-----------|-----------------------------------------------------------------------------------------------------------------|

| JMP4  | 将 4 短接至 6 | <b>MODE。</b><br>默认为引脚配置 (Strap) 模式。如果需要 I2C 模式 , 请将该跳线保持开路或无连接。更多详细信息 , 请参阅数据表。                                 |

| JMP5  | 将 2 短接至 4 | <b>CTLEMAP_SEL。</b> 有关不同 CTLEMAP 选项的详细信息 , 请参阅数据表。                                                              |

| JMP6  | 开路        | <b>EQ1。</b> 在引脚配置 (Strap) 模式下 , 该跳线连同 JMP8 (EQ0) 将为接收器选择 EQ 值。可能需要根据所用 HDMI 电缆的质量来调整 EQ。有关 EQ 选项的详细信息 , 请参阅数据表。 |

| JMP7  | 开路        | <b>TXPRE。</b> 有关详细信息 , 请参阅数据表。                                                                                  |

| JMP8  | 将 4 短接至 6 | <b>EQ0/ADDR。</b> 在引脚配置 (Strap) 模式下 , 该跳线连同 JMP6 (EQ1) 将为接收器选择 EQ 值。可能需要根据所用 HDMI 电缆的质量来调整 EQ。有关详细信息 , 请参阅数据表。   |

| JMP9  | 开路        | <b>TXSWG。</b> 有关详细信息 , 请参阅数据表。                                                                                  |

| JMP13 | 将 4 短接至 6 | <b>LINEAR_EN。</b> 有关详细信息 , 请参阅数据表。                                                                              |

表 2-2. 跳线 (continued)

| 跳线    | 默认位置      | 说明                                                                                                                                                                                                                                   |

|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JMP15 | 将 4 短接至 6 | <b>SCL 和 CFG0。</b><br>将 1 短接至 3：来自 TUSB3410 (U7) 的 I2C 时钟。<br>将 3 短接至 5：来自 Aardvark 连接器 (J5) 的 I2C 时钟。<br>将 2 短接至 4：CFG0 上拉至 VIO (3.3V)。有关 CFG0 的详细信息，请参阅数据表。<br>将 4 短接至 6：CFG0 下拉至 GND。有关 CFG0 的详细信息，请参阅数据表。                        |

| JMP16 | 将 4 短接至 6 | <b>SDA 和 CFG1。</b><br>将 1 短接至 3：来自 TUSB3410 (U7) 的 I2C 数据。<br>将 3 短接至 5：来自 Aardvark 连接器 (J5) 的 I2C 数据。<br>将 2 短接至 4：CFG1 上拉至 VIO (3.3V)。有关 CFG1 的详细信息，请参阅数据表。<br>将 4 短接至 6：CFG1 下拉至 GND。有关 CFG1 的详细信息，请参阅数据表。                        |

| J25   | 将 2 短接至 3 | <b>HPDOUT_SEL。</b><br>将 1 短接至 2：HPD_OUT 为漏极开路。<br>将 2 短接至 3：HPD_OUT 是推挽式。                                                                                                                                                            |

| J27   | 将 2 短接至 3 | <b>AC_EN</b><br>将 1 短接至 2：OUT_D[2:0] 和 OUT_CLK 为交流耦合。确保 R171、R172、R173、R174、R175、R176、R177 和 R178 装有 100nF 电容器，或确保交流电容器位于 EVM 电路板外部。<br>将 2 短接至 3：OUT_D[2:0] 和 OUT_CLK 为直流耦合。确保 R171、R172、R173、R174、R175、R176、R177 和 R178 装有 0Ω 电阻器。 |

| J31   | 将 2 短接至 3 | <b>DDC 电平转换器启用/禁用</b><br>将 1 短接至 2：禁用分立式 DDC 电平转换器 (U23)。<br>将 2 短接至 3：启用分立式 DDC 电平转换器 (U23)。                                                                                                                                        |

| J32   | 将 1 短接至 2 | <b>VIO 电压。</b><br>将 1 短接至 2：VIO 连接到电路板 3.3V。<br>开路：VIO 由外部电源供电。                                                                                                                                                                      |

## 2.4 Rx EQ 配置

共有 16 种 EQ 设置，0 为最低，Fh 为最高。具体 EQ 值请参阅数据表。

表 2-3. Rx 均衡控制

| 寄存器：CLK_EQ、D0_EQ、<br>D1_EQ、D2_EQ<br>均衡设置编号 | EQ1 引脚电平 | EQ0 引脚电平 | EQ 增益     |

|--------------------------------------------|----------|----------|-----------|

| 0                                          | 0        | 0        | 最低 EQ 设置。 |

| 1                                          | 0        | R        |           |

| 2                                          | 0        | F        |           |

| 3                                          | 0        | 1        |           |

| 4                                          | R        | 0        |           |

| 5                                          | R        | R        |           |

| 6                                          | R        | F        |           |

| 7                                          | R        | 1        |           |

| 8                                          | F        | 0        |           |

| 9                                          | F        | R        |           |

| 10                                         | F        | F        |           |

| 11                                         | F        | 1        |           |

| 12                                         | 1        | 0        |           |

| 13                                         | 1        | R        |           |

| 14                                         | 1        | F        |           |

| 15                                         | 1        | 1        | 最高 EQ 设置  |

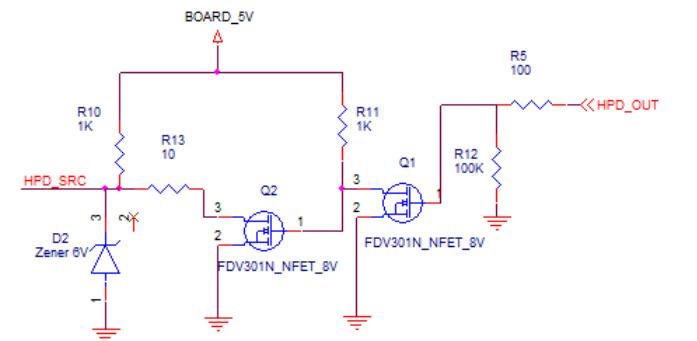

## 2.5 HPD 监控选项

为了适应在 HPD 变为低电平后无法正确重新发送 DDC 命令的系统，我们在 TDP1204 EVM 上实现了 HPD 监控模式。该模式允许在 TDP1204 周围路由 HPD 线路，但保持与接收端上 TDP1204 的连接，以允许 TDP1204 监控其状态。

- 组装 R131，不组装 R129，使 HPD 开启。

- 不组装 R131，组装 R129，仅实现 HPD 监控

## 2.6 本地 I2C 访问

通过 J5 连接器可以访问 TDP1204 的本地 I2C 信号。TDP1204 支持 1.2V、1.8V 和 3.3V LVCMOS 电平。

TDP1204 VIO 引脚用于选择以下 2 电平控制引脚使用的电压电平：LV\_DDC\_SDA、LV\_DDC\_SCL、SCL/CFG0 和 SDA/CFG1。通过连接器访问 I2C 接口时，I2C 信号电平必须符合 TDP1204 LVCMOS 电平。

可通过 J5 连接独立式外部 I2C 主机，以进行调试和控制。外部 I2C 主机控制器的一个示例是 Total Phase Aardvark I2C/SPI 主机适配器 ( Total Phase 器件型号 : TP240141 )。该 I2C 主机控制器的示例脚本应要求提供。

可通过 EVM 跳线 JMP8 修改 TDP1204 的目标 I2C 地址。请参阅 TDP1204 ADR/EQ 引脚设置及其相应的 I2C 地址。有关 7 位 I2C 目标地址选项，请参阅 TDP1204 数据表。

**表 2-4. Aardvark I2C (J5) 引脚排列**

| J5 引脚编号 | 说明      | J5 引脚编号 | 说明  |

|---------|---------|---------|-----|

| 1       | SCL_CTL | 2       | GND |

| 3       | SDA_CTL | 4       | NC  |

| 5       | NC      | 6       | NC  |

| 7       | NC      | 8       | NC  |

| 9       | NC      | 10      | GND |

## 3 快速入门指南

以下说明假设 EVM 配置为引脚配置 (Strap) 模式并由桶形插孔供电。

1. 将 +5V 直流电源插入桶形插孔。闭合 SW2。

2. 如果使用外部 I2C 配置而不是引脚配置 (Strap)，请在此步骤配置 TDP1204。

3. 使用标准 HDMI 电缆将 HDMI 源插入 P1 ( HDMI 插座 )。

4. 使用标准 HDMI 电缆将 HDMI 视频接收器插入 P2 ( HDMI 插座 )。

5. 应能观察到 HDMI 接收器上的视频输出。

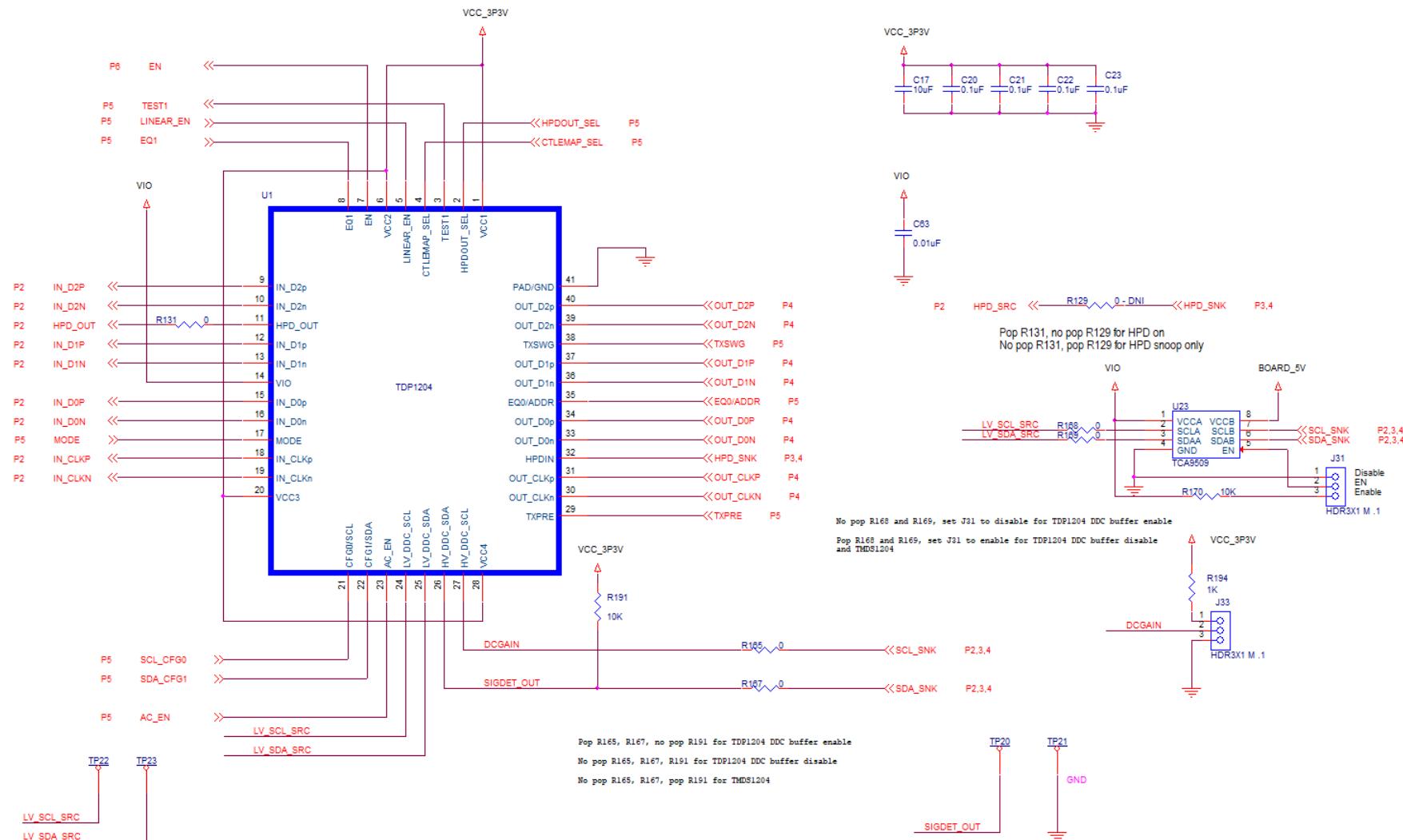

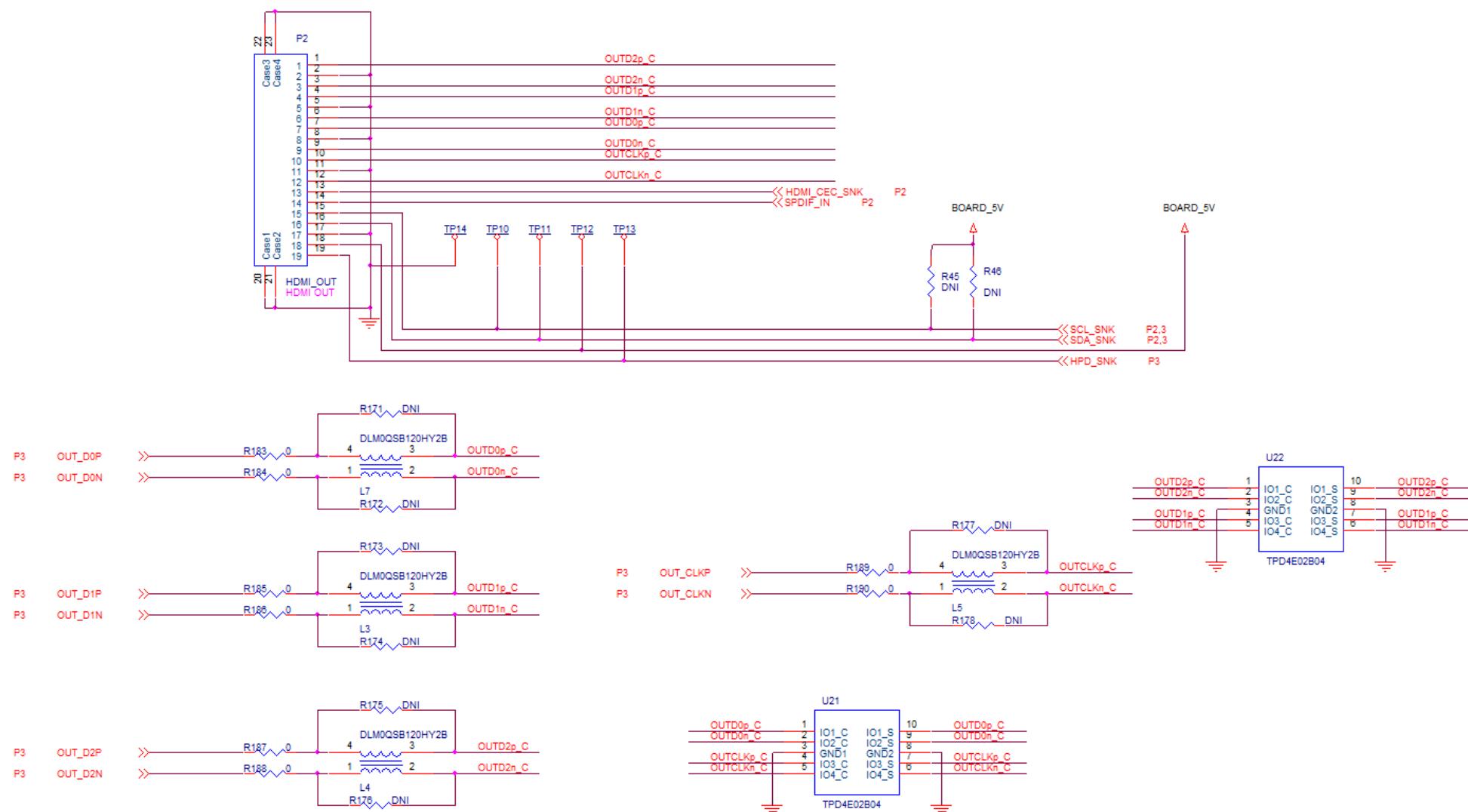

## 4 原理图

### NOTES:

- 100-ohm differential impedance for HDMI differential pairs.

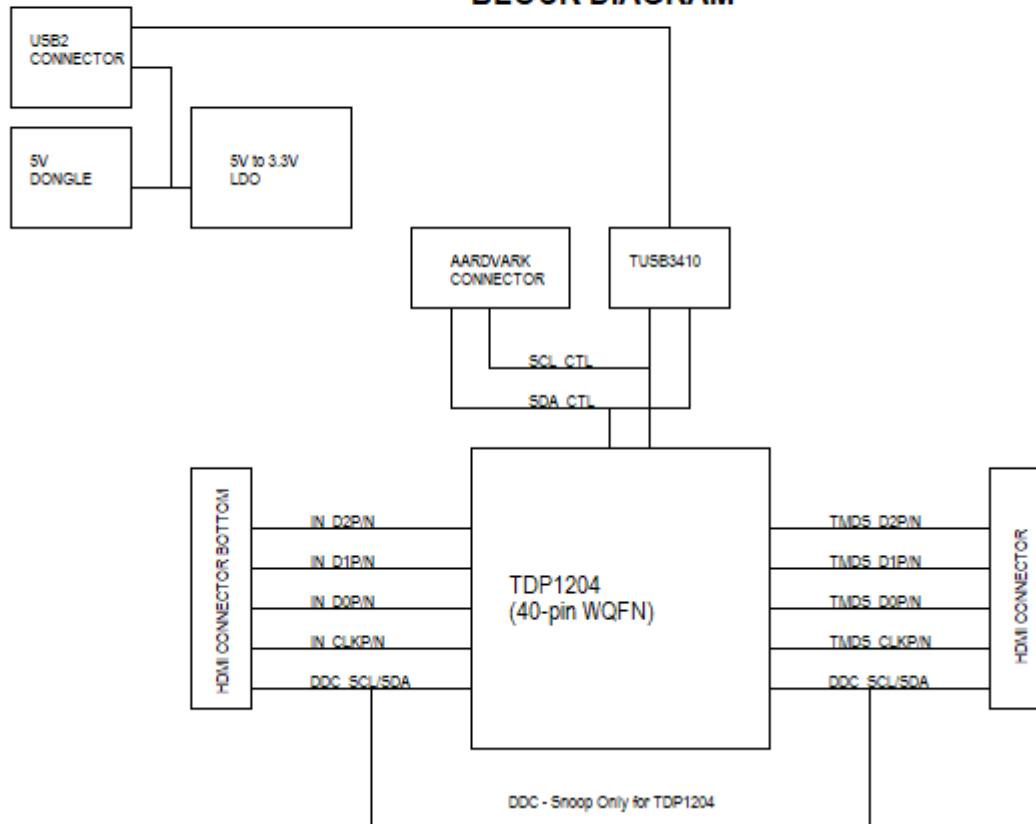

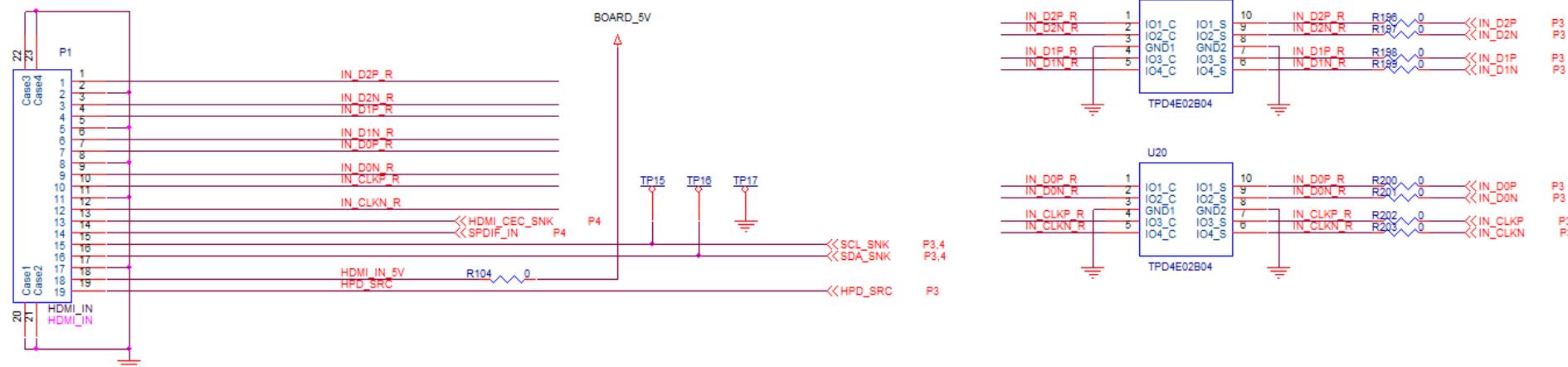

BLOCK DIAGRAM

HDMI RX

HDMI TX

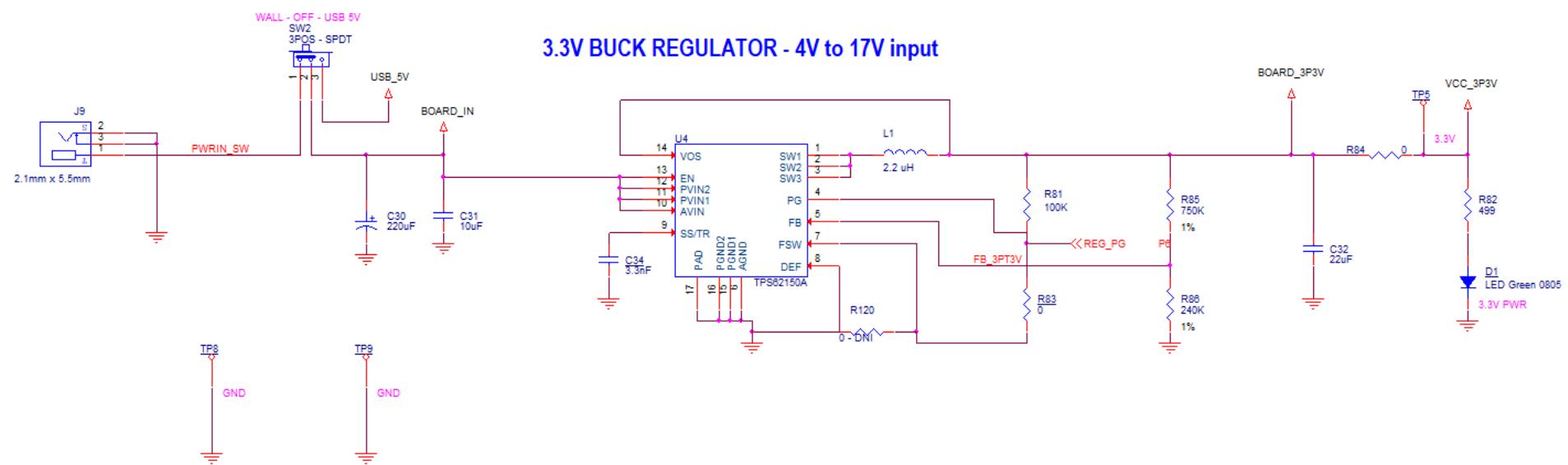

### 3.3V BUCK REGULATOR - 4V to 17V input

## 重要声明和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，TI 对此概不负责。

TI 提供的产品受 [TI 的销售条款](#) 或 [ti.com](#) 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址：Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2023, 德州仪器 (TI) 公司