# 设计指南: TIDA-010083

# 适用于机器视觉摄像机和视觉传感器的高密度隔离式 PoE 和 GigE 参考设计

# TEXAS INSTRUMENTS

#### 说明

以太网供电 (PoE) 提供了简单、可靠的解决方案,可通过单根线缆实现高数据速率、长距离的电力和数据传输。这种同时传输数据和供电的功能使 PoE 适用于机器视觉摄像机和视觉传感器等小型器件。

此参考设计使用完整的 PoE 供电设备 (PD),包括 1Gb/s 物理层 (PHY) 和外形尺寸极小的 27 x 27mm 高效隔离式电源解决方案。

#### 资源

| TIDA-010083 | 设计文件夹 |

|-------------|-------|

| TPS23758    | 产品文件夹 |

| DP83867IR   | 产品文件夹 |

| LM74700-Q1  | 产品文件夹 |

| TVS3300     | 产品文件夹 |

| ISO1212     | 产品文件夹 |

| TPS62801    | 产品文件夹 |

| TPS62802    | 产品文件夹 |

| TPD4E05U06  | 产品文件夹 |

| CSD17579Q3A | 产品文件夹 |

| CSD19538Q2  | 产品文件夹 |

|             |       |

Search Our E2E™ support forums

#### 特性

- IEEE802.3at PoE 1 类 PD 0 级设备: 13W

- 具有同步整流功能的反激式器件

- 无光耦合器的初级侧反馈

- 5V 输出,精度优于 ±2%

- 效率高达 92%

- 额外的 24V 辅助输入

- 10/100/1000Mbit/s 以太网

- RGMII 接口

- 2x 隔离式数字输入

- 1x 隔离式数字输出

- 27 x 27mm 的小外形尺寸

#### 应用

- 视觉传感器

- 摄像机

- 条形码读取器

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

System Description www.ti.com.cn

#### 1 System Description

Machine vision is becoming more popular in factory automation, where cameras can not only read codes but also identify objects, conduct quality tests, and control processes. Because of these quality tests and control of processes, there is demand to have a 100% quality check for the production line.

A vision camera simply delivers a raw image of an object. Most modern vision cameras come in a very small footprint – 29 x 29 x 29 mm³ – with all electronics, including the interfaces, located in this small housing. Complementary metal oxide semiconductor (CMOS) sensors used in such cameras are sensitive to heat. Their image quality degrades with higher temperatures, therefore it is important to keep the power dissipation low. The small housing leaves no room for a fan or heat sink and doesn't allow the dissipation of a lot of heat. It is still necessary to include a CMOS sensor and a field-programmable gate array (FPGA) or processor, as well as a high-speed interface and the necessary power supply. The electronic system must be able to capture, process, and transmit uncompressed video frames at high frame rates and resolutions. Gigabit Ethernet is widely used for these type of cameras as it is a reliable and very well supported interface.

An increasing amount of these devices make use of PoE. This offers the possibility to add power to the high speed Ethernet connection. This has the advantage to use one cable for power as well as for data connection with up to 100-m cable length at a data rate of up to 1000 Mbit/s. Such a camera requires the installation of only one standard Ethernet cable and can connect the camera without an additional cable for powering the camera. This combination of a widely used data interface together with power makes it very simple and reliable to setup a machine vision camera in the factory floor.

This reference design features a power solution which uses the available 13 W of input power to generate an isolated 5-V rail in a highly efficient way. The reference design also includes the Ethernet data transformer and PHY. Moreover, digital inputs and outputs are part of this design. The design has a small footprint of 27 x 27 mm<sup>2</sup>.

This design consists of three major independent parts:

- The first part is the IEEE802.3at compliant Type 1 Class 0 PD with up to 13 W and a 5-V output

voltage. The TPS23758 used here combines the PD controller as well as the flyback converter with an

integrated switching MOSFET. The flyback converter uses primary side feedback, so an optocoupler or

secondary shunt reference is not needed. To maintain a stable voltage over a wide load range and

high efficiency, synchronous rectification is used.

- The second part is the Ethernet subsystem, including a data transformer and 10/100/1000 Mbit/s

Ethernet PHY DP83867IR. In addition to the PHY, the necessary power and clock supply are also

included on the board. Three status LEDs on the board show the link state of the PHY.

- As most systems also need some digital inputs and outputs, this design contains two isolated digital inputs and one digital output.

www.ti.com.cn System Description

#### 1.1 Key System Specifications

# **WARNING**

Depending on the load and input voltages connected to this design, some components can reach high temperatures. See 节 3.4.1 for thermal images showing the hot spots. Overloading the circuit can result in overheating components and damaged parts.

#### 表 1. Key System Specifications

| PARAMETER                | SPECIFICATIONS     | DETAILS   |

|--------------------------|--------------------|-----------|

| PoE input voltage        | 36 - 57 V          | 节 2.4.1.2 |

| Auxiliary input voltage  | 18 - 36 V          | 节 2.4.1.4 |

| Isolated output voltage  | 5 V                | 节 2.4.1.2 |

| Output current           | Up to 2.3 A        | 节 2.4.1.2 |

| Output voltage tolerance | < ±2 %             | 节 3.2.1   |

| Efficiency               | Up to 92%          |           |

| Maximum PoE power        | 13 W               | 节 2.4.1.1 |

| PoE class                | Type 1 Class 0     | 节 2.4.1.1 |

| Isolation                | Functional         |           |

| Data rate                | 10/100/1000 Mbit/s | 节 2.4.2   |

| Digital inputs           | 2x Isolated        | 节 2.4.3   |

| Digital outputs          | 1x Isolated        | 节 2.4.3   |

#### 2 System Overview

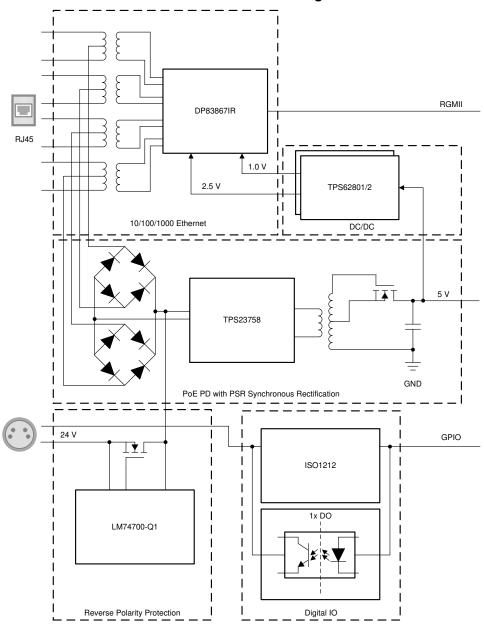

# 2.1 Block Diagram

图 1. TIDA-010083 Block Diagram

#### 2.2 Design Considerations

The target of this design is a complete PoE PD with isolation as well as an Ethernet PHY for space-critical applications such as machine vision cameras, but also applications with the demand for higher peak power are covered.

This reference design is designed for a very small form factor of 27 x 27 mm<sup>2</sup>. Because the area taken by the connectors and the data transformer is already in that range, it is split into two boards of that size. The two boards are connected together by a flex PCB in the middle and can be folded to fit into that small area. However, this reference design is not manufactured in that way as it would complicate testing and development. Instead, it is manufactured as a standard rigid PCB, so it can easily be tested.

One board contains the connectors to the outer world of the system, the RJ45 connector for Ethernet and an 8-pin connector for auxiliary power as well as digital inputs and outputs. Also on this board are the data transformer and a couple of status LEDs signaling the state of the Ethernet PHY.

The second board contains the rest of the subsystem, as well as a connector interfacing a processor or FPGA board. On this board, the complete PoE PD, including the diode bridges, filtering, PD controller, auxiliary input, and flyback, are located. Also, the Ethernet PHY with the necessary components such as DC/DC regulators and clock generation are on this board.

This reference design can be operated as a stand-alone design or together with a processor or FPGA board. For testing the data path in a stand-alone operation, the PHY can be placed in a loop-back mode to send back every received frame.

#### 2.3 Highlighted Products

This section contains the most important parts used in the reference design, mentioning the most important technical data that make it suitable for this subsystem.

#### 2.3.1 TPS23758

The TPS23758 device combines a Power over Ethernet (PoE) powered device (PD) interface, a 150-V switching power FET, and a current-mode DC-DC controller optimized for flyback topology. The high level of integration along with primary side regulation (PSR), spread spectrum frequency dithering (SSFD), and advanced startup makes the TPS23758 an ideal solution for size-constrained applications. The PoE implementation supports the IEEE 802.3at standard as a 13-W, Type 1 PD.

# 图 2. TPS23758 Block Diagram - vcc VDD COMP Regulator 50k0 S Vrefc (1.75V) 50kΩ ≷ RTN Control SST disch Regulator Current Ramp 40 μA (pk) cs DRAIN 0.55 V CLK DTHR

Key features that make it suitable for this application:

- Complete IEEE 802.3at PD solution for type 1 PoE

- Robust 100-V, 0.36-Ω (typical) hotswap MOSFET

- Integrated PWM controller with 0.77-Ω (typical) 150-V power MOSFET

- · Flyback controller with PSR

- Supports CCM operation with secondary side synchronous FET— multi-outputs

- ±1% (typical, 5-V output) load regulation (0-100% load range) with Sync FET

- · Primary adapter priority input

#### 2.3.2 **DP83867IR**

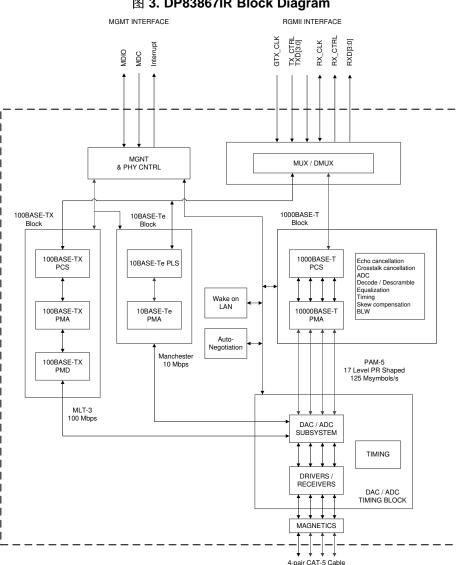

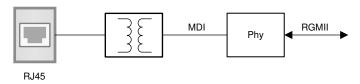

The DP83867 device is a robust, low power, fully featured physical layer transceiver with integrated PMD sublayers to support 10BASE-Te, 100BASE-TX, and 1000BASE-T Ethernet protocols. Optimized for ESD protection, the DP83867 exceeds 8-kV IEC 61000-4-2 (direct contact).

The DP83867 is designed for easy implementation of 10/100/1000 Mbps Ethernet LANs. It interfaces directly to twisted pair media through an external transformer. This device interfaces directly to the MAC layer through the IEEE 802.3 Standard Media Independent Interface (MII), the IEEE 802.3 Gigabit Media Independent Interface (GMII) or Reduced GMII (RGMII). The QFP package supports MII/GMII/RGMII whereas the QFN package supports RGMII.

The DP83867 provides precision clock synchronization, including a synchronous Ethernet clock output. It has low latency and provides IEEE 1588 Start of Frame Detection.

图 3. DP83867IR Block Diagram

Key features that make it suitable for this application:

- Low power consumption of 457 mW

- Ultra low RGMII latency TX < 90 ns, RX < 290 ns

- Exceeds 8000-V IEC 61000-4-2 ESD protection

- Integrated MDI termination resistors

- Programmable MII/GMII/RGMII termination impedance

- IEEE 1588 time stamp support

- Fully compatible to IEEE 802.3 10BASE-Te, 100BASE-TX, and 1000BASE-T specification

- Configurable I/O voltage (3.3 V, 2.5 V, 1.8 V)

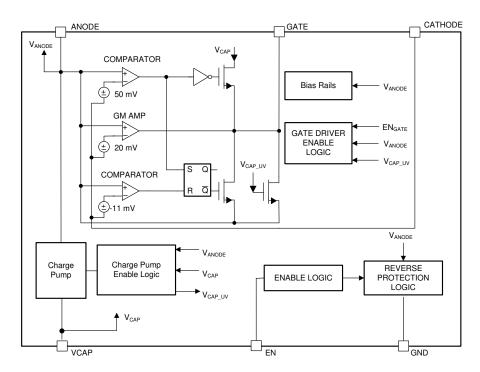

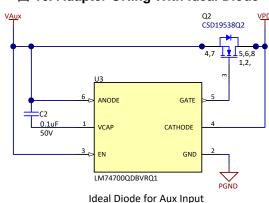

#### 2.3.3 LM74700-Q1

The LM74700-Q1 ideal diode controller operates in conjunction with an external N-channel MOSFET as an ideal diode rectifier for low-loss, reverse-polarity protection. The wide supply input range of 3 to 65 V allows control of many popular DC bus voltages. The device can withstand and protect the loads from negative supply voltages down to -65 V. With a low  $R_{DS(on)}$  external N-channel MOSFET, a very low forward voltage drop can be achieved while minimizing the amount of power dissipated in the MOSFET. For low-load currents, the forward voltage is regulated to 20 mV to enable graceful shutdown of the MOSFET. External MOSFETs with 5 V or lower threshold voltage are recommended. With the enable pin low, the controller is off and draws approximately 3  $\mu$ A of current.

The LM74700-Q1 controller provides a charge pump gate drive for an external N-channel MOSFET. The high voltage rating of LM74700-Q1 helps to simplify the system designs for automotive ISO7637 protection. Fast response to reverse current blocking makes the device suitable for systems with output voltage holdup requirements during ISO7637 pulse testing, as well as power fail and brownout conditions. The LM74700-Q1 is also suitable for ORing applications or AC rectification.

#### 图 4. LM74700-Q1 Block Diagram

Copyright © 2017, Texas Instruments Incorporated

Key features that make it suitable for this application:

- 3.2-V to 65-V input range (3.9-V start up)

- –65-V reverse voltage rating

- Charge pump for external N-Channel MOSFET

- 20-mV ANODE to CATHODE forward voltage drop regulation

- 80-µA operating quiescent current (EN = High)

- Fast response to reverse current blocking: < 0.75 μs</li>

#### 2.3.4 TVS3300

The TVS3300 device robustly shunts up to 35 A of IEC 61000-4-5 fault current to protect systems from high-power transients or lightning strikes. The device offers a solution to the common industrial signal line EMC requirement to survive up to 1-kV IEC 61000-4-5 open circuit voltage coupled through a 42- $\Omega$  impedance. The TVS3300 device uses a unique feedback mechanism to ensure precise flat clamping during a fault, assuring system exposure below 40 V. The tight voltage regulation allows designers to confidently select system components with a lower voltage tolerance, lowering system costs and complexity without sacrificing robustness.

In addition, the TVS3300 is available in small 1 mm × 1.1 mm WCSP and 2 mm × 2 mm SON footprints which are ideal for space-constrained applications, offering up to a 90 percent reduction in size compared to industry standard SMA and SMB packages. The extremely low device leakage and capacitance ensure a minimal effect on the protected line. To ensure robust protection over the lifetime of the product, TI tests the TVS3300 against 4000 repetitive surge strikes at high temperature with no shift in device performance.

图 5. TVS3300 Block Diagram

Key features that make it suitable for this application:

- Protection against 1-kV, 42-Ω IEC 61000-4-5 surge test for industrial signal lines

- Maximum clamping voltage of 40 V at 35 A of 8/20-µs surge current

- Standoff voltage: 33 V

- Low leakage current: 19 nA typical at 27°C

- Low capacitance: 130 pF

- Integrated level 4 IEC 61000-4-2 ESD protection

#### 2.3.5 ISO1212

The ISO1211 and ISO1212 devices are isolated 24-V to 60-V digital input receivers, compliant to IEC 61131-2 Type 1, 2, and 3 characteristics. These devices enable 9-V to 300-V DC and AC digital input modules in programmable logic controllers (PLCs), motor-control, grid infrastructure, and other industrial applications. Unlike traditional optocoupler solutions with discrete, imprecise current limiting circuitry, the ISO121x devices provide a simple, low-power solution with an accurate current limit to enable the design of compact and high-density I/O modules. These devices do not require field-side power supply and are configurable as sourcing or sinking inputs.

The ISO121x devices operate over the supply range of 2.25 V to 5.5 V, supporting 2.5-V, 3.3-V, and 5-V controllers. A ±60-V input tolerance with reverse polarity protection helps ensure the input pins are protected in case of faults with negligible reverse current. These devices support up to 4-Mbps data rates passing a minimum pulse width of 150 ns for high-speed operation. The ISO1211 device is ideal for designs that require channel-to-channel isolation and the ISO1212 device is ideal for multichannel space-constrained designs.

# R<sub>THR</sub> SENSE IN CURRENT LIMIT OUT

REF

1

#### 图 6. ISO1212 Block Diagram

Key features that make it suitable for this application:

- Compliant to IEC 61131-2; type 1, 2, 3 characteristics for 24-V isolated digital inputs

- Supports 9-V to 300-V DC and AC digital input designs using external resistors

- Accurate current limit for low-power dissipation:

- 2.2 mA to 2.47 mA for type 3

- Adjustable up to 6.5 mA

- High input-voltage range with reverse polarity protection: ±60 V

- High data rates: up to 4 Mbps

- Wide supply range (VCC1): 2.25 V to 5.5 V

- UL 1577 recognition, 2500-VRMS insulation

#### 2.3.6 TPS62801/2

The TPS6280x device family is a step down converter with 2.3-µA typical quiescent current featuring highest efficiency and smallest solution size. Tl's DCS-Control™ topology enables the device to operate with tiny inductors and capacitors with a switching frequency up to 4MHz. At light load conditions, it seamlessly enters Power Save Mode to reduce switching cycles and maintain high efficiency.

Connecting the VSEL/MODE pin to GND selects a fixed output voltage. With only one external resistor connected to VSEL/MODE pin, 16 internally set output voltages can be selected. An integrated R2D (resistor to digital) converter reads out the external resistor and sets the output voltage. The same device part number can be used for different applications and voltage rails just by changing a single resistor. Furthermore, the internally set output voltage provides better accuracy compared to a traditional external resistor divider network. Once the device has started up, the DC/DC converter enters Forced PWM Mode by applying a high level at the VSEL/MODE pin. In this operating mode, the device runs at a typical 4-MHz or 1.5-MHz switching frequency, enabling lowest output voltage ripple and highest efficiency. The TPS6280x device series comes in a tiny 6-pin WCSP package with 0.35-mm pitch.

#### ΕN Smart Enable Ultra Low Power UVLO Pulldown Control 0.4V V<sub>REF</sub> 500kΩ Input Buffer vos Thermal Shutdown R2D converter VOS UVLO VSEL/ Internal ΕN MODE Discharge Resistor to feedback Digital divider Control Logic Converter network Power Stage Current Limit Comparator VIN Power Save / Forced PWM **PMOS** VIN Mode operation Ton High Side DCS Control VOS Timer ////Ramp VOS Direct Control **Gate Driver** SW Startup Delay NMOS Softstart Timing Limit Low Side Error Main amplifier Comparator GND Current **Limit Comparator**

#### 图 7. TPS62801/2 Block Diagram

Key features that make it suitable for this application:

- Input voltage range from 1.8 V to 5.5 V

- 2.3-µA operating quiescent current

- Up to 4-MHz switching frequency

- R2D converter for flexible V<sub>OUT</sub> setting

- Output discharge

- 100% duty cycle operation

#### 2.4 System Design Theory

This reference design consists of three major parts that will be discussed here: The Power over Ethernet (PoE) powered device (PD), the Ethernet physical layer (PHY), and the digital IO.

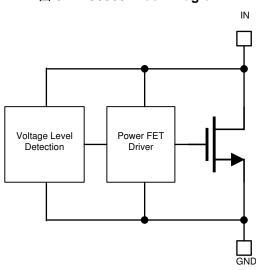

#### 2.4.1 Power Tree

图 8. Power Tree of the TIDA-010083

This reference design has two different power supply inputs. One power option is Power over Ethernet (PoE), and the other option is an auxiliary voltage input. These two power inputs are multiplexed to power a flyback converter. If both power sources are present, the auxiliary power is prioritized. The flyback is configured to a regulated output voltage of 5 V that can be used to power a system. Moreover, this 5-V rail is used to generate two additional voltages, necessary to supply the Ethernet physical layer (PHY).  $\boxed{\$}$  9 gives an overview of the power tree.

The details about this power solution will be discussed in the following sections.

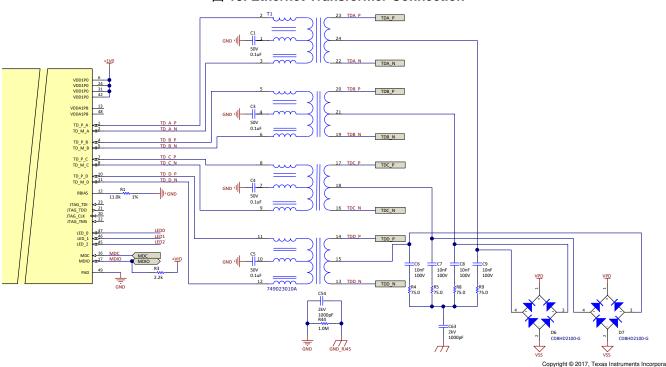

#### 2.4.1.1 Powered Device

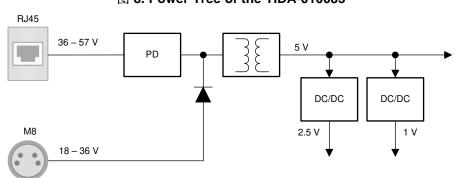

Adding PoE to a gigabit Ethernet system requires some modifications. The schematic on the left side of  $\boxtimes$  10 shows how the transformer is usually connected to the cable in a gigabit configuration. All of the middle taps of the transformers are connected to each other through a 75- $\Omega$  resistor and to ground (GND) by a capacitor. This circuit is typically called the Bob Smith termination. This circuit does not allow power to be added between the differential pair because it acts as a short.

To create the ability to inject power, adding one capacitor per middle tap interrupts the DC path. Because the DC path is no longer shorted, a DC voltage can be applied symmetrically between each differential pair. In total, it is possible to have up to four power lines. These lines go to the powered device (PD) controller over two rectifier bridges. By using a rectifier, the polarity, as well as the pairs used, does not matter.

图 9. Ethernet Transformer Connection

The device delivering power, the power sourcing equipment (PSE), must ensure that a PoE-capable PD is connected before powering it so as not to damage it. There are a few passive PoE implementations on the market that just connect a power supply to the middle tap of a transformer without any detection. This works when used with a proper PoE PD but could damage anything else.

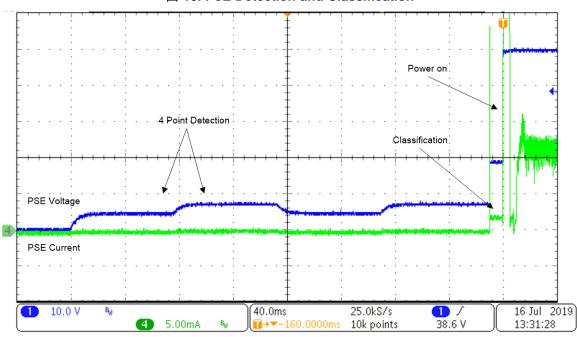

When connecting a PD to a PSE, the first step is detection by the PSE. During this step, a low voltage drop of 2.7 V and 10.1 V over the PD is used for sensing a signature resistor. 211 shows the complete procedure of an IEEE 802.3af-compliant class 0 PD. The detection of the signature resistance (in the range of 19 k $\Omega$  - 26.5 k $\Omega$ ) occurs over four steps to make it robust.

图 10. PoE Detection and Classification

After correct detection of the signature, the classification starts. The PSE increases the voltage to a level of 14.5 V to 20.5 V. The PD then must draw a constant current to signal its power needs. A current of 0 mA is a valid classification here – meaning Class 0 or a non-implemented classification – which translates to 15.4 W of power coming from the PSE.

The example in [8] 11 starts with a voltage between 5 V and 8 V. During this time, the signature is detected. After successful detection, the voltage increases to 19 V, and the PD draws a current of 2 mA. The PSE now knows that there is a class 0 device connected and will provide up to 15.4 W. The PSE turns on the full supply voltage, which can be between 37 V and 57 V.

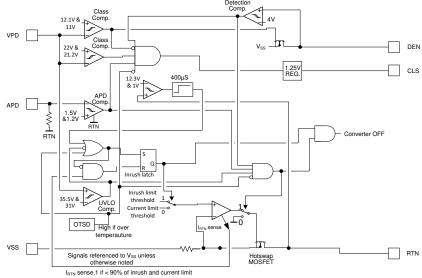

In 🛚 12, the implementation of this part in the TPS23758 is shown. The rectifier coming from the RJ45 connector and data transformer is connected between VPD and VSS. During detection and classification, the hot swap MOSFET is open and no current can flow into the remaining circuit, so the IC can switch on either the detection resistor or the classification current sink. When the voltage rises to operating voltage, the internal hot swap MOSFET gets turned on, and the circuit connected between VPD and RTN can operate.

#### Detection Comp. Class Comp. 12.1 V & VPD Class Comp. DEN 22 V & 21.2 V CLS 12.3 V 400 μS APD Comp 1.5 V &1.2 V RTN Converter OFF Inrush limit 35.5 V & 31 V threshold ÚVLO Current limit 0 threshold OTSD I<sub>RTN</sub> sense High if over temperauture VSS RTN Signals referenced to V<sub>SS</sub> unless Hotswap MOSFET otherwise noted

图 11. Block Diagram of the TPS23758 PD Part

I<sub>RTN</sub> sense,1 if < 90% of inrush and current limit

The schematic in  $\[mathbb{R}\]$  13 shows how the PD must be configured. The resistor R20 is necessary for the detection phase. Typically a 24.9-k $\Omega$  resistor is placed to VPD. However, depending on the rectification diode that is used, it can be necessary to change this, especially when using Schottky diodes for lower voltage drop and so higher efficiency this resistor might be increased. Schottky diodes have a higher leakage current that can cause problems. TI recommends observing the leakage current over temperature to ensure that the detection resistance is in a valid range over the whole desired temperature.

Resistor R29 defines the current in the classification phase. Depending on the power class that is desired, this resistor must be selected.  $\frac{1}{2}$  gives an overview of the different classes that this design and an IC can be used for as well as the recommended current ranges. By default, this reference design has assembled a 649- $\Omega$  resistor and is therefore being detected as a class 0 powered device with up to 15.4 W from the PSE, meaning that the PD can draw up to 13 W.

| CLASS | CLASSIFICATION CURRENT<br>ACCORDING TO 802.3af (mA) | $\begin{array}{c} \text{RECOMMENDED CLS} \\ \text{RESISTOR } (\Omega) \end{array}$ | TPS23758 CLASSIFICATION<br>CURRENT (mA) | MAXIMUM POWER FROM THE PSE |

|-------|-----------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------|----------------------------|

| 0     | 0 - 4                                               | 649                                                                                | 1.8 - 2.4                               | 15.4                       |

| 1     | 9 -12                                               | 121                                                                                | 9.9 - 11.3                              | 4                          |

| 2     | 17 - 20                                             | 68.1                                                                               | 17.6 - 19.4                             | 7                          |

| 3     | 26 - 30                                             | 45.3                                                                               | 26.5 - 29.3                             | 15.4                       |

表 2. Classification Current and Resistor Selection

#### 2.4.1.2 Flyback

The next relevant functional block is the flyback, generating a regulated isolated voltage from the PSE voltage. When operating from PoE power, the PD controller passes through a voltage roughly in the range between 36 V and up to 57 V. When operating from the auxiliary 24-V input, a voltage range of 18 V up to 36 V is specified. This leads to an overall voltage range of 18 V to 57 V for the flyback converter to operate. When designing the transformer and the power stage, the whole voltage range must be considered. However, the output power must be reduced when operating from the auxiliary input to limit the power dissipation to a reasonable level.

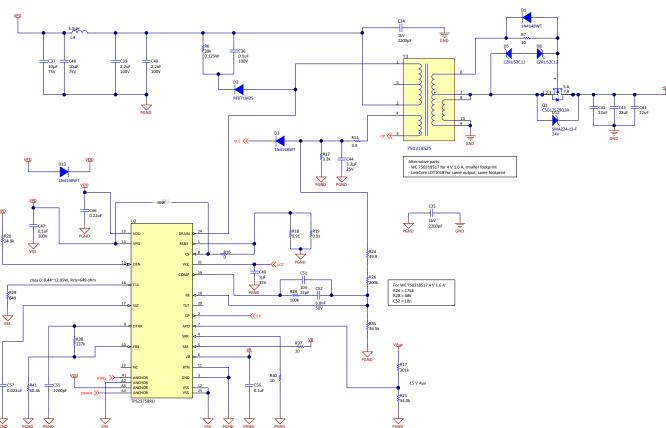

图 12. Schematic of the PD and Flyback

The transformer shown in the schematic has a turn ration of 6:1 primary to secondary and a primary inductance of 150  $\mu$ H. Together with the desired voltage range output voltage and current, the primary switch current can be calculated. The switch current is at the highest level at maximum load current and lowest input voltage, so this worst case is used for designing the power stage.

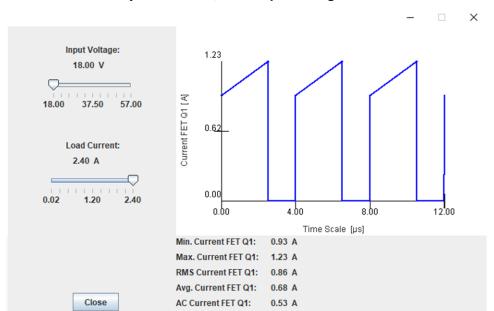

In  $\boxtimes$  14, this is done for a 5-V output at 2.4 A at a 18-V input voltage. It can be seen in  $\boxtimes$  13 that the peak current is at 1.23 A and the RMS current is at 0.86 A. Because the MOSFET of the flyback is integrated into the TPS23758 device, the designer has to take care not to overload it. The data sheet specifies a maximum peak current of 1.6 A, so this is acceptable. For estimating the static losses in the FET (1.28  $\Omega$  × 0.86² A² = 0.95 W) shows that already the power dissipation caused by the static losses is quite high for a small QFN IC with a thermal resistance of 34.7 K/W. It is not recommended to operate the device at these parameters, especially as the PCB size and therefore the area for heat dissipation is very limited.

图 13. Flyback for 5-V, 2.4-A Input Voltage Set to 18 V

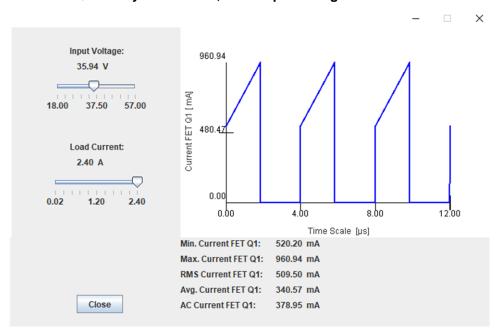

Checking the same conditions at a higher input voltage of 36 V, as shown in 🗵 15, shows much better results. The peak current is as expected well within the allowed range. The RMS current is with 0.5 A much lower, yielding to a power dissipation of 0.3 W. This can be handled much better.

图 14. Flyback for 5-V, 2.4-A Input Voltage Set to 36 V

The current limit of the IC is configured with the resistors R18 and R19. The current limit is set to a peak current of 1.3 A to have some headroom:  $0.6 \text{ V} / 1.3 \text{ A} = 0.46 \Omega$ . To handle the power dissipation, two resistors are connected in parallel.

The feedback path of this regulator is realized by measuring the voltage of the auxiliary winding. This makes it necessary to have a good coupling between the auxiliary winding and the output voltage to see a good representation of the output voltage. Also, the turns ratio between auxiliary and output must be designed accordingly. The voltage divider R26 and R35 defines the voltage on the auxiliary winding and therefore the output voltage. In this design, the auxiliary voltage is set to  $((200 \text{ k}\Omega / 36.5 \text{ k}\Omega) + 1) \times 1.75 \text{ V} = 11.3 \text{ V}$ . This results in an output voltage of 11.3 V  $\times$  2.66/6 = 5.02 V. When designing for another output voltage, the designer must ensure that the auxiliary voltage is in a valid range and that the turns ratio meets the requirements.

For smaller output power, a smaller transformer can be used. This design is also tested with a 7-W transformer with smaller mechanical size. See † 3.2.1.3 for the test results with a 4-V, 7-W solution. For applications requiring even less power, a transformer for 3 W can be designed, which is even smaller than the 7-W solution.

#### 2.4.1.3 Sync Rectification

When using a diode rectification at the output of a primary-side regulated flyback, the output voltage changes depending on the load. At a very low load, the regulator operates in discontinuous conduction mode (DCM), and the diode rectifies the peak voltage at the output, resulting in a higher voltage. With an increasing load, the voltage drops, as the forward voltage of the diode is depending on the current. Moreover, the output voltage is temperature-dependent. All of these effects have a rather low impact on the voltage. However, this can be especially true at low output voltages, such as 5 V or 3.3 V, which are already too high. The power dissipation of the diode can be a reason to use a synchronous approach.

For low-output voltages, the synchronous rectification is a good approach to get a stable voltage over the full load range. This type of rectification forces the converter to always stay in continuous conduction mode (CCM) and therefore always operate at the same duty cycle independent of the load at the output.

The MOSFET for rectification is driven by an additional winding on the transformer, and the gate drive can be implemented in a simple way. The gate-source voltage is limited by two Zener diodes, D5 and D8, to not exceed the maximum allowed voltages. The gate is charged through a resistor to control the slew rate and is turned off through a diode to turn off fast and reduce shoot through.

For selecting the MOSFET, a device with very low gate charge and that is slightly higher on resistance is a good choice, as most losses are caused by delayed turn on and off.

#### 2.4.1.4 Auxiliary Power

Adding an option for external power can be done in different ways.

16 gives an overview of the different options that are possible.

Adapter

Option 1

www.ti.com.cn System Overview

#### From Ethernet - ransformers VPD VDD Low Voltage DEN Output 0.1uF 587 CLS Power From Spare Pairs or Transformers PS23758 Circuit VSS RTN

Adapter

Option 2

#### 图 15. Adapter ORing Options

Implemented in this design is option 2, injecting the power right after the PD controller and before the flyback converter. Compared to option 1, option 2 allows a wider voltage range for the auxiliary input. Option 1 would limit the input voltage range to a voltage above 42 V. Option 3 would require an additional voltage regulator when realizing a 24-V input, as ORing is happening after the regulator.

Adapter

Option 3

To realize the powering option in the reference design, voltage must be injected between the VPD net and PGND. Decoupling the PoE voltage from the auxiliary voltage is done by using an ideal diode to minimize the voltage drop as well as power dissipation.

17 shows the schematic of the ideal diode. Compared to a standard or Schottky diode, the LM74700-Q1 has a regulated voltage drop of only 20 mV. Ensure that a MOSFET with proper voltage rating is used. The VPD voltage is used during PoE operation at a level of up to 57 V, whereas VAux can be zero or even at a reversed auxiliary power. This reference design uses a 100-V MOSFET here to have enough headroom.

图 16. Adapter ORing With Ideal Diode

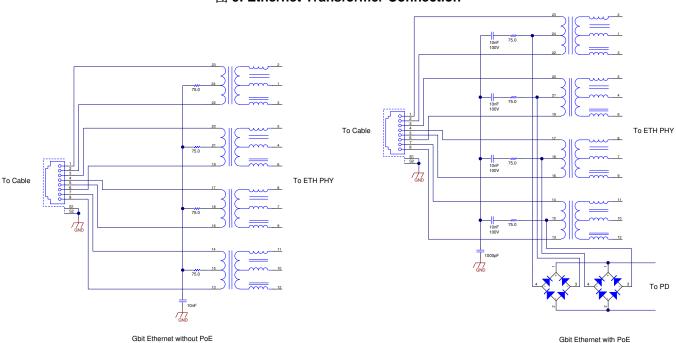

#### 2.4.2 Ethernet Connection

The Ethernet PHY DP83867 builds the interface to the physical layer of the Ethernet connection. The overall dataflow is shown in 🗵 18. The task of the PHY is to translate the reduced gigabit media independent interface (RGMII) signals to a media dependent interface (MDI). This PHY supports 10/100/1000 Mbit/s Ethernet at a low power dissipation of typically 495 mW.

图 17. Data Path of the TIDA-010083

#### 2.4.2.1 MDI Connection

The connection from the MDI of the PHY towards the network cable is DC isolated by using a transformer. For each pair, it is required to be isolated. As 1000-MBit/s Ethernet uses four pairs, four transformers are needed. Typically, integrated solutions with the four necessary transformers in one package are used. In space-constrained applications, it can be beneficial to have two packages with two transformers each.

图 18. Ethernet Transformer Connection

One device is used integrating four isolated channels. To implement PoE, it is important to have access to the middle tap of the transformer. In some cases, the channels are already tied together to minimize the footprint.

19 shows the connection in this reference design. On the left side, the PHYs MDI connection is shown going to the transformer. The middle tap on the PHY side must connect to the GND by using a capacitor. The middle tap of the other side is providing power to the PD controller and therefore must be connected to a diode bridge. Also, it is necessary to have a termination here. This Bob Smith termination uses a capacitor and a resistor to connect the middle taps together and to the GND. For electromagnetic interference (EMI) reasons, TI recommends connecting the GND of the cable side to the GND of the PHY through the RC network R44 and C54.

The MDI must be routed on the board as a differential pair with an impedance of 100  $\Omega$ , and the lines of each pair should have the same length. The pairs are independent to each other and do not need tight matching.

#### 2.4.2.2 Power

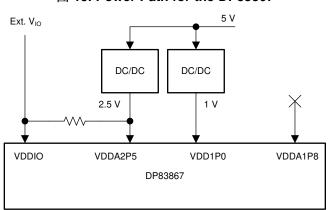

№ 20 shows the power tree for the DP83867 Ethernet PHY. From the 5 V at the output of the PoE part, two additional voltages are generated to supply the Ethernet PHY.

图 19. Power Path for the DP83867

The PHY requires a 2.5-V and 1.0-V supply voltage. An optional 1.8-V rail exists that can be used to reduce the power dissipation of the PHY. However, in this reference design, this voltage is not used and is generated internally in the PHY. The IO voltage of the DP83867 can be either 1.8, 2.5, or 3.3 V. This design offers the option to either use the 2.5 V as IO voltage or an externally applied voltage. In an externally applied voltage, the resistor R42 must be removed.

#### R10 SW 470nH vos C58 R36 VSEL/MODE 10V 23.7k 10uF GND TPS62801YKAR GND GND +2V5 SW 470nH vos R39 VSEL/MODE 10V 44.2k 10uF TPS62802YKAR GND

#### 图 20. Power Supply of the DP83867

In 21, the power supply using the TPS62801 and TPS62802 is shown. The input voltage can be disconnected by removing R10 during efficiency measurements and initial bring up. The resistor R42 is used for bridging the 2.5-V rail to the IO voltage. This voltage can be set for stand-alone testing, to supply the IO voltage to the connector, or for use on an external board. If any other IO voltage is to be used, this resistor must be removed.

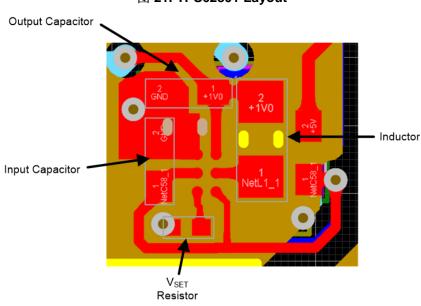

图 21. TPS62801 Layout

Both regulators offer a very high switching frequency of 4 MHz and require only one resistor to set the output voltage. This enables a very small PCB footprint as shown in 22 for the power supply. The area shown in 21 is less than 4 x 4 mm² in size. Especially at this switching frequency, it is necessary to place the components as close as possible to minimize parasitic effects. The IC package is designed in a way that the critical GND, as well as the switching part, can be routed very short.

#### 2.4.2.3 PHY

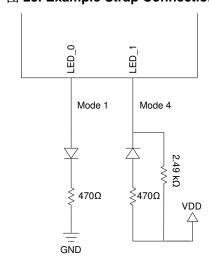

Besides power and the transformer connection, the PHY also requires additional configuration. In 🖺 23, the strapping configuration that is done on the board is shown. The PHY supports a four-level strapping, meaning for each configuration pin, four voltage levels are valid to define a parameter. A table in the datasheet of the DP83867 clarifies which parameter can be set on which pin. These pins are multiplexed with other functions, so following the release from reset, the strap level is read, and the pin switches its function, for example, to GPIO.

Straps: R23 LED 0 6.04k 1% LEDO LED1 LED2 LED 1 ANEG SELO LED 2 Open 150040GS73240 150040GS73240 6.04k // 2.49k RX CTRL Auto Neg on 2.49k 1% Further strapping done on other board R32 R33 GND

图 22. DP83867 Configuration Strapping

The LED pins are also used as strap and depending on the level here, the connection of the LED has to be changed.

図 24shows how to connect the LEDs for different strap options.

图 23. Example Strap Connection

Some of the configuration of the PHY can also be set by using MDIO, whereas the MDI address can only be set by using the strap options.

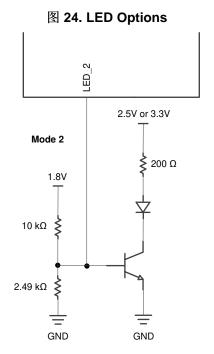

The connection of the LEDs is a bit special when using 1.8 V as IO voltage.

■ 25 shows how to connect an LED in this case. As LEDs typically require more than 1.8 V to light up, an open-collector, level-shifting circuit must be built at the LED output, and a higher voltage must be used for the LED itself. This circuit can also be built using a MOSFET as long as the gate threshold voltage is low enough so that the FET switches on at 1.8 V.

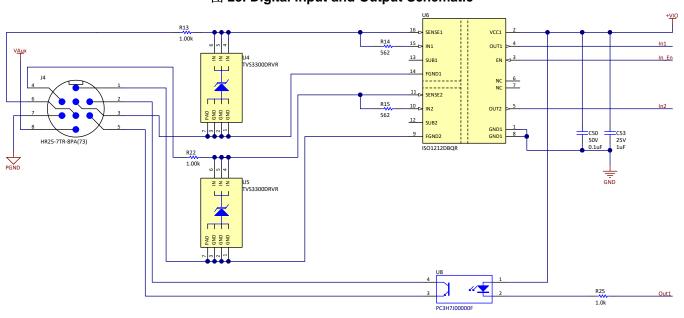

#### 2.4.3 Digital IO

The reference design includes two digital inputs as well as one digital output. Depending on how the PoE is realized, together with an additional auxiliary power it can be required to have an isolation for all other digital inputs and output of a system.

图 25. Digital Input and Output Schematic

Here a digital isolation of the IOs is implemented. This enables flexibility in how to use the inputs and outputs.

26 shows the implementation in the schematic. All digital channels are isolated to each other and can be used in an NPN or PNP configuration.

The digital inputs are realized with an ISO1212 that can be used for realizing type 1, 2, and 3 digital inputs and withstands  $\pm 60$  V.

#### 3 Hardware, Software, Testing Requirements, and Test Results

#### 3.1 Required Hardware

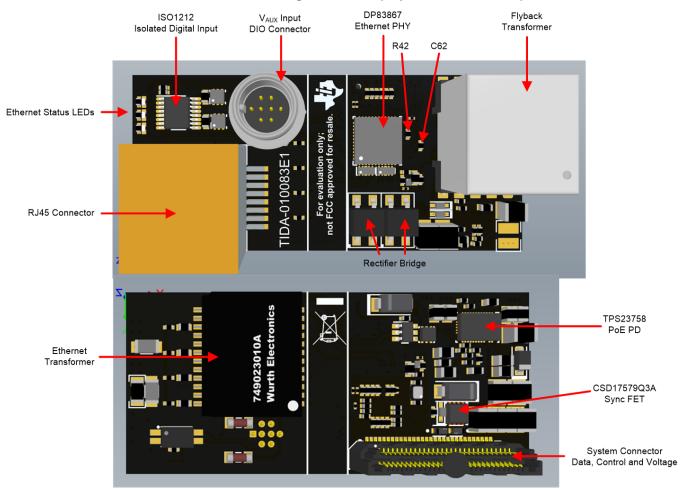

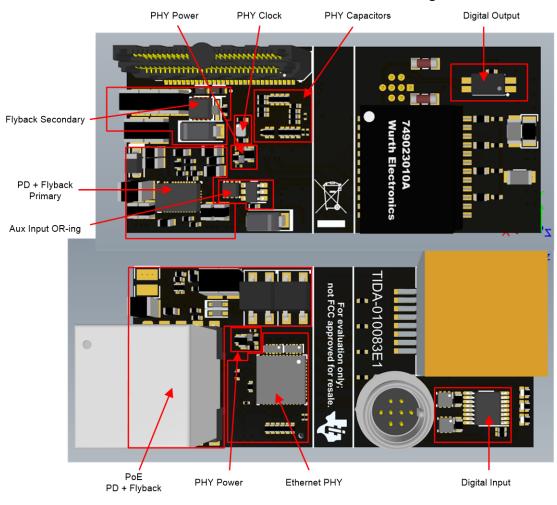

This reference design can be evaluated alone or with an additional FPGA or a processor board with an RGMII interface. The IO voltage for RGMII, as well as the digital IOs, can either come from the design and be set to 2.5 V, or it can be applied externally after removing R42. The Ethernet PHY can either be clocked by the on-board crystal or by removing the crystal and assembling C62 from any external source. See 27 for an overview of the physical location of the main components and connectors.

图 26. Reference Design Overview (Top and Bottom View)

The system connector shown in 26 provides access to the RGMII signals and digital IO and provides 5 V at a maximum of 2.4 A of output power. For complete evaluation of the data connection, TI recommends using a custom adapter board with the correct impedance and length matching to have a proper signal integrity of the RGMII signals to connect to a MAC, either in FPGA or processor. For testing the MDI path including the RJ45 Ethernet transformer and PHY, the PHY can be placed into a reverse loopback mode. This enables remote testing of the connection and impact of PoE without the RGMII connection. See 3.5 To the test setup and results of this test.

For evaluating the power stage of the board, it is necessary to connect a load to the system connector and a power source to one of the inputs as described in  $\dagger$  3.2.1. Three different transformers are tested as a part of this design. Two variants are designed for 5 V and 13 W, and one variant is designed for lower power applications with 4 V and 7 W.

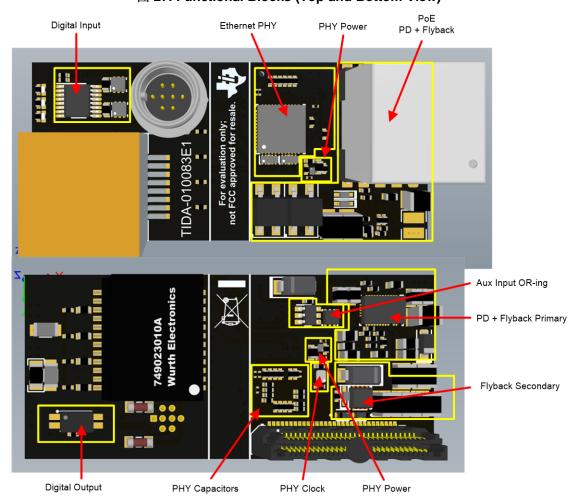

In 🛭 28 an overview is shown where the different functional blocks of the system are located on the PCB.

图 27. Functional Blocks (Top and Bottom View)

#### 3.2 Testing and Results

The following section contains measurement data of the isolated flyback converter, the PD controller, and the Ethernet PHY itself. Also included are thermal images showing the design at different load levels and transformer configurations. The test setup is explained in each section.

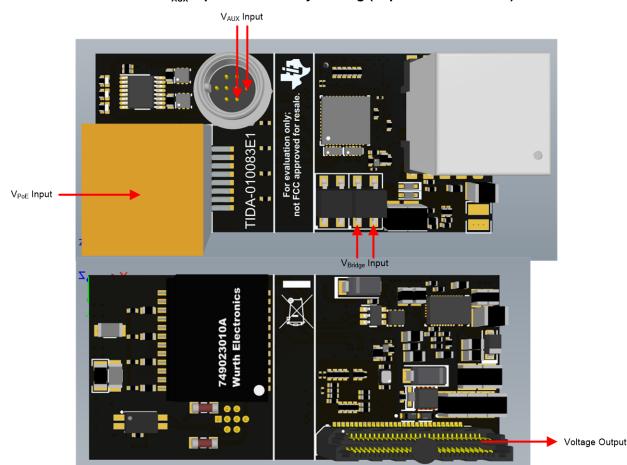

#### 3.2.1 TPS23758 PoE Flyback

This section covers different tests that were done on the flyback part of the design. The efficiency and voltage drop is tested with different transformers and input voltages. Because there are different possibilities to power the flyback, these where tested separately. In  $\boxtimes$  29, the different options for voltage input on the PCB are shown. Power comes through the RJ45 connector (shown as  $V_{PoE}$ ) which is the usual way to power a PoE PD from the PSE. A second option is to power it through the  $V_{AUX}$  input, bypassing the PD part of the TPS23758 and powering the flyback converter directly. A third option is powering the part after the diode bridges ( $V_{Bridge}$ ), bypassing the diodes but not the PD part. The different variants for powering have different path losses like voltage drop on the diode bridges and the pass FET for the PD. Though the efficiency depends on where the voltage is injected. The highest efficiency can be achieved using the  $V_{AUX}$  input that bypasses the PD part.

As the flyback is using primary side regulation, the voltage at the output can show a small current depended drop.

图 28. V<sub>AUX</sub> Input for Efficiency Testing (Top and Bottom View)

#### 3.2.1.1 TPS23758 Using LinkCom® LDT1018 Transformer

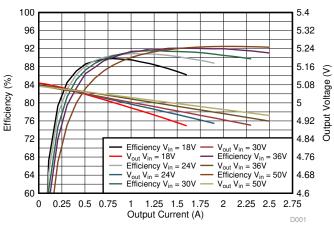

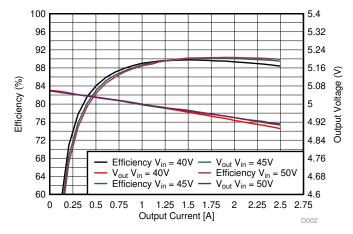

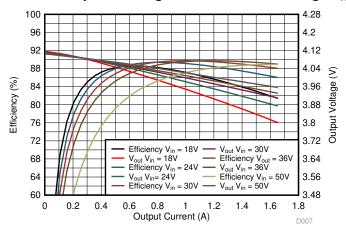

This sections covers all tests done with a LinkCom® LDT1018 transformer, designed for 13 W at 5 V. In  $\boxtimes$  30 shows the efficiency and drop of the output voltage. For this test, the power comes through the V<sub>AUX</sub> input, giving the highest efficiency. As it is not designed to be fully loaded at low input voltages, the curves for 18 V, 24 V, and 30 V are not measured up to 2.5 A.

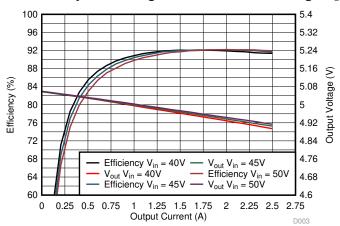

The same tests are done with power over the RJ45 connector, V<sub>PoF</sub>, shown in \( \bar{\text{\text{S}}} \) 31.

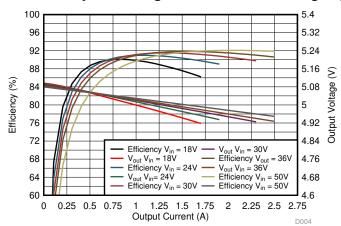

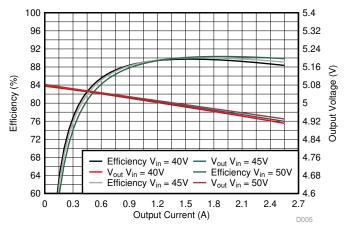

A third test is done powering after the diode bridges,  $V_{Bridge}$ , shown in  $\boxtimes$  32.

图 29. Efficiency and Voltage When Powered Through VAUX

图 30. Efficiency and Voltage When Powered Through V<sub>PoE</sub>

#### 图 31. Efficiency and Voltage When Powered Through V<sub>Bridge</sub>

#### 3.2.1.2 TPS23758 Using Würth 750318525 Transformer

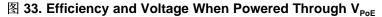

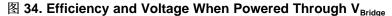

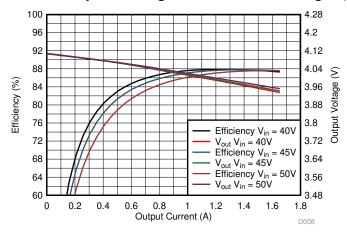

This section handles the same tests as before with a 750318525 transformer from Würth, designed for 13 W at 5 V.

图 32. Efficiency and Voltage When Powered Through V<sub>AUX</sub>

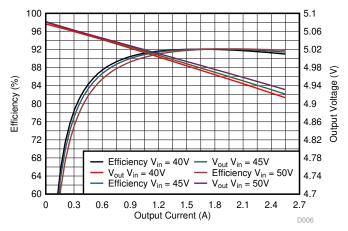

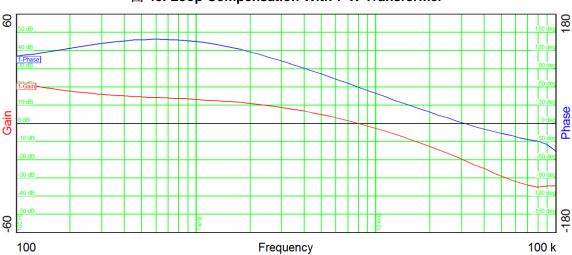

图 35. Loop Compensation With 750318525 Transformer

§ 36 shows the frequency response of the regulation loop with the Würth 750318525 13-W transformer tested at a 2.4-A load with a 36-V input voltage. The value of C52 must be set to 6.8 nF and R28 to 100 kOhm for this as noted in the schematic.

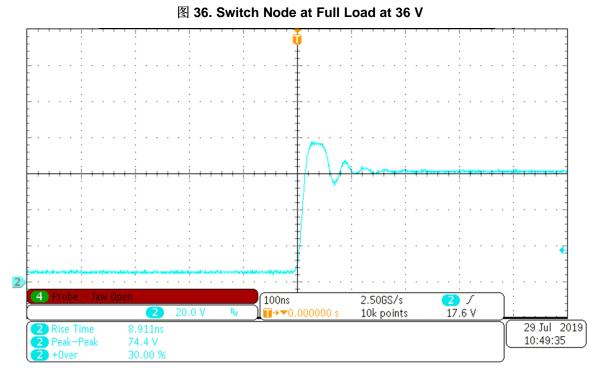

🛚 37 shows the switch node at an load current of 2.4 A and an input voltage of 36 V.

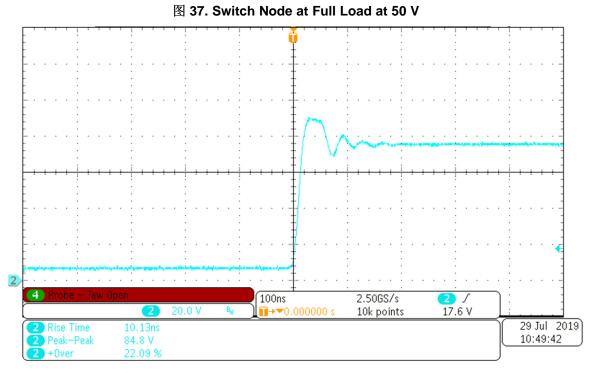

🛚 38 shows the switch node with same load as before at an input of 50 V.

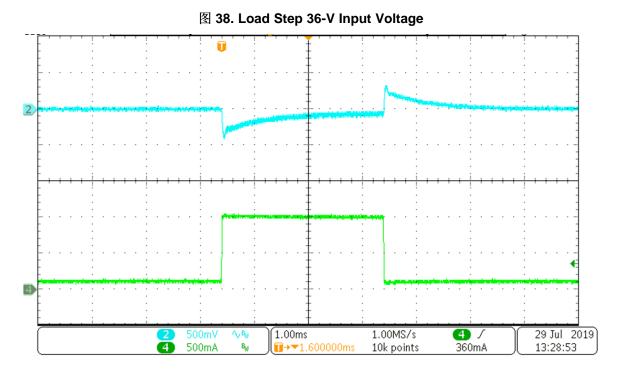

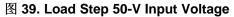

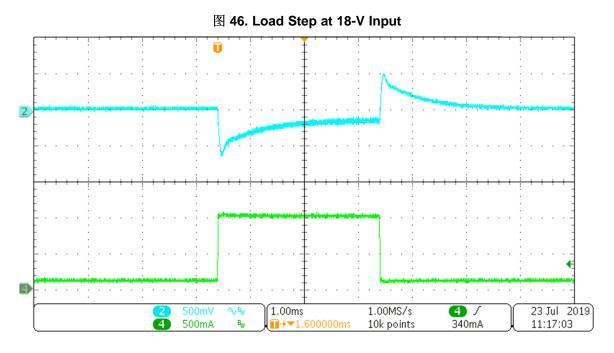

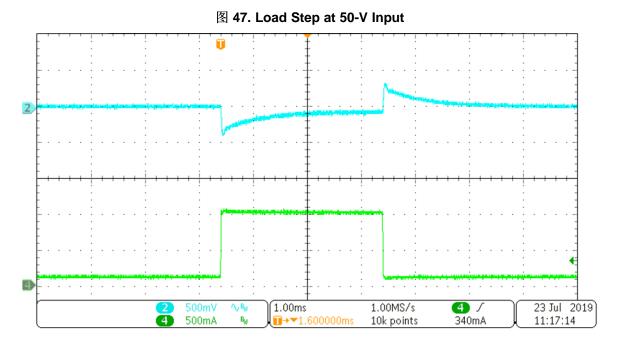

§ 39 and § 40 show the response to a fast load step from 0.1 A to 1 A at different input voltages. The reaction on the step confirms a fast and stable regulation.

#### 3.2.1.3 TPS23758 Using Würth 750318517 Transformer

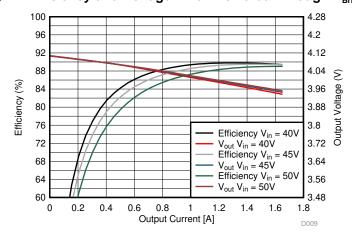

The same tests as performed previously are done with a Würth 750318517 transformer. This transformer has a smaller mechanical size and is designed for 7 W at an output voltage of 4 V.

#### 图 40. Efficiency and Voltage When Powered Through V<sub>AUX</sub>

#### 图 41. Efficiency and Voltage When Powered Through V<sub>PoE</sub>

# 图 42. Efficiency and Voltage When Powered Through $V_{\mbox{\scriptsize Bridge}}$

图 43. Loop Compensation With 7-W Transformer

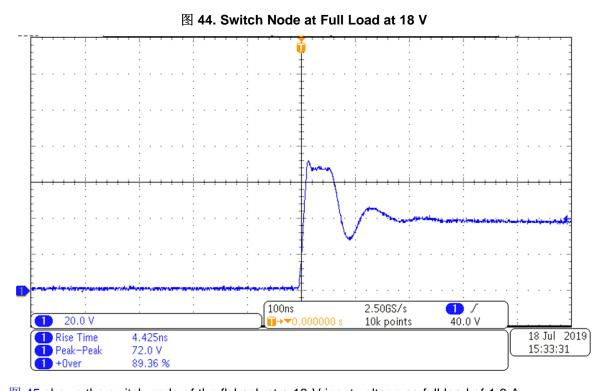

44 shows the frequency response of the regulation loop with the 7-W transformer tested at a 1.6-A load with a 18-V input voltage. The value of C52 must be set to 10 nF and R28 to 68 kOhm for this as noted in the schematic.

8 45 shows the switch node of the flyback at a 18-V input voltage as full load of 1.6 A.

1 +Over

26.44 %

图 45. Switch Node at Full Load at 50 V

100ns 2.506S/s 1 /

20.0 V

1 Rise Time 11.31ns 18 Jul 2019 15:33:40

In 🛭 46, the switch node with the 750318517 7-W transformer is shown at a 50-V supply voltage.

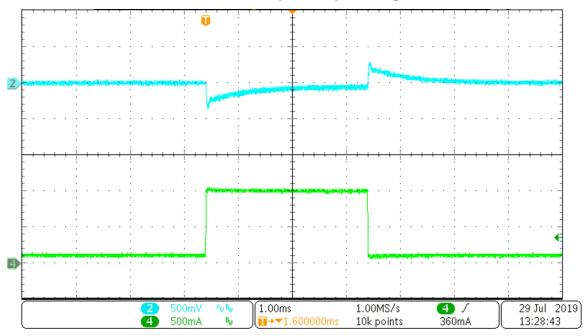

§ 47 and § 48 show the response to a fast load step from 0.1 A to 1 A at different input voltages. The reaction on the step confirms a fast and stable regulation.

#### 3.2.2 TPS23758 PoE Powered Device - Detection and Classification

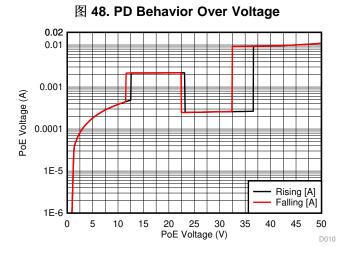

Depending on the voltage coming from the PSE, the PD must behave differently to do the correct signaling for detection and classification. To test the proper behavior, the PoE voltage is swept from 0 V to 50 V, and the input current is measured.

In the phase between 2.7 V and 10.1 V, the detection happens, and it must behave like a resistor of 19 k $\Omega$  and 26.5 k $\Omega$ .

Between 14.5 V and 20.5 V, the classification is happening and the current must be for a class 0 device between 0 mA and 4 mA.

Between 36 V and 42 V, the PD must turn on when the voltage is rising.

In 🖺 49, the results of sweeping the PoE voltage is shown. The different current levels, the turn on point, and the hysteresis can be seen.

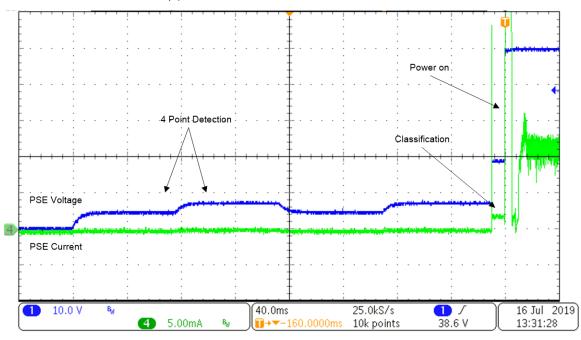

When connecting the PD to a PSE, the PSE senses the detection resistance followed by the classification current. 🛭 50 shows the scope plot of this process. The blue line shows the voltage which defines the state the PD is in. It starts with a detection phase, followed by the classification and then finally powers the device on.

图 49. PoE Detection and Classification

# 3.3 Auxiliary Power Priority

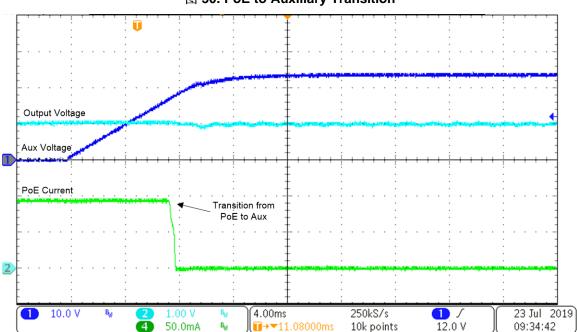

The TPS23758 allows a smooth transition from PoE power to auxiliary power.

图 50. PoE to Auxiliary Transition

🛚 52 shows how the TPS23758 transitions from PoE power supply to auxiliary power. As soon as the auxiliary voltage is above a certain level, the PD switches off and the PoE current falls to zero. The necessary power is provided over the auxiliary power supply. The output voltage remains stable during the transition.

#### 3.4 Thermal Performance

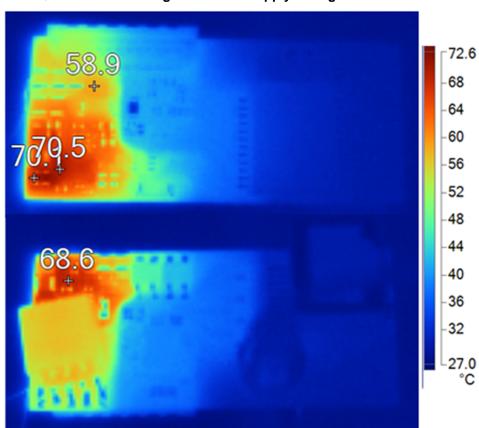

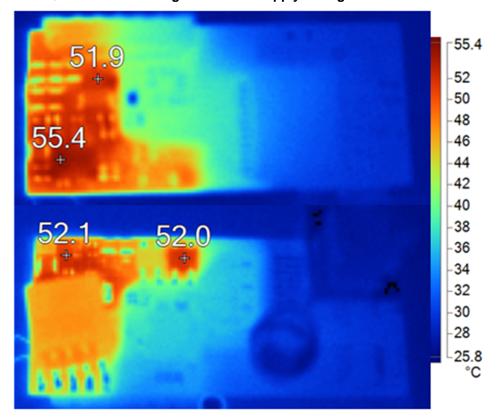

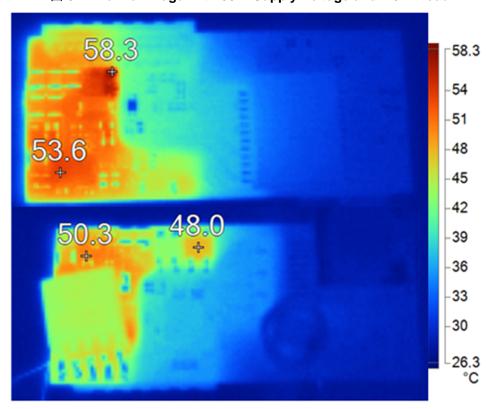

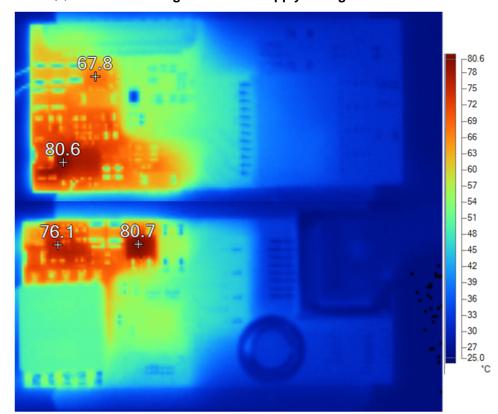

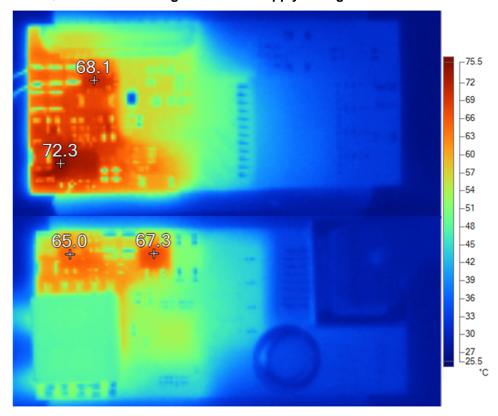

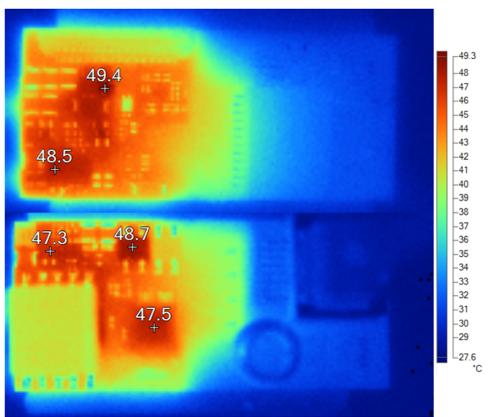

This sections shows the thermal performance of the reference design with two different configurations. One variant uses the previously mentioned 750318517 transformer tested up to 7 W, and the other variant uses one of the 13-W transformers.

The thermal images below are stitched together to show both sides of the PCB at once.

§ 51 shows the functional blocks on the board in the same orientation as in the thermal images to understand the thermal behavior of the different subsystems.

## 图 51. Functional Blocks as Shown in Thermal Images

## 3.4.1 Output Configured for 7 W, 4 V

For this test, the reference design uses the Würth 750318517 transformer and is loaded with 1.6 A.

图 52. Thermal Image With 18-V Supply Voltage and 1.6-A Load

853 shows the design loaded with 1.6 A and an input voltage of 18 V. For this test, the design is powered through the  $V_{AUX}$  input. As this is the lowest designed input voltage, this results in the highest input and switching currents, as well as the highest duty cycle. The image shows that the highest temperature is at the TPS23758 and the shunt resistor for current measurement, so the most power is dissipated by the switch FET of the flyback regulator. The rectification FET on the secondary side does not dissipate that much power. Also, the ORing FET that is used at the  $V_{AUX}$  input does not heat up significantly.

图 53. Thermal Image With 36-V Supply Voltage and 1.6-A Load

图 54. Thermal Image With 50-V Supply Voltage and 1.6-A Load

$\boxtimes$  54 and  $\boxtimes$  53 show the design powered through the  $V_{PoE}$  input at different voltage levels. In addition to the heat dissipated from the TPS23758, here also the diode bridge gets a significant heat source.

## 3.4.2 Output Configured for 13 W, 5 V

For this test, the reference design uses the Würth 750318525 transformer and is loaded with 2.4 A.  $\boxtimes$  55 and  $\boxtimes$  56 show the design powered through the  $V_{PoE}$  input at different voltage levels. In addition to the heat dissipated from the TPS23758, here also the diode bridge gets a significant heat source.

图 55. Thermal Image With 36-V Supply Voltage and 2.4-A Load

图 56. Thermal Image With 50-V Supply Voltage and 2.4-A Load

图 57. Thermal Image With 48-V Supply Voltage and 1-A Load

§ 56 and § 57 show the 13-W solution at full load and two different input voltages. In § 58, the system is shown with a load of 1 A and a typical PoE voltage of 48 V.

Depending on the desired total system power, it might be necessary to have better cooling or reduction of the diode losses in the rectifier bridge by using an active rectification circuit. In larger applications, a larger cooling plane will help to reduce the temperature on the board. A thicker copper layer on the board will help to improve thermal transfer.

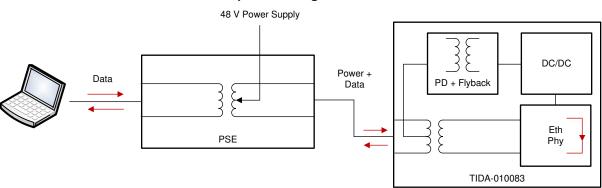

### 3.5 Data Interface

To test the MDI interface and by this the path from the RJ45 connector over the data transformer towards the PHY, the setup shown in § 59 is used. The PHY is configured in reverse loopback, so it sends every frame that is received on the MDI interface back. When sending data to it from a PC, this PC should see every frame that is sent.

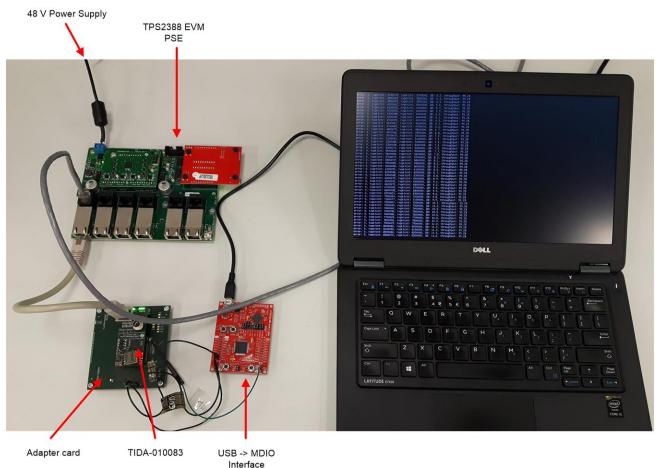

图 58. Setup for Testing the Data Transfer

The actual test setup is shown in 2.3 † in addition to \$\infty\$ 58, a converter from MDIO to USB is used for configuring the PHY. Normally MDIO is used by a processor or FPGA to configure the PHY and read back status information. For debugging, the PHY is configured into reverse loopback by writing register 0x16 to 0x20. A PC running Linux is used for sending ethernet frames with a unique 64-bit sequence number and checking back if this is received. When an error on the transmission occurs, a frame will be dropped as the FCS will not match. The PC will then see a missing sequence number.

This test is done with different PoE load conditions as shown in  $\frac{1}{2}$  3. For every test frame with a size of 1500 bytes + headers are used and at least 1 TB of test data is transmitted and received back.

表 3. Error Rates

| TEST CONDITION                  | NUMBER OF ERRORS WITH 20-cm CAT 6<br>CABLE | NUMBER OF ERRORS WITH 150-m<br>CAT 6 CABLE |

|---------------------------------|--------------------------------------------|--------------------------------------------|

| No PoE                          | 0                                          | 0                                          |

| PoE 7-W transformer no load     | 0                                          | 0                                          |

| PoE 7-W transformer 1.6-A load  | 0                                          | 0                                          |

| PoE 13-W transformer no load    | 0                                          | 0                                          |

| PoE 13-W transformer 2.4-A load | 0                                          | 0                                          |

www.ti.com.cn Design Files

## 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-010083.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-010083.

## 4.3 PCB Layout Recommendations

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-010083.

## 4.4 Altium Project

To download the Altium Designer® project files, see the design files at TIDA-010083.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-010083.

## 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-010083.

#### 5 Software Files

To download the software files, see the design files at TIDA-010083.

#### 6 Related Documentation

- Texas Instruments, TPS23758 IEEE 802.3at PoE PD with No-Opto Sync Flyback DC-DC Controller Data Sheet

- 2. Texas Instruments, TPS23758EVM-080 Evaluation Module User's Guide

- Texas Instruments, DP83867IR/CR High Immunity 10/100/1000 Ethernet Physical Layer Transceiver Data Sheet

- 4. Texas Instruments, DP83867EVM User's Guide

- 5. Texas Instruments, LM74700-Q1 Low IQ Reverse Polarity Protection Ideal Diode Controller Data Sheet

- 6. Texas Instruments, ISO121x Isolated 24-V to 60-V Digital Input Receivers for Digital Input Modules

Data Sheet

- 7. Texas Instruments, Broken Wire Detection Using an Optical Switch Reference Design

- 8. Texas Instruments, TPS6280x 1.8-V to 5.5-V, 0.6A / 1-A, 2.3-μA IQ Step Down Converter 6-Pin, 0.35-mm Pitch WCSP Package Data Sheet

#### 6.1 商标

E2E, DCS-Control are trademarks of Texas Instruments.

Altium Designer is a registered trademark of Altium LLC or its affiliated companies.

LinkCom is a registered trademark of LinkCom Manufacturing Co.

All other trademarks are the property of their respective owners.

Related Documentation www.ti.com.cn

## 6.2 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

### 7 About the Author

**STEFFEN GRAF** is a systems engineer at Texas Instruments where he is responsible for developing reference design solutions for the industrial segment. He earned his master of science in electrical engineering at the University of Applied Science in Darmstadt, Germany.

## 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司