# 设计指南: TIDA-050022 适用于输入电压低于 100V 的直流/直流转换器的功率级参考设 计

# 🐺 Texas Instruments

#### 说明

此参考设计基于 UCC27282 120V 半桥 MOSFET 驱动 器和 CSD19531 100V 功率 MOSFET,可实现高频功 率级设计。凭借高效开关和灵活的 V<sub>GS</sub> 工作范围,此设 计可降低总体栅极驱动和传导损耗,以实现最佳效率。此功率级设计可广泛应用于众多空间受限型 应用,例 如电信砖型电源模块、光伏逆变器和直流电机驱动器。

#### 资源

TIDA-050022 UCC27282 CSD19531 设计文件夹 产品文件夹 产品文件夹

咨询我们的 E2E™ 专家

#### 应用

A

- 电信砖型电源模块

- 光伏微型逆变器和电源优化器

- 服务器和网络电源

- 直流电机驱动器

#### 特性

- 开关频率高达 1MHz 的紧凑型 100V 功率级设计

- 适用于高侧和低侧并具有跨导保护功能的独立脉宽 调制 (PWM) 输入

- 16ns 的低传播延迟,延迟匹配典型值为 1ns,最大 值为 7ns

- 驱动器 VDD 工作范围为 6V 至 16V

- 负电压能力,可承受高噪声环境

- 具有低待机电流的使能端

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

#### 1 System Description

Telecom and datacom equipment capabilities keep increasing with demand for more processing power within a given size, or even size reduction as well. Increased capabilities of the equipment result in more demand from the power supplies. The power supplies in these systems must be optimized from a space utilization an efficiency standpoint. The complexity of control and interface is also increasing in telecom, datacom, and solar systems which make them more susceptible to noise and transients .

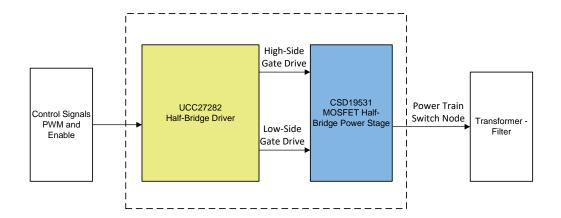

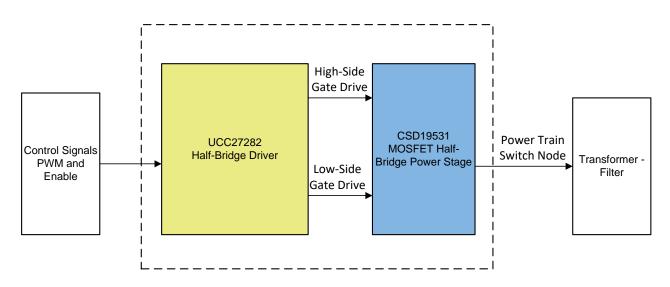

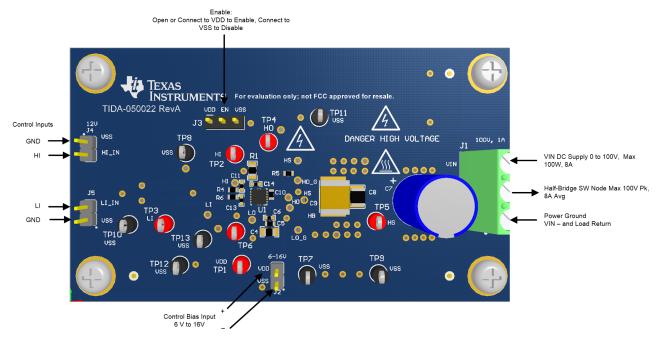

The half-bridge driver and power MOSFET power stage is used in a variety of DC/DC converter topologies including half-bridge, full bridge, synchronous buck, and full-bridge synchronous rectification. Solar micro inverters, solar optimizers and motor drive also use this power stage in many applications.

This reference design uses CSD19531 NexFET<sup>™</sup> Si power MOSFETs and the UCC27282 120-V halfbridge driver to realize a power stage with high efficiency. The half-bridge driver allows two independent inputs for high-side and low-side gate drive and has cross conduction protection which turns off both gate drive signals in the event both inputs are high. The cross conduction protection does not have a fixed dead time so the controller can control precise timing of the turn on and turn off of the power MOSFETs.

This design can be applied to many high-efficiency applications such as telecom power modules, solar power, 48V server power, and industrial power supplies.

#### 1.1 Key System Specifications

| PARAMETER                        | TEST CONDITIONS                                                                                             | MIN | TYP | MAX                | UNITS |

|----------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|--------------------|-------|

| INPUT AND OUTPUT CH              | ARACTERISTICS                                                                                               | U   |     |                    |       |

| Input and output voltage         |                                                                                                             | 0   |     | 100 <sup>(1)</sup> | V     |

| Input and output current         |                                                                                                             | 0   | 4   | 8                  | А     |

| Bias voltage                     |                                                                                                             | 6   | 8   | 16                 | V     |

| LI and HI Inputs to VGS<br>Delay |                                                                                                             |     | 15  | 30                 | ns    |

| Delay Matching                   | LI/HI Complimentary                                                                                         |     | 1   | 7                  | ns    |

| SYSTEM CHARACTERIS               | TICS                                                                                                        |     |     |                    |       |

| Switching frequency              |                                                                                                             | 10  | 200 | 1000               | kHz   |

| Efficiency                       | $V_{IN} = 48 \text{ V}, V_{OUT} = 24 \text{ V}, I_{OUT} = 4 \text{ A}, $<br>$f_{SW} = 200, 300 \text{ kHz}$ | 94  | 95  | 95.3               | %     |

#### 表 1. Key System Specifications

<sup>(1)</sup> HS voltage (MOSFET switch node) is limited to 100 V including overshoot. This may limit input voltage to a lower value.

#### 2 System Overview

#### 2.1 Block Diagram

#### 图 1. TIDA-050022 Block Diagram

## 2.2 Design Considerations

#### 2.2.1 FET Selection

The majority of 48 V input voltage telecom and datacom power module designs have gate driver bias voltage ( $V_{DD}/V_{CC}$ ) voltage in the 9 V to 10 V range using 100 V ( $V_{DS}$ ) rated power MOSFETs. The gate drive losses are reduced with lower gate drive voltage ( $V_{GS}$ ) and many MOSFET devices  $R_{DS(on)}$  versus  $V_{GS}$  curves indicate that there is little reduction in  $R_{DS(0n)}$  beyond 8 V to 10V  $V_{GS}$ . One consideration of selecting the driver  $V_{DD}$  is the turn on UVLO threshold and including some margin for negative voltage transients on the bias supply. This may result in selecting the driver  $V_{DD}$  to be higher than the optimum gate drive and conduction loss operating point when using previous generation drivers.

The CSD10531 100V 5.3 m $\Omega$  MOSFET total gate charge, or  $Q_G$ , vs  $V_{GS}$  and the  $R_{DS(on)}$  vs  $V_{GS}$  can be viewed in the CSD19531 data sheet. Although this MOSFET has an  $R_{DS(on)}$  specification with  $V_{GS}$  = 6 V you can see that the  $R_{DS(on)}$  curve still has a noticeable declining  $R_{DS(on)}$  vs  $V_{GS}$  at 6 V. At  $V_{GS}$  = 8 V the curve slope is much lower.

The gate drive losses for each driver output channel are dependent on  $V_{DD}$ , switching frequency ( $F_{SW}$ ), and MOSFET  $Q_G$  as shown in  $\Delta r$  1.

$$\mathsf{P}_{\mathsf{GD}} = \mathsf{V}_{\mathsf{DD}} \times \mathsf{f}_{\mathsf{SW}} \times \mathsf{Q}_{\mathsf{G}}$$

(1)

Another consideration for applications which will have body diode conduction during the switching transitions such as synchronous buck or synchronous rectification is the body diode  $t_{rr}$  and  $Q_{rr}$ . The body diode reverse recovery losses delta can exceed conduction loss delta even though the  $R_{DS(on)}$  is lower if the body diode reverse recovery time is longer. See  $\gtrsim 2$  for parameter comparison of the CSD19531 MOSFET and CSD19533 MOSFET.

System Overview

www.ti.com.cn

(2)

(3)

表 2. Parameter Comparison of Switching FETs

| PARAMETER                                         | CSD19531 | CSD19533 |

|---------------------------------------------------|----------|----------|

| Max V <sub>DS</sub> (V)                           | 100      | 100      |

| $R_{DS(on)}$ (m $\Omega$ ), V <sub>GS</sub> =10 V | 5.3      | 7.8      |

| $R_{DS(on)}(m\Omega), V_{GS}=6 V$                 | 6.0      | 8.7      |

| Q <sub>g</sub> (nC)                               | 37       | 27       |

| t <sub>rr</sub> (ns), Body Diode                  | 147      | 62       |

| Q <sub>rr</sub> (nC), Body Diode                  | 226      | 163      |

#### 2.2.2 Component Selection

#### 2.2.2.1 Bootstrap and VDD Capacitor

The bootstrap capacitor must maintain the V<sub>HB-HS</sub> voltage above the UVLO threshold for normal operation. To determine the minimum required bootstrap capacitance first calculate the maximum allowable drop across the bootstrap capacitor,  $\Delta V_{HB}$ , with  $\Delta \vec{\chi}$  2.

$$\Delta \mathsf{V}_{\mathsf{H}\mathsf{B}} = \mathsf{V}_{\mathsf{D}\mathsf{D}} - \mathsf{V}_{\mathsf{D}\mathsf{H}} - \mathsf{V}_{\mathsf{H}\mathsf{B}\mathsf{L}}$$

where

- V<sub>DD</sub> is the supply voltage of the gate driver device

- $V_{\text{DH}}$  is the bootstrap diode forward drop

- V<sub>HBL</sub> is the HB falling UVLO threshold (V<sub>HBR(max)</sub> V<sub>HBH</sub>)

Many applications may target ripple voltage lower than the equation result, such as 0.5 V to 1 V ripple.

Determine the estimated charge per switching cycle from the bootstrap capacitor with 公式 3.

$$Q_{TOTAL} = Q_G + I_{HBS} \times \left(\frac{D_{MAX}}{f_{SW}}\right)$$

where

- $Q_G$  is the total MOSFET gate charge

- $I_{HBS}$  is the HB to VSS leakage current

- D<sub>Max</sub> is the converter maximum duty cycle

- I<sub>HB</sub> is the HB quiescent current

Once the total charge is known the minimum bootstrap capacitance can be determined as follows in  $\Delta \mathfrak{K}$  4.

$$C_{BOOT(min)} = \frac{Q_{TOTAL}}{\Delta V_{HB}}$$

(4)

The bootstrap capacitor should be X7R or better dielectric with low inductance package(s). Also since the capacitance is reduced with DC bias, choose a capacitor with at least two times the expected maximum voltage in the application.

TI recommends the VDD capacitor value at least 10x the value of the bootstrap capacitance to minimize VDD ripple from charging the bootstrap capacitor. The VDD capacitor should also be X7R or better temperature stability dielectric. It is recommended to parallel a high frequency bypass capacitor in a small package size, 0402, and low value such as 1nF to filter high frequency noise with the VDD capacitor.

#### 2.2.2.2 External Gate Resistor

these possible issues.

In high frequency switching power supply applications where high-current gate drivers such as the UCC27282 are used, high current loops with parasitic inductances and parasitic capacitances can cause noise and ringing on the gate of power MOSFETs. Gate resistors are used often to damp this ringing and noise. There are also cases where gate resistance may be selected to address EMI and excessive switch node voltage spikes. It is good practice to make provisions for external gate resistors to allow addressing

Use the following equations to calculate the driver pullup and pulldown current.

The high-side driver pullup current can be determined with  $\Delta \pm 5$ .

$$I_{OHH} = \frac{V_{DD} - V_{DH}}{R_{HOH} + R_{GATE} + R_{GFET(int)}}$$

where

- I<sub>OHH</sub> is the high-side peak pullup current

- V<sub>DH</sub> is the bootstrap diode forward drop

- $R_{HOH}$  is the gate driver internal high-side pullup resistance. Value can be calculated from test conditions ( $R_{HOH} = V_{HOH}/I_{HO}$ )

- R<sub>GATE</sub> is the external gate resistance between the driver output and MOSFET gate

- R<sub>GFET(int)</sub> is the MOSFET internal gate resistance in the MOSFET datasheet

The high-side driver sink current can be determined with 公式 6.

$$I_{OLH} = \frac{V_{DD} - V_{DH}}{R_{HOL} + R_{GATE} + R_{GFET(int)}}$$

where

- $I_{OLH}$  is the high-side peak pullup current

- R<sub>HOL</sub> is the gate driver internal high-side pull-down resistance. Value can be calculated from test conditions (R<sub>HOL</sub>= V<sub>HOL</sub>/I<sub>HO</sub>)

(6)

The low-side driver pullup current can be calculated with 公式 7.

$$I_{OHL} = \frac{V_{DD}}{R_{LOH} + R_{GATE} + R_{GFET(int)}}$$

where

R<sub>LOH</sub> is the gate driver low-side pullup resistance

The low side driver sink current can be determined with  $\Delta \pm 8$ .

$$I_{OLL} = \frac{V_{DD}}{R_{LOL} + R_{GATE} + R_{GFET(int)}}$$

(8)

#### 2.2.3 Layout Considerations

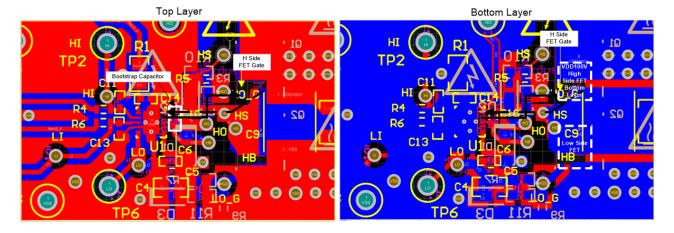

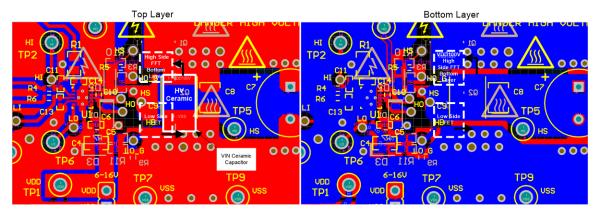

To achieve best performance the layout of the 100-V power stage requires attention to the loop inductance for both the power loop and gate drive loop. 🛽 2 shows a general view of the layout.

System Overview

5

(7)

(5)

#### 图 2. Layout General View

#### 2.2.3.1 Gate Drive Loop Layout

图 3 and 图 4 show the layout of the gate loop of the upper and lower FETs. To achieve the minimum loop inductance, the layout of gate drive loop must follow these rules:

- Have the VDD capacitor or bootstrap capacitor as close as possible to the gate driver because these traces will be part of the gate loop.

- Use a dedicated Kelvin source or minimum sharing of source trace between the gate drive loop and main power loop to achieve the minimum common source inductance. The high di/dt on the power loop can easily be coupled to the gate drive loop. This may cause decreased switching speed and other negative effects.

- To keep the return loops as short as possible, vias in pads are used in this design to further reduce the parasitic inductances and improve the current extraction from components.

#### 图 3. Gate Drive Loop Layout for High-Side FET

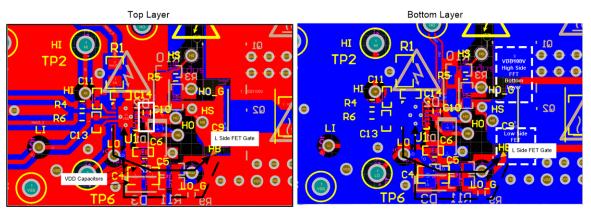

#### 2.2.3.2 Power Loop Layout

The power loop layout objective is to minimize stray inductance. To realize a small power loop:

- Place ceramic capacitors with a small package as close to the devices as possible. These capacitors are usually better in frequency response and have a high bandwidth to absorb high-frequency noise generated during switching than bulk capacitors.

- A compact component placement is needed. Place the upper and lower FETs stacked from VIN to the power ground as close as possible to the input voltage (V<sub>IN</sub>) capacitors.

- Minimize the overlap between switching node and ground/Vin copper. This overlap avoids the extra

parasitic capacitance, which adds to C<sub>oss</sub> of FETs. If not designed well, the parasitic capacitors can

generate significant loss at high switching frequency.

#### 图 5. Half-Bridge Power Loop Layout

#### 2.3 Highlighted Products

#### 2.3.1 UCC27282

The UCC27282 is a 120-V, half-bridge, high-performance MOSFET driver designed for applications that require high drive strength, wide bias voltage operating range, low propagation delays and excellent delay matching.

The UCC27282 half-bridge driver has new features and parameter improvements to achieve optimum power module performance and enhance robustness. The wide operating VDD range of 6 V to 16 V with adequate gate drive strength enhances flexibility to optimize efficiency based on gate drive losses, resistive losses and switching loss. A low signal on the EN pin disables the driver and sets the UCC27282 in a state of low bias current  $I_{DD}$  typically 7  $\mu$ A. This low current will help achieve low standby power when the module is disabled. High-frequency operation and precise timing can be achieved due to low typical propagation delay of 16 ns and typical delay matching of 1 ns.

The UCC27282 includes an input interlock feature which prevents both gate driver outputs from being in the high state at the same time in the event both inputs are high. This will prevent cross conduction of the power MOSFETs in the case of unexpected disturbance or noise on the driver inputs. The UCC27282 operates over a wide temperature range from  $-40^{\circ}$ C to  $+140^{\circ}$ C and is offered in a small 3 x 3 QFN package.

#### 2.3.2 CSD19531

8

The CSD19531 is a 100-V N-Channel NexFET<sup>TM</sup> designed to minimize loss in power conversion applications. The  $R_{DS(on)}$  is rated at 6.0 m $\Omega$  and 5.3 m $\Omega$  at  $V_{GS}$  of 6V and 10 V. The  $Q_G$  is only 37 nC at 10 V  $V_{GS}$  resulting in low gate drive loss.

The CSD19531 5-mm x 6-mm SON package has very low thermal resistance and is a common package size. The CSD19531 is also avalanche rated to improve the robustness of the power converter design.

The CSD19531 is well suited for power conversion applications including primary side telecom, secondary side synchronous rectification, and motor drive.

## 3 Hardware, Software, Testing Requirements, and Test Results

#### 3.1 Required Hardware

- DC voltage source: Capable of supplying the input of the board up to 100 V is desired; capable of supplying 10 A and supports current limiting

- DC bias source: Capable of 6-V to 18-V output at up to 0.3 A

- Oscilloscope: Capable of at least a 500-MHz operation, using oscilloscope probes with a "pigtail" spring ground clip instead of the standard alligator clip

- DC multimeters: Capable of 100-V measurement, suitable for determining operation and efficiency (if desired)

- DC load: Capable of 100-V operation at up to 10 A in constant current-mode operation

- Function generator

- Dual synchronous output for independent mode; capable of at least 0-V to 3-V signal.

- (Optional) Power meter: Capable of 100-V operation at up to 8 A

# 3.2 Testing and Results

#### 3.2.1 Test Setup

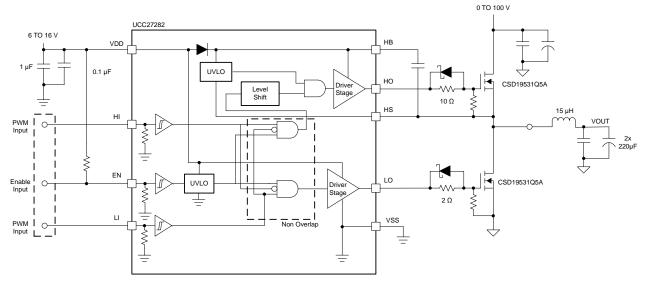

Connect the input and bias supplies and DC electronic load as shown in  $\boxed{8}$  6.

#### 图 6. TIDA-050022 Top View

To obtain the best performance of this board:

- Thermal: The parts used on this board are small with limited heatsink copper. If the dissipation exceeds 4 W, actively cool the board (as it has no heat-sink) using a fan or a similar device.

- Voltage spikes: As the test is running, whenever increasing the voltage and the current, it is important to monitor the voltage on the switched node to ensure the peak voltage does not exceed the 100-V rating of the CSD19531 FETs as this could damage the components.

• Additional capacitance on switched nodes: Typically, the method to observe the voltage at the highside gate and the switched node is using a voltage probe. These probes come with several tens of pF of capacitance, which given the frequency can negatively impact efficiency. For precise efficiency measurements, remove all probes connected to switching nodes.

#### 3.2.2 Test Results

#### 3.2.2.1 Losses and Efficiency

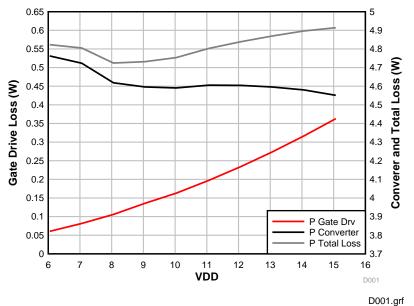

The TIDA-050022 power stage is tested in a synchronous-buck configuration to illustrate optimization of converter, gate drive and total losses.  $\boxtimes$  7 shows the tested configuration of the synchronous-buck converter operating under the following conditions:  $V_{IN} = 48$  V,  $f_{SW} = 200$  kHz and 300 kHz,  $I_{OUT} = 4$  A(DC), LI/HI deadtime = 50 ns, 50 percent duty cycle.

#### 图 7. TIDA-05022 Test Configuration

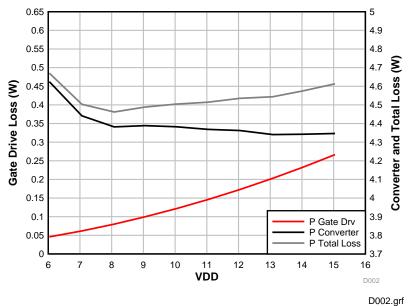

The synchronous-buck test circuit with CSD19531 MOSFETs loss data with an output power of 96 W and  $f_{SW}$  of 200 kHz is shown in 🔀 8. You can see that the gate drive power dissipation increases with  $V_{DD}$  as expected. The power converter losses are higher at 6 V and 7 V and are relatively stable from 8 V and higher. The combined gate drive and converter losses are minimum at 8 V  $V_{DD}$ .

#### 图 8. Gate Drive, Converter, and Total Loss: CSD19531 MOSFETs, and f<sub>sw</sub> 200 kHz

In 2, the CSD19531 MOSFET parameters are compared to the CSD19533. Although the CSD19531 has lower R<sub>DS(on)</sub>, the gate charge is higher and the body diode t<sub>RR</sub> is longer than the CSD19533. Since the synchronous-buck test circuit will have continuous current operation and some body diode conduction, the body diode recovery time is an important consideration in this case. The synchronous-buck test data with the CSD19533 MOSFETs operating at 200 kHz is shown in [8] 9. You can see that the minimum total losses are still with V<sub>DD</sub> = 8V and the converter and total losses are lower.

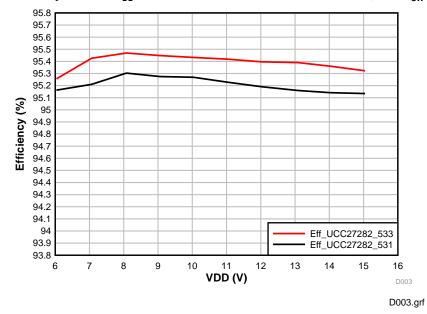

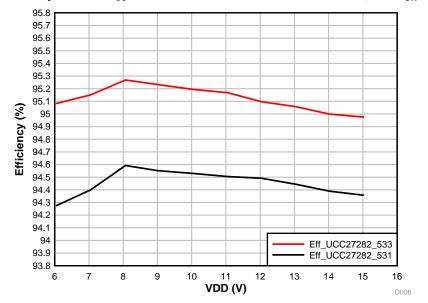

In  $\boxtimes$  10 the efficiency versus V<sub>DD</sub> accounting for all losses is shown for the CSD19531 and CSD19533 MOSFETs. The CSD19533 efficiency is slightly higher in this test condition.

图 9. Gate Drive, Converter and Total Loss: CSD19533 MOSFETs, and f<sub>sw</sub> 200 kHz

图 10. Efficiency versus V<sub>DD</sub>: CSD19531 and CSD19533 MOSFETs, and f<sub>sw</sub> 200 kHz

The converter was also tested at a switching frequency of 300 kHz to confirm if the optimum gate drive voltage follows the same trend.

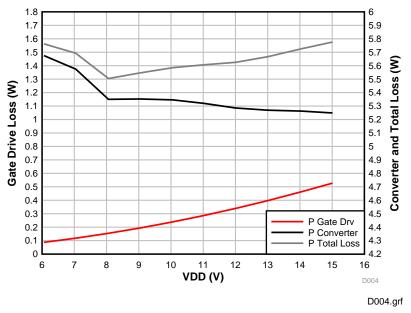

The synchronous-buck test circuit with CSD19531 MOSFETs loss data with an output power of 96 W and  $f_{SW}$  of 300 kHz is shown in 🔄 11. As before, the gate drive power dissipation increases with  $V_{DD}$  as expected. The power converter losses show the same trend and are higher at 6 V and 7 V and are relatively stable from 8 V and higher. The combined gate drive and converter losses are minimum at 8 V  $V_{DD}$ . Note that the overall losses are higher and the scale has increased.

图 11. Gate Drive, Converter, and Total Loss: CSD19531 MOSFETs, and f<sub>sw</sub> 300 kHz

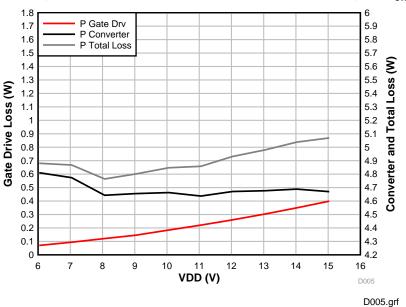

With higher operating frequency the body diode recovery time will likely have more impact on the efficiency in the synchronous-buck converter. The synchronous-buck test data with the CSD19533 MOSFETs operating at 300 kHz in shown in  $\bigotimes$  12. You can see that the minimum total losses are still with V<sub>DD</sub> = 8V and the losses are considerably lower.

In  $\boxtimes$  13, the efficiency versus V<sub>DD</sub> accounting for all losses is shown for the CSD19531 and CSD19533 MOSFETs operating at 300 kHz. The CSD19533 efficiency is noticeably higher in this test condition.

# B 12. Gate Drive, Converter and Total Loss: CSD19533 MOSFETs, and $f_{sw}$ 300 kHz

# $\boxtimes$ 13. Efficiency Versus $V_{\text{DD}}$ : CSD19531 and CSD19533 MOSFETs, and $f_{\text{sw}}$ 300 kHz

#### 3.2.2.2 Switching Waveforms

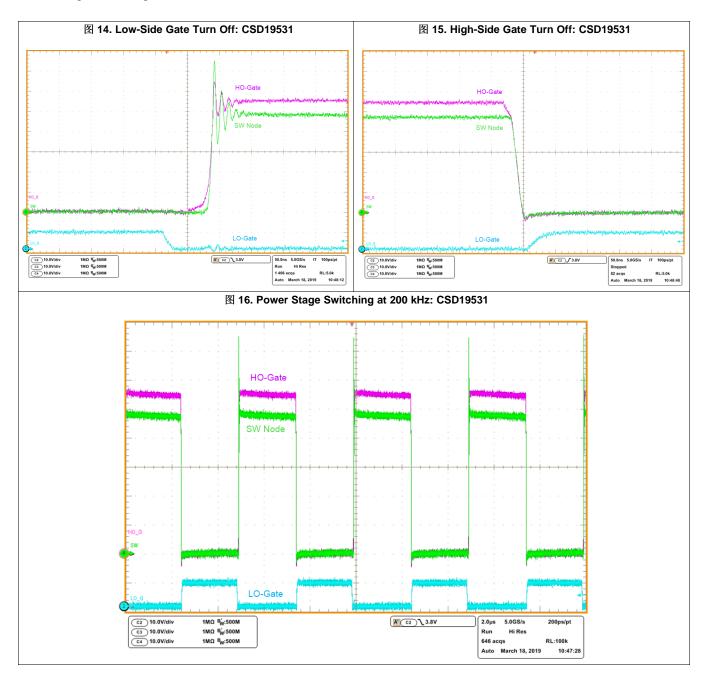

图 14 and 图 15 show the CDS19531 low- and high-side gate turn off waveforms. 图 16 shows the power stage switching at 200 kHz.

#### 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-050022.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-050022.

#### 4.3 PCB Layout Recommendations

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-050022.

#### 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-050022.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-050022.

#### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-050022.

#### 5 Related Documentation

- 1. Texas Instruments, Using the UCC27282EVM-335 User's Guide

- 2. Texas Instruments, UCC27282 120-V Half-Bridge Driver with Cross Conduction Protection and Low Switching Loss Data Sheet

- 3. Texas Instruments, CSD19531Q5A 100 V N-Channel Nex FET<sup>™</sup> Power MOSFETs Data Sheet

#### 5.1 商标

E2E, NexFET are trademarks of Texas Instruments.

修订历史记录

#### www.ti.com.cn

Page

# 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Changes from Original (May 2019) to A Revision |  | Page |  |

|------------------------------------------------|--|------|--|

| <br>• 己更改 link                                 |  | 17   |  |

已更改 link ..... 17 已更改 link ...... 17 .

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司