# 使用独立 ADC 的高精度分相 CT 电量计参考设计

# 说明

此参考设计使用高性能、多通道模数转换器 (ADC) 实现 0.1 级分相电能测量。该独立 ADC 对电流互感器 (CT) 在 8kHz 时的输出进行取样,以测量主交流电源各分支的电流和电压。该参考设计在宽输入电流范围下

(0.05–100 安培)能达到很高的精度,在必要时还支持高采样频率,以实现独立谐波分析等高级电能质量 功能。与集成 SoC 和应用特定的专用产品相比,通过使用独立 ADC 对 CT 输出进行采样,可以让设计人员更加灵活地选择计量微控制器。该参考设计使用SimpleLink™ ARM® Cortex®-M4 主机微控制器来计算电能计量参数。

### 资源

| TIDA-010037 | 设计文件夹 |

|-------------|-------|

| ADS131M04   | 产品文件夹 |

| MSP432P4111 | 产品文件夹 |

| TPS3840     | 产品文件夹 |

| TPS25921I   | 产品文件夹 |

| THVD1500    | 产品文件夹 |

| ISO7731B    | 产品文件夹 |

| TRS3232E    | 产品文件夹 |

咨询我们的 E2E™ 专家

# 特性

- 电量计分相计量,符合 10000:1 输入范围的 ANSI C12.20 0.1 类有功电能精度要求

- 有功和无功电能和功率、均方根 (RMS) 电流和电压、功率因数以及线路频率计算

- 具有 5kV<sub>RMS</sub> 隔离的隔离式 RS-232 和 RS-485

- 具有电流限制及过压和欠压保护的通信模块扩展

- 在 50mA 至 100A 输入范围内进行了测试

# 应用

- 电表

- 电能质量监测仪

- 电能质量分析仪

System Description www.ti.com.cn

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

# 1 System Description

### 1.1 End Equipment

### 1.1.1 Electricity Meter

An increase in utility providers' desired functionality for an electricity meter has driven a need for more features from electricity meters. Advanced features, such as harmonic analysis, are increasingly being required from meters. To meet these requirements, the processing and accuracy requirements often also have to evolve. As an example, adding harmonic analysis capabilities to an electricity meter may require an increase in the sample rate of the meter to capture the desired frequency range. The increase in sample frequency many times has to be done without compromising on accuracy or even while simultaneously increasing accuracy. The high sample rate, in turn, also requires more processing.

As the accuracy and amount of processing expected from electricity meters increases, it becomes more difficult to find a metrology SoC that fulfills both the processing and accuracy requirements of an electricity meter. To address this limitation, a standalone ADC can be used with a host microcontroller (MCU) to simultaneously overcome the processing and accuracy limitations of electricity meter SoCs. Using an accurate standalone ADC typically has the following advantages:

- It enables meeting the most stringent of accuracy requirements

- It enables meeting minimum sample rate requirements(without compromising on accuracy) that may not be obtainable with applications specific products or metrology SoCs

- It enables flexibility in selecting the host microcontroller since you are not limited to selecting host

microcontrollers that have accurate ADCs. The host microcontroller can be selected solely based on

application requirements, such as processing capability, minimum RAM and Flash storage for logging

energy usage, and microcontroller security features for ensuring meter data security.

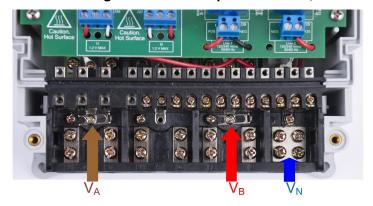

To properly sense energy consumption, voltage and current sensors translate mains voltage and current to a voltage range that an ADC can sense. To sense the energy consumption when a split-phase distribution system is used, it is necessary for the current sensors to be isolated so they can properly sense the current drawn from the two different lines without damaging the ADC. As a result, current transformers, which inherently have isolation, have historically been used for the current sensors for split-phase, two-phase, and three-phase electricity meters.

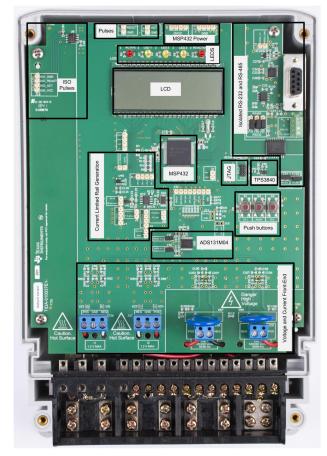

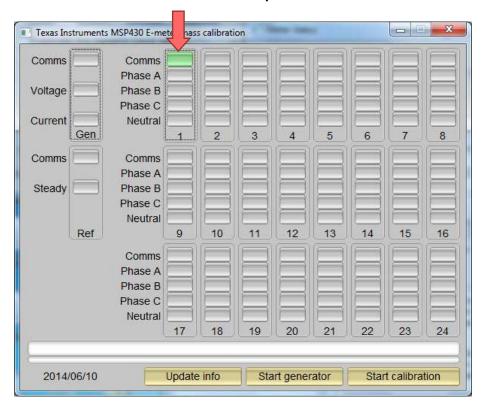

In this reference design, Class 0.1 split-phase CT-based energy measurement is implemented by using a standalone ADC device. The standalone ADC senses the Mains voltage and current. When there are new ADC samples available, the host MCU communicates to the standalone ADC via SPI to get the new samples. The host microcontroller uses the new ADC samples from the standalone ADC to calculate metrology parameters. In addition to calculating the metrology parameters, the host MCU also drives the liquid crystal display (LCD) of the board and communicates to a PC GUI through either the isolated RS-232 circuitry or isolated RS-485 circuitry on the board. As an additional safeguard, an external SVS device is added to the design to reset the host MCU when the supplied voltage to power the host MCU is not sufficient. In general, using an external SVS provides more security than the internal SVS on a host microcontroller.

www.ti.com.cn System Description

In this design, the test software specifically supports calculation of various metrology parameters for splitphase energy measurement. These parameters can be viewed either from the calibration GUI or LCD. The key parameters calculated during energy measurements are:

- Active, reactive, apparent power and energy

- RMS current and voltage

- Power factor

- Line frequency

The design also enables adding external radio or radio modules for communication. The rail for these external radio modules is current limited in this design to prevent any shorting issues with the communication modules from affecting the metrology.

### 1.1.2 Power Quality Meter, Power Quality Analyzer

In addition to being used for electricity meters, this standalone ADC architecture can be used for power quality analyzers and power quality meters. Power quality meters and power quality analyzers are used to help utilities and industrial enterprises monitor and control power quality by measuring certain power quality parameters, such as voltage harmonics, current harmonics, supply voltage dips, supply voltage swells, and other parameters as well. For these end equipment, a lot of computation is required for calculating the power quality parameters. Also, accuracy is important to be able to meet the accuracy requirements for the different power quality parameters. The requirement for high accuracy and computation power is something well supported by having a standalone ADC and separate host MCU or processor, as is done in this design.

A couple of the parameters commonly measured by power quality meters and power quality analyzers are voltage and current harmonics. For the most accurate harmonic calculations, coherent sampling should be implemented. One way of implementing coherent sampling is to vary the sampling clock based on the Mains frequency. The standalone ADC in this design has the ability to take in a varying clock so it can support coherent sampling. It should be noted that although the clock to the standalone ADC in this design can be varied, this design cannot support coherent sampling because the sampling clock cannot be varied with the proper resolution; however, this feature can be added in a future design since the standalone ADC can have its clock varied.

# 1.2 Key System Specifications

### 表 1. Key System Specifications

| FEATURES                                         | DESCRIPTION                                                                                    |

|--------------------------------------------------|------------------------------------------------------------------------------------------------|

| Number of phases                                 | 1 (split-phase with two voltages measured), 1 (split-phase with one voltage measured), 2 phase |

| Electricity meter accuracy class                 | Class 0.1                                                                                      |

| Current sensor                                   | Current transformer                                                                            |

| Tested current range                             | 0.05–100 A                                                                                     |

| Tested voltage range                             | 15 V-240 V                                                                                     |

| ADS131M04 CLKIN frequency                        | 8,192,000 Hz                                                                                   |

| ADS131M04 Delta-sigma modulation clock frequency | 4,096,000 Hz (= CLKIN / 2)                                                                     |

| SPI Clock                                        | 8,192,000 Hz                                                                                   |

| Oversampling ratio (OSR)                         | 512                                                                                            |

| Digital filter output sample rate                | 8,000 samples per second                                                                       |

System Description www.ti.com.cn

# 表 1. Key System Specifications (continued)

| FEATURES                            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Phase compensation implementation   | Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Phase compensation resolution       | 0.0088° at 50 Hz or 0.0105° at 60 Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Selected CPU clock frequency        | 48 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MCU External SVS voltage            | 2.0–2.1 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| System nominal frequency            | 50 or 60 Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Measured parameters                 | <ul> <li>Active, reactive, apparent power and energy</li> <li>Root mean square (RMS) current and voltage</li> <li>Power factor</li> <li>Line frequency</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Update rate for measured parameters | Approximately equal to 1 second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Communication options               | LCD     PC GUI via 5 kV <sub>RMS</sub> isolated RS-232 or isolated RS-485     External radio, or radio module connected to the Comms header     - 5-V rail, current limited to 1.6 A with manual reset after overcurrent thermal shutdown event     - Measured power failure detection threshold (VIN Falling) for 5-V rail = 4.05 V     - Measured release UVLO (VIN Rising) for 5-V rail = 4.28 V     - Measured release overvoltage condition(VIN Falling) for 5-V rail = 5.62 V     - Measured overvoltage cutoff threshold(VIN Rising) for 5-V rail = 5.81 V     - Custom software must be written for communication) |

| Utilized LEDs                       | Total active energy and total reactive energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Board power supply                  | Option 1: 3.3 V directly to DVCC rail; Option 2: 5V to J4 header                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# 2 System Overview

# 2.1 Block Diagram

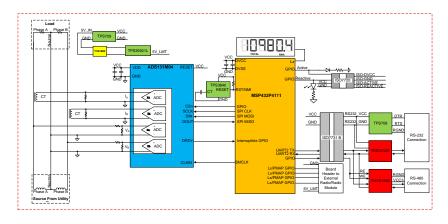

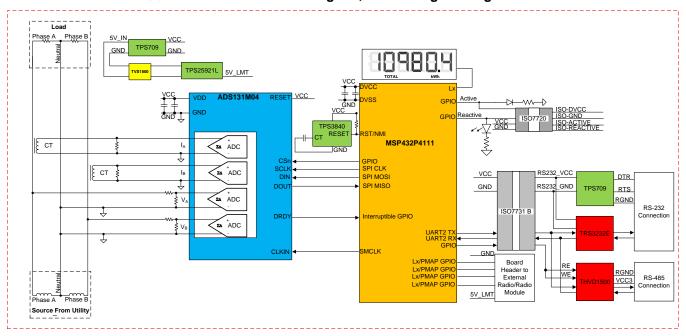

### 图 1. TIDA-010037 Block Diagram, Two-Voltage Configuration

### 图 2. TIDA-010037 Block Diagram, One-Voltage Configuration

In the diagrams, a current sensor connects to the current channels and a simple voltage divider is used for the corresponding voltage. The CT has an associated burden resistor that must be connected at all times to protect the measuring device. The selection of the CT and the burden resistor is made based on the manufacturer and current range required for energy measurements.

The choice of voltage divider resistors for the voltage channel is selected to ensure the mains voltage is divided down to adhere to the normal input ranges of the ADS131M04 device. Since the ADS131M04 ADCs have a large dynamic range and a large dynamic range is not needed to measure voltage, the voltage front-end circuitry is purposely selected so that the maximum voltage seen at the inputs of the voltage channel ADCs are only a fraction of the full-scale voltage. By reducing the voltage fed to the ADS131M04 voltage ADC, voltage to current crosstalk, which actually affects metrology accuracy more than voltage ADC accuracy, is reduced at the cost of voltage accuracy, thereby resulting in more accurate energy measurements at lower currents.

In this design, the ADS131M04 device interacts with the MSP432™ MCU in the following manner:

- The CLKIN clock used by the ADS131M04 device is provided from the SMCLK clock signal output of the MSP432 MCU.

- 2. The ADS131M04 device divides the clock provided on its CLKIN pin by two and uses this divided clock as its delta-sigma modulation clock.

- 3. When new ADC samples are ready, the ADS131M04 device asserts its DRDY pin, which alerts the MSP432 MCU that new samples are available.

- 4. After being alerted of new samples, the MSP432 MCU uses one of its SPI interfaces and its DMA to get the voltage and current samples from the ADS131M04 device.

In this design, a TPS3840 device is used as an external SVS for the MSP432 MCU. Although the MSP432 MCU has an internal SVS that suffices for this application, the TPS3840 standalone SVS is used because there is additional security in having a SVS that is independent of the MCU.

Other signals of interest in 2 1 and 2 2 are the active and reactive energy pulses used for accuracy measurement and calibration. The ISO7720 device provides an isolated connection for these pulses for connecting to non-isolated equipment. This is especially needed for the one-voltage configuration since the system is referenced with respect to one of the two high-voltage line voltages for this configuration.

In addition to isolated pulses, the design supports isolated RS-232 communication through the use of the TPS70933, ISO7731B, and TRS3232E devices. The design can be configured to use RS-485 as well instead of RS-232 through the use of the ISO7731B and THVD1500 devices on the board.

The design also supports communication using external radios or radio modules that are connected to the J11 and J12 headers of the board. The J11 header connects the P7.0, P7.1, P7.2, and P7.3 port pins, which can be configured as port mappable GPIO pins, if the LCD is disabled. Software can be added to the MSP432 MCU to communicate to an external radio or radio module by configuring any of these four pins as communication pins(SPI or UART) and appropriately writing and reading packets to and from them. The J12 header is the power rail and GND connection to the radio. The power rail on J12 is the current-limited version of the 5V\_IN rail at J4. The J12 power rail is specifically current limited to 1.6 A by the TPS25921L device. If there is a short on the radio module or the current exceeds 1.6 A for some reason, the power to this rail will be limited to prevent the power supply from affecting the power to the metrology-relevant portions of this board. If it is a transient overcurrent event, the module continues to receive power and operate without interruption. However, if there is a persistent fault on the module, the

TPS25921L device will enter thermal shutdown and power is disconnected. After this thermal shutdown event, the power can only be reconnected to the radio module manually by driving the P5.2 GPIO pin. In addition, if the voltage fed to the 5V\_IN rail at J4 is below approximately 4.0 V or above 5.8 V, the TPS25921L device is configured to disconnect the power rail on J12. To protect the TPS25921L device from any transients due to switching, a TVS1800 transient protection device is connected to this device.

The design can be powered either by applying 3.3 V at the DVCC header(J9) directly or through the TPS70933 device by applying 5 V at the 5V\_IN header(J4). See 表 2 for more details on the proper jumper connections for powering the board for both options.

# 2.2 Highlighted Products

### 2.2.1 ADS131M04

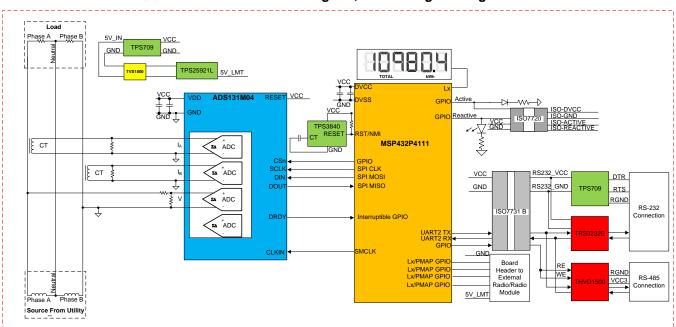

The ADS131M04 device is a four-channel, simultaneously-sampling, 24-bit, 2nd order delta-sigma ( $\Delta\Sigma$ ), analog-to-digital converter (ADC) that offers wide dynamic range, and internal calibration features making it well-suited for energy metering, power quality, and protection applications. The ADC inputs can be directly interfaced to a resistor-divider network, a transformer to measure voltage or current, or a Rogowski coil to measure current.

The individual ADC channels can be independently configured depending on the sensor input. A low noise, programmable gain amplifier (PGA) provides gains ranging from 1 to 128 to amplify low-level signals. Additionally, these devices integrate channel to channel phase alignment and offset and gain calibration registers to help remove signal chain errors. A low-drift, 1.2-V reference is integrated into the device reducing printed circuit board (PCB) area. Cyclic redundancy check (CRC) options can be individually enabled on the data input, data output and register map to ensure communication integrity. Shows a block diagram of this device.

### AVDD 1.2-V Reference AIN0F Gain & Offset Phase Shift & ΛΣ ADC Digital Filter Calibration AIN0N SYNC / RESET AIN1F Phase Shift & Gain & Offset ΔΣ ADC Digital Filter $\overline{\mathsf{cs}}$ AIN1N SCLK Control & DIN Serial Interface DOUT AIN2P ORDY Phase Shift & Gain & Offset ΔΣ ADC Digital Filter Calibration AIN2N Clock CLKIN AIN3F Phase Shift & Gain & Offset Generatio ΛΣ ΑΠΟ Digital Filter Calibration AIN3N AGND DGND

# 图 3. ADS131M04 Functional Block Diagram

In  $\boxtimes$  3, 2.7 V–3.6 V must be fed between AVDD and AGND as well as between DVDD and GND. In addition, an external clock must be connected to CLKIN. When the ADS131M04 device is configured for high-resolution mode, this clock must be between 1 MHz and 8.3 MHz for the ADS131M04 to properly work. The CLKIN clock of the ADS131M04 device can be generated from the SMCLK clock output of the MSP432 MCU. The ADS131M04 divides this clock by two and uses this divided clock for its delta-sigma modulator clock. When new ADC samples are ready, the ADS131M04 asserts its  $\overline{DRDY}$  pin to alert the host MCU that there are new ADC samples that are available. Since the ADS131M04 device can accept a clock with a wide frequency range, the device itself can also be used for applications that require coherent sampling.

### 2.2.2 MSP432P4111

The SimpleLink™ MSP432P4111 MCUs are optimized MCUs that deliver ultra-low-power performance with FPU and DSP extensions. This device has an Arm® 32-bit Cortex®-M4F CPU with Floating-Point Unit and Memory Protection Unit, a real-time clock, LCD driver, port mappable GPIOs, an AES encryption and decryption accelerator, and multiple serial communication options. The MSP432P4111 device is part of the SimpleLink MCU platform, which consists of Wi-Fi®, *Bluetooth*® low energy, Sub-1 GHz, and host MCUs. All of these devices share a common, easy-to-use development environment with a single-core software development kit (SDK) and rich tool set.

The MSP432 MCU in this design retrieves voltage and current samples from the ADS131M04 device and calculates metrology parameters. In addition, the device also keeps track of time with its RTC module, drives the LCD on the board with its internal LCD driver module, and uses one of its UART interfaces to communicate to a PC GUI using either the isolated RS-232 or isolated RS-485 circuit of the board. The CRC module of the MSP432 MCU is also used to accelerate the CRC calculations that are done to verify the integrity of the ADC packet sent by the ADS131M04 device.

### 2.2.3 TPS3840

The TPS3840 family of voltage supervisors or reset ICs can operate at high voltage levels while maintaining very low quiescent current across the whole VDD and temperature range. The TPS3840 device offers best combination of low power consumption, high accuracy and low propagation delay.

The reset output signal of the device is asserted when the voltage at VDD drops below the negative voltage threshold ( $V_{IT}$ .) or when manual reset is pulled to a low logic ( $V_{MR}$ \_L). The reset signal is cleared when VDD rises above  $V_{IT}$  plus hysteresis ( $V_{IT+}$ ) and manual reset ( $\overline{MR}$ ) is floating or above  $V_{\overline{MR}}$  and the reset time delay ( $t_D$ ) expires. Reset time delay can be programmed by connecting a capacitor to ground in the CT pin, for a fast reset CT pin can be left floating. Additional features include low power on reset voltage ( $V_{POR}$ ), built in glitch immunity protection for  $\overline{MR}$  and VDD, build in hysteresis and low open drain output leakage current ( $I_{LKG(OD)}$ ).

For electricity meters, some manufacturers prefer to have external SVS devices to reset any microcontrollers in the system, even if the microcontrollers already have an internal SVS. External SVS devices are sometimes preferred over using the SVS within a microcontroller because the external option can be more secure than the internal option, since the external devices function independently of the microcontroller. Although the SVS of the MSP432 MCU suffices for this application, the TPS3840 external SVS device is added to this design for an additional level of security. External SVS devices may sometimes also be used for early detection of a Mains blackout condition by monitoring one of the rails of an AC/DC powered from Mains.

In this design, the TPS3840DL20 variant is specifically used, which has a 2-V threshold and an open drain, active low output.

### 2.2.4 TPS25921L

The TPS25921 device is a compact, feature-rich eFuse with a full suite of protection functions. The wide operating voltage allows control of many popular DC buses. The precise ±2% current limit, at room temperature, provides excellent accuracy making the TPS25921 device well-suited for many system protection applications. It provides robust protection for all systems and applications powered from 4.5 V to 18 V. For hot-plug-in boards, the device provides in-rush current control and programmable output ramp-rate.

The TPS25921 device integrates overcurrent and short-circuit protection. The precision overcurrent limit helps to minimize over design of the input power supply, while the fast response short circuit protection immediately isolates the load from input when a short circuit is detected. The device allows the user to program the overcurrent limit threshold between 0.4 A and 1.6 A via an external resistor.

The device provides precise monitoring of voltage bus for brown-out and overvoltage conditions and asserts fault for downstream system. Its threshold accuracy of 3% ensures tight supervision of bus, eliminating the need for a separate supply voltage supervisor chip. The TPS25921 device is designed to protect systems such as White Goods, STBs, DTVs, Smart Meters, and Gas Analyzers.

Additional features of the device include:

- Overtemperature protection to safely shutdown in the event of an overcurrent event

- Fault reporting for brown-out and overvoltage faults

- · A choice of latched or automatic restart mode

For electricity meters, many manufacturers are using wireless communication to transmit data. These wireless modules may require from hundreds of milliamps to a couple of Amps to operate during the signal emission. If there is a malfunction that causes the current drawn from the module to exceed the current allotted for the wireless module, the power supply could fail, which could affect the metrology side of the meter if it shares the same power supply source as the wireless module without some type of current limiting. To ensure that the metrology is working properly and accurately at any moment, it is important to have a way to control this current spike. The TPS25921 device resolves this issue by limiting the current provided to the wireless communication module.

In this design, the latched version (TPS25921L) of this part is used, which enable the system to choose when the eFuse is reset after a thermal shutdown event. When an overcurrent situation triggers the thermal shutdown event of the TPS25921L device, the current is limited by quickly opening it and triggering the FLT signal. This FLT signal is fed to the MSP432 MCU to let it know that an event happened. After a thermal shutdown event, the MSP432 MCU can pull the ENUV pin low to reset the device and start powering the wireless module again , assuming that the overcurrent condition is no longer present.

### 2.2.5 THVD1500

The THVD1500 device is a robust half-duplex RS-485 transceiver for industrial applications. The bus pins are immune to high levels of IEC Contact Discharge ESD events eliminating the need of additional system-level protection components.

The device operates from a single 5-V supply. The wide common-mode voltage range and low input leakage on bus pins make THVD1500 suitable for multi-point applications over long cable runs.

The THVD1500 device is available in industry standard 8-pin SOIC package for drop-in compatibility. The device is characterized from –40°C to 125°C. The device also meets or exceeds the requirements of the TIA/EIA-485A Standard and the State Grid Corporation of China (SGCC) Part 11 Serial Communication Protocol RS-485 Standard.

This device is specifically used in this design to convert from UART to RS-485 signals.

### 2.2.6 ISO7731B

To add isolation to the RS-232 and RS-485 connection to a PC, the isolated RS-232 and isolated RS-485 portion of this reference design uses capacitive galvanic isolation, which has an inherent life span advantage over an opto-isolator. In particular, industrial devices are usually pressed into service for much longer periods of time than consumer electronics; therefore, maintenance of effective isolation over a period of 15 years or longer is important.

The variant of the ISO7731B device used in the RS-232 and RS-485 circuitry of this reference design provides galvanic isolation up to 5  $kV_{RMS}$  for one minute per UL. This digital isolator has three isolated channels where two channels are forward channels and the other is a reverse channel. In this design, two isolation channels are used for the TX and RX. If RS-485 is selected for communication, the third isolation channel is used for the control signal used to enable the receiver or driver. If RS-232 is selected, the third

isolation channel is not needed. If RS-232 is desired in a customer's system instead of RS-485, only two isolation channels are needed, so a two-channel ISO7721B device could be used to reduce cost instead of using the three-channel ISO7731B device (keep in mind that these two devices are not pin-to-pin compatible). Each isolation channel has a logic input and output buffer separated by a double capacitive silicon dioxide (SiO2) insulation barrier. This chip supports a signaling rate of 100 Mbps. The chips can operate from a 2.5 V, 3.3-V, and 5-V supply and logic levels.

### 2.2.7 TRS3232E

To properly interface with the RS-232 standard, a voltage translation system is required to convert between the 3.3-V domain on the board and from the 12 V on the port itself. To facilitate the translation, the design uses a TRS3232E device. The TRS3232E device is capable of driving the higher voltage signals on the RS-232 port from only the 3.3-V DVCC through a charge pump system.

The TRS3232E device consists of two line drivers, two line receivers, and a dual charge-pump circuit with ±15-kV electrostatic discharge (ESD) protection pin-to-pin (serial-port connection pins, including GND). The device meets the requirements of the Telecommunications Industry Association and Electronic Industries Alliance TIA/EIA-232-F and provides the electrical interface between an asynchronous communication controller and the serial-port connector. The charge pump and four small external capacitors allow operation from a single 3-V to 5.5-V supply. The devices operate at data signaling rates up to 250 kbps and a maximum of 30-V/µs driver output slew rate.

# 2.2.8 TPS709

To power the data terminal equipment (DTE) side of the isolation boundary and the RS-232 charge pump, there are two choices. The interface can either implement an isolated power supply or harvest power from the RS-232 line. Integrating a power supply adds cost and complexity to the system, which is difficult to justify in low-cost sensing applications.

To implement the second option of harvesting power from the RS-232 port itself, this reference design uses the flow control lines that are ignored in most embedded applications. The RS-232 specification (when properly implemented on a host computer or adapter cable), keeps the request to send (RTS) and data terminal ready (DTR) lines high when the port is active. As long as the host has the COM port open, these two lines retain voltage on them. This voltage can vary from 5 V to 12 V, depending on the driver implementation. The 5 V to 12 V is sufficient for the use requirements in this design.

The voltage is put through a diode arrangement to block signals from entering back into the pins. The voltage charges a capacitor to store energy. The capacitor releases this energy when the barrier and charge pump pull more current than what is instantaneously allowed. The TPS70933 device is used to bring the line voltage down to a working voltage for the charge pump and isolation device.

In addition to being used in the RS-232 circuit, an additional TPS709 device is used to regulate the 5-V input voltage from the 5V\_IN rail down to the 3.3 V used to power most of the components on the board.

The TPS70933 linear regulator is an ultra-low quiescent current devices designed for power-sensitive applications. A precision band-gap and error amplifier provides 2% accuracy overtemperature. A quiescent current of only 1 µA makes these devices ideal solutions for battery-powered, always-on systems that require very little idle-state power dissipation. These devices have thermal-shutdown, current-limit, and reverse-current protections for added safety. These regulators can be put into shutdown mode by pulling the EN pin low. The shutdown current in this mode goes down to 150 nA (typical).

### 2.2.9 TVS1800

The TVS1800 device robustly shunts up to 40 A of IEC 61000-4-5 fault current to protect systems from high power transients or lightning strikes. The device offers a solution to the common industrial signal line EMC requirement to survive up to  $\pm 1$  kV IEC 61000-4-5 open circuit voltage coupled through a 42- $\Omega$  impedance. The TVS1800 device uses a unique feedback mechanism to ensure precise flat clamping during a fault, assuring system exposure below 25 V. The tight voltage regulation allows designers to confidently select system components with a lower voltage tolerance, lowering system costs and complexity without sacrificing robustness. In addition, the TVS1800 device is available in a small 2-mm  $\times$  2-mm SON footprint which is ideal for space-constrained applications, offering a 70 percent reduction in size compared to industry standard SMA and SMB packages. The extremely low device leakage and capacitance ensure a minimal effect on the protected line. To ensure robust protection over the lifetime of the product, TI tests the TVS1800 device against 5,000 repetitive surge strikes at high temperature with no shift in device performance. In this design, the TVS1800 device is placed at the input of the TPS25921L device to protect it from any transient voltages that would occur from the TPS25921L disconnecting the load during overcurrent, overvoltage, or undervoltage events.

### 2.2.10 ISO7720

The ISO772x devices are high-performance, dual-channel digital isolators with 5000 V<sub>RMS</sub> (DW package) and 3000 V<sub>RMS</sub> (D package) isolation ratings per UL 1577. These devices are also certified by VDE, TUV, CSA, and CQC. The ISO772x devices provide high electromagnetic immunity and low emissions at low power consumption, while isolating CMOS or LVCMOS digital I/Os. Each isolation channel has a logic input and output buffer separated by a silicon dioxide (SiO2) insulation barrier. The ISO7720 device has both channels in the same direction while the ISO7721 device has both channels in the opposite direction. In the event of input power or signal loss, the default output is high for devices without suffix F and low for devices with suffix F. Through innovative chip design and layout techniques, the electromagnetic compatibility of the ISO772x devices has been significantly enhanced to ease system-level ESD, EFT, surge, and emissions compliance. The ISO772x family of devices is available in 16-pin SOIC wide-body (DW) and 8-pin SOIC narrow-body (D) packages.

To test the active energy and reactive energy accuracy of a meter, pulses are output at a rate proportional to the amount of energy consumed. A reference meter can then determine the accuracy of the electricity meter by calculating the error based on these pulses and how much energy is provided to the meter. In this reference design, pulses are output through headers for the cumulative active and reactive energy consumption. Using the ISO7720 device provides an isolated version of these headers for connection to non-isolated equipment, which is especially needed when the design is configured for one-voltage operation since the design is referenced with respect to one of the high-voltage line connections. In this design, the D package of the ISO7720 device is used, which provides an isolation voltage of 3000 V<sub>RMS</sub> for these signals. These isolated active and reactive signals can be set to have either a 3.3- or 5-V maximum voltage output by applying the selected maximum voltage output between the VCC (ISO\_VCC) and GND (ISO\_GND) of the isolated side.

# 2.3 Design Considerations

### 2.3.1 Design Hardware Implementation

### 2.3.1.1 Current Limiter Circuit

For smart meters, it is often desired to limit the current to any communication radios in the system. Limiting the current of the communication devices prevents any issues, whether accidentally induced from unintended shorts or purposely induced by someone for the sake of tampering with the meter, from affecting the metrology. When the design is properly configured, the voltage rail at header J3 is current-limited so that it can be used to power an external radio or radio module while ensuring that any shorts on the radio module would not affect the metrology or any other portions of the system.

4 shows the current-limiting circuit used in this design.

# 50V 2.2uF GND DVCC C121 TPS70933DBVF GND VIN OUT R120 430k EN/UVLO FLT DNP HDVCC TVS1800DRVR ILIM D10 C125 R121 75.0k R123 150k 50V 1000pF R122 160k

σπ́D

图 4. Current Limiting Circuitry

The current-limiting functionality in this design is performed by the TPS25921L e-Fuse device, which powers the load connected to the J3 header from the source connected to the header on J4. For proper operation, use 5 V as the voltage provided by the source connected to J4. There is a TPS70933 LDO that can be used to generate the 3.3-V rail for the ADS131M04 device and MSP432 MCU from the 5 V applied at J4 so that only one input rail is necessary.

If the voltage provided to J4 is below 4.036 V (based on internal undervoltage lockout voltage) or above 5.78 V, the source at J4 will be disconnected from the load at J3. In addition, if the current drawn from the load exceeds 1.6 A, thermal shutdown is eventually triggered and the source is disconnected from the load. During an overvoltage, undervoltage, or thermal shutdown event, the FLT\_TPS25921 GPIO pin connected to the FLTb pin on the TPS2591L device is asserted low. During a thermal shutdown event, the TPS25921L device remains off until the EN\_TPS25921 GPIO pin is toggled. In the test software, the TPS25921L device is only reset after thermal shutdown by toggling the EN\_TPS25921 GPIO pin if the overcurrent condition is immediately addressed and if there were no previous overvoltage, undervoltage, or thermal shutdown events.

In 图 4, R120, R121, and R122 are selected based on the desired overvoltage thresholds. Also, R123 is selected based on the desired current limit. For details on selecting new values of R120, R121, R122, and R123 to change the overvoltage, and current limiting thresholds, see the *TPS25921x 4.5 V - 18 V eFuse with precise current limit and overvoltage protection* data sheet. In this design, the internal undervoltage lockout voltage is used for the undervoltage threshold.

### 2.3.1.2 TPS3840 SVS

The TPS3840 device is an external supply voltage supervisor (SVS) that is used to externally reset the MSP432 MCU. The TPS3840 maintains very low quiescent current, which enables this device to still be used if there is a power outage and the meter is running from a backup battery. The MSP432 MCU has an internal SVS device that can be used as well, which will suffice for this application; however, using an external SVS instead of the internal SVS of the microcontroller adds an additional layer of security since it is not independent of the microcontroller, and therefore, is less affected by any issues that affect the microcontroller itself.

In this design, the TPS3840DL20 device variant is specifically used, which has a negative-voltage threshold voltage of 2 V. When the voltage rail that powers the MSP432 MCU drops below 2 V, the TPS3840 device resets the MSP432 MCU. When the monitored voltage rises above the undervoltage threshold plus hysteresis voltage value (approximately equal to 2.1 V total) , the RESET pin of the TPS3840 is pulled back high after a user-defined reset delay time,  $t_{\text{D}}$ , elapses.  $t_{\text{D}}$  is determined based on the value of the capacitor connected to the CT pin of the TPS3840 device. In this design, a 0.33- $\mu$ F capacitor is connected to the CT pin of the TPS3840 device, which leads to a reset delay time of about 204 ms.

The TPS3840 device is available with both push-pull and open-drain outputs. The open-drain output is specifically selected for this design since a 47-k $\Omega$  pullup resistor is recommended in the JTAG circuitry of the MSP432 MCU.

### 2.3.1.3 Analog Inputs

The analog front end in this design consists of the ADS131M04 delta sigma standalone ADC. Each of the ADS131M04 converters is differential and requires that the input voltages at the pins does not exceed  $\pm 1.2 \text{ V}$  (gain = 1). To meet this input voltage specification, the current and voltage inputs must be divided down. In addition, the ADS131M04 device can sense voltages down to -1.2 V; therefore, AC signals from mains can be directly interfaced without the need for level shifters. This subsection describes the analog front end used for voltage and current channels.

# 2.3.1.3.1 Voltage Measurement Analog Front End

The nominal voltage from the mains is from 100 V–240 V so it needs to be scaled down to be sensed by an ADC. 图 5 shows the analog front end used for this voltage scaling. J28 is where the voltage is applied.

图 5. Analog Front End for Voltage Inputs

### R106 R107 R103 R105 R109 0 330k 330k 330k 1.00k B72220S0271K101 DNP R87 R108 **₹**750 C105 6800pF 100V **GND** DNPC104 R110 R104 1.00k

In the analog front end for voltage, there consists a spike protection varistor (R87), footprints for electromagnetic interference filter beads (resistor footprints R103 and R104), a voltage divider network (R105, R106, R107, and R108), and an RC low-pass filter (R109, R110, C103, C104, and C105).

At lower currents, voltage-to-current crosstalk affects active energy accuracy much more than voltage accuracy, if power offset calibration is not performed. To maximize the accuracy at these lower currents, in this design the entire ADC range is not used for voltage channels. Since the ADCs of the ADS131M04 device are high-accuracy ADCs, using the reduced ADC range for the voltage channels in this design still provides more than enough accuracy for measuring voltage. 公式 1 shows how to calculate the range of differential voltages fed to the voltage ADC channel for a given Mains voltage and selected voltage divider resistor values.

$$V_{ADC\_Swing,Voltage} = \pm V_{RMS} \times \sqrt{2} \left( \frac{R_{108}}{R_{105} + R_{106} + R_{107} + R_{108}} \right) \tag{1}$$

Based on this formula and the selected resistor values in  $\ensuremath{\mathbb{R}}$  5, for a mains voltage of 120 V (as measured between the line and neutral), the input signal to the voltage ADC has a voltage swing of ±128 mV (91 mV<sub>RMS</sub>) when using the two-voltage configuration. For the one-voltage configuration, for a mains voltage of 120 V (as measured between the line and neutral), 240 V would be input to the front-end circuit in  $\ensuremath{\mathbb{R}}$  5 since the line-to-line voltage is measured instead of the line-to-neutral voltage. The 240-V input to the front-end circuit produces a voltage swing of ±257 mV (182 mV<sub>RMS</sub>). The ±128-mV and the ±257-mV voltage ranges for the two-voltage and one-voltage configurations are both well within the ±1.2-V input voltage that can be sensed by the ADS131M04 device for the selected PGA gain value of 1 that is used for the voltage channels.

Note that the pin order of the AINxP and AINxN pins on the ADS131M04 is swapped when going from one converter to another. As an example, AIN2P is pin 7 and AIN2N is pin 8 but AIN3N is pin 9 and AIN3P is pin 10. The swapped order is why the order of the positive input voltage and negative input voltage is swapped between the J28 voltage input terminal block of Phase A and the J29 voltage input terminal block of Phase B.

# 2.3.1.3.2 Current Measurement Analog Front End

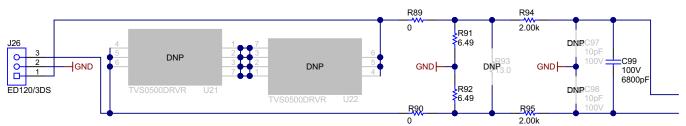

The analog front end for current inputs is different from the analog front end for the voltage inputs. **8** 6 shows the analog front end used for a current channel, where the positive and negative leads from a CT are connected to pins 1 and 3 of header J26.

# 图 6. Analog Front End for Current Inputs

The analog front end for current consists of footprints for electromagnetic interference filter beads (R89 and R90), burden resistors for current transformers (R91 and R92), and an RC low-pass filter (R94, R95, C97, C98, and C99) that functions as an anti-alias filter. There are also footprints (U21 and U22) that can be replaced with the TVS0500 for supplemental protection from surges, if required.

As  $\[mathbb{R}\]$  6 shows, resistors R91 and R92 are the burden resistors, which are in series with each other. For best THD performance, instead of using one burden resistor, two identical burden resistors in series are used with the common point being connected to GND. This split-burden resistor configuration ensures that the waveforms fed to the positive and negative terminals of the ADC are 180 degrees out of phase with each other, which would provide the best THD results with this ADC. The total burden resistance is selected based on the current range used and the turns ratio specification of the CT (this design uses CTs with a turns ratio of 2000). The total value of the burden resistor for this design is 12.98  $\Omega$ .

公式 2 shows how to calculate the range of differential voltages fed to the current ADC channel for a given maximum current, CT turns ratio, and burden resistor value.

$$V_{ADC\_Swing,Current} = \pm \frac{\sqrt{2} \left( R_{91} + R_{92} \right) I_{RMS,max}}{CT_{TURNS\_RATIO}}$$

(2)

Based on the maximum current of 100 A, CT turns ratio of 2000, and burden resistor of 12.98  $\Omega$ , of this design, the input signal to the current ADC has a voltage swing of ±918 mV maximum (649 mV<sub>RMS</sub>) when the maximum current rating of the meter (100 A) is applied. This ±918-mV maximum input voltage is well within the ±1.2-V input range of the device for the selected PGA gain of 1 that is used for the current channels.

Note that the pin order of the AINxP and AINxN pins on the ADS131M04 is swapped when going from one converter to another. As an example, AIN0P is pin 3 and AIN0N is pin 4 but AIN1N is pin 5 and AIN1P is pin 6. The swapped order is why the order of the CT positive output terminal and negative output terminal is swapped between the J26 current input terminal block of Phase A and the J27 current input terminal block of Phase B.

### 2.3.2 How to Implement Software for Metrology Testing

The MSP432 software used for evaluating this design is test software. This section discusses the features of the test software, which should provide insights on how to implement custom software for metrology testing. The first subsection discusses the setup of the ADS131M04 device and various peripherals on the MSP432 MCU. Subsequently, the metrology software is described as two major processes: the foreground process and background process.

# 2.3.2.1 Setup

### 2.3.2.1.1 Clock

The MSP432 MCU is configured to have its CPU clock (MCLK) set at 48 MHz and its subsystem master clock (SMCLK) set to 8.192 MHz. The clock source for MCLK is the internal DCO of the MSP432 MCU, which is configured for a frequency of 48 MHz. The clock source for SMCLK is an external 16.384-MHz crystal, which is internally divided by 2 to create the 8.192-MHz SMCLK frequency. An external 32.768-kHz crystal is used as the clock source for the auxiliary clock (ACLK) of the device. This ACLK clock is set to a frequency of 32.768 kHz.

### 2.3.2.1.2 Port Map

The MSP432 MCU has a port mapping controller that allows a flexible mapping of digital functions to port pins. The set of digital functions that can be ported to other pins is dependent on the device. For the MSP432 device in particular, the SPI clock, SOMI, and SIMO functionality of the EUSCIB0 SPI module are all available options to port to ports P2, P3, and P7. In addition, the SMCLK clock output is also available for output to ports P2, P3, and P7. In the test software, this port mapping feature is used for providing flexibility in the PCB layout.

Using the port mapping controller, the following mappings are used:

- PMAP\_SMCLK (SMCLK clock output) → Port P2.0 (connected to the CLKIN pin of the ADS131M04 device so that it can be used to generate the modulator clock of the ADS131M04; however, note that this mapping is not enabled initially and is only enabled after the ADS131M04 is initialized.); this is pin 1 of header J32, which is labeled SMCLK on the board

- PMAP\_UCB0SIMO (EUSCIB0 SPI SIMO) → Port P2.1 (connected to the DIN pin of the ADS131M04 device) this is pin 2 of header J32, which is labeled SPI DOUT on the board

- PMAP\_UCB0SOMI (EUSCIB0 SPI SOMI) → Port P2.2 (connected to the DOUT pin of the ADS131M04 device) this is pin 3 of header J32, which is labeled SPI DIN on the board

- PMAP\_UCB0CLK (EUSCIB0 SPI Clock) → Port P2.3 (connected to the SCK pin of the ADS131M04 device) this is pin 4 of header J32, which is labeled SPI CLK on the board

# 2.3.2.1.3 UART Setup for GUI Communication

The MSP432 MCU is configured to communicate to the PC GUI through either the RS-232 or RS-485 connection on this reference design. The MSP432 MCU communicates to the PC GUI using a UART module configured for 8N1 at 9600 baud.

# 2.3.2.1.4 Real-Time Clock (RTC)

The real-time clock module of the MSP432 MCU is configured to give precise one-second interrupts and update the time and date, as necessary.

### 2.3.2.1.5 LCD Controller

The LCD controller on the MSP432P4111 MCU can support up to 8-MUX displays and 320 segments or 4-MUX displays and 176 segment displays. In the current design, the LCD controller is configured to work in 4-MUX mode using 144 segments. The eight segment lines not used in the 4-MUX mode of this design are used for the port mapping functionality. In this reference design, the LCD is configured for a refresh rate set to ACLK / 64, which is 512 Hz. For contrast control, external resistors are added between the R23, R13, R03 pins and GND, as 87 shows.

图 7. LCD External Resistors

### 2.3.2.1.6 Direct Memory Access (DMA)

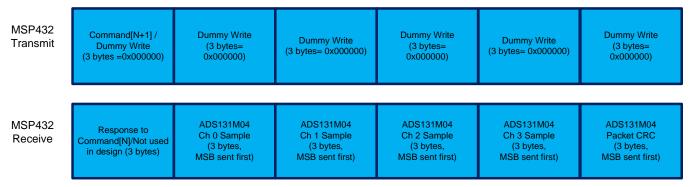

The direct memory access (DMA) module transfers packets between the MSP432 MCU and ADS131M04 device with minimal bandwidth requirements from the MSP432 CPU. Two DMA channels are used for communicating to the ADS131M04. One channel (channel 0) is used to send data to the ADS131M04 and the other channel (channel 1) is used to receive data from the ADS131M04. Once a complete packet has been received from the ADS131M04, an interrupt is generated to complete any necessary post-transfer processing, such as CRC verification and packet assembly. 图 12 shows the packets that are sent and received using the DMA of the MSP432 MCU.

### 2.3.2.1.7 ADC Setup

■ 8 shows the process used to initialize the ADS131M04. This process is followed when the ADS131M04 is being first setup after the MSP432 MCU resets as well as each time calibration is performed.

# Disable output of SMCLK to ADS131M04 CLKIN pin Disable IRQ Send ADS131M04 reset command Enable IRQ Send commands to configure ADS131M04 registers Setup port interrupt on falling edge of ADS131M04 DRDY Output SMCLK to ADS131M04 CLKIN pin to start sampling Return ADS131M04 Setup

图 8. ADC Initialization and Synchronization Process

Before setting up the ADS131M04 device, the modulator clock of the ADS131M04 is disabled to prevent the ADS131M04 from generating new samples while trying to set it up. The modulator clock is disabled by disabling the SMCLK output of the MSP432 MCU, which is fed to the CLKIN pin of the ADS131M04. Disabling the SMCLK output only needs to be done after calibration and not after an MSP432 MCU reset event since the SMCLK clock output is automatically not output after the MSP432 MCU resets.

After the SMCLK output is disabled, the EUSCIB0 SPI module of the MSP432 MCU is configured for communication to the ADS131M04 device. The EUSCIB0 SPI module is specifically configured as a master device that uses 3-wire mode (the chip select signal is manually asserted high and low in the test software instead of using the chip select feature of the SPI module) and has an 8.192-MHz SPI clock that is derived from the 8.192-MHz SMCLK clock. After the SPI is setup, all interrupts are disabled and a reset command is sent from the MSP432 MCU to the ADS131M04 via SPI. Interrupts are then re-enabled and the MSP432 MCU sends commands to the ADS131M04 to configure its registers.

At this point, note that the modulation clock is not output by the MSP432 MCU yet, which means that sampling is not started yet. By sending commands to the ADS131M04 to initialize the ADS131M04 registers, the ADS131M04 is configured for the following:

- MODE register settings: 16-bit CCITT CRC used, 24-bit length for each word in the ADS131M04 packet, DRDY signal asserted on most lagging enabled channel, DRDY asserted high when conversion value is not available, DRDY asserted low when conversion values are ready

- GAIN1 register settings: PGA gain of 1 used for all four ADC channels

- CFG register settings: Current detection mode disabled

- CHx\_CNG register settings (where x is the channel number)

Two-voltage mode: All four ADC channel inputs connected to external ADC pins and channel phase delay set to 0 for each channel (note that software phase compensation is used instead of ADS131M04 hardware phase compensation)

- One-voltage mode: Channels 0, 1, and 2 inputs connected to external ADC pins and channel phase delay set to 0 for channels 0, 1, and 2 (note that software phase compensation is used instead of ADS131M04 hardware phase compensation); the channel 3 config register is not modified since channel 3 is not used for this configuration.

- CLOCK register settings: 512 OSR, all channels enabled, and high-resolution modulator power mode

After the ADS131M04 registers are properly initialized, the MSP432 MCU is configured to generate a port interrupt whenever a falling edge occurs on the  $\overline{DRDY}$  pin, which would indicate that the ADS131M04 has new current samples that are available. Next, the MSP432 MCU outputs the SMCLK clock to the ADS131M04, which starts the voltage and current sampling.

The ADS131M04 modulator clock is derived from the clock fed to its CLKIN pin, which is output from the SMCLK output of the MSP432 MCU. The clock fed to the CLKIN pin of the ADS131M04 device is internally divided by two, to generate the ADS131M04 modulator clock. The sampling frequency of the ADS131M04 is therefore defined as  $f_{\rm s} = f_{\rm M}$  / OSR =  $f_{\rm CLKIN}$  / (2 × OSR), where  $f_{\rm s}$  is the sampling rate,  $f_{\rm M}$  is the modulator clock frequency,  $f_{\rm CLKIN}$  is the clock fed to the ADS131M04 CLKIN pin, and OSR is the selected oversampling ratio. In this design, the SMCLK clock of the MSP432 MCU that is fed to the ADS131M04 CLKIN pin has a frequency of 8.192 MHz. The oversampling ratio is selected to be 512 . As a result, the ADS131M04 modulator clock is set to 4.096 MHz and the sample rate is set to 8000 samples per second.

For a two-voltage system where each line-to-neutral voltage is measured, at least four ADC channels are necessary to independently measure two voltages and two currents. In this design, the following ADS131M04 channel mappings are used in software for the two-voltage configuration:

- AIN0P and AIN0N ADS131M04 ADC channel pins → Current I1 (Phase A Current)

- AIN1P and AIN1N ADS131M04 ADC channel pins → Current I2 (Phase B Current)

- AIN2P and AIN2N ADS131M04 ADC channel pins → Voltage V1 (Phase A Line-to-Neutral Voltage)

- AIN3P and AIN3N ADS131M04 ADC channel pins → Voltage V2 (Phase B Line-to-Neutral Voltage)

For a balanced split-phase system, each line-to-neutral voltage should be half of the line-to-line voltage. In the one-voltage configuration of this design, only the line-to-line voltage is measured. The line-to-line voltage readings are divided by two (this division is done automatically by following the calibration process) to get the line-to-neutral voltages of each phase. As a result, the same ADC samples are used in the software to calculate the RMS voltage and power for the two phases. This configuration uses three ADC channels: one to measure the line-to-line voltage and the other two for the two currents. In this design, the following ADS131M04 channel mappings are used in software for the one-voltage configuration:

- AIN0P and AIN0N ADS131M04 ADC channel pins → Current I1 (Phase A Current)

- AIN1N and AIN1P ADS131M04 ADC channel pins → Current I2 (Phase B Current)

- AIN2P and AIN2N ADS131M04 ADC channel pins → Line-to-Line Voltage (Phase A line voltage Phase B line voltage)

- AIN3P and AIN3N ADS131M04 ADC channel pins → Not used in design

Since the line-to-line voltage measured in the one-voltage configuration is the Phase A line voltage - Phase B line voltage and not the Phase B line voltage - Phase A line voltage, the orientation for phase B current should be reversed, which is done by either swapping where the positive and negative output terminals of the current transformers of Phase B are connected, swapping the polarity of the current fed to the Phase B current input in the design, or by using the same input current and CT output terminal polarity at phase A and just negating the current channel ADC channels in software. To prevent having to do any hardware changes when switching from two-voltage to one-voltage modes, this design reverses the polarity of the current channels by choosing the option where the phase B current channel values are negated in the test software.

# 2.3.2.2 Foreground Process

The foreground process includes the initial setup of the MSP432 hardware and software and the ADS131M04 registers immediately after a device RESET.

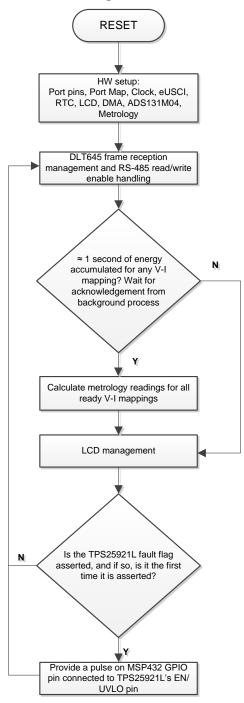

■ 9 shows the flowchart for this process.

图 9. Foreground Process

The initialization routines involve the setup of the MSP432 general purpose input/output (GPIO) port pins and associated port map controller; MSP432 clock system; MSP432 USCI\_A0 for UART functionality; MSP432 RTC module for clock functionality; MSP432 LCD; MSP432 DMA; ADS131M04 registers; and MSP432 metrology variables.

After the hardware is setup, any received frames from the GUI are processed. If RS-485 is selected for communication to the PC GUI, the THVD1500 device must have its RE and DE pins driven to enable the receiver and driver during the proper points in time to receive packets from the PC GUI and send responses back to the GUI. After any packet is sent from the MSP432 MCU to the PC GUI, the foreground process is responsible for asserting the RE and DE pins after the packet has been completely sent out from the MSP432 MCU but before the GUI sends out its next packet.

Subsequently, the foreground process checks whether the background process has notified the foreground process to calculate new metering parameters for any voltage-current mappings. This notification is accomplished through the assertion of the "PHASE\_STATUS\_NEW\_LOG" status flag whenever a frame of data is available for processing. The data frame consists of the processed dot products that were accumulated for approximately one second in the background process. This is equivalent to an accumulation of 50 or 60 cycles of data synchronized to the incoming voltage signal. In addition, a sample counter keeps track of how many samples accumulate over this frame period. This count can vary as the software synchronizes with the incoming mains frequency.

The processed dot products include the  $V_{RMS}$ ,  $I_{RMS}$ , active power, and reactive power. These dot products are used by the foreground process to calculate the corresponding metrology readings in real-world units. Processed voltage dot products, current dot products, active energy dot products, and reactive energy dot products are accumulated in separate 64-bit registers to further process and obtain the RMS and mean values. Using the calculated values of active and reactive power of the foreground process, the apparent power is calculated. The frequency (in Hz) and power factor are also calculated using parameters calculated by the background process using the formulas in  $\ddagger 2.3.2.2.1$ .

For the two-voltage configuration, there are two voltage-current mappings, where each voltage-to-current mapping has a different voltage and current channel. Specifically, in the two-voltage mapping, the line-to-neutral voltage measurement for line A and the line A current measurement are associated with each other for one mapping and the line-to-neutral voltage measurement for line B and the line B current measurement are associated with each other for the other mapping. Otherwise, for the one-voltage configuration, each voltage-current mapping has the same voltage for each mapping since only one voltage is measured. In the one-voltage configuration, the line-to-line voltage measurement is associated with the line A current for the first mapping and the same line-to-line voltage measurement is associated with the line B current for the second mapping. For simplicity, note that each voltage-to-current mapping, whether for two-voltage or one-voltage configurations, is referred to as a phase in the rest of this documentation as well as in the PC GUI.

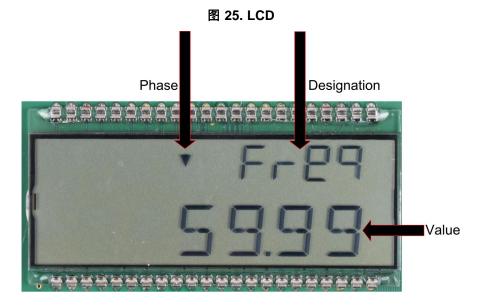

The foreground process also updates the LCD. The LCD display item is changed every two seconds. See 节 3.2.1.3.1 for more information about the different items displayed on the LCD.

In addition, the foreground process also takes action if the FLT pin of the TPS25921L device has been asserted low, which would indicate an undervoltage, overvoltage, or thermal shutdown event has occurred. If the FLT pin has been asserted low and it is the first time this has happened since the MSP432 MCU has been reset, the MSP432 MCU provides a pulse on the EN/UVLO pin of the TPS25921L device to reset the device. This reset pulse is meant to reconnect the load at the TPS25921L OUT pin with the source at its IN pin since this would be disconnected if the fault source was from a thermal shutdown event. After resetting the TPS25921L, if another thermal shutdown event occurs, the TPS25921L output is disconnected from the input again and the MSP432 MCU does not make any further attempts to provide a reset pulse to the TPS25921L to reconnect the output to the input rail.

### 2.3.2.2.1 Formulae

This section briefly describes the formulas used for the voltage, current, power, and energy calculations. As previously described, voltage and current samples are obtained at a sampling rate of 8000 Hz. All of the samples that are taken in approximately one second frames are kept and used to obtain the RMS values for voltage and current for each phase. The RMS values are obtained with the following formulas:

$$V_{RMS,ph} = K_{v,ph} \times \sqrt{\frac{\sum_{n=1}^{Sample Count} v_{ph}(n) \times v_{ph}(n)}{Sample Count} - v_{offset,ph}}}$$

$$I_{RMS,ph} = K_{i,ph} \times \sqrt{\frac{\sum_{n=1}^{Sample Count} i_{ph}(n) \times i_{ph}(n)}{Sample Count} - i_{offset,ph}}}$$

(3)

where

- ph = Phase parameters that are being calculated [that is, Phase A (= 1) or B (= 2)]

- V<sub>ph</sub>(n) = Voltage sample at a sample instant n

- V<sub>offset ph</sub> = Offset used to subtract effects of the additive white Gaussian noise from the voltage converter

- I<sub>ph</sub>(n) = Each current sample at a sample instant n

- I<sub>offset,ph</sub> = Offset used to subtract effects of the additive white Gaussian noise from the current converter

- Sample count = Number of samples within the present frame

- K<sub>v.ph</sub> = Scaling factor for voltage

- $K_{i,oh} = Scaling factor for current$  (4)

Power and energy are calculated for active and reactive energy samples of one frame. These samples are phase-corrected and passed on to the foreground process, which uses the number of samples (sample count) to calculate phase active and reactive powers through the following formulas:

$$P_{ACT,ph} = K_{ACT,ph} \frac{\sum_{n=1}^{Sample Count} v_{ph}(n) \times i_{ph}(n)}{Sample Count} - P_{ACT\_Offset,ph}$$

$$\sum_{n=1}^{Sample Count} V_{90,ph}(n) \times i_{ph}(n)$$

$$P_{REACT,ph} = K_{REACT,ph} \frac{\sum_{n=1}^{Sample Count} V_{90,ph}(n) \times i_{ph}(n)}{Sample Count} - P_{React\_Offset,ph}$$

$$P_{APP,ph} = \sqrt{P_{ACT,ph}^2 + P_{REACT,ph}^2}$$

(6)

where

- V<sub>90</sub>(n) = Voltage sample at a sample instant 'n' shifted by 90°

- K<sub>ACT.ph</sub> = Scaling factor for active power

- K<sub>REACT,ph</sub> = Scaling factor for reactive power

- P<sub>ACT\_offset,ph</sub> = Offset used to subtract effects of crosstalk on the active power measurements from other phases and the neutral

- P<sub>REACT\_offset,ph</sub> = Offset used to subtract effects of crosstalk on the reactive power measurements from other phases and the neutral (7)

Note that for reactive energy, the 90° phase shift approach is used for two reasons:

- 1. This approach allows accurate measurement of the reactive power for very small currents

- 2. This approach conforms to the measurement method specified by IEC and ANSI standards

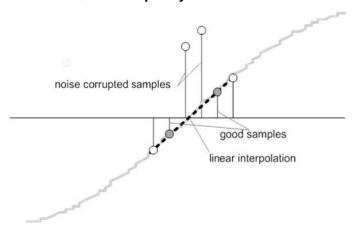

The calculated mains frequency is used to calculate the 90 degrees-shifted voltage sample. Because the frequency of the mains varies, the mains frequency is first measured accurately to phase shift the voltage samples accordingly.

To get an exact 90° phase shift, interpolation is used between two samples. For these two samples, a voltage sample slightly more than 90 degrees before the current sample and a voltage sample slightly less than 90 degrees before the current sample are used. The phase shift implementation of the application consists of an integer part and a fractional part. The integer part is realized by providing an N samples delay. The fractional part is realized by a one-tap FIR filter. In the test software, a lookup table provides the filter coefficients that are used to create the fractional delays.

In addition to calculating the per-phase active and reactive powers, the cumulative sum of these parameters are also calculated using 公式 8, 公式 9, and 公式 10:

$$P_{ACT,Cumulative} = \sum_{ph=1}^{2} P_{ACT,ph}$$

(8)

$$P_{REACT,Cumulative} = \sum_{ph=1}^{2} P_{REACT,ph}$$

(9)

$$P_{APP,Cumulative} = \sum_{ph=1}^{2} P_{APP,ph}$$

(10)

Using the calculated powers, energies are calculated with the following formulas in 公式 11:

$$E_{ACT,ph} = P_{ACT,ph} \times Sample count$$

$$E_{REACT,ph} = P_{REACT,ph} \times Sample count$$

$$E_{APP,ph} = P_{APP,ph} \times Sample count$$

(11)

From there, the energies are also accumulated to calculate the cumulative energies, by the following 公式 12, 公式 13, and 公式 14:

$$E_{ACT,Cumulative} = \sum_{ph=1}^{2} E_{ACT,ph}$$

(12)

$$E_{REACT,Cumulative} = \sum_{ph=1}^{2} E_{REACT,ph}$$

(13)

$$\mathsf{E}_{\mathsf{APP},\mathsf{Cumulative}} = \sum_{\mathsf{ph}=1}^{2} \mathsf{E}_{\mathsf{APP},\mathsf{ph}} \tag{14}$$

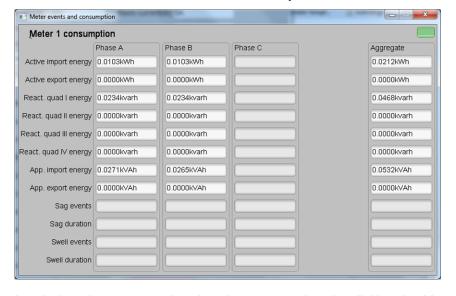

The calculated energies are then accumulated into buffers that store the total amount of energy consumed since system reset. Note that these energies are different from the working variables used to accumulate energy for outputting energy pulses. There are four sets of buffers that are available: one for each phase and one for the cumulative of the phases. Within each set of buffers, the following energies are accumulated:

- 1. Active import energy (active energy when active energy ≥ 0)

- 2. Active export energy (active energy when active energy < 0)

- 3. React. Quad I energy (reactive energy when reactive energy ≥ 0 and active power ≥ 0; inductive load)

- 4. React. Quad II energy (reactive energy when reactive energy ≥ 0 and active power < 0; capacitive generator)

- 5. React. Quad III energy (reactive energy when reactive energy < 0 and active power < 0; inductive

generator)

6. React. Quad IV energy (reactive energy when reactive energy < 0 and active power ≥ 0; capacitive load)

- 7. App. import energy (apparent energy when active energy  $\geq 0$ )

- 8. App. export energy (apparent energy when active energy < 0)

The background process also calculates the frequency in terms of samples-per-mains cycle. The foreground process then converts this samples-per-mains cycle to Hertz with 公式 15:

Frequency (Hz) =

$$\frac{\text{Sample Rate (samples / sec ond)}}{\text{Frequency (samples / cycle)}}$$

(15)

After the active power and apparent power have been calculated, the absolute value of the power factor is calculated. In the internal representation of power factor of the system, a positive power factor corresponds to a capacitive load; a negative power factor corresponds to an inductive load. The sign of the internal representation of power factor is determined by whether the current leads or lags voltage, which is determined in the background process. Therefore, the internal representation of power factor is calculated with 公式 16:

Internal Representation of Power Factor =

$$\begin{cases} \frac{P_{Act}}{P_{Apparent}}, & \text{if capacitive load} \\ \frac{P_{Act}}{P_{Apparent}}, & \text{if inductive load} \end{cases}$$

(16)

### 2.3.2.3 Background Process

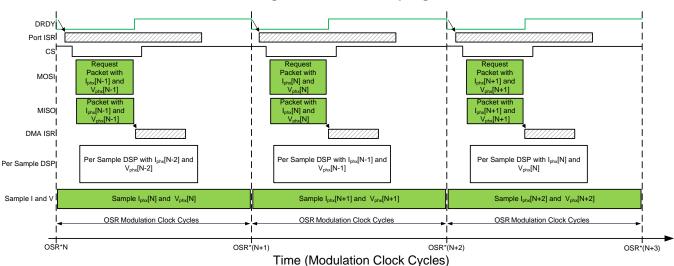

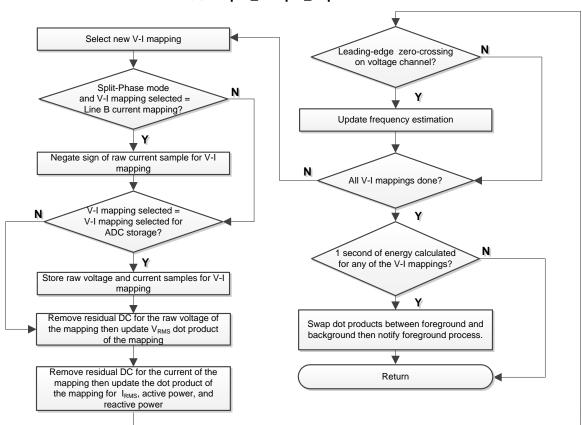

■ 10 shows the different events that occur when sampling voltage and current, where the items in olive green are done by the hardware settings and not the test software.

图 10. Voltage and Current Sampling Events

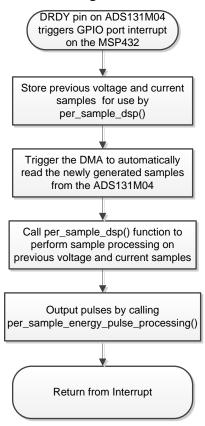

# 图 11. Background Process

In the background process, the previously-obtained voltage samples  $(V_{phx}[N-2])$  and previously obtained current samples  $(I_{phx}[N-2])$  are stored so that they can be used later by the per\_sample\_dsp function, which is responsible for updating the intermediate dot product quantities used to calculate metrology parameters. After the previously obtained voltage and current samples are stored, communication to the ADS131M04 is enabled by asserting the chip select signal low. The DMA is then configured to both send a request for the newest current and voltage samples  $(I_{phx}[N-1])$  and  $V_{phx}[N-1]$  of the ADS131M04 device and also to receive the data packet response from the ADS131M04. The request and reception of the current samples is done automatically by the DMA module instead of it being done by the software.

₹ 12 shows the packet that is transmitted by the DMA of the MSP432 MCU and the response packet from the ADS131M04 that is received and assembled by the DMA as well. The transmission and reception packets contain six words, where each word is three bytes long.

图 12. ADS131M04 ADC Sample Request Packet

When requesting the ADC data from the ADS131M04 device, the first word that has to be sent to the ADS131M04 is the command word. Since the test software does not need to change the settings of the ADS131M04 or read any registers during typical ADC sample readouts, a NULL command is sent to the ADS131M04, which allows you to get the ADC samples from the ADS131M04 without changing the state of the device. The actual size of the null command is 16-bits; however, since 24-bit words are used, the 16-bit command must be padded with an extra value of 0x00 at the end of the command. The NULL command word sent therefore has a value of 0x000000. While the MSP432 MCU is shifting out the command word, the MSP432 is simultaneously shifting in the response word to the command word of the previous packet. The response word to a NULL command is the contents of the STATUS register. The contents of the STATUS register is not used in this design so the first word received from the ADS131M04 is ignored.

After writing the command word, it is necessary for a dummy write to be performed for each byte that is to be read. The dummy byte write is necessary to enable the SPI clock, which is necessary to read a byte from the ADS131M04 device. For each dummy byte write, a value of 0x00 is written to the SPI transmit register for EUSCIB0. Immediately after writing the command byte, writing three dummy bytes allows the MSP432 MCU to receive the 3-byte ADC value from channel 0 of the ADS131M04. Writing the next nine dummy bytes gets the ADC data for channel 1, channel 2, and channel 3, respectively. Finally, writing the next three dummy bytes gets the CRC word. The CRC word is 24-bits; however, note that the actual CRC is only 16-bits, which are placed in the most significant bits of the 24-bit word. As a result, when parsing the CRC word, the last byte is not needed (note though that the dummy write for this zero-padded byte must still be sent though for proper ADS131M04 operation).

# 图 13. Code Snippet for Using the CRC Module of the MSP432 MCU for Calculating CRC Over an Odd Number of Bytes

Once the CRC has been calculated over the packet, it is compared to the CRC obtained in the packet sent from the ADS131M04. The sent CRC is parsed from bytes 16 and 17 of the ADS131M04 packet (byte 18, which is part of the CRC word, is zero-padded so it is not used in parsing). If the calculated CRC and the parsed CRC are equal, then the CRC check passes and the ADC data is parsed to get the values of the voltage and current samples at time N – 1. The parsed voltage and current samples are put in temporary buffers so that they are used the next time the per\_sample\_dsp function is called at the next interrupt. Before the DMA interrupt ends, the chip select line is pulled back high again to properly reset the ADS131M04 communication before the next time current samples are ready from the ADS131M04.

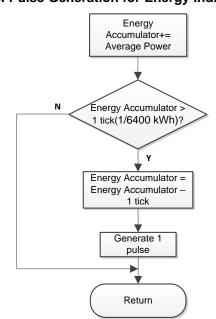

In parallel to receiving the newest current samples from the ADS131M04 using the DMA, the ADS131M04 is currently sampling the next voltage ( $V_{phx}[N]$ ) and current samples ( $I_{phx}[N]$ ) and the test software also performs per-sample processing on the last voltage ( $V_{phx}[N-2]$ ) and current samples ( $I_{phx}[N-2]$ ) obtained from the ADS131M04. This per-sample processing is used to update the intermediate dot product quantities that are used to calculate the metrology parameters. After sample processing, the background process uses the "per\_sample\_energy\_pulse\_processing" for the calculation and output of energy-proportional pulses. Once the per\_sample\_energy\_pulse\_processing is completed, the test software exits from the port ISR.

### 2.3.2.3.1 per\_sample\_dsp()

₹ 14 shows the flowchart for the per\_sample\_dsp() function. The per\_sample\_dsp() function is used to calculate intermediate dot product results that are fed into the foreground process for the calculation of metrology readings. Both voltage and current samples are processed and accumulated in dedicated 64-bit registers. Per-phase active power and reactive power are also accumulated in 64-bit registers.

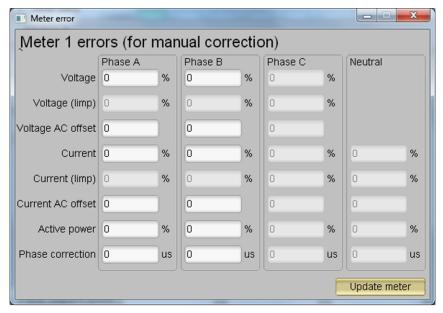

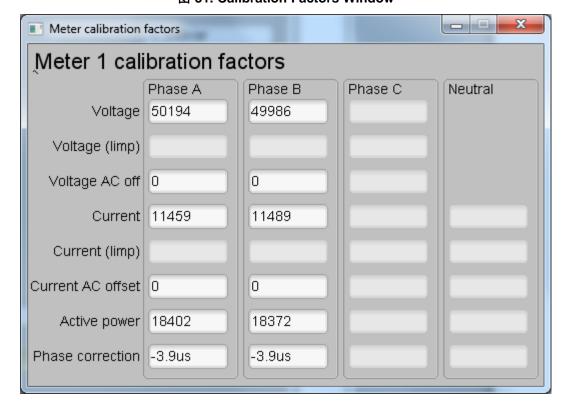

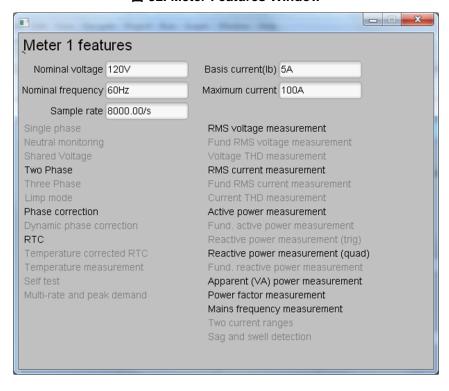

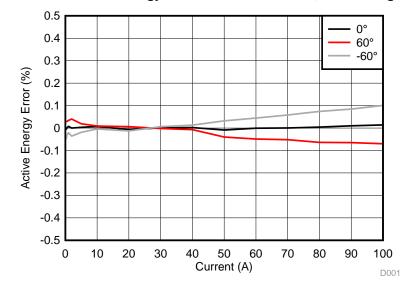

图 14. per sample dsp Function