## TI Designs: TIDA-010023

# 适用于三相逆变器的成本优化、< 1% 精确电流检测和保护参考 设计

# TEXAS INSTRUMENTS

#### 说明

此参考设计展示了一款成本优化的三相逆变器桥臂(低侧分流)电流感应解决方案,该解决方案精确度高,并 且可更快地响应无传感器的2分流或3分流磁场定向控制(FOC)。为了最大程度降低可闻噪声,驱动器需要更快的精确电流感应与优异的噪声抑制性能。此参考设计展示了充分摆幅响应趋稳时间接近1µs、准确度误差小于1%的逆变器桥臂电流感应。即使附近有高功率 IGBT 开关,此设计也可展现出优异的噪声抑制性能。 此设计通过硬件充分实现过流保护,总响应时间低于 1.5µs。该参考设计适用于压缩机电机。逆变器的功率级可在高达2kW的功率下工作。

#### 资源

| TIDA-010023   | 设计文件夹 |

|---------------|-------|

| TLV9064       | 产品文件夹 |

| UCC27712      | 产品文件夹 |

| TIDA-00947    | 设计文件夹 |

| TLV1701       | 产品文件夹 |

| SN74AHC367    | 产品文件夹 |

| TLV9001       | 产品文件夹 |

| TMS320F28027F | 产品文件夹 |

| TPD1E10B06    | 产品文件夹 |

|               |       |

#### 特性

- 低成本、精确的电流感应,适用于具有两个和三个 分流拓扑的无传感器 FOC,可最大程度减少电机驱 动器中的扭矩纹波和可闻噪声

- 电流感应的趋稳时间小于 1.25μs,校准精度低于 1%,可实现精确的电流感应

- 通过硬件全面实现过流保护,响应快速,响应时间 小于 1.5µs

- 只使用两个比较器,可在所有三个逆变器桥臂上实施正负过流保护

- 保护 功能: 电机过流和过热保护

- 三相逆变器功率级专门针对 2kW 输出功率以及

270V 至 390V 直流输入电压而设计

#### 应用

- 空调

- 洗衣机

- 冰箱

- 电器压缩机

- 电动工具

A

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

#### 1 System Description

Field-oriented control (FOC) is widely used for high-performance motor control to enable smooth rotation over the whole speed range, fast accelerations and decelerations, and efficient operation during dynamic load changes. Basic idea of FOC algorithm is to decompose the 3-phase winding current into magnetic field-generating part and torque-generating part via Clark and Park transformation.

Fast and precise motor winding current sensing is required for efficient and accurate implementation of FOC and to get the best performance from the motor. The most simplest and cost effective way of measuring the winding current is by sensing the inverter leg current using a sense resistor in the inverter legs of all the three phases. This method of current sensing is much cheaper compared to hall sensor based sensing.

The delay or slow response in current sensing can lead to incorrect current estimates and hence distorted current waveform in the motor. The motor drive applications in major appliances such as a compressor motor control in air conditioners and refrigerators require accurate torque control to have the best dynamic performance and low acoustic. An inaccurate current sensing leads to distorted current waveform in the motor winding and thus produces torque ripple, which, in turn, results in inefficient and noisy performance.

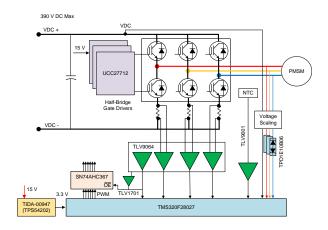

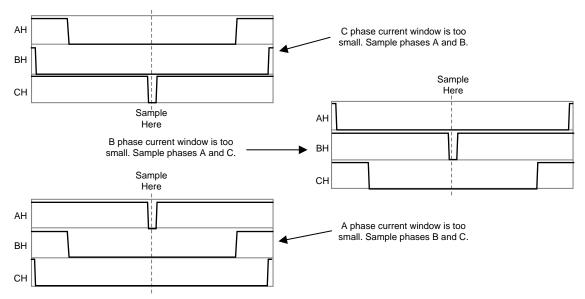

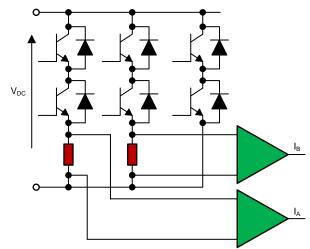

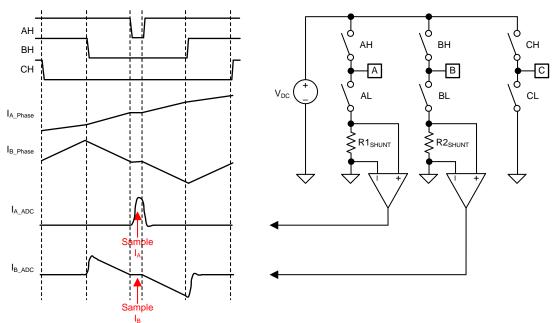

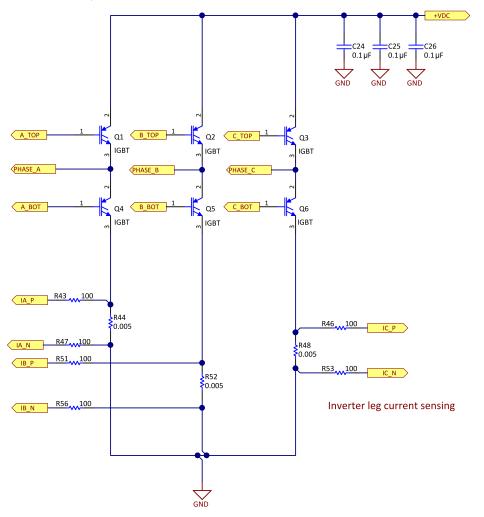

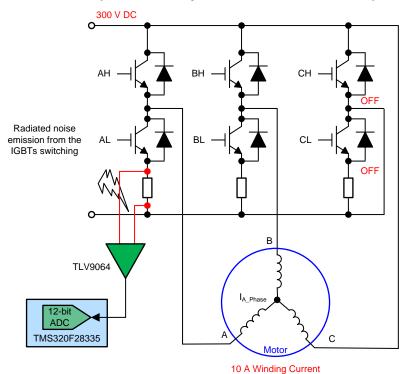

I shows three-shunt inverter leg current sensing. Three-shunt current sensing has some advantages. Contrary to the three-shunt technique, the use of a single- or two-shunt setup proves difficult to achieve circuit over modulation. Additionally, the use of a low-bandwidth op amp is sufficient. The three-shunt technique can bounce sampling between current signals, selecting two out of three phases each period, which allows long time periods for the current signals to settle, which means the current sensing window is no more limited by the minimum duty of PWM. If large current measurement windows are possible, then much slower and cheaper op amps can be used. For example, 图 2 shows three PWM switching signals and the corresponding shunt resistor to be sampled. As 图 2 shows, the current signal has plenty of time to stabilize.

#### 图 1. Three-Shunt Current Measurement Circuit With Inverter

图 2. Using Three-Shunt Current Sampling Technique

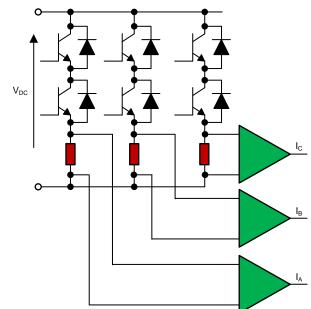

The two-shunt current measurement technique uses the principle of Kirchhoff's current law (KCL), which is that the sum of the currents into a single node equals zero. By measuring only two-phase currents, the third is calculated with KCL. 🛛 3 shows a circuit for the two-shunt current measurement technique.

The two- and three-shunt measurement circuit has an advantage over the single-shunt circuit in that it can detect circulating currents. A shows an example of a switching waveform and where the analog-todigital converter (ADC) samples the current. The PWM duty cycle for IA is almost 100% in this example, which causes the IA current to rise. The PWM for IB is about 50% duty cycle and its current stays at approximately 0 A for this period. Phase current can only be measured when the lower switch of that particular phase is conducting. In the example, IA is measurable for a very short time while IB has a long time to measure. The inherent problem of using the two-shunt technique is when the measured phase is operating at PWMs near 100%. For example, when sampling IA, the measured current signal has not yet stabilized, which gives an incorrect representation of the current signal.

#### 图 4. Sampling Current When Using Two-Shunt Measurement Technique

As the duty cycle increases, the time to measure voltage across the shunt resistor for the phase decreases and the current measurement must be quicker. As the duty cycle increases even more, the slew rate must be increased to properly capture the signal. Although the two-shunt current measurement technique lessens the speed requirement of the op amp as compared to the single-shunt measurement, there is a duty cycle where the slew rate has to be very large, but still less than the requirement for a single shunt.

Texas Instruments

www.ti.com.cn

## 1.1 Key System Specifications

${\it ${\rm ${\rm $\sharp$}}$}$  1 shows key parameters considered in the design of TIDA-010023.

## 表 1. Key System Specifications

| PARAMETER                                          | SPECIFICATIONS                                                | DETAILS                                                                                                                   |  |

|----------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| Input voltage                                      | 270-V to 390-V DC                                             | The DC voltage derived from the 195-V to 265-V AC input with or without power factor correction                           |  |

| Maximum output power                               | 2 kW                                                          | The IGBTs are selected to support a maximum 2 kW Power                                                                    |  |

| RMS winding current                                | 5.58 A                                                        | At 325-V DC delivering 2 kW at a power factor of 0.9 with space vector PWM                                                |  |

| Peak winding current                               | 7.89 A                                                        | At 325-V DC delivering 2 kW at a power factor of 0.9 with space vector PWM                                                |  |

| Control method                                     | Sensorless FOC                                                | Designed to support InstaSPIN-FOC                                                                                         |  |

| Inverter switching frequency                       | 15 kHz (adjustable from 5 kHz to 20 kHz)                      | Selection based on the motor inductance and desired current ripple                                                        |  |

| Feedback signals                                   | DC bus voltage, three winding voltages, inverter leg currents | The feedback signals are required for sensorless control                                                                  |  |

| Current shunt resistors used                       | 5-mΩ shunt for inverter leg current sensing using TLV9064     | See # 2.2.2 for design aspects                                                                                            |  |

| Op amps gain                                       | 25                                                            |                                                                                                                           |  |

| Inverter leg current sensing range                 | ±13.2 A                                                       | Scaled to 0 V to 3.3 V, level-shifted with 1.65-V bias                                                                    |  |

| Inverter leg current sensing accuracy (calibrated) | <1% (Calibrated)                                              | See # 3.2.1.3 for accuracy measurement                                                                                    |  |

| Protections                                        | Positive and negative winding<br>overcurrent, overtemperature | See 节 2.2.3 for the overcurrent protection measurement                                                                    |  |

| Cooling                                            | With external heat sink                                       |                                                                                                                           |  |

| Operating ambient                                  | –20°C to 55°C                                                 |                                                                                                                           |  |

| Board specification                                | 120 mm × 100-mm, two-layer, 1-oz<br>copper                    |                                                                                                                           |  |

| 15-V supply current for gate driver                | 50 mA (max)                                                   | See $\ddagger$ 2.2.4 for the power requirement in gate driver                                                             |  |

| 3.3-V supply current                               | 1 A (max)                                                     | For details, see 3.3-V, 1-A, Low EMI, 92% Efficiency<br>DC/DC Module in Dual Layer TO-220 Form Factor<br>Reference Design |  |

5

## 2 System Overview

## 2.1 Block Diagram

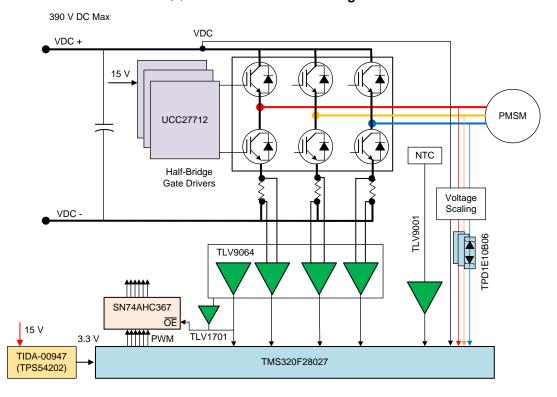

图 5. TIDA-010023 Block Diagram

## 2.2 Design Considerations

#### 2.2.1 Three-Phase Inverter

The three-phase inverter is designed to operate from the DC bus voltage up to 390 V. This design uses six IGBTs.

The designer has to adjust the position of the IGBT in the layout to fit the external heatsink. The power stage is designed to deliver up to 2-kW output power. The power stage is supplied with 390-V DC maximum and by considering the safety factor, switching spikes, and voltage build-up during regeneration, the IGBT is selected with the voltage rating equal to 600 V. 🛛 6 shows the structure of the board with heatsink installed.

6

#### 图 6. Structure of TIDA-010023 With External Heatsink

The current rating of the IGBT depends on the peak winding current. The three-phase inverter bridge is switched using SVPWM so that sinusoidal current is injected into the motor windings. The peak winding current can be calculated from the system specifications.

Inverter rated output power (POUT) = 2 kW

DC bus voltage = 325 V (rated), 270 V (minimum) - 390 V (maximum)

Power factor = 0.9 (assumed, for a low-inductance PMSM)

The nominal current in the IGBT can be calculated at the rated DC bus voltage. With space vector PWM, the maximum RMS line-to-line voltage can be 0.707 times the available DC bus voltage. For more details, see the *Space-Vector PWM With TMS320C24x/F24x Using Hardware and Software Determined Switching Patterns* application report.

$V_{LL_{RMS (nom)}} = 0.707 \times 325 = 229.8 V$

The rated winding current can be calculated using 公式 1:

$$I_{L(nom)} = \frac{P_{OUT}}{\sqrt{3} \times V_{LL(nom)} \times \cos\phi} = \frac{2000}{\sqrt{3} \times 229.8 \times 0.9} = 5.58 \text{ A}$$

(1)

The peak line current is calculated using  $\Delta \vec{x}$  2:

$$I_{L PEAK} = \sqrt{2 \times 5.58} = 7.89 A$$

(2)

(3)

The maximum current in the IGBT must be calculated at the minimum DC bus voltage. (see  $\Delta \pm 3$ ).

$$V_{LL\_RMS(nom)} = 0.707 \times 270 = 190.9 \text{ V}$$

$$I_{L} = \frac{P_{OUT}}{\sqrt{3} \times V_{L} \times \cos \phi} = \frac{2000}{\sqrt{3} \times 190.9 \times 0.9} = 6.72 \text{ A}$$

$$I_{L\_PFAK} = \sqrt{2} \times 6.72 = 9.5 \text{ A}$$

Considering an overloading and design margin of 200%, the maximum peak winding current to design should be  $\approx$  19 A. For this reference design, the IGBT IXDP20N60B is used. This IGBT has a continuous collector-current-carrying capacity of 32 A at Tc = 25°C, 20 A at Tc = 90°C and a peak current capacity of 60 A.

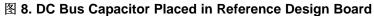

The inverter receives the DC power supply from the connector J4. C50 is the DC bus capacitor, as 🛛 8 shows. R80, R83 are the bleeder resistors for the capacitor.

7

注: C50 is designed as the local storage capacitor. The value is not designed to meet the full capacitor requirement for a 2-kW system. The capacitors on the AC-DC power supply which precede the inverter should be high enough, based on the design requirement.

#### 图 7. Three-Phase Inverter With Shunt Resistors

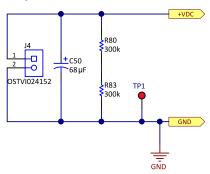

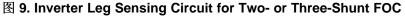

## 2.2.2 Current Sensing

The TIDA-010023 design has the option to use two or three shunt inverter leg current sensing. The following subsection details the design requirements and procedures for current sensing.

The TLV9064 device is used to sense and amplify the inverter leg current. The TLV906x series of devices feature rail-to-rail input- and output-swing capabilities, low input offset voltage and internal RFI and EMI filter. The TLV9064 device is a highly cost-effective solution for fast, accurate and robust current sensing. 9 shows the schematic of the inverter current sensing for phase A leg.

The current sensing circuit is designed as a non-inverting amplifier operating from unipolar single supply. The bidirectional current-sensing capability is achieved by adding a 1.65-V reference voltage level shift to the current sense amplifier output. The level shift of 1.65-V bias enables the positive current sensed at op-amp output is above 1.65-V and negative current sensed at op-amp output is below 1.65 V.

The calculation of the current-sense amplifier is as 2d 4 shows:

$V_{OUT} = (I_{SENSE} \times R_{SENS} \times GAIN) + V_{REF}$

where,  $I_{SENSE}$  is the current through the sense resistor,  $R_{SENSE}$  is the current sense resistor value, 5 m $\Omega$  is selected in this design, GAIN is set at 25,  $V_{REF}$  is the reference voltage of level shift, and 1.65 V is used.

The  $V_{REF}$  is generated by using divider resistors network at the non-inverter input pin of op-amp, the rules of calculation for divider resistors should follow &式 5:

$$R1 = R2 || (R3 + R7 + R43)$$

(5)

9

(4)

Power consumption in sense resistors and the input-offset error voltage of op amps are important when selecting the sense-resistance values. A high sense resistance value increases the power loss in the resistors. If the current sense amplifier is used without offset calibration, select the sense resistor value such that thee sense voltage across the resistor is sufficiently higher than the op-amp input offset voltage to reduce the effect of the offset error. The low input offset voltage of TLV9064 enables to use a high gain current sense amplifier and allows the designer to use a low sense resistor value.

The nominal RMS winding current is 5.58 A. The inverter leg shunt can only carry current while the lowside switch is ON; therefore, the RMS current in the inverter leg shunt will be smaller than the RMS winding current and the value depends on the duty cycle. However, for the simplification of analysis, the winding current is considered when calculating the shunt resistor power requirement. The peak winding current is 9.5 A, as mentioned in Equation 3. The TIDA-010023 uses a 5-m $\Omega$ , 3-W sense resistor which allows sensing up to ±13.2 A with an amplifier gain of 25. The sense resistor must be selected with a low temperature drift and minimum parasitic inductance (ideally zero).

System Overview

The maximum power dissipation in a single-inverter leg current sense shunt resistor equals:  $l^2_{RMS} \times R_{SENSE} = 6.72 \times 5 \ m\Omega = 0.225 \ W$

## 2.2.3 Overcurrent Protection

System Overview

#### 图 10. Overcurrent Protection for Both Positive and Negative Currents

+3.3VD R18 R19 R20 10.0k 21.5k 10.0k || AGND

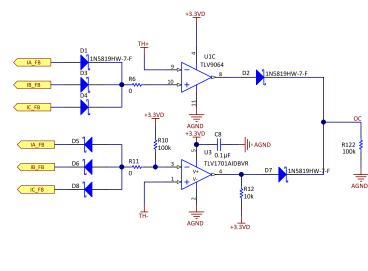

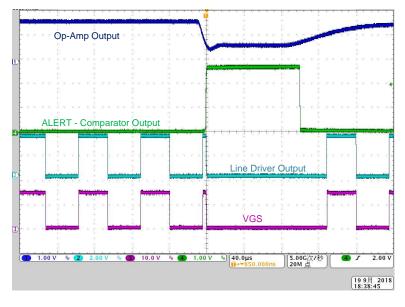

The overcurrent protection circuit output signal OC is connected to the enable pin of the line driver device - SN74AHC367. Once the overcurrent event occurs, the OC signal will be pulled up and disable the output of the line driver and hence the SVPWM signals at the input of gate driver - UCC27712. Thus, the process of protection is achieved all by hardware, which features very fast response time.

The overcurrent protection thresholds can be adjusted by changing the value of divider resistors - R18 and R20. A pullup resistor R12 is at the open-collector output of TLV1701, and meanwhile providing pull-up capability for enable signal of SN74AHC367.

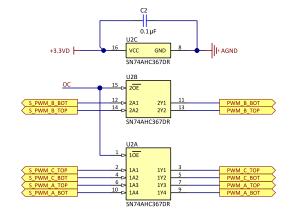

## 2.2.4 Gate Driver Using UCC27712

11 shows the circuit diagram for a half-bridge driver using the UCC27712 device.

System Overview

图 11. Gate Driver Schematic for Half Bridge

#### Selecting HI and LI Low Pass Filter Components:

A small RC filter should be added between output of line driver and input pin of UCC27712 to filter the high frequency noise. The recommend value of the RC filter is  $R35 = R36 = 49.9 \Omega$ , and C29 = C30 = 33 pF.

#### Selecting the Bootstrap Capacitor:

The bootstrap capacitor must be sized to have more than enough energy to drive the gate of the IGBT high without depleting the bootstrap capacitor more than 10%. A good guideline is to size CBOOT to be at least ten times as large as the equivalent IGBT gate capacitance ( $C_g$ ).  $C_g$  must be calculated based on the voltage driving the high-side gate of the IGBT ( $V_{GE}$ ) and the gate charge of the IGBT ( $Q_g$ ).  $V_{GE}$  is approximately the bias voltage supplied to VDD after subtracting the forward-voltage drop of the bootstrap diode D11 (VDBOOT). In this design example, the estimated  $V_{GE}$  is approximately 14.4 V, as  $\Delta$ T shows.

$$V_{GE} \approx V_{DD} - V_{DBOOT} = 15 \text{ V} - 0.6 \text{ V} = 14.4 \text{ V}$$

(7)

The IGBT in this reference design has a specified  $Q_g$  of 70 nC. The equivalent gate capacitance of thee IGBT can be calculated as  $\Delta \chi 8$  shows.

$$C_{G} = \frac{Q_{g}}{V_{GE}} = \frac{70 \text{ nC}}{14.4} \approx 4.86 \text{ nF}$$

(8)

After estimating the value for  $C_g$ ,  $C_{BOOT}$  must be sized to at least ten times larger than  $C_g$ , as  $\Delta rac{3}{3}$  shows.

$C_{BOOT} \ge 10 \times C_{G} \times 48.6 \text{ nF}$ (9)

For this reference design, a 680-nF capacitor has been chosen for the bootstrap capacitor, as  $\Delta$  $\pm 10$  shows.

$$C_{BOOT} = C_{28} = 0.68 \,\mu\text{F}$$

(10)

#### Selecting VDD bypass/holdup capacitor C<sub>VDD</sub> and R<sub>bias</sub>:

The  $V_{DD}$  capacitor ( $C_{VDD}$ ) must be chosen to be at least ten times larger than  $C_{BOOT}$ . For this design, a 10- $\mu$ F capacitor has been selected.

A 2.2- $\Omega$  resistor R<sub>BIAS</sub>in series with bias supply and VDD pin is recommended to make the VDD ramp up time larger than 20µs to minimize LO and HO rising.

Selecting the bootstrap resistor (R<sub>BOOT</sub>):

Select the resistor  $R_{BOOT}$  to limit the current in  $D_{BOOT}$  and limit the ramp-up slew rate of the voltage across the HB and HS pin. TI recommends selecting an  $R_{BOOT}$  resistor between 2  $\Omega$  and 20  $\Omega$  when using the UCC27712 gate driver. This TIDA-010023 reference design uses a current-limiting resistor of 3.3  $\Omega$ . The peak bootstrap diode current ( $I_{DBOOTPK}$ ) is limited to approx. 4.36 A.

$$R_{BOOT} = R30 = 3.3 \Omega$$

$$I_{DBOOT_{PK}} = \frac{V_{DD} - V_{DBOOT}}{R_{BOOT}} \frac{15 \text{ V} - 0.6 \text{ V}}{3.3 \Omega} \approx 4.36 \text{ A}$$

(11)

The power dissipation capability of the bootstrap resistor is important. The bootstrap resistor must be able to withstand the short period of high power dissipation during the initial charging sequence of the bootstrap capacitor. This energy is equivalent to  $\frac{1}{2} \times \text{CBOOT} \times \text{V2}$ . This energy is also dissipated during the charging time of the bootstrap capacitor (approximately  $3 \times \text{RBOOT} \times \text{CBOOT}$ ). The TIDA-010023 reference design uses a 3.3- $\Omega$ , 0.125-W resistor.

#### Selecting the bootstrap diode:

The voltage that the bootstrap diode encounters is the same as the full DC bus voltage (in this case a maximum of 390-V DC). The bootstrap diode voltage rating must be greater than the DC bus rail voltage. The bootstrap diode must be a fast recovery diode to minimize the recovery charge and thereby the charge that feeds from the bootstrap capacitor to the 15-V VDD supply. The diode must be able to carry a pulsed peak current of 4.36 A. However, the average current is much smaller and depends on the switching frequency and the gate charge requirement of the high-side IGBT. The TIDA-010023 reference design uses a 1000-V, 1-A, fast-recovery diode.

#### Selecting thee-gate resistor $R_{ON}$ and $R_{OFF}$ :

Resistor  $R_{\mbox{\scriptsize ON}}$  and  $R_{\mbox{\scriptsize OFF}}$  are sized to achieve the following:

- Limit ringing caused by parasitic inductances and capacitances.

- Limit ringing caused by high voltage/current switching dV/dt, dl/dt, and body diode reverse recovery.

- Fine-tune gate drive strength to optimize switching loss.

- Reduce electromagnetic interference (EMI)

From the UCC27712 620-V, 1.8-A, 2.8-A High-Side Low-Side Gate Driver with Interlock data sheet:

LO and HO output pulldown resistance,  $\rm R_{HOL}$  =  $\rm R_{LOL}$  = 1.5  $\Omega$

LO and HO output pullup resistance,  $R_{HOH} = R_{LOH} = 3.0 \Omega$

The TIDA-010023 reference design uses different gate resistors in the turnon and turnoff path of the IGBT. The external gate resistance in the turnon path is  $R33 = R38 = 5.0 \Omega$ , and external gate resistance in the turnoff path is 5.0  $\Omega$  and 12  $\Omega$  in parallel.

公式 12 calculates the maximum HO drive current ( $I_{HO DR}$ ):

$$I_{HO_{DR}} = \frac{V_{DD} - V_{DBOOT}}{R_{HOH} + R_{ON} + R_{GFET_{Int}}} = \frac{12 \, V - 0.6 \, V}{3 \, \Omega + 5 \, \Omega + 1 \, \Omega} \approx 1.27 \, A$$

(12)

公式 13 calculates the maximum HO sink current (I<sub>HO SK</sub>):

$$I_{HO_SK} = \frac{V_{DD} - V_{DBOOT} - V_{DGATE}}{R_{HOL} + R_{ON} + R_{GFET_{int}}} = \frac{12 \ V - 0.6 \ V - 0.6 \ V}{1.5 \ \Omega + 3.53 \ \Omega + 1\Omega} \approx 1.7 \ A$$

(13)

公式 14 calculates the maximum LO drive current ( $I_{LO DR}$ ):

$$I_{LO_DR} = \frac{V_{DD}}{R_{LOH} + R_{ON} + R_{GFET_{int}}} = \frac{12 V}{3 \Omega + 5 \Omega + 1 \Omega} \approx 1.33 A$$

(14)

公式 15 calculates the maximum LO sink current ( $I_{LO_SK}$ ):

$$I_{LO_{SK}} = \frac{V_{DD} - V_{DGATE}}{R_{LOL} + R_{ON} + R_{GFET_{Int}}} = \frac{12 \text{ V} - 0.6 \text{ V}}{1.5 \Omega + 3.53 \Omega + 1\Omega} \approx 1.9 \text{ A}$$

(15)

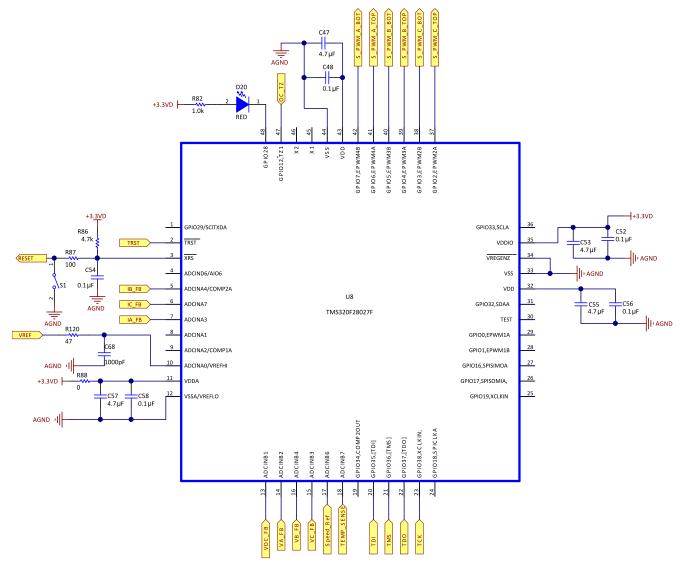

## 2.2.5 Microcontroller Unit

Piccolo TMS320F28027F MCU is used in the reference design. This MCU has special motor control software in execute-only ROM to enable InstaSPIN-FOC solution, with system software support through MotorWare<sup>TM</sup> Software. The F2802x Piccolo<sup>TM</sup> family of microcontrollers provides the power of the C28x core coupled with highly-integrated control peripherals in low pin-count devices. The digital and analog power supplies are provided with adequate decoupling. The analog power supply is decoupled through R88 resistor (the designer can choose a value up to 10  $\Omega$ ) to isolate the switching currents from the digital power supply, which provides a better power supply noise rejection for the ADC of the MCU.

#### 图 12. MCU Schematic and Peripheral Connections

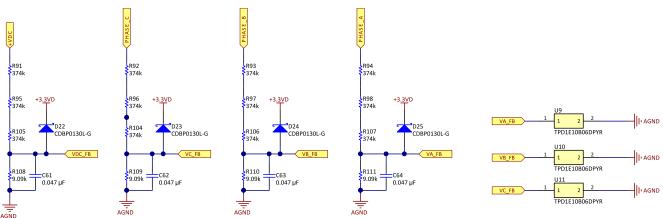

#### 2.2.6 Voltage Sensing

The voltage divider circuit that 🕅 13 shows is used to measure the winding voltages and DC bus voltage. Voltage feedback is required in the FAST<sup>™</sup> software encoder estimator of the InstaSPIN-FOC to allow the best performance at the widest speed range. In FAST, phase voltages are measured directly from the motor phases instead of a software estimate. This software value

(USER\_ADC\_FULL\_SCALE\_VOLTAGE\_V) depends on the voltage divider gain of the circuit, which senses the voltage feedback from the motor phases

In 图 13, PHASE\_A, PHASE\_B, and PHASE\_C are the phase voltages. These voltages are properly scaled and fed to the MCU through VA\_FB, VB\_FB, and VC\_FB. The maximum phase voltage feedback measurable by the MCU can be calculated as 公式 16 shows, considering the maximum voltage for the ADC input is 3.3 V.

$$V_{a}^{max} = V_{ADC_{a}}^{max} \times \frac{(9.09 \, k\Omega + 1122 \, k\Omega)}{9.09 \, k\Omega} = 410.62 \, V$$

(16)

For a motor with a maximum operating voltage of 390 V, this voltage feedback resistor divider is ideal. This divider makes sure that the ADC resolution is at the maximum for a motor working from 270-V DC to 390-V DC.

The voltage filter pole is required by the FAST estimator (see the *InstaSPIN-FOC<sup>TM</sup>* and *InstaSPINMOTION<sup>TM</sup>* user's guide) to allow an accurate detection of the voltage feedback. The filter cutoff frequency should be low enough to filter out the PWM signals. As a general guideline, a cutoff frequency of a few hundred Hertz is enough to filter out a PWM frequency of 10 kHz to 20 kHz. The hardware filter should only be changed when ultra-high speed motors are run, which generate phase voltage frequencies in the order of a few kHz. In this reference design, consider the PMSM to have a maximum speed of approximately 3,000 RPM with eight pole pairs. This scenario gives a voltage frequency of:  $3000 \times 8 / 60 = 400$  Hz. The voltage filter of 400 Hz should be enough cutoff frequency for this motor and speed. The filter pole setting is calculated using  $\Delta \pm 17$ .

$$F_{\text{filter\_pole}} = \frac{1}{2 \times \pi \times R_{\text{parallel}} \times C} = \frac{1}{2 \times \pi \times \frac{(1122 \text{ k}\Omega \times 9.09 \text{ k}\Omega)}{(1122 \text{ k}\Omega \times 9.09 \text{ k}\Omega)} \times 0.047 \text{ }\mu\text{F}} = 375.7 \text{ Hz}$$

(17)

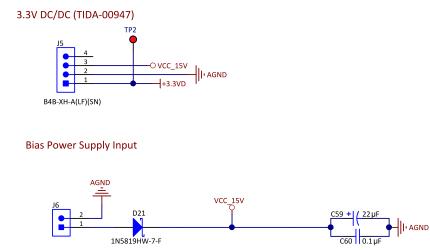

## 2.2.7 External Bias Power Supply and Onboard DC/DC module

The TIDA-010023 reference design board requires external 15 V, which is used for the gate driver power supply. The 3.3-V power supply for MCU, current sense amplifier, and the signal conditioning circuits is from TIDA-00947 reference design board.

The TI Design TIDA-00947 demonstrates a small, high efficiency, low EMI DC/DC module to replace LDOs in major home appliance applications. This results in drastic improvement in efficiency, saving both size and cost, as no heat sink is required. With the same input current, the TPS54202, as a power converter, enables the supplying of higher output current as well as having lower power consumption at full load, low load, and standby operation. This module is size and pin compatible with a TO-220 LDO enabling a quick evaluation and time to market.

## 图 14. Bias Power Supply Connection

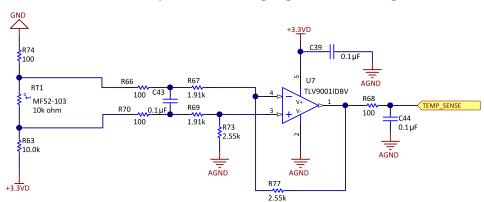

#### 2.2.8 IGBT Temperature-Sensing Signal Conditioning Circuit

A NTC resistor is used and can be mounted on the heatsink. The NTC is biased using one resistor R63 (10 k $\Omega$ ) to 3.3 V and one resistor R74 (100  $\Omega$ ) to ground as 🔀 15 shows. The 10-k $\Omega$  resistor limits the current in the circuit at the minimum temperature sensor resistance. The voltage across the NTC is connected as the differential input to the TLV9001 op amp configured as a differential amplifier.

#### 图 15. IGBT Temperature-Sensing Signal Conditioning Circuit

The ADC of the MCU reads the output of the temperature sense signal-conditioning circuit and necessary action can be taken for overtemperature protection.

## 2.3 Highlighted Products

#### 2.3.1 TLV9064

The major requirements in selecting the current sense amplifier are adequate gain bandwidth & slew rate, RRIO capability, good CMRR and PSRR, good EMI and RFI rejection, low offset voltage and input offset current and stable capacitive load drive.

The TLV9061 (single), TLV9062 (dual), and TLV9064 (quad) are single-, dual-, and quad- low-voltage (1.8 V to 5.5 V) operational amplifiers (op amps) with rail-to-rail input- and output-swing capabilities. These devices are highly cost-effective solutions for applications where low-voltage operation, a small footprint, and high capacitive load drive are required. Although the capacitive load drive of the TLV906x is 100 pF, the resistive open-loop output impedance makes stabilizing with higher capacitive loads simpler.

## 2.3.2 TLV1701

The TLV170x family of devices offers a wide supply range, rail-to-rail inputs, low quiescent current, and low propagation delay. The open collector output offers the advantage of allowing the output to be pulled to any voltage rail up to +36 V above the negative power supply, regardless of the TLV170x supply voltage, and allows easy-wired OR structure with other fault outputs All devices are specified for operation across the expanded industrial temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

#### 2.3.3 UCC27712

The UCC27712 is a 620-V high-side and low-side gate driver with 1.8-A source, 2.8-A sink current, targeted to drive power MOSFETs or IGBTs. The recommended VDD operating voltage is 10-V to 20-V for IGBTs and 10-V to 17-V for power MOSFETs. The UCC27712 includes protection features where the outputs are held low when the inputs are left open or when the minimum input pulse width specification is not met. Interlock and deadtime functions prevent both outputs from being turned on simultaneously. In addition, the device accepts a wide range bias supply range and offers UVLO protection for both the VDD and HB bias supply. Developed with TI's state of the art high-voltage device technology, the device features robust drive with excellent noise and transient immunity including large negative voltage tolerance on its inputs, high dV/dt tolerance, wide negative transient safe operating area (NTSOA) on the switch node (HS), and interlock. The device consists of one ground-referenced channel (LO) and one floating channel (HO) which is designed for operating with bootstrap or isolated power supplies. The device features fast propagation delays and excellent delay matching between both channels. On the UCC27712, each channel is controlled by its respective input pins, HI and LI

#### 2.3.4 TLV9001

The TLV900x family includes single (TLV9001), dual (TLV9002), and quad-channel (TLV9004) low-voltage (1.8 V to 5.5 V) operational amplifiers (op amps) with rail-to-rail input and output swing capabilities. These op amps provide a cost-effective solution for space-constrained applications such as smoke detectors, wearable electronics, and small appliances where low-voltage operation and high capacitive-load drive are required. The capacitive-load drive of the TLV900x family is 500 pF, and the resistive open-loop output impedance makes stabilization easier with much higher capacitive loads. These op amps are designed specifically for low-voltage operation (1.8 V to 5.5 V) with performance specifications similar to the TLV600x devices.

The robust design of the TLV900x family simplifies circuit design. The op amps feature unity-gain stability, an integrated RFI and EMI rejection filter, and no-phase reversal in overdrive conditions. The TLV900x devices include a shutdown mode (TLV9002S and TLV9004S) that allow the amplifiers to switch off into standby mode with typical current consumption less than 1  $\mu$ A.

## 2.3.5 SN74AHC367

The SN74AHC367 devices are hex buffers and line drivers designed for 2-V to 5.5-V VCC operation. These devices are designed specifically to improve both the performance and density of 3-state memory address drivers, clock drivers, and bus-oriented receivers and transmitters. The SN74AHC367 devices are organized as dual 4-line and 2-line buffers/drivers with active-low output-enable (1OE and 2OE) inputs. When OE is low, the device passes non-inverted data from the A inputs to the Y outputs. When OE is high, the outputs are in the high-impedance state. To ensure the high-impedance state during power up or power down, OE should be tied to VCC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

## 2.3.6 TMS320F28027F

The F2802x Piccolo family of microcontrollers provides the power of the C28x core coupled with highlyintegrated control peripherals in low pin-count devices. This family is code-compatible with previous C28xbased code and also provides a high level of analog integration. An internal voltage regulator allows for single-rail operation. Enhancements have been made to the HRPWM to allow for dual-edge control (frequency modulation). Analog comparators with internal 10-bit references have been added and can be routed directly to control the PWM outputs. The ADC converts from 0- to 3.3-V fixed full-scale range and supports ratio-metric VREFHI and VREFLO references. The ADC interface has been optimized for low overhead and latency.

Piccolo TMS320F28027F has special motor control software in execute-only ROM to enable InstaSPIN-FOC solution, with system software support through MotorWare<sup>™</sup>. While standard C2000<sup>™</sup> controlSUITE<sup>™</sup> software can be used with these devices, note that this special ROM replaces the standard ROM, which means that certain software functions that controlSUITE<sup>™</sup> projects expect to be in ROM must to be linked into the project. See the *InstaSPIN-FOC and InstaSPIN-MOTION Memory Considerations* section of the *InstaSPIN-FOC<sup>™</sup>* and *InstaSPINMOTION<sup>™</sup>* user's guide or the *Memory* section of *TMS320F2802x Piccolo<sup>™</sup> Microcontrollers* for more details.

## 3 Hardware, Software, Testing Requirements, and Test Results

## 3.1 Required Hardware and Software

## 3.1.1 Hardware

## 3.1.1.1 Connector Configuration of TIDA-010023

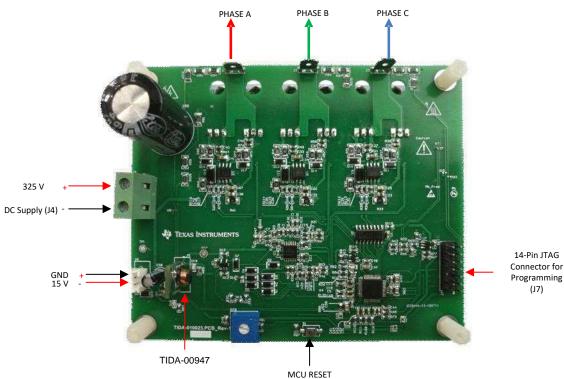

图 16 shows the TIDA-010023 connector configuration, the details follow:

- Two-terminal connector for high voltage DC input (J4): This pin is used to connect the input DC supply from the preceding AC-DC power supply or the power factor correction (PFC) circuit. The positive and negative terminals can be identified as shown in <a>[8]</a> 16. The maximum voltage allowed at this pin is 3900 V.

- Two-terminal output connector for bias power supply (J6): This connector is used to provide external power supply to the board. The board requires an external 15-V power supply with ±10% tolerance.

- Four-terminal connector for installing TIDA-00947: This connector is used to install a LDO with TO-220 footprint or a DC/DC module such as TIDA-00947.

- Three separate connectors for motor winding connection: 🛽 16 shows the phase output connections for connecting to the three-phase motor winding.

- 14-pin JTAG connector (J7): This connector is used for programming the MCU from an external JTAG interface driver.

#### 图 16. TIDA-010023 PCB Connectors

表 2 lists the recommended operating voltages on the connectors.

| DESCRIPTION                 | VOLTAGE SPECIFICATION |       |        | MAXIMUM CURRENT |

|-----------------------------|-----------------------|-------|--------|-----------------|

| DESCRIPTION                 | MIN                   | ТҮР   | MAX    | MAXIMOW CORRENT |

| High: DC Input (J4)         | 270 V                 | 325 V | 390 V  | 10 A            |

| Motor: Connection           | 270 V                 | 325 V | 390 V  | 10 A            |

| 15-V bias power supply (J6) | 13.5 V                | 15 V  | 16.5 V | 50 mA           |

#### 表 2. Recommended Operating Voltage on Connectors

## 3.1.1.2 Programming the TMS320F28027F

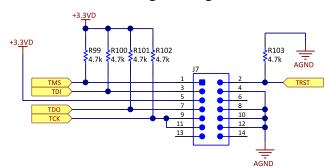

图 17 shows thee pin details of the 14-pin JTAG connector provided in the board.

## 图 17. MCU Programming Connector

See http://www.ti.com/product/TMS320F28027F/toolssoftware#devtools for the different programming options of the TMS320F28027.

#### CAUTION

Use an isolated JTAG interface for programming and real-time debugging of the board, if the board is powered from non-isolated power supplies. The use of a non-isolated JTAG interface is only permitted if all of the power supply to the system is properly isolated with sufficient safety precautions.

## 3.1.1.3 Procedure for Board Bring-up and Testing Using InstaSPIN-FOC<sup>™</sup>

The following list details the procedure for board bring-up and testing:

- 1. Remove the motor connection and high-voltage DC supply input from the board and power on the 15-V supply.

- 2. Use the power supply from the computer to power the JTAG driver.

- 3. Program the MCU as detailed in  $\ddagger$  3.1.1.2.

- 4. Connect the inverter output to the motor winding terminals.

- 5. Use a current-limited DC source to power up the high-voltage supply input.

- 6. See the *InstaSPIN-FOC™* and *InstaSPINMOTION™* user's guide to understand the detailed procedure for using InstaSPIN-FOC.

#### 3.1.2 Software

The InstaSPIN-FOC is selected as it is easy to work with motors with unknown parameters. The MCU firmware for the C2000<sup>™</sup> is taken from MotorWare Software. MotorWare contains the required projects and libraries to use TI's InstaSPIN-FOC technology. Download the MotorWare Software from http://www.ti.com/tool/motorware.

This design is similar to the 'HVMotorCtrl+PfcKit\_v2.1' hardware. Therefore, for Code Composer Studio<sup>™</sup> projects, use the projects under "hvkit\_rev1p1". After installing the MotorWare Software, the projects are found in the folder location:

$...\label{eq:loss} with the set of the set$

$\pm$  3 shows the hardware assignments in the TIDA-010023 reference design.

| HARDWAR          | RE ASSIGNMENTS                       | DESCRIPTION                                                         |  |

|------------------|--------------------------------------|---------------------------------------------------------------------|--|

| Developm         | ent and emulation                    | Code Composer Studio software                                       |  |

| Targ             | jet controller                       | TMS320F28027F                                                       |  |

| PWI              | M frequency                          | 15-kHz PWM (default), programmable for higher and lower frequencies |  |

| P                | WM mode                              | Space vector, complimentary with dead time                          |  |

|                  |                                      | EPWM4A → Phase-A top-switch PWM                                     |  |

|                  | PWM Generation                       | $EPWM4B \rightarrow Phase-A \text{ bottom-switch } PWM$             |  |

|                  |                                      | EPWM3A → Phase-A top-switch PWM                                     |  |

|                  |                                      | $\text{EPWM3B} \rightarrow \text{Phase-A bottom-switch PWM}$        |  |

|                  |                                      | EPWM2A → Phase-A top-switch PWM                                     |  |

|                  |                                      | $\text{EPWM2B} \rightarrow \text{Phase-A bottom-switch PWM}$        |  |

| Over             | Overcurrent PWM shutoff<br>trip-zone | TZ1 $\rightarrow$ Overcurrent comparator output (OC)                |  |

|                  | ADC Channel assignment               | ADCINA3 $\rightarrow$ Phase-A inverter leg current sense feedback   |  |

| Peripherals Used |                                      | ADCINA4 $\rightarrow$ Phase-A inverter leg current sense feedback   |  |

|                  |                                      | ADCINA7 $\rightarrow$ Phase-A inverter leg current sense feedback   |  |

|                  |                                      | ADCINB2 $\rightarrow$ Phase-A motor voltage sense feedback          |  |

|                  |                                      | ADCINB4 $\rightarrow$ Phase-A motor voltage sense feedback          |  |

|                  |                                      | ADCINB3 $\rightarrow$ Phase-A motor voltage sense feedback          |  |

|                  |                                      | ADCINB1 $\rightarrow$ DC bus voltage sense feedback                 |  |

|                  |                                      | ADCINB7 $\rightarrow$ Temperature sense feedback                    |  |

|                  |                                      | ADCINB6 → Potentiometer voltage feedback                            |  |

|                  | GPIO                                 | $GPIO28 \rightarrow LED$ indication                                 |  |

## 表 3. Hardware Assignments in TIDA-010023

Before running the InstaSPIN projects, the hardware assignments should be modified in software because of the difference between this design and 'HVMotorCtrl+PfcKit\_v2.1' hardware. The details of modifying the hardware assignments is provided in section 6 of 'Hardware Abstraction Layer (HAL) Module of MotorWare<sup>™</sup> in ...\motorware\motorware\_1\_01\_00\_18\docs\tutorials\motorware\_hal\_tutorial.pdf.

Before running the InstaSPIN projects, the user parameters should also be modified in software. The details of modifying the user parameters is provided in chapter 4 of *InstaSPIN-FOC<sup>TM</sup>* and *InstaSPINMOTION<sup>TM</sup>*.

The detailed procedure to build and run the lab is provided in 'InstaSPIN Projects and Labs User's Guide' in : .../motorware/motorware\_1\_01\_00\_18/docs/labs/instaspin\_labs.pdf.

## 3.2 Testing and Results

$\frac{1}{8}$  4 lists the key test equipment. The following subsections descriptions and pictures of the test setup for specific tests.

| DESCRIPTION                  | PART NUMBER                                         |

|------------------------------|-----------------------------------------------------|

| High-speed oscilloscope      | MSO4104B mixed-signal oscilloscope 1 GHz            |

| High-voltage DC power        | 6260-600 digital DC power supply                    |

| Adjustable power supply      | GPS-3303C laboratory DC power supply                |

| High-current adjustable Load | Chroma 63103 DC electronic load 6 A, 60 A, 300<br>W |

| JTAG debugger                | XDS100V3 emulator                                   |

## 表 4. Key Test Equipment

## 3.2.1 Test Results

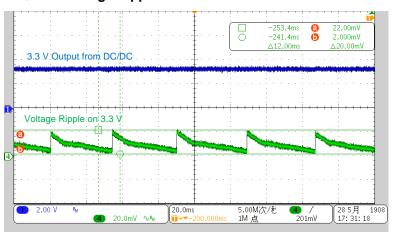

## 3.2.1.1 3.3-V Power Supply Generated by TIDA-00947

## 图 18. Voltage Ripple From TIDA-00947 DC/DC Module

Hardware, Software, Testing Requirements, and Test Results

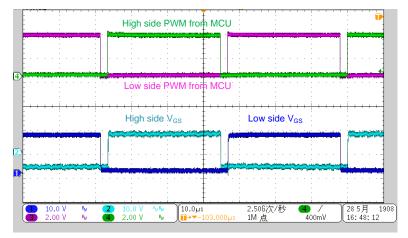

#### 3.2.1.2 Functional Evaluation of UCC27712 Gate Driver

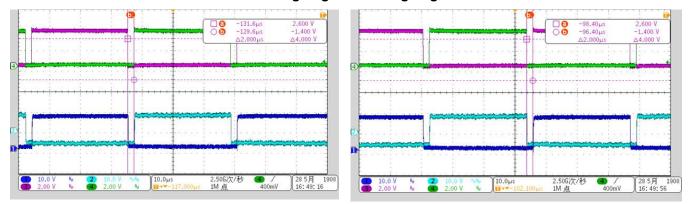

The UCC27712 gate driver receives PWM signals from the line driver output of the SN74AHC367 and the corresponding gate driver voltages are generated. [3] 19 shows the low-side and high-side PWM input of the UCC27712 device and the corresponding low-side and high-side output of the UCC27712 device measured across the gate to the emitter ( $V_{GE}$ ) of the IGBT.

#### 图 19. Low-Side and High-Side Gate Driver Voltage from UCC27712

$\boxtimes$  20 shows the PWM signals of high-side and low-side gate to source voltage from UCC27712, which shows that the dead time configured by the MCU at both of the edges of the PWM. The dead time is programmed to 2 µs.

图 20. Dead Time at Falling Edge and Rising Edge of Low-Side PWM

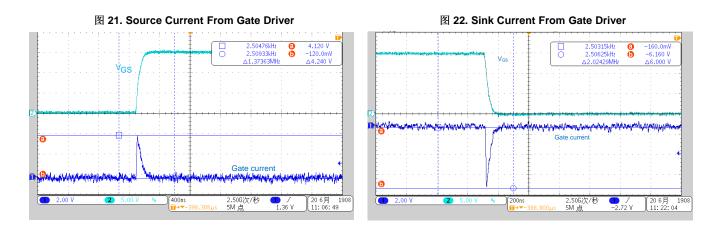

图 21, 图 22, and 图 23 show the source and sink current provided by UCC27712. The peak gate current is captured by monitoring the voltage across the gate resistors. The test conditions follow:

- $R_{G(ON)} = 5.0 \ \Omega$

- $R_{G(OFF)} = 3.53 \ \Omega$

- Gate charge (Q<sub>q</sub>) of IGBT = 70 nC

During the testing no external capacitance is connected between the gate and source of the IGBT. The reference design is tuned to get a source current of approximately 0.85 A, and the sink current of approximately 1.7 A.

#### 图 23. Source and Sink Current From Gate Driver

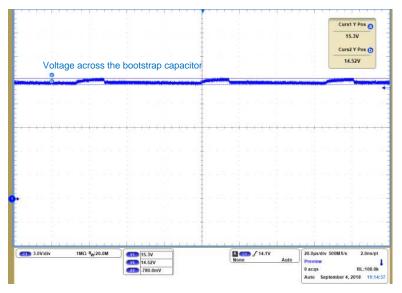

A bootstrap capacitor of 0.68  $\mu$ F is used in the reference design. (24) shows the ripple on the bootstrap capacitor. The peak-to-peak ripple voltage is 0.78 V. The test result is taken with a duty cycle of 80% and the designed bootstrap capacitor maintains voltage ripple within 5% and eliminates undervoltage lockout even in the worst conditions.

#### 图 24. Voltage Ripple Across Bootstrap Capacitor

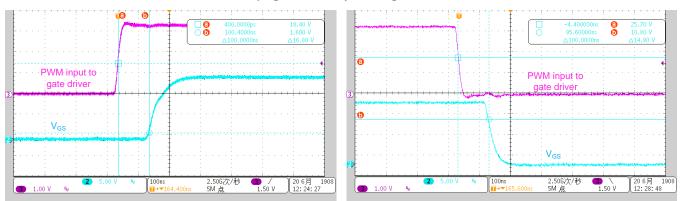

#### 图 25. Gate Driver Propagation Delay During PWM Turnon and Turnoff

☑ 25 shows the UVLO protection of UCC27712, and the threshold voltage observed is approximately 8.4

V, which ensure that the IGBT is turned on properly with sufficient gate voltage.

#### 3.2.1.3 Current Sensing

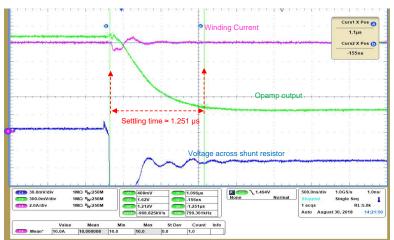

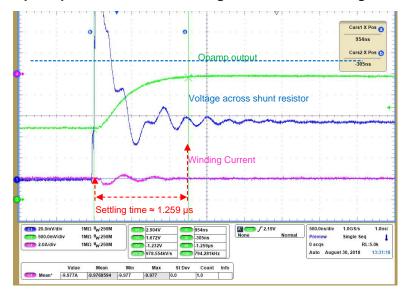

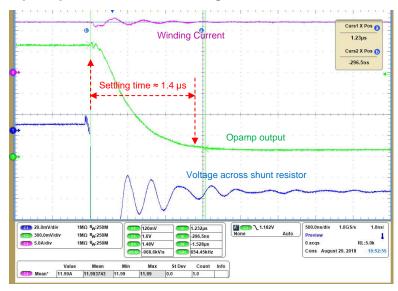

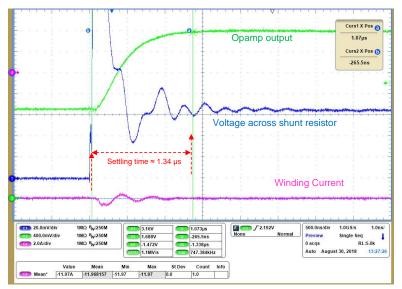

The transient response of the current sense amplifier is evaluated with a step change in voltage across the shunt resistor. The step change in sense voltage is created by switching the corresponding IGBTs with the motor connected, causing the winding current to flow through the sense resistor.

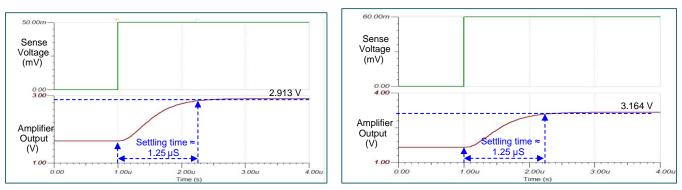

## 图 26. Simulated Step Response of Current Sensing Circuit

## 图 27. Step Response of Current Sensing Circuit

#### 图 28. Step Response of Current-Sensing Circuit With 10-A Positive Current

图 29. Step Response of Current-Sensing Circuit With 10-A Negative Current

$\boxtimes$  30 and  $\boxtimes$  31 show the step response with winding current at 12 A winding current. The settling time of current sense amplifier output is 1.34 µs. Faster settling time and rail to rail output capability helps to minimize the current sense distortion especially with 2-shunt at lower phase duty cycles.

图 30. Step Response of Current Sensing Circuit With 12-A Positive Current

#### 图 31. Step Response of Current-Sensing Circuit With 12-A Negative Current

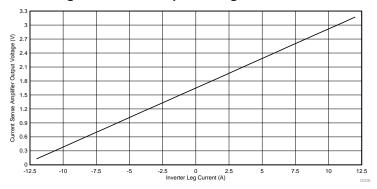

$\boxtimes$  32 shows the steady-state transfer function of the inverter leg current through the 5-m $\Omega$  shunt resistor versus the output voltage of the TLV9064 amplifier. The output voltage equals 9.2 mV when the inverter leg current is zero, mainly contributed by the offset voltage of the op-amp, which can be calibrated. The test is done across the full swing range from -12 A to +12 A current. The transfer function is linear, which makes the software processing simple.

图 32. Inverter Leg Current vs Output Voltage Transfer Function Op Amp

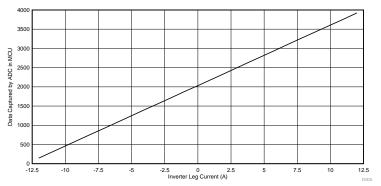

With the purpose of evaluating the transfer function for actual data used in the sensorless FOC algorithm, 33 shows the transfer function of the inverter leg current through the shunt resistor versus the values read from ADC data buffer of TMS320F28027F. The transfer function is linear across -12 A to +12 A current. The transfer function is also linear, which means no extra calibration algorithm needed.

图 33. Inverter Leg Current vs Data Acquired by ADC in MCU Transfer Function

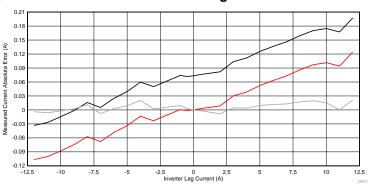

DC accuracy of the current sense amplifier TLV9064 is done with 5-m $\Omega$  sense resistor at a gain of 25.125 V/V and at 25°C ambient temperature. The full-scale DC bus current range is –13.2 A to +13.2 A. The inverter leg current is measured with a precision 6½ digit multimeter connected in series to the inverter leg shunt and the output voltage of the current sense amplifier TLV9064 is measured with another precision 6½ digit multimeter.

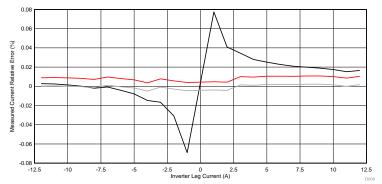

The TLV9064 has low input offset voltage of  $\pm 0.3 \text{ mV}$ , low input offset current of 0.05 pA, and high CMRR. 34 shows the absolute error in inverter leg current measurement. The uncalibrated absolute error (shown in black curve in 34) is less than 0.25 A (absolute value) with respect to the input current range from -12 A to 12 A. The uncalibrated error is dominated by sense resistor tolerance, offset voltage of the amplifier, feedback resistor tolerance, variation in reference voltage, and power supply ripple. The current sense amplifier output error is calibrated for offset voltage (shown in red curve in  $\oiint{34}$ ) and the calibrated output error is less than  $\pm 0.11$  A. The current sense amplifier output error is calibrated for sense resistor tolerance (shown in green curve in  $\oiint{34}$ ) and the calibrated output error is less than  $\pm 0.02$  A.  $\oiint{35}$ shows the relative error [%] in measured current from the amplifier output voltage, and the calibrated relative error for offset voltage and sense resistor tolerance is less than 1%, after calibrating for op-amp offset voltage.

图 34. Absolute Error in Inverter Leg Current Measurement

图 35. Relative Error [%] in Inverter Leg Current Measurement

## 3.2.1.4 Noise Rejection of Current Sense Amplifier

With the purpose of understanding the noise rejection by current sense amplifier, the test is done as per the set up shown in  $[\[mathbb{M}]]$  36.

#### 图 36. Test Setup for Noise Rejection of Current Sense Amplifier

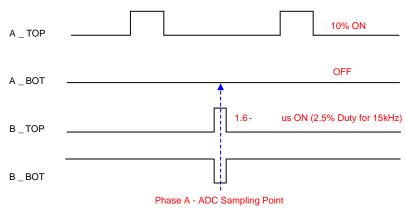

The DC bus voltage is set at 300 V, and the winding current is at 10 A. PWM is applied to Phase A and Phase B. Phase C is left open. 🕅 37 shows the PWM signals, the PWM signal driving the high-side IGBT for Phase A has 10% duty, and the low-side IGBT is kept off. The PWM signal driving high-side IGBT for Phase B has 2.5% duty, and the frequency is set at 15 kHz.

#### 图 37. PWM Signals for Phase A and Phase B

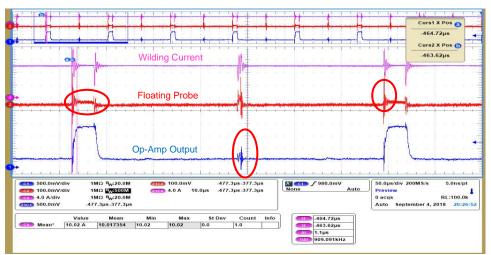

During the testing the ADC of the MCU samples the current sense amplifier output at the middle of phase A high side off period, which is falling near the IGBT switching of phase B, meaning the noise generated during the IGBT switching will couple to the current sense amplifier circuit. The radiated noise emission signal is captured by a floating probe close to the input path of the current sense amplifier, which 🕅 38 shows.

## 图 38. Floating Probe Close to Input Path of the Amplifier

39 shows the test results of noise effect on current sense amplifier, the floating probe near amplifier input shows DC shift and noise oscillation due to IGBTs switching. Noise is also observed on the amplifier output.

图 39. Noise Effect on Current Sense Amplifier

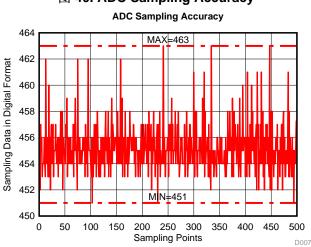

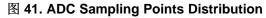

The ADC converts such 500 samples over 500 PWM cycles and stores them in the MCU data buffer. The data is analyzed to understand the effect of IGBT noise coupling on the current sense amplifier output.图 40 and 图 41 show the data analysis from ADC data in MCU. 图 40 shows the maximum error is 12 codes, which corresponds to 10-mV voltage error or 0.08-A error in measured current.图 41 shows the error distribution is 8 codes at 96.2% of 500 points. It turned out the noise observed on current sense amplifier output is actually due to probe pick up, and the output of the amplifier is quite stable even with IGBTs switching near by.

The integrated RFI and EMI filters at the input of the amplifier helps to reject the high-frequency noise coupled to the input of amplifier by nearby IGBT switching. A good PSRR of 7 µV/V, high CMRR and high stability of TLV9064 also contributes to the noise rejection on the input pins or output pins or the power supply.

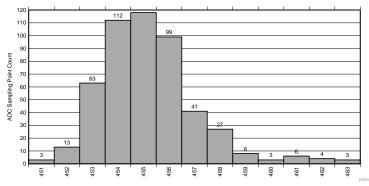

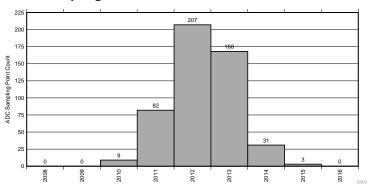

With the purpose of understanding the effect of error codes in the ADC result, due to the ADC reference voltage, a LDO with voltage ripple less than 5 mV is used to replace the DC/DC. 2 42 shows the ADC result distribution.

#### 图 42. ADC Sampling Points Distribution with LDO as Power Supply

The error variation when using a LDO as the power supply is 4 codes, which means the error of the output of the amplifier is effected by the ripple in the ADC reference which is divided from 3.3-V power supply. If the designer need more accurate ADC data, it is recommended to use a LC filter at the ADC reference voltage input.

#### 3.2.1.5 Overcurrent Protection in Hardware

As explained in  $\ddagger$  2.2.3, the inverter leg OCP is implemented by using one channel of the TLV9064 configured as a comparator and TLV1701 comparator.

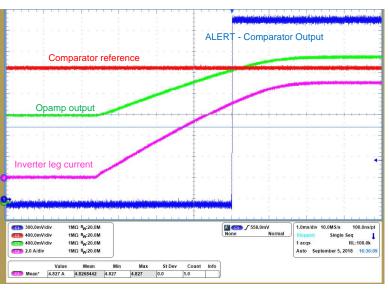

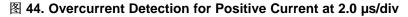

[X] 43 shows the overcurrent detection for the positive inverter leg current (positive inverter leg current refers to negative winding current). [X] 44 shows the response time for overcurrent detection and the response time is approximately 1.5 µs.

#### 图 43. Overcurrent Detection for Positive Current at 1.0 ms/div

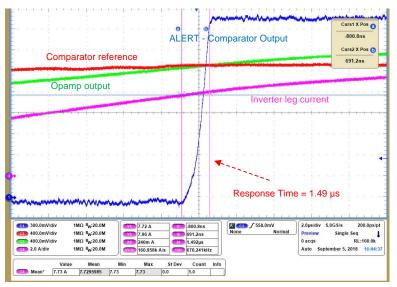

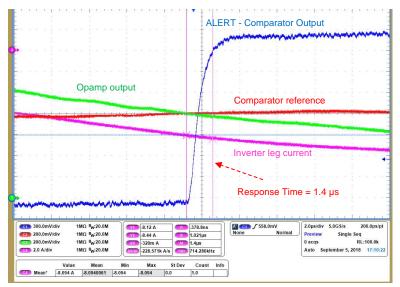

$\boxtimes$  45 shows the overcurrent detection for negative inverter leg current (positive inverter leg current refers to negative winding current).  $\boxtimes$  46 shows the response time for overcurrent detection and the response time is approximately 1.4  $\mu$ s.

#### 图 45. Overcurrent Detection for Negative Current at 1.0 ms/div

图 46. Overcurrent Detection for Negative Current at 2.0 ms/div

#### 图 47. Overcurrent Protection in Hardware

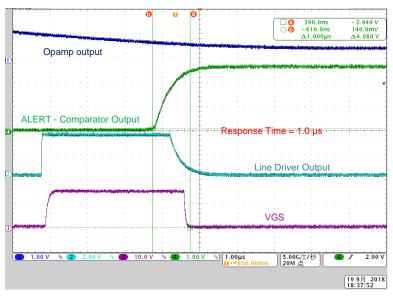

图 48. Response Time of Overcurrent Protection in Hardware

The response time of the overcurrent detection is less than 1.0  $\mu$ s in hardware protection, which is fast enough to protect an IGBT (IGBTs typically have more than a 5- $\mu$ s short-circuit capability). The lowest propagation delay of gate driver and line driver enables the fast turnoff of the IGBTs during an overcurrent event.

## 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-010023.

## 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-010023.

## 4.3 PCB Layout Recommendations

Use the following layout recommendations when designing the current sense layout.

- Use Kelvin connection for the sense resistor placement and sense voltage routing.

- The sense voltage signal connection to the amplifier must be connected using a symmetric differential trace routing.

- The recommended placement of the low-pass RC filter at the output of the amplifier is near the MCU.

- The recommended placement of the current sense amplifier input filter is close to the op amp.

- The creepage distance used for IGBT and gate driver layout is set within 4 mm.

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-010023.

#### 4.4 Altium Project

To download the Altium Designer® project files, see the design files at TIDA-010023.

## 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-010023.

## 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-010023.

## 5 Software Files

To download the software files, see the design files at MotorWare<sup>™</sup> Software.

#### 6 Related Documentation

- 1. Texas Instruments, Current Sensing With < 1-µs Settling for 1-, 2-, and 3-Shunt FOC Inverter Reference Design

- 2. Texas Instruments, Space-Vector PWM With TMS320C24x/F24x Using Hardware and Software Determined Switching Patterns Application Report

- 3. Texas Instruments, InstaSPIN-FOC™ and InstaSPINMOTION™ User's Guide

#### About the Author (Optional)

## 6.1 商标

E2E, MotorWare, Piccolo, InstaSPIN-FOC, Code Composer Studio are trademarks of Texas Instruments. Altium Designer is a registered trademark of Altium LLC or its affiliated companies. All other trademarks are the property of their respective owners.

## 7 About the Author (Optional)

**ZHILONG (BRYAN) LIU** is a system engineer at Texas Instruments, responsible for developing subsystem design solutions for the Industrial appliances systems. He has system-level product experience in analog and mixed-signal designs. Bryan earned his Bachelor of Technology in electrical and information engineering from Xidian University, and his Master of Technology in circuit and system from Xidian University.

**MANU BALAKRISHNAN** is a systems engineer at Texas Instruments where he is responsible for developing subsystem design solutions for the Industrial Motor Drive segment. Manu brings to this role his experience in power electronics and analog and mixed-signal designs. He has system-level product design experience in permanent magnet motor drives. Manu earned his bachelor of technology in electrical and electronics engineering from the University of Kerala and his master of technology in power electronics from National Institute of Technology Calicut, India.

#### 重要声明和免责声明

TI 均以"原样"提供技术性及可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证其中不含任何瑕疵,且不做任何明示或暗示的担保,包括但不限于对适销性、适合某特定用途或不侵犯任何第三方知识产权的暗示担保。

所述资源可供专业开发人员应用TI产品进行设计使用。您将对以下行为独自承担全部责任:(1)针对您的应用选择合适的TI产品;(2)设计、验证并测试您的应用;(3)确保您的应用满足相应标准以及任何其他安全、安保或其他要求。所述资源如有变更,恕不另行通知。TI对您使用所述资源的授权仅限于开发资源所涉及TI产品的相关应用。除此之外不得复制或展示所述资源,也不提供其它TI或任何第三方的知识产权授权许可。如因使用所述资源而产生任何索赔、赔偿、成本、损失及债务等,TI对此概不负责,并且您须赔偿由此对TI及其代表造成的损害。

TI所提供产品均受TI的销售条款 (http://www.ti.com.cn/zh-cn/legal/termsofsale.html) 以及ti.com.cn上或随附TI产品提供的其他可适用条款的约束。TI提供所述资源并不扩展或以其他方式更改TI 针对TI 产品所发布的可适用的担保范围或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司

#### 重要声明和免责声明

TI 均以"原样"提供技术性及可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证其中不含任何瑕疵,且不做任何明示或暗示的担保,包括但不限于对适销性、适合某特定用途或不侵犯任何第三方知识产权的暗示担保。

所述资源可供专业开发人员应用TI产品进行设计使用。您将对以下行为独自承担全部责任:(1)针对您的应用选择合适的TI产品;(2)设计、验证并测试您的应用;(3)确保您的应用满足相应标准以及任何其他安全、安保或其他要求。所述资源如有变更,恕不另行通知。TI对您使用所述资源的授权仅限于开发资源所涉及TI产品的相关应用。除此之外不得复制或展示所述资源,也不提供其它TI或任何第三方的知识产权授权许可。如因使用所述资源而产生任何索赔、赔偿、成本、损失及债务等,TI对此概不负责,并且您须赔偿由此对TI及其代表造成的损害。

TI所提供产品均受TI的销售条款 (http://www.ti.com.cn/zh-cn/legal/termsofsale.html) 以及ti.com.cn上或随附TI产品提供的其他可适用条款的约束。TI提供所述资源并不扩展或以其他方式更改TI 针对TI 产品所发布的可适用的担保范围或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司