# TI Designs: TIDA-01403

适用于热成像摄像机的 **74dB SNR**、10MSPS、14 位模拟前端 参考设计

# TEXAS INSTRUMENTS

### 说明

此参考设计在构建时考虑到了电子成像系统的一些要求。当今的图像传感器对 ADC 具有非常高的要求,具体表现在以下方面: 出色的线性度(DNL < 0.5LSB 并且 INL < 4LSB)、高分辨率(12 至 18 位)、高速(高达 20MSPS)和高 SNR (> 74dB SNR),以确保卓越的图像质量并且不会随着时间的推移而产生失真。该参考设计通过 TI 的低噪声高速放大器、全差分放大器(FDA)、高速 ADC 和低噪声 LDO 实现,演示了如何设计用于对热成像摄像机中的像素输出信号进行数字化的高性能模拟信号链。

### 资源

| TIDA-01403 | 设计文件夹 |

|------------|-------|

| TINA-TI    | 工具文件夹 |

| ADS4142    | 产品文件夹 |

| OPA2626    | 产品文件夹 |

| THS4551    | 产品文件夹 |

| TPS717     | 产品文件夹 |

|            |       |

咨询我们的 E2E 专家

### 特性

- 采样速度:针对 10MSPS 或更低速度进行了优化的 前端电路

- 模拟输入类型: 单极单端信号

- ADC 分辨率和满标量程 (FSR): 14 位和 2V<sub>PP</sub> 差分

- 输出数据接口: 1.8V 并行 CMOS 或 DDR LVDS

- 积分非线性 (INL) < 1LSB (典型值), 微分非线性 (DNL) < 0.5LSB (典型值)

- SNR、ENOB 和 THD: > 74dB、12 位和 < -84dB

- 总体功耗: < 80mW

### 应用

- 安全和监控: 热成像摄像机

- 医疗成像

- 测试和测量

- 车用夜视设备

- 航空航天与国防

System Description www.ti.com.cn

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

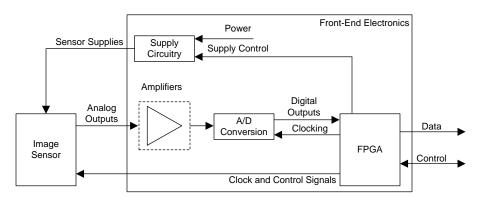

## 1 System Description

Virtually every imaging system includes an image sensor, AFE circuit, and digital signal processor (DSP). Every electronic imaging system starts with an image sensor. The AFE conditions the pixel-output signal from the image sensor in the analog domain and converts it to digital by employing an ADC. The digitized-pixel data is easily interfaced to a broad range of DSPs, including the DaVinci™ and Sitara™ processors from TI, with an integrated image pipe for enhanced video and image processing. As the interface between the analog core and DSP, ADCs are the second most performance-critical component in the complete-image signal-processing chain, after the image sensor. Image sensors of today force heavy demands on ADCs, in terms of excellent linearity (DNL < 0.5 LSBs and INL < 4 LSBs), high resolution (12 to 18 bits), high speed (up to 20 MSPS), and high SNR (> 74-dB SNR) to assure superior image quality and freedom from distortion over time.

The rich product portfolio of TI covers a broad spectrum of image-capture applications with diverse requirements. Portfolio offerings, reference-design support, product quality, and manufacturing excellence lets system designers customize imaging systems for specific applications with confidence. The imaging products from TI are optimized to work together, yet also let designers mix-and-match with third-party components when required. As modern imaging systems become more portable and compact, TI is committed to solving challenges that manufacturers face when designing these increasingly complex systems.

Enabled by the low-noise, high-speed amplifier, fully differential amplifier (FDA), high-speed ADC, and low-noise LDO from TI, this reference design demonstrates how to design a high-performance, analog-signal chain for thermal imaging cameras. This design guide was written to describe key system-performance requirements that are translated into the specifications of the signal-chain components, to achieve optimal performance by making correct choices. The scope of this TI reference-design subsystem is to give system designers a head start in designing the complete-image signal-processing chain responsible for digitizing the pixel-output signal from the sensor, using low-noise amplifiers and a high-speed sampling ADC with excellent linearity (DNL and INL), high SNR, and low distortion, giving superior imaging performance. This reference design provides a complete set of downloadable documents such as the comprehensive design guide, schematic, Altium PCB layout files, bill of materials (BOM), test results, and Gerber files, which aid system designers in the design and development of their end-equipment systems.

System performance requirements must be translated into the specifications of the key signal-path components, to achieve the best tradeoffs between performance, power consumption, size, and ease of use (see 表 1). The following subsections describe the various blocks within the TI reference-design system and what characteristics are most critical to best implementing the corresponding function.

www.ti.com.cn System Description

# 1.1 Key System Specifications

# 表 1. Key System Specifications

| PARAMETER                  | SPECIFICATION                                                                                     |

|----------------------------|---------------------------------------------------------------------------------------------------|

| Number of analog inputs    | One                                                                                               |

| Input range and type       | Unipolar, single-ended                                                                            |

| ADC full-scale input range | 2 V <sub>PP</sub> differential                                                                    |

| ADC architecture           | Pipeline                                                                                          |

| Resolution                 | 14 bit                                                                                            |

| SNR                        | > 74 dB using the DC-input histogram method                                                       |

| ENOB                       | > 12 bit                                                                                          |

| THD                        | < -84 dB                                                                                          |

| INL                        | < 1 LSB                                                                                           |

| DNL                        | < 0.5 LSB                                                                                         |

| Sampling frequency         | ADC can sample frequencies up to 65 MSPS, however, the AFE has been optimized for 10 MSPS or less |

| Operating voltage          | External supplies: 5.5-V DC and 3.3-V DC                                                          |

| Power consumption          | Approximately 80 mW                                                                               |

| Connector                  | One SMA connector for the analog input signal                                                     |

|                            | One SMA connector for the common-mode input voltage                                               |

|                            | Two SMA connectors for the single-ended or differential clock                                     |

|                            | One 40 x 2, Samtec connector for the data capture card                                            |

System Overview www.ti.com.cn

## 2 System Overview

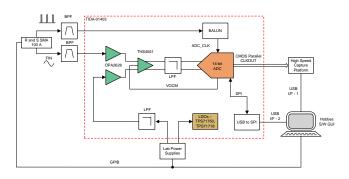

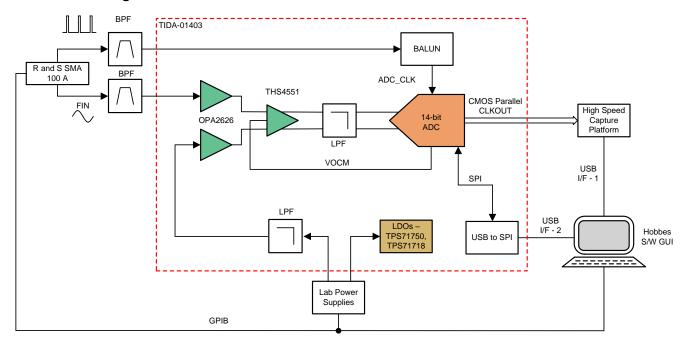

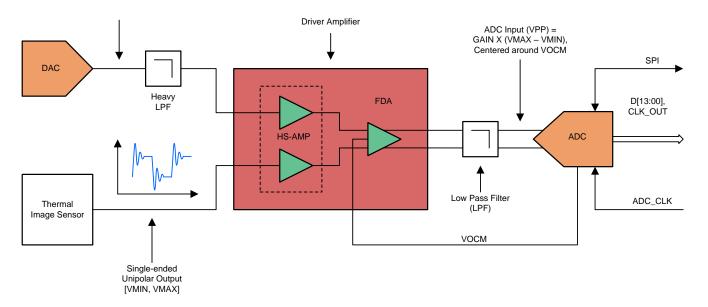

### 2.1 Block Diagram

# 2.2 Highlighted Products

At a high level, this reference-design subsystem consists of high-speed, low-noise, front-end amplifiers, a high-speed, 14-bit pipeline ADC, and power management devices. The high-speed ADC digitizes the conditioned analog-image signal to the digital domain, allowing for additional processing by a FPGA or DSP. The ADS4142 is a 14-bit, fully-differential, pipeline ADC (low-speed variant of the ADS41xx family), offering the advantages of good common-mode rejection and low-distortion products. In any imaging system, the AFE electronics must not be the limiting factor in performance, so for high-end imaging applications, a 14-bit ADC is necessary. One of the most common ways to drive a differential-input ADC is with a transformer. However, there are applications such as imaging systems, where the ADC cannot be driven with transformers, because the frequency response to the DC is also expected. Although an ADC can be driven single-ended, a fully-differential driver usually optimizes overall performance. The signal from the image sensor must be conditioned before being sent to the ADC. The front-end, ADC driver circuitry is basically a single-ended-to-differential conversion stage. In the front end there is the OPA2626, a high-speed, high-precision, low-noise amplifier presenting high-input impedance to the output of the sensor, followed by the THS4551, a high-speed, precision, low-noise FDA, providing low impedance and fast-signal settling when differentially driving ADC inputs. The TIDA-01403 design features the following devices.

### 2.2.1 ADS4142

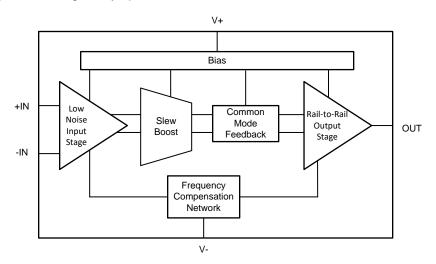

The ADS412x and ADS414x devices are lower-sampling, speed variants in the ADS41xx family of ADCs (see ☑ 1). These devices use innovative design techniques to achieve high-dynamic performance, while consuming extremely low power at 1.8-V supply. The devices are well suited for multicarrier, widebandwidth, communication applications.

www.ti.com.cn System Overview

The ADS412x and ADS414x devices have fine-gain options that can be used to improve SFDR performance at lower full-scale input ranges, especially at high-input frequencies. They include a DC-offset correction loop that can be used to cancel the ADC offset. At lower sampling rates, the ADC automatically operates at scaled-down power with no loss in performance.

The ADS412x and ADS414x devices are available in a compact, VQFN-48 package and are specified over the industrial temperature range (–40°C to +85°C). The ADS412x and ADS414x devices have the following features:

- Ultra-low power with 1.8-V single supply:

- 103-mW total power at 65 MSPS

- 153-mW total power at 125 MSPS

- High-dynamic performance:

- SNR: 72.2 dBFS at 170 MHz

- SFDR: 81 dBc at 170 MHz

- Dynamic power scaling with sample rate

- Idle channel SNR: 74.8 dBFS (ADS414x)

- Output interface:

- Double data rate (DDR), LVDS with programmable swing and strength:

- Standard swing: 350 mV

- Low swing: 200 mV

- Default strength: 100-Ω termination

- 2x strength: 50-Ω termination

- 1.8-V parallel CMOS interface also supported

- Programmable gain up to 6 dB for SNR, SFDR trade-off

- DC offset correction

- Supports low-input clock amplitude, down to 200 mV<sub>PP</sub>

图 1. ADS41xx Block Diagram

System Overview www.ti.com.cn

### 2.2.2 OPA2626

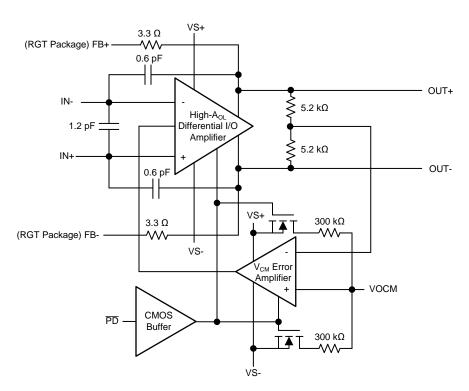

The OPAx626 family of operational amplifiers (op amps) are 16-bit and 18-bit, high-precision, successive-approximation register (SAR), ADC drivers, with low total harmonic distortion (THD) and noise (see ② 2). This family of precision op amps is fully characterized and specified with a 16-bit settling time of 280 ns that enables a true 16-bit effective number of bits (ENOB). With a high-DC precision of only 100-µV offset voltage, a wide gain-bandwidth product of 120 MHz, and a low-wideband noise of 2.5 nV/√Hz, this family of devices is optimized for driving high-throughput, high resolution, SAR ADCs, in applications such as the ADS88xx family of SAR ADCs.

The OPAx626 family is available in 5-pin SOT and 8-pin VSSOP packages and is specified for operation from –40°C to +125°C. The OPAx626 family has the following features:

- Excellent dynamic performance:

- Low distortion: -122 dBc for HD2 and -140 dBc for HD3 at 100 kHz

- Gain bandwidth (G = 100): 120 MHz

- Slew rate: 115 V/µs

- 16-bit settling at 4-V step: 280 ns

- Low-voltage noise: 2.5 nV/√Hz at 10 kHz

- Low-output impedance: 1  $\Omega$  at 1 MHz

- Excellent DC precision:

- Offset voltage: ±100 µV (maximum)

- Offset voltage drift: ±3 μV/°C (maximum)

- Low-quiescent current: 2 mA (typical)

- Input common-mode range includes negative rail

- · Rail-to-rail output

- Wide temperature range: fully specified from –40°C to +125°C

图 2. OPAx262 Functional Block Diagram

www.ti.com.cn System Overview

### 2.2.3 THS4551

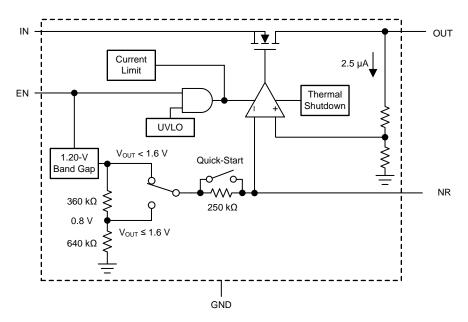

The THS4551 fully-differential amplifier (see 🛭 3) offers an easy interface, from single-ended sources to the differential output required by high-precision ADCs. Designed for exceptional DC accuracy, low noise, and robust capacitive-load driving, this device is well suited for data-acquisition systems where high precision is required, along with the best SNR and spurious-free dynamic range (SFDR), through the amplifier and ADC combination.

The THS4551 device features the negative-rail input required when interfacing a DC-coupled, ground-centered, source signal to a single-supply, differential-input ADC. Low DC error and drift terms support the emerging 16- to 20-bit SAR input requirements. A wide-range, output common-mode control supports the ADC running from 1.8-V to 5-V supplies, with ADC common-mode input requirements from 0.7 V to greater than 3.0 V.

The THS4551 device is characterized for operation over the wide temperature range of –40°C to +125°C, and is available in 8-pin VSSOP, 16-pin VQFN, and 10-pin WQFN packages. The THS4551 device has the following features:

- Bandwidth: 150 MHz (G = 1 V/V)

- Differential output slew rate: 220 V/µs

- Gain bandwidth product: 135 MHz

- Negative rail input (NRI), rail-to-rail output (RRO)

- · Wide-output common-mode control range

- Single-supply operating range: 2.7 V to 5.4 V

- Trimmed-supply current: 1.37 mA at 5 V

- 25°C input offset: ±175 μV (maximum)

- Input offset voltage Drift: ±1.8 μV/°C (maximum)

- Differential input voltage noise: 3.3 nV/√Hz

- HD2: –128 dBc at 2 V<sub>PP</sub>, 100 kHz

- HD3: –139 dBc at 2 V<sub>PP</sub>, 100 kHz

- < 50-ns settling time: 4-V step to 0.01%</li>

- 18-bit settling time: 4-V step, < 500 ns</li>

System Overview www.ti.com.cn

图 3. THS4551 Functional Block Diagram

### 2.2.4 TPS717xx

The TPS717 family of low-dropout (LDO), low-power, linear regulators offers high power-supply rejection (PSRR), while maintaining low, 45- $\mu$ A ground current in an ultra-small, five-pin, SOT package (see § 4). The family uses an advanced BiCMOS process and a PMOS pass device to achieve fast start-up, low noise, excellent transient response, and excellent PSRR performance. The TPS717 device is stable with a 1- $\mu$ F ceramic output capacitor and uses a precision voltage reference and feedback loop to achieve a worst-case accuracy of 3% over all load, line, process, and temperature variations. The device family is fully specified from T $_J$  =  $-40^{\circ}$ C to 125°C and is offered in a small SOT (SC70-5) package, a 2-mm × 2-mm WSON-6 package with a thermal pad, and a 1.5-mm × 1.5-mm WSON-6 package, which are ideal for small form factor portable equipment (such as wireless handsets and PDAs). The TPS717xx device has the following features:

- Input voltage: 2.5 V to 6.5 V

- Available in multiple output versions:

- Fixed output with voltages from 0.9 V to 5 V

- Adjustable output voltage from 0.9 V to 6.2 V

- · Ultra-high PSRR:

- 70 dB at 1 kHz, 67 dB at 100 kHz, and 45 dB at 1 MHz

- Excellent load and line transient response

- Low dropout: 170 mV at 150 mA (typical)

- Low noise: 30 μV<sub>RMS</sub> (typical), 100 Hz to 100 kHz

- Small 5-pin SC-70, 2-mm x 2-mm WSON-6, and 1.5-mm x 1.5-mm WSON-6 packages

图 4. TPS717xx Functional Block Diagram

# 3 System Design Theory

Usually, image-sensor manufacturers may not be experts in designing ADCs. Consequently, sometimes ADC manufacturers are not aware of the critical requirements that ADCs must satisfy for pixel output digitization. Improving the speed and resolution of ADCs sometimes requires performance tradeoffs, and these tradeoffs must be made in favor of the imaging applications. Typically, any ADC is used in one of three modes of operation: DC conversion, multiplexing (time domain), and signal reconstruction (frequency domain). Before proceeding further, it is important to understand how an electronic-imaging system differs from signal-reconstruction applications. Focal plane arrays (FPA) used in IR-imaging applications typically output single-ended, ground-referenced, signal-containing pixel information that is read pixel-by-pixel by the read out integrated circuit (ROIC). Therefore, analog-video output of an image sensor is not a continuous, periodic waveform. The output is actually a pseudo-DC waveform that resembles a series of steps with different amplitudes. The characteristics of such a video waveform dictate time rather than frequency. The ADC samples the analog-video signal only during the relatively slow-moving portion of the waveform, preferably in the end when the pixel is most settled. Therefore, electronic imaging differs from signal reconstruction applications, because it is strictly a multiplexed-input time-domain data-acquisition application. That characteristic means a designer should not focus more on optimizing the THD, which is a frequency-domain specification. A high-THD specification is irrelevant for most of the imaging applications. In time-domain applications, spectral purity is not that important. The AFE circuit is the crucial link for establishing and maintaining good system performance. The design of an AFE circuit, for an imaging application, depends on many factors, like the type of sensor being used, dynamic range, image resolution, speed, noise performance, power consumption, and form-factor requirements. 8 5 shows the basic architecture of the electronics of a camera.

图 5. Basic Architecture of Camera Electronics

The linearity of the AFE can impact the imaging system performance. The nonlinearities of a real ADC can cause artifacts in the digitized image, which are easily noticeable to human eyes. The human-vision system has excellent edge, or discontinuity-detection capability, and therefore can pick-up different geometric shapes quite comfortably. In imaging applications, the AFE must be designed while keeping in mind the capabilities of the human-vision system. Improper selection of the ADC and the driver amplifiers in imaging applications may create edges or discontinuities that do not exist or eliminate edges that do exist, and our eyes can spot such artifacts instantly. Therefore, an imaging system must do the following:

- Not introduce discontinuities where they do not exist in the scene more related to selection of the ADC

- Preserve discontinuities wherever they exist in the scene more related to selection of driver amplifier circuitry

### 3.1 Selecting an ADC

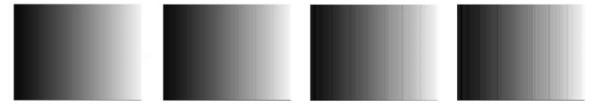

An imaging system must not introduce discontinuities where they do not exist in the scene – This requirement is more related to the nonlinearity of the ADC. ADCs, by nature, add discontinuities (DNL and INL). It is difficult to predict how ADC nonlinearity impacts final imagery, due to the strong dependence on scene details. Therefore, to surface any impact due to ADC imperfections, electronic-imaging systems are tested or calibrated with a continuous-tone wedge, which is a gradual linear excursion of gray tones from white to black or black to white (see

6). The DNL of the ADC is the most critical specification for imaging, because a DNL error results in edge distortion. In an ideal converter, the step width or analog increment of each conversion value is the same, and the DNL is zero. Such an ideal converter would translate increasing light intensity into digital values that an ideal D/A converter could reconvert to resemble perfectly stepped wedges of increasing intensity. If the DNL is not zero, then each step has a different width. This imperfection affects intensity fidelity and causes improper gradation of the image scale with local imperfections. A large, positive DNL error would look like a flat spot, where color stays the same for many stepped wedges. A large, negative DNL error would look like a sudden color jump. A DNL error greater than 0.5 LSB usually creates objectionable artifacts.

图 6. Smooth Gradient Scene With Increasing DNL Error

In addition, small DNL values can add to a significant error in INL. Erroneous INL corrupts the entire image scale with a gradual nonlinearity. The human eyes are generally less sensitive to this type of error than to DNL-induced edge problems. However, more INL errors results in color artifacts that may cause deceptive results. The detector was placed in front of a black body with uniform temperature, and images were captured with different ADCs with INL specifications from 1 LSB to 5 LSB. An INL error greater than 3 LSB creates noticeable color artifacts.

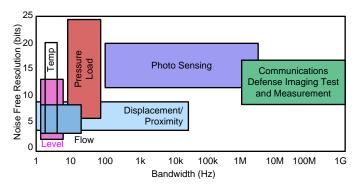

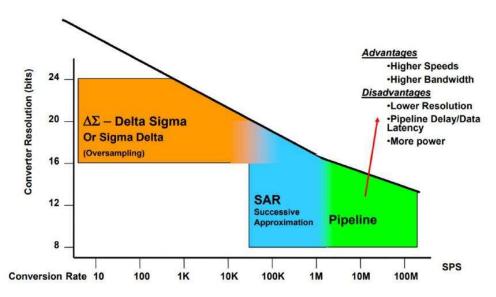

Not all ADCs are created equal. There are different architectures to accomplish the task. Different architectures bring different strengths and weaknesses and lend themselves to the optimization of different applications. With ADCs, as with any circuit, designers face many tradeoffs. The ADC is a performance-critical component in the image-signal processing chain. To establish accurate and detailed images of scanned objects, these applications employ larger arrays with more pixels and longer frame-update times. The ADC must provide high resolution with excellent linearity, low noise, low drift, and low offset. All this performance is necessary to assure image quality, color purity, and freedom from distortion over time. The pipelined ADC is the architecture of choice for imaging applications, because pipeline ADCs provide an optimum balance of noise, linearity, speed, resolution, power dissipation, and size.

图 7. Noise-Free Resolution Versus Bandwidth

图 8. Converter Resolution Versus Conversion Rate

With the system specifications provided, designers can begin working on the center of the input-signal path — the ADC. Key specifications and properties identified for a high-speed ADC follow:

- ADC channels: Number of channels must be equal to the number of video outputs in the image sensor. Generally, image sensors up to QVGA resolution come with only one video output.

- **Need for speed:** Sampling rate must be greater than the sensor resolution (M × N) times the frame rate (frames per second). For a QVGA-resolution (320 × 240 pixels) sensor with a 100-Hz frame rate, the sampling rate is greater than 320 × 240 × 100 = 7.68 MSPS.

- SNR: Noise generated within the AFE circuitry directly affects the dynamic range of the imaging system. Therefore, the SNR of the ADC must be 6 to 10 dB greater than the SNR of the image sensor. If the SNR of an image sensor is unknown, the SNR of the ADC must be 10 dB higher than the dynamic range (DR) of the image sensor. For an image sensor with a DR of 1.25 mV<sub>PP</sub> to 2 V<sub>PP</sub> or 64 dB, the minimum SNR of the ADC must be 74 dB (64 dB + 10 dB).

- Resolution of ADC: Most of the image-processing algorithms output 8 to 10 bits for the display. Therefore, the resolution of the ADC must be 2 to 4 bits greater than the number of bits in the final image after digital image processing. Advanced, digital, image-processing algorithms require more bits from the ADC, allowing extra headroom in image manipulation and editing, ensuring minimal loss of image integrity. The more bits in a camera, the smoother the digitization process. More bits also mean higher accuracy and more information. With enough bits, the human eye can no longer determine the difference between a continuous grayscale and its digital representation. Continuing deeper, the effective resolution (ENOB) of the ADC should be such that it digitizes the entire DR (see 公式 1).

$$DR = 10^{\frac{DR(dB)}{20}} = 10^{\frac{64 dB}{20}} = 1585$$

$$ENOB = log_2(DR) = log_2(1585) = 10.6 \text{ bit}$$

(1)

In this case, the resolution of the ADC must be higher than the ENOB (10.6 bits), considering the noise introduced by the analog signal-processing circuitry and digitization process. Designers may also want to keep the maximum signal from the sensor smaller than the ADC full scale range (FSR), to avoid clipping anywhere is the signal path. This step helps in eliminating the risk of overdrive. A 12-bit ADC

cannot meet the SNR requirement. With all of this considered, a 14-bit ADC with 74-dB SNR or greater is a good choice for high-end imaging applications.

- DNL: DNL of the ADC must be less than 0.5 LSBs

- INL: INL of the ADC must be less than 3 LSBs

- **Low-power consumption:** In general, AFE circuitry is placed close to the image sensor, inside a closed camera housing. Heat generated by the AFE may interfere with IR energy coming in through the lens from the scene. Therefore, power consumption of the design must be minimized.

- Small package: Security cameras are compact. Space is always a challenge. Sometimes, it is

possible that an ADC with the best specifications cannot be used, simply because it has a bigger

package.

Go to www.ti.com to see ADC options.

TI Home → Data Converters → Analog-to-Digital Converters (ADCs) → High Speed ADCs (> 10 MSPS)

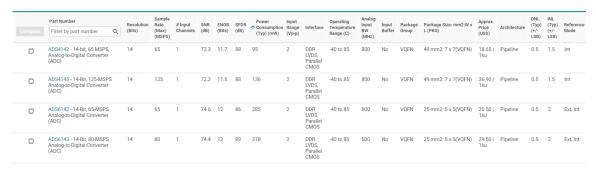

图 9. ADC Selection

The ADS4142 device meets all the necessary requirements – linearity, speed, and accuracy. The ADS4142 device is a 14-bit, 65-MSPS, pipeline ADC, which operates from 1.8-V analog and 1.8-V digital power supplies with low-power consumption of 65 mW at 10 MSPS. The ADS4142 device is a single-channel ADC that has the same, excellent, 14-bit performance and low power, with parallel outputs that can simplify the FPGA code required to collect data. The ADS4142 device gives users the flexibility to include the choice of CMOS or DDR LVDS outputs, with programmable digital-output timing and LVDS drive strength. The ADS4142 device is available in a RoHS compliant, 7 mm × 7 mm, QFN48 package. The ADS4142 device has additional specifications that are important to note as the rest of the signal path is designed. First, the input characteristics of the ADC. Its full-scale differential-input range is 2 V<sub>PP</sub>, common-mode voltage (VCM) is 0.95 V, and differential-input capacitance is 4 pF. The ADS4142 device uses differential inputs to reject common-mode noise and interference, increase DR, and improve overall performance due to balanced signaling.

### 3.2 Selecting the Amplifiers

An imaging system must preserve discontinuities wherever they exist in the scene – This requirement is more related to the step response of ADC-input circuitry (including the front-end amplifier, if any). As already discussed, the video output of the sensor is a pseudo-DC signal. Therefore, it is possible to encounter a full-scale change between adjacent pixels (or two consecutive conversions). The frequency content of the resulting waveform can greatly exceed the Nyquist frequency derived from the ADC sampling rate. These high-frequency contents in the waveform do not contain any information of interest, but must be processed by the front-end amplifier and input circuitry of the ADC. The insufficient BW and slew rate of the amplifier and ADC input circuitry may result in degradation of the system performance.

The signal must settle within 0.5 LSB at the input of the ADC for the worst-case, full-scale change in the given sampling period. This condition is critical to maintain the overall linearity performance of the ADC. Typically, amplifier data sheets specify output-settling performance only from 0.1% to 0.01%, which may not be sufficient for high-resolution converters (> 14 b). Therefore, the designer must verify the input-driver settling behavior, with simulators such as TINA-TI, to assist in amplifier selection.

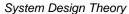

The ADC AFE circuitry must be designed to complement the performance of the ADC and mainly consists of two parts: a driving amplifier and a flywheel RC filter, as shown in 图 10. Important functions in this key block include:

- Filtering to remove unwanted high-frequency signals

- Low-output impedance, which provides a buffer between the signal source and the ADC input

- Single-ended to differential conversion

- Amplification, to match signal levels to the ADC-input range

- · Level shifting, to match the ADC common-mode input level

Select components which minimize the component count in this block. The next step is to look at one of the more demanding requirements for the analog signal-processing block – optimizing the bandwidth of the circuit. This design uses a simple, passive, single-pole, low-pass filter between the amplifier stage and ADC. The filter bandwidth is primarily driven by the following requirements:

- The RC-filter bandwidth must be low enough to band-limit the noise fed into the input of the ADC, thereby increasing the SNR of the system.

- The overall system bandwidth must be large enough to accommodate optimal settlings of the input signal at the ADC input before the start of the conversion.

Generate voltage from DAC or lab power supply VCMI = (VMAX + VMIN)/2

图 10. Conceptual Schematic of AFE Circuit for IR Imaging Applications

The settling time available to the amplifier may not equal an entire clock cycle. The source may dictate this, but there is a disturbance produced by the ADC on the opposite edge of the clock, and this event gives the filter only a  $\frac{1}{2}$ -clock cycle to settle, even if the amplifier is not otherwise disturbed. If the amplifier is disturbed by this event, it does not leave as much time for the filter to settle. Theoretically, a simple RC requires about 10.4 time constants to settle to 14 bits, and for 10 MSPS, it results in a bandwidth of about 33 MHz.  $\frac{1}{2}$  gives the step response of the simple, first-order system for the worst-case full-scale change ( $\frac{1}{2}$ V).

$$v_{ADC}\left(t\right) = \pm \, \Delta V \left(1 - e^{-2\pi BWt}\right)$$

### where

BW is the 3-dB bandwidth of the system.

The settling error at the end of the ½-clock cycle (t = Ts / 2) is  $\Delta V - 0.5$  LBS, see  $\Delta \vec{x}$  3.

$$BW \geq \frac{In\left(2^{N+1}\right)}{\pi Ts} = \frac{In\left(2^{N+1}\right)}{\pi} \times Fs = \frac{In\left(2^{14+1}\right)}{\pi} \times 10 \ \text{MHz} = ~~33.112 \ \text{MHz}$$

$$BW \geq ~~33.112 \ \text{MHz}$$

#### where

- · Ts is the sampling period.

- Fs is the sampling frequency.

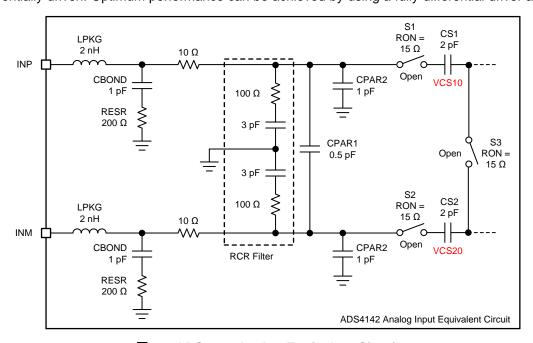

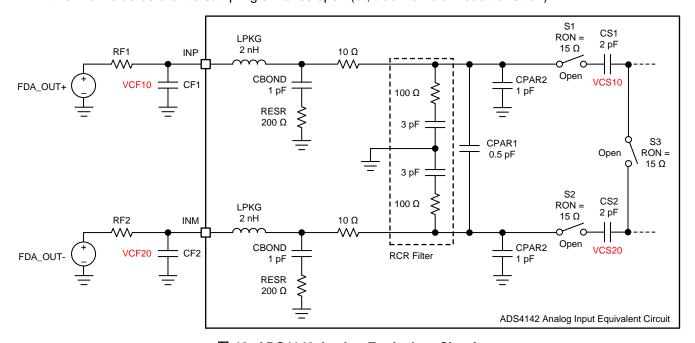

₹ 11 shows the equivalent circuit for the analog input of the ADS4142 device, consisting of a switched-capacitor-based, differential, sample-and-hold architecture. The INP and INM pins must be externally biased around a common-mode voltage of 0.95 V, available on the VCM pin. For a full-scale differential input, each input, the INP and INM pins, must swing symmetrically between (VCM + 0.5 V) and (VCM − 0.5 V), resulting in a 2-V<sub>PP</sub>, differential-input swing. The input-sampling circuit has a full-power bandwidth that extends up to 550 MHz (measured from the input pins to the sampled voltage). Although the input structure of the ADS4142 device is completely differential, this ADC can be either single-ended or differentially driven. Optimum performance can be achieved by using a fully-differential driver amplifier.

图 11. ADS4142 Analog Equivalent Circuit

(2)

(3)

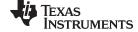

The two distinctive stages to ADC operation are the track and hold phases. In the track phase, the sampling switches S1, S2, and S3 are closed and the sampling capacitors (CS1 and CS2) track the input signal with a certain RC-time constant. During the next clock phase (or the hold phase), the sampling switches S1, S2, and S3 are open and the sampling capacitors (CS1 and CS2) are held at the constant value of the input signal, that ideally corresponds to the last value of the track instant. These sampling switches (S1, S2, and S3) open or close at the sampling frequency (Fs), as shown in  $\boxtimes$  12.

图 12. Sampling Switches S1 and S2

The ADC takes the sample of the input signal at the rising edge of the sampling clock, also known as track-to-hold mode transition. In \$\mathbb{B}\$ 14, all the pixel outputs are time-multiplexed to the input of a global ADC to provide the digital output. The sensor output changes soon after the ADC takes a sample. The input of the driver amplifier may see a full-scale change between adjacent pixels immediately after the track-to-hold mode transition. When the ADC enters the hold phase, the sampling capacitor is not tracking the input signal. During this time, it is a good opportunity for the output of the driver amplifier to quickly settle and start acting like a DC source. Considering the correct sampling process, output of the driver-amplifier stage must continue to act like a DC source throughout the track phase. At the hold-to-track mode transition, the sampling switches reconnect to the source to recharge the sampling capacitors to a new value, by the external filter capacitors. This results in charge kick-back transients at the input of the ADC, as \$\mathbb{B}\$ 14 shows. This occurrence is the most critical moment that determines the accuracy of the design, because the voltage across the sampling capacitors must settle to a \$\pmu\$0.5-LSB error band around the final value before the sampling switches open (or, track-to-hold mode transition).

图 13. ADS4142 Analog Equivalent Circuit

$$\Delta V = \frac{C_{S1}}{C_{F1} + C_{S1}} \times \left( V_{CF10 - V_{CS10}} \right) = \frac{1}{\frac{C_{F1}}{C_{S1}} + 1} \times \left( V_{CF10} - V_{CS10} \right)$$

(4)

A higher ratio between the input capacitor and sampling capacitor produces a smaller voltage drop. The input capacitor, CF, helps to reduce the kickback noise at the ADC input and provides a charge bucket to quickly charge the sampling capacitor during the track phase. The value of CF must be chosen such that the voltage droop ( $\Delta V$ ) on the external filter capacitor is less than 10% of the input voltage. Therefore, the generalization given in  $\Delta \vec{x}$  4 can be used to estimate the necessary size of the external capacitor, CF.

- C<sub>F</sub> ≥ 15 C<sub>S</sub>

- $C_{F1}$  and  $C_{F2} \ge 33 \text{ pF}$

For low distortion, the external filter capacitors (CF1 and CF2) must be a C0G or NP0 type. C0G-type capacitors exhibit minimal change in capacitance over input voltage, frequency, temperature, and so on, and are typically available in values of 10 nF or less. Thus, a C0G-type capacitor with a value of CF1 and CF2 = 33 pF is selected for this TI reference design. At this point, it is important to understand the tradeoffs involved in selecting the values of CF and RF. If the value of CF is high, it provides better attenuation against kickback noise when the sampling switches are closed. However, CF cannot be made arbitrarily high, because it degrades the phase margin of the driving amplifier, thus making it unstable. The series resistor, RF, acts as an isolation resistor, which helps to stabilize the driving amplifier. A higher value of RF is helpful from the amplifier stability perspective, but it degrades AC performance and must be balanced with the amplifier stability, to ensure that the distortion does not exceed the required specifications. Distortion happens due to the nonlinear input impedance of the ADC, and it increases with source impedance, input signal frequency, and amplitude. The maximum value of RF depends upon the fact that by the end of the track phase (TS/2), the sampling capacitor (CS) must be charged to an acceptable level of the measured input voltage. That statement means the signal must settle within 0.5 LSB at the input of the ADC for the worst-case, full-scale change at the end of acquisition time. 公式 5 gives the value of the required external-filter resistance.

$$(R_F + R_{SH}) \times (C_F + C_S) \le \frac{t_{TRACK}}{k1}$$

where

- k1 is number of time constants for the kick-back transient to settle, as defined in 公式 7.

- R<sub>SH</sub> represents the total series resistance from the ADC input pin to the sampling capacitor.

$$k1 = ln \left( \frac{\left(V_{IN} - V_{CSH0}\right)}{\left(1 + \frac{C_F}{C_S}\right)} \times 2^{(N+1)} \right)$$

(6)

For this design, the values of the parameters used in 公式 6 follow:

- $t_{TRACK} = 50 \text{ ns}$

- C<sub>F</sub> = 27 pF

- C<sub>s</sub> = 2 pF

- $V_{INP} = V_{CM} + 0.5 \text{ V}$

- $V_{CSH0} = V_{CM} 0.5 \text{ V}$

- V<sub>FSR</sub> = 1 V

- N = 14

- RSH =  $10 \Omega + 15 \Omega + 7.5 \Omega = 32.5 \Omega$

(5)

After inserting these values in  $\triangle$ 式 6, RF should be less than 200  $\Omega$ . The minimum value for RF depends on the output impedance of the amplifier, based on stability considerations. First select the driver amplifiers and then use the TINA simulations to further refine the values of the filter components.

www.ti.com.cn

图 14. Waveforms at Different Stages in the Signal Chain

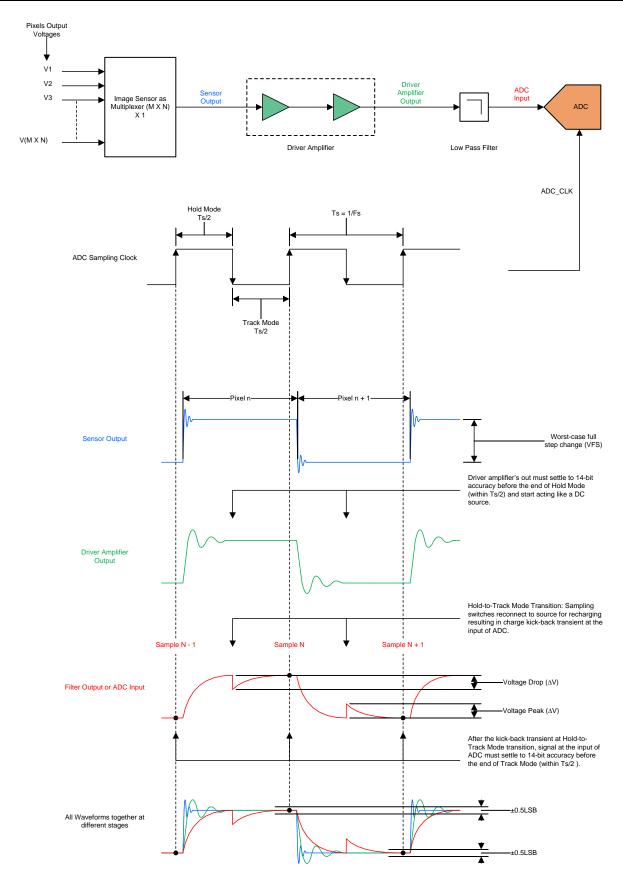

The process of selecting suitable amplifiers for driving the high-speed ADC with differential inputs may be a challenging task. Multiplexed applications, such as pixel-by-pixel reading in imaging systems, exercise the slewing capability and bandwidth capability of the driving amplifier. Bandwidth and slew rate requirements are significantly increased by operating in a multiplexed mode, and care must be taken in selecting a component for this application. The settling time of an amplifier mainly consists of dead time, slew time, recovery time, and linear settling time, as shown in  $\boxtimes$  15.

图 15. Settling Time

In 图 15, the high-speed amplifier (HS-AMP), FDA, and filter must settle to 0.5 LSB for a worst-case, full-step change (VFSR) within a given sampling period. Assuming each stage is a simple, first-order system, then 公式 7 can give the number of time constants (k2) required for N-bit settling.

$$k2 = (N + 1) \ln 2$$

where

· N is the resolution of the ADC.

When the amplifier is out of slew, and if the input is not changing significantly, then the amplifier perceives the input as small signal. Therefore, 公式 8 and 公式 9 give the individual settling times of the HS-AMP, FDA, and filter.

(7)

$$t_{HS-AMP} = \frac{\Delta V}{SR_{HS-AMP}} + \frac{k}{2\pi \times SSBW_{HS-AMP}}$$

where

- t<sub>HS-AMP</sub> is settling time of the HS-AMP.

- SR<sub>HS-AMP</sub> is slew rate of the HS-AMP.

$$t_{FDA} = \frac{\Delta V}{SR_{FDA}} + \frac{k}{2\pi \times SSBW_{FDA}}$$

where

- t<sub>EDA</sub>is settling time of the HS-AMP.

- SR<sub>FDA</sub>is slew rate of the HS-AMP.

- SSBW<sub>FDA</sub> is small-signal bandwidth of the FDA.

For a cascaded configuration, 公式 10 gives a close approximation of the overall settling time.

Settling Time of Driver Amplifier =

$$t_{Settling} = \sqrt[2]{t_{HS-AMP}^2 + t_{FDA}^2}$$

(10)

The settling time of the driver amplifier should be smaller than the duration of the hold phase ( $T_s/2$ ), as given in  $\Delta \vec{x}$  11.

$$t_{\text{Settling}} < \frac{T_{\text{S}}}{2} = \frac{100 \text{ ns}}{2} = 50 \text{ ns}$$

(11)

Now, select the HS-AMP and FDA such that 公式 11 is satisfied.

Go to www.ti.com to find a FDA (see 图 16).

TI Home → Amplifiers → Operational Amplifiers (Op Amps) → Fully Differential Amplifiers

| Compare | Part Number  Filter by part number Q                                                                                        | Number<br>of<br>Channels<br>(#) | Total<br>Supply<br>Voltage<br>(Min)<br>(+5V=5,<br>+/-5V=10) | Total<br>Supply<br>Voltage<br>(Max)<br>(+5V=5,<br>+/-5V=10) | BW @<br>AcI<br>(MHz) | Acl,<br>min<br>spec<br>gain<br>(V/V) | Slew<br>Rate<br>(Typ)<br>(V/us) | Vn at Flatband (Typ) (nV/rtHz) | Iq per<br>channel<br>(Typ)<br>(mA) | Rail-<br>to-<br>Rail   | Vos<br>(Offset<br>Voltage<br>@ 25C)<br>(Max)<br>(mV) | Rating       | Operating<br>Temperature<br>Range (C) | Package<br>Group       | Approx.<br>Price<br>(US\$) | Output<br>Current<br>(Typ)<br>(mA) | 2nd<br>Harmonic<br>(dBc) | 3rd<br>Harmonic<br>(dBc) | Package Size: mm2:W x L<br>(PKG)                                       |

|---------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|----------------------|--------------------------------------|---------------------------------|--------------------------------|------------------------------------|------------------------|------------------------------------------------------|--------------|---------------------------------------|------------------------|----------------------------|------------------------------------|--------------------------|--------------------------|------------------------------------------------------------------------|

| 0       | THS4551 - Low Noise,<br>Precision, 150MHz, Fully<br>Differential Amplifier                                                  | 1                               | 2.7                                                         | 5.4                                                         | 150                  | 1                                    | 220                             | 3.3                            | 1.35                               | In<br>to<br>V-,<br>Out | 0.175                                                | Catalog      | -40 to 125                            | QFN,<br>VQFN,<br>VSSOP | 1.39  <br>1ku              | 45                                 | 128                      | 139                      | 4 mm2: 2 x 2(QFN),<br>9 mm2: 3 x 3(VQFN),<br>15 mm2: 4.9 x 3(VSSOP)    |

|         | THS4531 - Ultra low power<br>0.25mA, RRO, fully differential<br>amplifier                                                   | 1                               | 2.5                                                         | 5.5                                                         | 36                   | 1                                    | 220                             | 10                             | 0.25                               | Out                    | 1                                                    | Catalog      | -40 to 125                            | QFN,<br>SOIC,<br>VSSOP | 1.32  <br>1ku              | 26                                 | 128                      | 137                      | 4 mm2: 2 x 2(QFN),<br>29 mm2: 6 x 4.9(SOIC),<br>15 mm2: 4.9 x 3(VSSOP) |

|         | THS4531A - Ultra Low Power,<br>RRO, Fully-Differential Amplifier                                                            | 1                               | 2.5                                                         | 5.5                                                         | 36                   | 1                                    | 220                             | 10                             | 0.25                               | In<br>to<br>V-,<br>Out | 0.4                                                  | Catalog      | -40 to 125                            | QFN,<br>SOIC,<br>VSSOP | 1.10  <br>1ku              | 26                                 | 129                      | 138                      | 4 mm2: 2 x 2(QFN),<br>29 mm2: 6 x 4.9(SOIC),<br>15 mm2: 4.9 x 3(VSSOP) |

|         | THS4521-HT - High<br>Temperature, Very Low Power,<br>Negative Rail Input, Rail-to-Rail<br>Output, Differential Amp - Hi-Rel | 1                               | 2.5                                                         | 3.6                                                         | 40.7                 | 1                                    | 39                              | 19.95                          | 1.1                                | In<br>to<br>V-,<br>Out | 11.5                                                 | High<br>Temp | -55 to 175,<br>-55 to 210             | CFP,<br>SOIC           |                            | 33                                 | 96                       | 91.5                     | See datasheet (CFP),<br>29 mm2: 6 x 4.9(SOIC)                          |

图 16. High-Speed, Fully-Differential Amplifier Comparison

Go to www.ti.com to find a HS-AMP (see \bigsepace 17).

TI Home → Amplifiers → Operational Amplifiers (Op Amps) → High-Speed Op Amps (GBW ≥ 50MHz)

(9)

|   | Part Number                                                                                             | Number          | Architecture           | Total<br>Supply<br>Voltage    | Total<br>Supply<br>Voltage    | BW @  | Acl,<br>min<br>spec | Slew<br>Rate    | Vn at<br>Flatband  | Vn at 1kHz         | Iq per<br>channel | Vos<br>(Offset<br>Voltage | Rail-                  | Features                   | Rating   | Operating<br>Temperature | Package                         | Approx.       | Package Size: mm2:W x L                                                                       | Input Bias<br>Current | GBW<br>(Typ) |

|---|---------------------------------------------------------------------------------------------------------|-----------------|------------------------|-------------------------------|-------------------------------|-------|---------------------|-----------------|--------------------|--------------------|-------------------|---------------------------|------------------------|----------------------------|----------|--------------------------|---------------------------------|---------------|-----------------------------------------------------------------------------------------------|-----------------------|--------------|

|   | Filter by part number Q                                                                                 | Channels<br>(#) | Architecture           | (Min)<br>(+5V=5,<br>+/-5V=10) | (Max)<br>(+5V=5,<br>+/-5V=10) | (MHz) | gain<br>(V/V)       | (Typ)<br>(V/us) | (Typ)<br>(nV/rtHz) | (Typ)<br>(nV/rtHz) | (Typ)<br>(mA)     | @ 25C)<br>(Max)<br>(mV)   | Rail                   | reatures                   | Kating   | Range (C)                | Group                           | (US\$)        | (PKG)                                                                                         | (Max) (pA)            | (MHz         |

|   | OPA2684 - Dual, Low Power,<br>Current Feedback Operational<br>Amplifier                                 | 2               | Bipolar,<br>Current FB | 5                             | 12                            | 210   | 1                   | 820             | 3.7                | 3.7                | 1.7               | 3.5                       | No                     | Small<br>Size,<br>Shutdown | Catalog  | -40 to 125               | SOIC,<br>SOT-23                 | 2.58  <br>1ku | 29 mm2: 6 x 4.9(SOIC),<br>8 mm2: 2.8 x 2.9(SOT-23)                                            | 10000000              | 210          |

|   | OPA2683 - Very Low Power,<br>Dual Current Feedback<br>Operational Amplifier                             | 2               | Bipolar,<br>Current FB | 5                             | 12                            | 145   | 1                   | 210             | 4.4                | 4.4                | 0.79              | 3.5                       | No                     | Shutdown                   | Catalog  | -40 to 85                | SOIC,<br>SOT-23,<br>VSSOP       | 2.01  <br>1ku | 29 mm2: 6 x 4.9(SOIC),<br>8 mm2: 2.8 x 2.9(SOT-23),<br>15 mm2: 4.9 x 3(VSSOP)                 | 4000000               | 145          |

| 0 | OPA2836 - Dual, Very Low<br>Power, Rail to Rail out, Negative<br>Rail in, VFB Op Amp                    | 2               | Bipolar,<br>Voltage FB | 2.5                           | 5.5                           | 205   | 1                   | 560             | 4.6                | 4.6                | 1                 | 0.4                       | In<br>to<br>V-,<br>Out | Small<br>Size,<br>Shutdown | Catalog  | -40 to 125               | QFN,<br>SOIC,<br>UQFN,<br>VSSOP | 1.50  <br>1ku | 4 mm2: 2 x 2(QFN),<br>29 mm2: 6 x 4.9(SOIC),<br>4 mm2: 2 x 2(UQFN),<br>15 mm2: 4.9 x 3(VSSOP) | 1000000               | 120          |

|   | OPA2835 - Dual, Ultra Low<br>Power, Rail to Rail Out, Negative<br>Rail In, VFB Amplifier                | 2               | Bipolar,<br>Voltage FB | 2.5                           | 5.5                           | 56    | 1                   | 160             | 9.3                | 10                 | 0.25              | 0.5                       | In<br>to<br>V-,<br>Out | Shutdown                   | Catalog  | -40 to 125               | QFN,<br>SOIC,<br>UQFN,<br>VSSOP | 1.35  <br>1ku | 4 mm2: 2 x 2(QFN),<br>29 mm2: 6 x 4.9(SOIC),<br>4 mm2: 2 x 2(UQFN),<br>15 mm2: 4.9 x 3(VSSOP) | 400000                | 30           |

|   | LM6172 - Dual High Speed, Low<br>Power, Low Distortion Voltage<br>Feedback Amplifiers                   | 2               | Bipolar,<br>Voltage FB | 5.5                           | 36                            | 160   | 1                   | 3000            | 12                 | 12                 | 2.3               | 1.5                       | No                     | N/A                        | Catalog  | -40 to 85                | PDIP,<br>SOIC                   | 2.17  <br>1ku | See datasheet (PDIP),<br>29 mm2: 6 x 4.9(SOIC)                                                | 1500000               | 160          |

|   | LM6172QML-SP - Dual High<br>Speed, Low Power, Low<br>Distortion Voltage Feedback<br>Amplifiers - Hi-Rel | 2               | Voltage<br>FB, Bipolar | 5.5                           | 36                            | 80    |                     | 3000            | 12                 | 12                 | 2.3               | 1.5                       |                        | N/A                        | Space    | -55 to 125               | CDIP,<br>CFP                    |               | See datasheet (CDIP),<br>See datasheet (CFP)                                                  |                       | 80           |

|   | LM6172QML - Dual High Speed,<br>Low Power, Low Distortion<br>Voltage Feedback Amplifiers -<br>Hi-Rel    | 2               | Voltage<br>FB, Bipolar | 5.5                           | 36                            | 80    |                     | 3000            | 12                 | 12                 | 2.3               | 1.5                       |                        | N/A                        | Military | -55 to 125               | CDIP,<br>CFP                    |               | See datasheet (CDIP),<br>See datasheet (CFP)                                                  |                       | 80           |

图 17. High-Speed Amplifier Comparison

For this design, the OPA2626 and THS4551 devices seem to be better choices in terms of bandwidth, slew rate, noise, IQ, distortion, and device package. Other FDAs also satisfy the settling-time requirement and available in smaller packages, for example, the THS4541 device, with low noise  $(2.2 \text{ nV/}\sqrt{\text{Hz}})$ , high bandwidth (approximately 620 MHz) and high-slew rate (approximately 1500V/ $\mu$ s), but at the cost of a higher operating current (approximately 10.1 mA). With a high DC precision of only 100- $\mu$ V offset voltage, a wide gain-bandwidth product of 120 MHz, and a low wideband noise of 2.5 nV/ $\sqrt{\text{Hz}}$ , the OPAx626 family of devices is optimized for driving high-throughput, high-resolution ADCs. The OPA2626 device is available in an 8-pin VSSOP package. In cascaded configuration, the OPA2626 and THS4551 devices settle to 0.5 LSB for a worst-case, full-step change (VFSR) within 38 ns. That occurrence means the output of the driver-amplifier circuitry starts acting like a constant DC source, even before the ADC enters into the track phase.

# 3.3 Refining Values of Filter Components: Parameter Stepping Technique in TINA-TI Simulation

The resistor-capacitor combination can be optimized slightly for the circuit and input signal being converted by simply varying the R-C combination; however, remember that having the incorrect combination will limit the linearity performance of the ADC. Also, increasing the bandwidth as seen by the ADC introduces more noise.

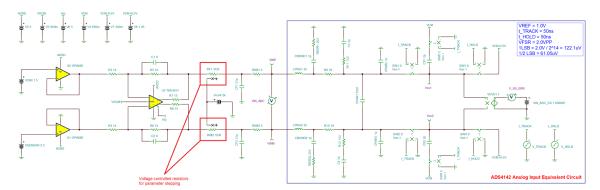

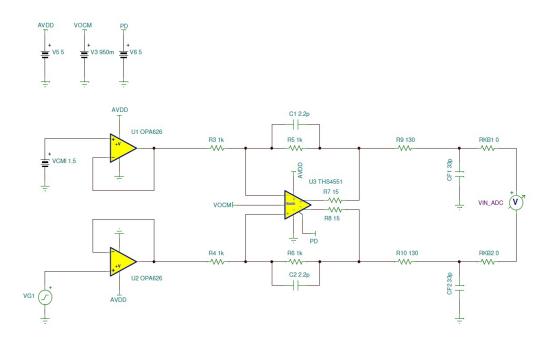

№ 18 shows the TINA schematic of driver amplifier and analog input equivalent circuit for the ADS4142 device. The analog input equivalent circuit in TINA schematic is slightly different from the one in the ADS4142 data sheet. For example, in the TINA schematic, all the switches have been replaced by voltage controlled switches, so that these switches can be controlled to model the track and hold process of the ADC. On the left-hand side is the OPA2626 op amp, THS4551 FDA, and RC-charge bucket circuit. V<sub>TRACK</sub> and V<sub>HOLD</sub> are signal sources used to control the timing of the switches. The timings of these sources were configured for a 10-MSPS sampling rate.

图 18. TINA Schematic for Parameter Stepping

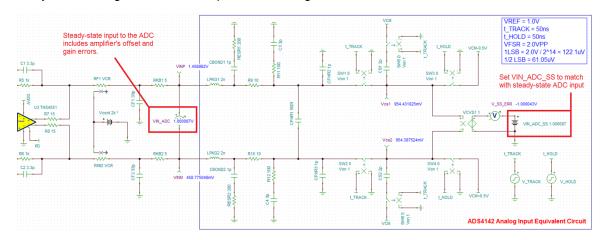

The settling-error meter must be configured to read zero error when the voltage across the sample capacitor has settled to the steady-state output of the amplifier. This reading is achieved by running DC analysis and setting the voltage source, VIN\_ADC\_SS, to a DC voltage equal to the steady-state output of the amplifier, VIN\_ADC, as shown in 19. The voltage-controlled voltage source VCVS1 translates the voltage across the sample capacitors from differential to single-ended. This voltage is compared to a steady-state voltage source to compute the settling error.

图 19. Run DC Analysis for Steady State ADC Input Voltage

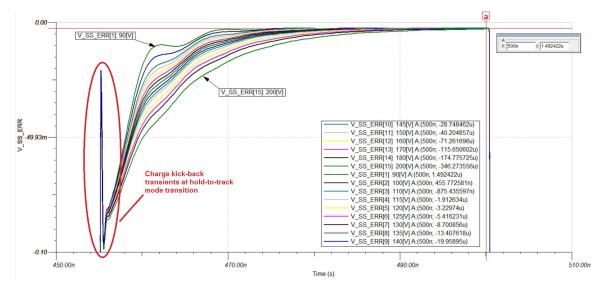

The TINA-TI SPICE simulator was used to optimize the RC-charge bucket circuit and to verify that the error target is achieved. As a reminder, we know the filter capacitor value is 33 pF and the maximum filter resistance value is 200  $\Omega$ . Filter resistance cannot be too low; otherwise the stability of the THS4551 FDA may become a concern. The parameter-stepping technique was used to find the best resistance for a given fixed-filter capacitor. To start, the range of the filter-resistor values can be from 90  $\Omega$  to 200  $\Omega$ . Parameter stepping sweeps the values of the filter resistor. However, parameter stepping does not allow for two equal components to be simultaneously stepped. A way around this limitation is to use a voltage-controlled resistor. 20 shows two voltage-controlled resistors controlled by the source, Vcont. The resistance is equal to the control source, so each resistor in this example is set to 1 k $\Omega$ , because Vcont is 1 kV. Vcont was configured to run 15 different simulations, with resistor values ranging from 90 to 200  $\Omega$ , using either the linear sweep type or list of standard resistor values. Run the transient analysis for several conversion cycles. 20 shows a graph containing 15 sets of curves – one for each resistance value in the parameter step. To make the simulation results easier to look at, adjust the vertical and horizontal axis scaling. The main curves to look at here are the error curves – V\_SS\_ERR [1] through V\_SS\_ERR [15].

The error curves should ideally settle to 0 V, so set the vertical range accordingly for zooming in on the error. On the horizontal axis, always ignore the first cycle, because some start-up behavior invalidates these results. After adjusting the curves,  $\mbox{\ensuremath{\mathbb{Z}}}$  20 shows what the graphs look like. There is one error curve for each resistance value, for a total of 15 different curves. The legend lists the curve name, parameter step value for that curve, time, and value of the curve at that time. So, for example, the curve V\_SS\_ERR[10] is the error voltage source measured with a 145- $\Omega$  resistor, at 500 ns, with an error of -28.748462  $\mu$ V. Remember, the parameter being stepped is actually a voltage source that is used to set resistance, so the 145- $\Omega$  resistor shows up as a voltage.

图 20. Parameter Stepping Simulation for Filter Resistors from 90  $\Omega$  to 200  $\Omega$

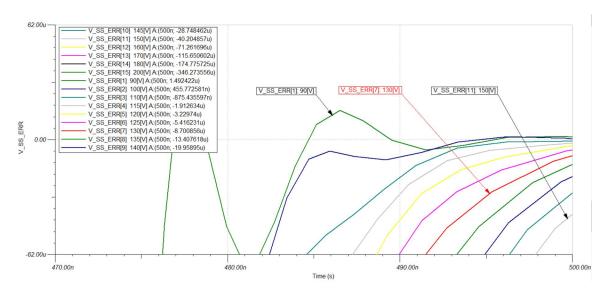

Generally, there are three types of curves – one curve has overshoot, one curve is under-damped, and one curve is in-between the other two curves. Based on a visual inspection and the errors listed in the legend, look for the best curves from a settling perspective. Or, adjust the voltage scale to  $\pm 62~\mu\text{V}$  ,representing  $\pm 0.5~\text{LSB}$  of the ADS4142 ADC. As shown in  $\boxed{8}$  21, all curves from V\_SS\_ERR[1] through V\_SS\_ERR[11] settle to  $\pm 0.5~\text{LSB}$  in a given time period. Notice that the polarity of the settling error transitions from 1.492422  $\mu\text{V}$  to  $-40.204857~\mu\text{V}$ . The idea is that some curve within this range will have an error near zero, for example, curve V\_SS\_ERR[2], with 100  $\Omega$ , settles to 455.77258 nV that is closest to the final value. However for this design, 130  $\Omega$  is used with a settling error of about 8.700856  $\mu\text{V}$ , which is not far from the final value but well within  $\pm 0.5~\text{LSB}$  error limits. Now, the low-pass filter formed by 130  $\Omega$  and 33 pF reject more noise than the low-pass formed by 100  $\Omega$  and 33 pF. Therefore, with 130  $\Omega$  and 33 pF, the system bandwidth (–3 dB) is 37.12 MHz.

The RKB series resistor on the ADC inputs to damp-out ringing caused by package parasitic. Increasing this resistor also tends to reduce bandwidth peaking. However, increasing RKB increases signal attenuation, and the amplifier must drive a larger signal to fill the ADC input range. Select a kickback resistor (RKB1 and RKB2), based on experience and the ADC data sheet recommendations or both. The ADS4142 data sheet recommends a value between  $5-\Omega$  to  $15-\Omega$  in series with each input pin.

图 21. Parameter Stepping: Curves Settling Within ±0.5 LSB

### 3.4 Noise

Noise generated by the analog front-end electronics (AFE) must be minimized because it directly impacts dynamic range of the system. Noise in the AFE consists of wideband noise from driver amplifier circuitry, wideband noise from the ADC, and quantization noise from the ADC. The ac specifications of a standalone ADC like SNR and SINAD are usually tested with a sinusoidal input. Because imaging signals are not pure sine waves, ADC's ac specifications such as SNR and SINAD are not directly applicable to imaging systems. ADCs SNR or SINAD is tested with a sine-wave input, and includes the effects of distortion of the analog signal, converter distortion due to integral and differential nonlinearity (INL and DNL), quantization noise, and thermal noise. The distortion numbers are not of interest in imaging applications because image sensor's output signal is not sinusoidal in nature, and the frontend of the ADC samples the thermal image sensor's signal only during a relatively slow-moving portion of the waveform. Instead, SNR can be defined in a somewhat different manner, based on wideband noise. The wideband noise of an AFE can be measured by using a "fixed-input histogram" test. In an ideal system, a fixed input should produce a single output code. Noise in the system will produce a range of codes; from their random distribution, the RMS noise value can be statistically calculated. The RMS wideband noise can then be compared with imager noise, and the overall system SNR can be calculated. Noise will also be introduced by the amplifier circuitry, though this can be minimized by amplifier choice and circuit techniques.

图 22. TINA Schematic for Noise Simulation

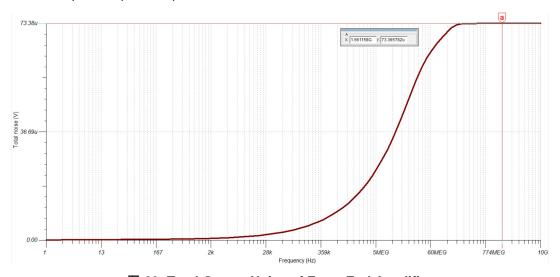

From TINA-TI simulation, the integrated output noise of the driver amplifier circuitry over the system bandwidth is around 73.38  $\mu V_{RMS}$ . The amplitude of the noise is supposed to have a Gaussian distribution. Therefore, the peak-to-peak output noise is calculated in  $\triangle$ 式 12.

图 23. Total Output Noise of Front-End Amplifier

$$V_{\text{Noise-AFE}}(P-P) = 6.6 \times 73.38 \ \mu V_{\text{RMS}} = 484.308 \ \mu V_{\text{PP}} \tag{12}$$

Compare the output noise of the driver amplifier with 1 LSB ( $\Delta$  $\pm$  13) of the ADS4142 device, based on 12-bit ENOB and 2-V full-scale input range.

$$1LSB = \frac{2V}{2^{12}} = 488 \ \mu V \tag{13}$$

The peak-to-peak output noise of the driver amplifier is comparable to the 1 LSB of the ADS4142 device with respect to 12-bit ENOB. Therefore, this driver amplifier circuitry seems to be a good choice from the noise perspective. However, the final decision must be made after testing the driver amplifier and ADC together.

Hardware Overview www.ti.com.cn

### 4 Hardware Overview

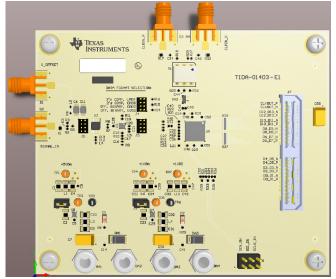

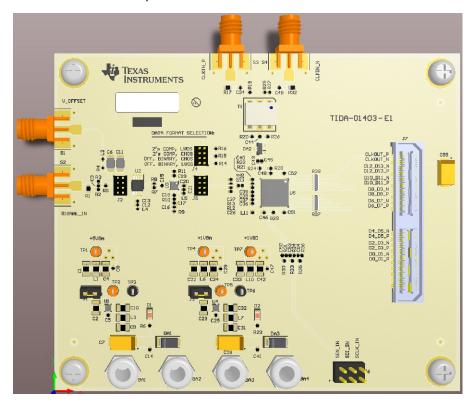

₹ 24 shows the TIDA-01403 hardware and allows users to evaluate the performance of the TI Design system. All of the components such as ICs (high speed amplifier, fully differential amplifier, ADC, and LDOs), connectors, pin headers, and others are placed on the top side of the PCB. There are test points located on the PCB for most of the power nodes. The size of the board is 105.41 mm × 87.63 mm that was chosen for easy handling during the tests. However, the board size should be optimized as per mechanical constraints of the end product.

图 24. TIDA-01403 TI Design Hardware

www.ti.com.cn Hardware Overview

TI Design hardware can be put in different configuration by changing jumper settings. 表 2 shows the function and setting of jumpers and connectors used in this reference design.

# 表 2. TIDA-01403 Connector and Jumper Details

| CONNECTOR, JUMPER | FUNCTION, SETTINGS                                                                                                                                                                                                                  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S1                | V_OFFSET: 2 V DC from lab power supply                                                                                                                                                                                              |

| S2                | SIGNAL_IN: Single-ended 2-V <sub>PP</sub> sinusoidal input signal from function generator                                                                                                                                           |

| S3                | CLKIN_P: Differential input sampling clock positive                                                                                                                                                                                 |

| S4                | CLKIN_N: Differential input sampling clock negative                                                                                                                                                                                 |

| BA1 and BA3       | Circuit Ground                                                                                                                                                                                                                      |

| BA2               | External power supply input: 5.5 V Nominal; 6.5 V Max                                                                                                                                                                               |

| BA4               | External power supply input: 2.5 V Nominal; 6.5 V Max                                                                                                                                                                               |

| J1                | Connect or disconnect 5-V LDO output with the 5-V supply of the system                                                                                                                                                              |

| J2                | For SNR, INL and DNL testing:  • Jumper on J2-3 and J2-4  • Jumper on J2-5 and J2-6  For histogram testing  • Jumper on J2-1 and J2-2  • Jumper on J2-5 and J2-6                                                                    |

| J3                | Connect or disconnect 1.8-V LDO output with the 1.8-V supply of the system                                                                                                                                                          |

| J4                | ADC data output format selection:  • Jumper on J4-1 and J4-2: Offset binary, LVDS  • Jumper on J4-3 and J5-4: Offset binary, CMOS  • Jumper on J4-5 and J4-6: 2's complement, CMOS  • Jumper on J4-7 and J5-8: 2's complement, LVDS |

| J5                | For normal operation:  • Jumper on J5-3 and J5-4  • Jumper on J5-5 and J5-6  To disconnect amplifier stage and stand-alone ADC testing:  • Jumper on J5-1 and J5-2  • Jumper on J5-7 and J5-8                                       |

| J6                | SPI interface to configure the internal registers of the ADC using GUI  • J6-2: SEN  • J6-4: SDI  • J6-6: SCLK  • J6-1, J6-3, J6-5: GND                                                                                             |

| J7                | Interface to FPGA high speed data capture card                                                                                                                                                                                      |

Test Setup www.ti.com.cn

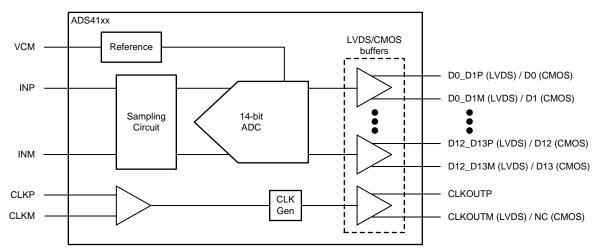

## 5 Test Setup

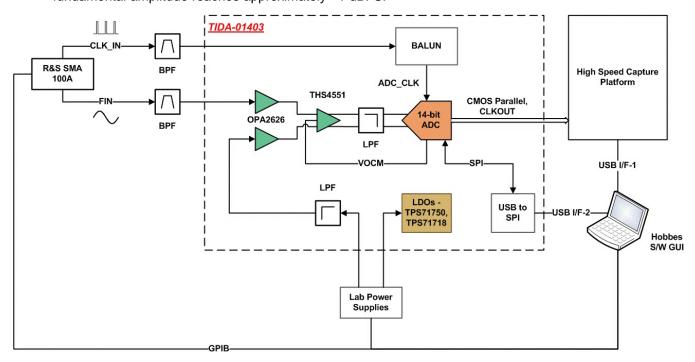

The test set-up for the TIDA-01403 is shown in ₹ 25. The test set-up requires either two signal generators that are externally locked through the 10-MHz reference or single function generator capable of providing synchronized clock and signal. The clock source is commonly synchronized with the signal generator of the input frequency to keep the clock and IF coherent for meaningful FFT analysis. A single-ended clock is supplied to the SMA connecter, S3, directly. This clock is converted to differential and AC coupled to the ADC by transformer coupling. The clock input must be from a clean, low-jitter source and is commonly filtered external to the board by a narrow bandpass filter. Depending on filter attenuation, the clock generator amplitude must be set to 10–13 dBm and the amplitude offset is not an issue due to the AC coupling of the clock input. The GUI automatically calculates the input frequency based on the FFT record length and the desired ADC sampling frequency. The function generator and lab power supplies are controlled by the GUI over the GPIB interface bus. The amplitude of input signal is adjusted until fundamental amplitude reaches approximately −1 dBFS.

图 25. TIDA-01403 Test Setup

www.ti.com.cn Test Results

# 6 Test Results

The test data in the following sections were measured with the system at room temperature, unless otherwise noted.

All of the measurements in this section were measured with calibrated lab equipment.

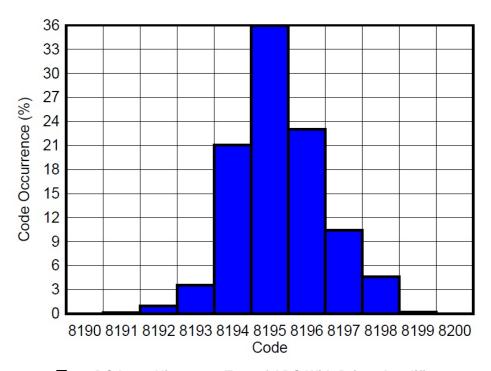

# 6.1 Histogram Test

图 26. DC Input Histogram Test of ADC With Driver Amplifier

Test Results www.ti.com.cn

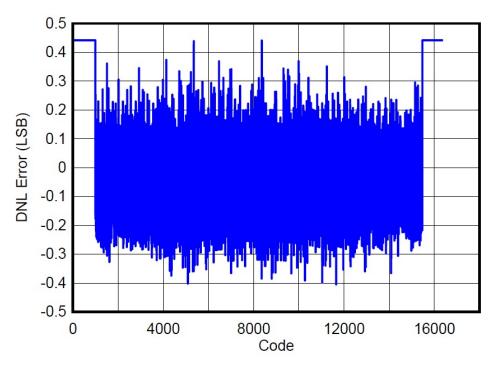

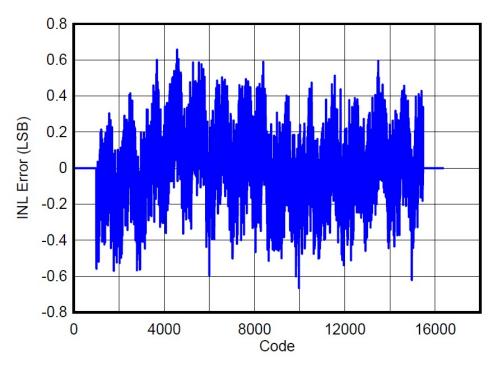

# 6.2 DNL and INL Test

图 27. ADC DNL Test With Driver Amplifier

图 28. ADC INL Test With Driver Amplifier

www.ti.com.cn Design Files

# 7 Design Files

### 7.1 Schematics

To download the schematics, see the design files at TIDA-01403.

### 7.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01403.

# 7.3 PCB Layout Recommendations

# 7.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01403.

# 7.4 Altium Project

To download the Altium project files, see the design files at TIDA-01403.

### 7.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01403.

# 7.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01403.

### 8 Software Files

To download the software files, see the design files at TIDA-01403.

### 9 About the Author

**Mike Wang** is a field application engineer (FAE) at TI, where he has supported the video surveillance market for over three years, including sectors such as thermal imaging cameras, IP network cameras, video recorders, and so on. He received his master of science in mechantronic engineering at Zhejiang University in Hangzhou, Zhejiang.

**Sharad Yadav** is a systems architect at TI India, where he is responsible for developing reference design solutions fo the industrial segment. Sharad has twelve years of experience in high-speed digital, mixed-signal boards, low-noise analog, and EMI/EMC protection circuit design.

### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能而设计。除特定 TI 资源的公开文档中明确列出的测试外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司