# TI Designs: TIDA-010013

# 适用于 Sitara™ 处理器的 RGB 到 OLDI/LVDS 显示桥接参考 设计

# TEXAS INSTRUMENTS

#### 说明

市场对更高分辨率显示屏的需求一直在不断增加。这就 需要采用更高像素的时钟,这种时钟可能会导致需要较 高的 EMI 辐射和噪声抵抗能力等设计难题。因此,视频 接口现在已从传统的 RGB 过渡至 LVDS 视频接口。由 于集成了显卡单元的微控制器可以仅输出单端 RGB 视 频数据,本参考设计展示了如何轻而易举地从 RGB 转 换至 LVDS。

#### 资源

TIDA-010013 SN65LVDS93B TL431 设计文件夹 产品文件夹 产品文件夹

#### 特性

- 从小巧的 24 位 RGB 到开放式 LVDS 显示接口 (OLDI) 或 LVDS 接口

- 支持 AM335x 入门套件 和 AM572x 评估模块

- 高分辨率 10.1 英寸宽超视频图形阵列 (WSVGA) LCD 显示模块(1024×600 像素)

- 通过 Sitara 进行显示亮度控制

#### 应用

- 面板 PLC

- 便携式监视器

- 工业机器人示教盒

- 物流机器人示教盒

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

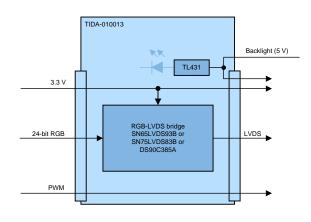

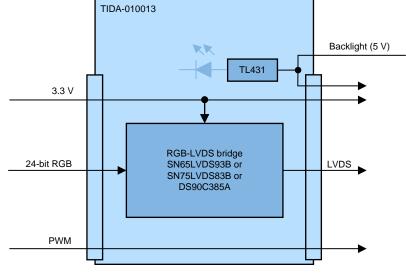

#### 1 System Description

The solution proposed is applicable when the video source interface (for example, video processor) is incompatible with the video sink interface (for example, display). An example is to connect a AM335x or AM572x Sitara microprocessor with 24-bit single-ended LVCMOS outputs to an LCD with differential LVDS input. Dedicated integrated circuits are available for this purpose, such as the SN65LVDS93B, SN75LVDS83B, or the DS90C385A, which are investigated in this reference design. The SN75LVDS83B video bridge supports a pixel clock of up to 135 MHz, which translates to a super-extended graphics array (SXGA) of 1280×1024 pixel display resolution at a frame rate of 75 Hz.

The video source interface, the video bridge, and the video sink interface use the same voltage to power up or power down at the same time to make data buffers redundant. In addition, the voltage level of the three components are kept equal at the benefit of signal integrity.

The backlight power is not the focus of this design and is delivered from an external power supply unit. A low voltage indicator is added to easily observe the correct voltage level. Inside the LCD module, this constant voltage is input to a power supply with constant output current to precisely set the LED brightness. An additional PWM signal provided to the LCD module controls the duty cycle of the LED current, which directly sets the backlight brightness.

Another option is to use an LCD glass instead of an LCD module, which exposes the terminals of the backlight LED strings directly to the outside. All backlight power generation is moved from the LCD to the main board with same functionality as previously shown.

The focus of this reference design is the video signal conversion. It is shown that only the video bridge and a few passive components are required to accomplish this task.

#### 1.1 Key System Specifications

| PARAMETER                                         | SPECIFICATIONS                  | DETAILS   |

|---------------------------------------------------|---------------------------------|-----------|

| Video input                                       | Up to 24-bit RGB (CMOS)         | 节 2.4.1   |

| Video output                                      | 4 LVDS pairs (3 data + 1 clock) | 节 2.4.1   |

| Pixel clock                                       | Up to 135 MHz (SN75LVDS83B)     | 节 2.3.1.2 |

| Power consumption (LVDS bridge)                   | 130 mW at 3.3 V                 | 节 3.3.2.1 |

| LCD backlight power consumption (full brightness) | 4.6 W at 7 V                    | 节 3.3.2.2 |

| Operating temperature                             | 0°C to +50°C                    | 节 2.4.5   |

| Form Factor                                       | 122 mm × 87 mm                  | 节 3.1.3   |

#### 表 1. Key System Specifications

# 2 System Overview

# 2.1 Block Diagram

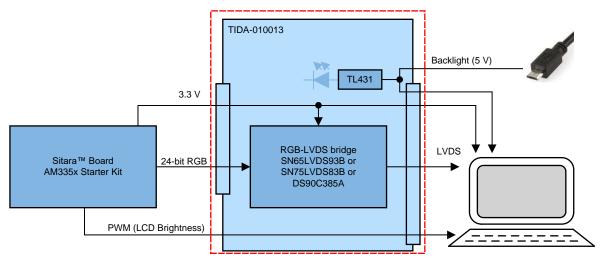

图 1. TIDA-010013 Block Diagram

# 2.2 Design Considerations

This design soley serves the purpose of resolving interface incompatibilities of the video source and video sink. With a careful board layout, the video port becomes more robust with lower EMI emission at the same time. This is accomplished by minimizing the trace length of the single-ended 24-bit RGB video interface. The layout for this design is not able to follow this rule due to mechanical constrains as two Sitara platforms (AM335x and AM572x) are supported. The focus is more on the functionality than layout optimization. See the video bridge data sheets for layout considerations.

The video source and video are assumed in close proximity, as seen in a panel PLC, for instance. In applications where the video signal must overcome longer distances, for example in a remote display application, dedicated transmitter and receiver devices are available. The FPD-III link video protocol serves this purpose, which is able to transmit the video signal and an auxiliary bidirectional channel over up to 15 m with a pixel clock of up to 170 MHz. See the Texas Instruments Web page (www.ti.com) for more information about FPD-III link technology.

## 2.3 Highlighted Products

#### 2.3.1 SN65LVDS93B, SN65LVDS83B, or DS90C385A

The SN65LVDS93B, SN75LVDS83B, and DS90C385A have been tested with this design. Only one part is used at a time. These three parts have the same functions and are pin-to-pin compatible.

#### 2.3.1.1 SN65LVDS93B

The SN65LVDS93B LVDS SerDes (serializer, deserializer) transmitter contains four 7-bit parallel load serial-out shift registers, a 7 × clock synthesizer, and five low-voltage differential signaling (LVDS) drivers in a single integrated circuit. These functions allow synchronous transmission of 28 bits of single-ended LVTTL data over five balanced-pair conductors.

#### System Overview

When transmitting, data bits D0 through D27 are each loaded into registers upon the edge of the input clock signal (CLKIN). The rising or falling edge of the clock can be selected through the clock select (CLKSEL) pin. The frequency of CLKIN is multiplied seven times and then used to serially unload the data registers in 7-bit slices. The four serial streams and a phase-locked clock (CLKOUT) are then output to LVDS output drivers. The frequency of CLKOUT is the same as the input clock, CLKIN.

The SN65LVDS93B device requires no external components and little or no control. The data bus appears the same at the input to the transmitter and output of the receiver with the data transmission transparent to the users. The only user intervention is selecting a clock rising edge by inputting a high level to CLKSEL or a falling edge with a low-level input and the possible use of the shutdown, clear (SHTDN) signal. SHTDN is an active-low input to inhibit the clock and shut off the LVDS output drivers for lower power consumption. A low level on this signal clears all internal registers at a low level.

The input pixel clock range is 10 MHz to 85 MHz.

The SN65LVDS93B is characterized for operation over ambient air temperatures of -40°C to 85°C.

#### 2.3.1.2 SN75LVDS83B

The SN75LVDS83B shares the same functionality, but has a more narrow operation over ambient air temperatures of  $-10^{\circ}$ C to  $70^{\circ}$ C and a higher pixel clock frequency of up to 135 MHz, compared to the SN65LVDS93B.

#### 2.3.1.3 DS90C385A

The DS90C385A transmitter converts 28 bits of LVCMOS, LVTTL data into four low-voltage differential signaling (LVDS) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over the fifth LVDS link. Every cycle of the transmit clock 28 bits of input data are sampled and transmitted. At a transmit clock frequency of 87.5 MHz, 24 bits of RGB data and 3 bits of LCD timing and control data (FPLINE, FPFRAME, DRDY) are transmitted at a rate of 612.5Mbps per LVDS data channel. Using a 87.5-MHz clock, the data throughput is 306.25Mbytes/sec. This transmitter can be programmed for rising edge strobe or falling edge strobe through a dedicated pin. A rising edge or falling edge strobe transmitter will interoperate with a falling edge strobe FPDLink receiver without any translation logic.

This chipset is an ideal means to solve EMI and cable size problems associated with wide, high-speed TTL interfaces with added spread spectrum clocking support.

#### 2.3.2 TL431

The TL431 is a three-terminal adjustable shunt regulator, with specified thermal stability over applicable automotive, commercial, and military temperature ranges. The output voltage can be set to any value between  $V_{REF}$  (approximately 2.5 V) and 36 V, with two external resistors. These devices have a typical output impedance of 0.2  $\Omega$ . Active output circuitry provides a very sharp turn-on characteristic, making these devices excellent replacements for Zener diodes in many applications, such as onboard regulation, adjustable power supplies, and switching power supplies.

The TL431 is offered in three grades, with initial tolerances (at 25°C) of 0.5%, 1%, and 2%, for the B, A, and standard grade, respectively. In addition, low output drift versus temperature ensures good stability over the entire temperature range.

The TL431 variant used in this design is characterized for operation from -40°C to 125°C.

#### System Overview

# 2.4 System Design Theory

#### 2.4.1 LVDS Video Bridge

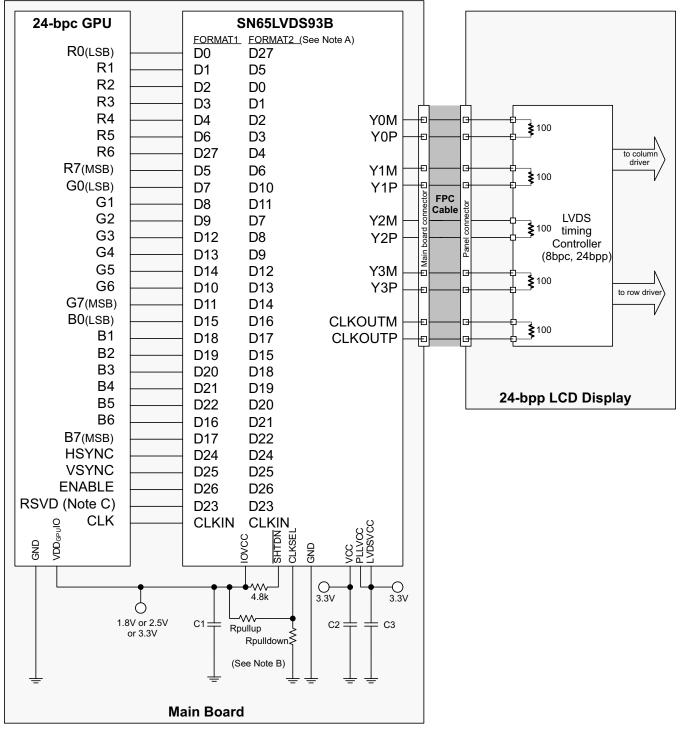

The main component of the design is the video bridge, U1. It converts the 24-bit wide RGB video signal, including the control signal HSYNC, VSYNC, DE, and the pixel clock (all single-ended LVCMOS) to an LVDS signal with four signals and one clock lane. The LVDS output clock is 7× the incoming pixel clock. The LVDS video output consists of four data lanes and one clock lane. See 🛽 2 for a functional diagram of the SN65LVDS93B, as an example.

图 2. SN65LVDS93B Functional Block Diagram

System Overview

www.ti.com.cn

The color mapping of the 24-bit RGB signal to the LCD\_DATA terminals for the AM335x Sitara family is not intuitive. Please refer to erratum *LCD: Color Assignments of LCD\_DATA Terminals* in the *AM335x Sitara*<sup>™</sup> *Processors Silicon Revisions 2.1, 2.0, 1.0 Silicon Errata*document. The color mapping of the AM572x Sitara processor is straight forward. See the *DSS Output Data Signals to RGB Color Components Mapping* table in the *AM572x Sitara Processors Technical Reference Manual.* இ 3 shows the mapping of the RGB and control signals to the input of the video bridge.

Note A. Connection format 1 is used in this design (see also  $\ddagger$  3.1.3). Note B. Data bits are latched on the falling pixel clock edge (CLKSEL = LOW).

图 3. Sitara<sup>™</sup> to Video Bridge Signal Mapping

#### System Overview

#### 2.4.2 Power Supply

The 3.3-V power rail for the video bridge is provided by the Sitara development platforms. This keeps the design simple (no additional supply rail generation and data buffers) and close to the real application. The development platforms are capable of supplying the additional power for the video bridge and the digital part of the LCD. See  $\ddagger$  3.3.2 for power consumption measurements.

The backlight power for the LCD is supplied from an external power supply. The LCD accepts an input range of 4 V to 7.3 V. A standard micro-USB connector allows for simple voltage delivery of 5 V. In addition, no overvoltage and reverse polarity protection is implemented as it is common sense that a micro-USB delivers 5 V with a standardized power connection. The indicator LED, D1, lights if the voltage is 4.6 V and above. This is useful if the power source cannot deliver the required 1 A as standard USB ports may deliver up to 0.5 A only. A common wall plug charger with USB output usually supplies more than 1 A.

#### 2.4.3 Brightness Control

The LCD module accepts a PWM at signal LED\_PWM to control the backlight brightness. The allowed frequency range of the PWM is from 500 Hz to 20 kHz with a duty cycle range of 10% to 100%.

#### 2.4.4 LCD Control Pins

The LCD module has 8 control pins. 表 2 shows their meanings and the modes selected.

| SIGNAL  | DESCRIPTION                    | SELECTED MODE      |

|---------|--------------------------------|--------------------|

| BIST    | Built-in self test             | Deasserted (LOW)   |

| LED_EN  | Backlight LED on or off        | Asserted (HIGH)    |

| LED_PWM | Backlight LED control          | PWM brightness     |

| STBYB   | LCD standby                    | Deasserted (HIGH)  |

| RESET   | LCD reset                      | Deasserted (HIGH)  |

| SHLR    | Gate driver left or right scan | Normal scan (HIGH) |

| UPDN    | Gate driver up or down scan    | Normal scan (LOW)  |

| INSEL   | Data input format              | 8-bit input (LOW)  |

#### 表 2. LCD Control Pins Setting

#### 2.4.5 Operating Temperature

The limiting factor in the system in terms of operating temperature is the LCD with an operating range of  $0^{\circ}$ C to  $+50^{\circ}$ C. The industrial version of the video bridge, the SN65LVDS93B, can operate in a temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

# 3 Hardware, Software, Testing Requirements, and Test Results

#### 3.1 Hardware

This design requires a video source and a video sink to operate. The video source is provided by a Sitara processor. The *AM3558 Starter Kit* and the *AM572X Evaluation Module* is supported by this design from a mechanical point of view. Other Sitara subfamilies are supported electrically only and can be blue-wired.

#### 3.1.1 AM335x Starter Kit

The *AM335x Starter Kit* provides a stable and affordable platform to quickly start evaluation of Sitara Arm® Cortex®-A8 AM335x Processors (AM3351, AM3352, AM3354, AM3356, AM3358) and accelerate development for smart appliance, industrial, and networking applications. It is a low-cost development platform based on the ARM Cortex-A8 processor that is integrated with options such as Dual Gigabit Ethernet, DDR3, and LCD touch screen.

#### 3.1.2 AM572x Evaluation Module

The *AM572x Evaluation Module* provides an affordable platform to quickly start evaluation of Sitara ARM® Cortex®-A15 AM57x Processors (AM5728, AM5726, AM5718, AM5716) and accelerate development for HMI, machine vision, networking, medical imaging, and many other industrial applications. It is a development platform based on the dual ARM Cortex-A15, dual C66x DSP processor that is integrated with lots of connectivity such as PCIe, SATA, HDMI, USB 3.0, USB 2.0, Dual Gigabit Ethernet, and more.

The *AM572x Evaluation Module* also integrates video and 3D, and 2D graphics acceleration, as well as a dual-core Programmable Real-time Unit (PRU) and dual ARM Cortex-M4 cores.

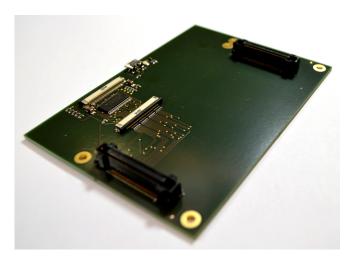

#### 3.1.3 Reference Design

The reference design takes the RGB video interface signals from the Sitara development platforms. The *AM335x Starter Kit* provides the video port over a 40-pin FFC, which connects to J1 of the reference design. The *AM572x Evaluation Module* provides the video port over J18, a 30×2 pin connector designed for high-speed signals (Hirose FX-18 series). J17 is introduced for mechanical stability reasons only.

The RGB video signal is connected to the video bridge in a way that the generated LVDS data are understandable by the LCD. The connection follows the more common *Format 1*, which maps the 2 MSB of each color to the LVDS output Y3. With the pixel clock of 51.2 MHz, the LVDS clock is seven times higher, 358.4 MHz. This allows to map 24+3 incoming signals to 4 LVDS outgoing signals.

The LVDS signal is provided to the LCD over FFC connector J2.

The backlight power is provided over the micro-USB connector J3 and is directly passed to J3 to supply the LCD. A indicator LED, D1, is introduced to visually indicate the correct voltage. If the voltage is 4.6 V, the shunt regulator reference voltage pin U2.3 is 2.5 V. At this voltage, U2 starts to conduct current from the cathode to the anode and D1 lights.

The board width of 122 mm is derived from the width of the *AM335x Starter Kit*. The board height of 87 mm is for no particular reason, but to take measurements at the video bridge while the *AM572x Evaluation Module* is plugged on top of the reference design.

#### 3.1.4 Display

The display used in this design is the 10.1-inch TFT color LCD module NHD-10.1-1024600AF-LSXV# from Newhaven Display<sup>®</sup>. It features a 1024×600 pixel resolution and runs at a pixel clock of about 51.2 MHz. The LCD uses the HX8282-A01 from Himax as a source driver. The HX8282-A01 data sheet provides the display timings, which where adopted in this design. Refer to *HX8282-A01 TXT LCD Source Driver with LVDS TCONF Data Sheet* for timings.

#### 3.2 Software

This design uses standard software components available from the Texas Instruments Web page (www.ti.com). Both development platforms provide a bootable SD-card image and the AM335x and AM57xx Linux SDK Essentials required to operate the reference design.

#### 3.2.1 Software Change Procedure

The following sections describe the software setup for the SD-card including the changes required in the device tree to support the display used in this reference design.

#### 3.2.1.1 Create a Bootable SD-Card

Starting from the processor SDK for *AM335x* or AM572x Web page, click *Get Software* for the latest PROCESSOR-SDK-LINUX-<AMxxxx> software package. Under the *AMxxxx Linux SDK SD Card Creation* section, download the *<amxxxx>-evm-linux-<linux-sdk-version>.img.zip* file. Unzip this bootable image and flash it to an SD-card.

#### 3.2.1.2 Linux SDK Essentials

Download the file *ti-processor-sdk-linux-<amxxxx>-evm-<linux-SDK-version>-Linux-x86-Install.bin* and install it on a Linux host machine.

In the following sections, the *SD root directory* is ~/ti-processor-sdk-linux-<amxxxx>-evm-<linux-SDK-version>. The *device tree source directory* is <SDK root directory>/board-support/linux.../arch/arm/boot/dts/.

#### 3.2.1.3 Device Tree Changes

The *AM335x Starter Kit* is shipped with a WQVGA (480×273 pixel) LCD and the *AM572x Evaluation Module* with a WVGA (800×600 pixel) LCD. The display used in this reference design is a WSVGA (1024×600 pixel) LCD. The timing of the video interface must be changed to support the new resolution. This is accomplished by changing the device tree configuration of the Sitara microprocessor. The video bridge itself is transparent to the system and does not required any software support.

Open in the device tree source directory the file *am335x-evmsk.dts*(AM335x) or *am57xx-evm-common.dtsi* (AM572x) with a text editor and change the timings to run the WSVGA display:

```

1024x600 {

clock-frequency = <51206400>;

hactive = <1024>;

vactive = <600>;

hfront-porch = <160>;

hback-porch = <160>;

hsync-len = <10>;

vfront-porch = <12>;

vback-porch = <23>;

vsync-len = <10>;

hsync-active = <0>;

```

Go to the SDK root directory and run the command:

#### > make linux.dtbs

This will recompile the device tree. As a result, the recompiled file *am335x-evmsk.dtb* (AM335x) or am57xx-evm-reva3.dtb (AM572x) is available in the device tree source directory including the new display timings. Copy and replace files on the SD-card (partition roots, directory boot) as follows:

- AM335x: am335x-evmsk.dtb -> devicetree-zImage-am335x-evmsk.dtb

- AM572x: am572x-evm-reva3.dtb -> devicetree-uImage-am572x-evm-reva3.dtb

Insert the SD-card to the AM335x Starter Kit, or AM572x Evaluation Module. After power up, the display shows the Matrix App Launcher application.

## 3.3 Testing and Results

#### 3.3.1 Test Setup

The hardware is inserted between the video source (Sitara platform) and video sink (display). The following sections describe the setup for both the *AM335x Starter Kit* and the *AM572x Evaluation Module*.

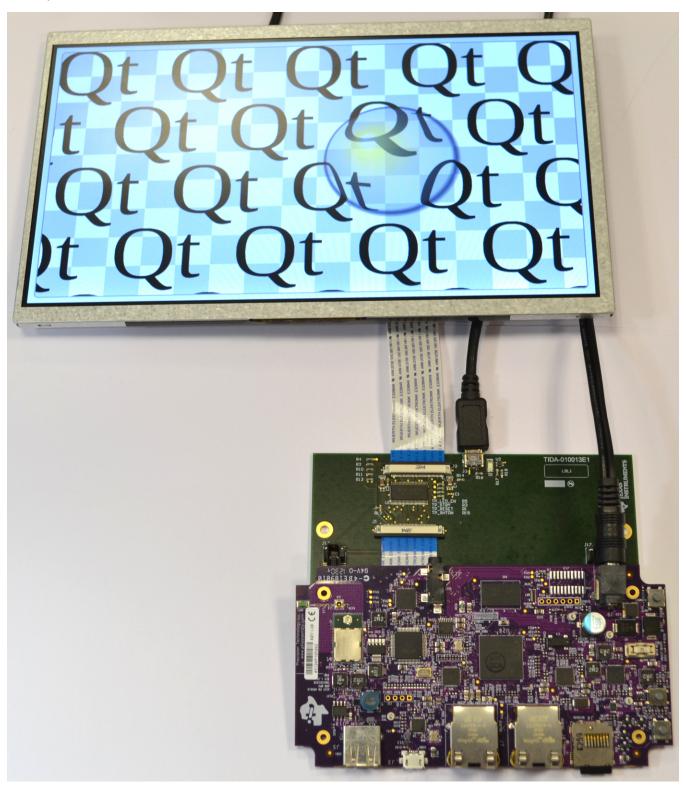

#### 3.3.1.1 AM335x Starter Kit

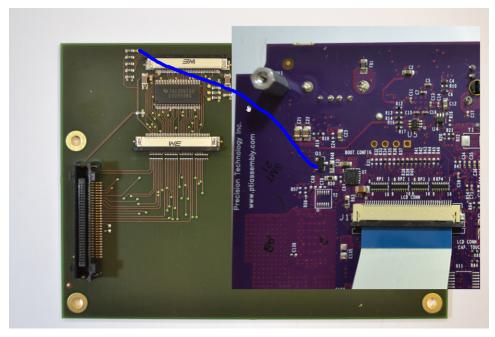

The AM335x Starter Kit includes a 40-pin FFC connector at the bottom, which connects to J1 of the reference design. The LVDS output video signal is available at J2 where the display connects seamlessly. See  $\mathbb{E}$  4 for the complete setup.

图 4. Hardware Setup With AM335x Starter Kit

Full LCD brightness is selected by the pullup resistor R4. If brightness control is required, additional bluewiring must be performed since the FFC video connector does not provide such a signal. Solder a wire between the gate of transistor Q1 of the *AM335x Starter Kit* and testpoint *PWM* close to R4 of the reference design (see  $\mathbb{R}$  5).

图 5. Blue-Wiring for AM335x Brightness Control

For the display used in this reference design, the backlight power is generated by the LCD module and controlled by an externally-provided PWM. For the original LCD, the (PWM controlled) backlight power is generated on the *AM335x Starter Kit* and connected to the LCD over the FFC. This means the PWM signal is available and already considered in the device tree and can be used just the same way as with the original LCD.

When the two boards and the LCD are connected, provide +5 V to the reference design via the micro-USB connector and power up the *AM335x Starter Kit* afterwards. The *Matrix App Launcher* application is displayed after around 1 minute.

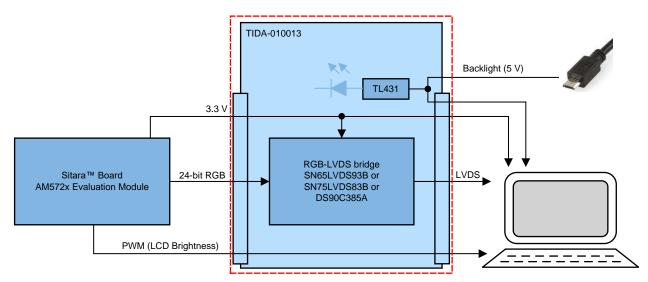

#### 3.3.1.2 AM572x Evaluation Module

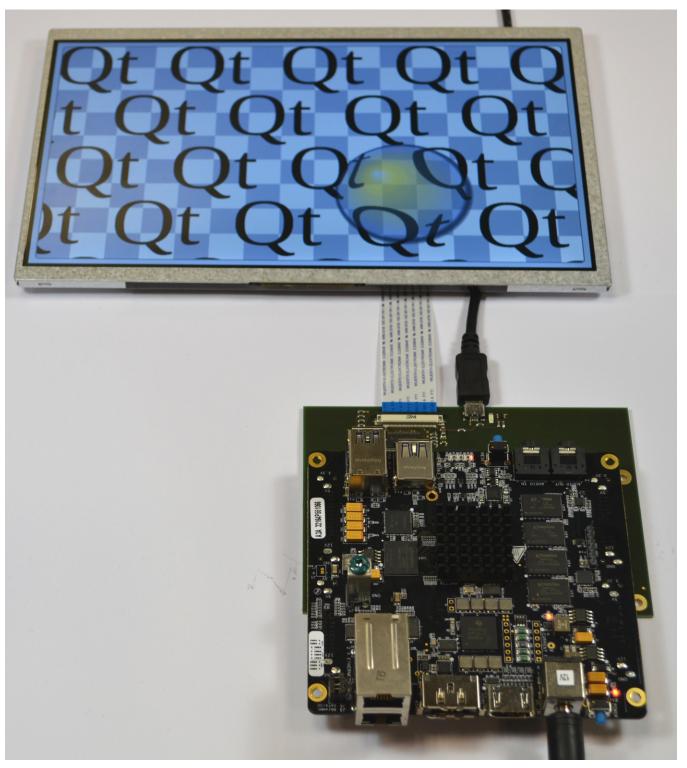

The *AM572x Evaluation Module* consists of two boards: The processor board and the LCD board with a 7inch wide video graphics array (WVGA) LCD with RGB interface. The LCD board is fully replaced by the reference design and the display. The processor board connectors P17 and P18 connect to J17 and J18 of the reference design. The LVDS output video signal is available at J2 where the display connects seamlessly. See 🗟 6 for the complete setup. The PWM signal for LCD backlight brightness can be provided by the AM572x high-resolution PWM output EHRPWM2. This peripheral is available from pin P18.44 of the AM572X processor board if R19 is populated (0  $\Omega$ ). For simplification reasons for the bringup-procedure, R19 remains unpopulated (full backlight brightness).

图 6. Hardware Setup with AM572x Evaluation Module

When the two boards and the LCD are connected, provide +5 V to the reference design via the micro-USB connector and power-up the *AM572x Evaluation Module* afterwards. The *Matrix App Launcher* application is displayed after around 1 minute.

#### 3.3.2 Test Results

#### 3.3.2.1 Video Bridge Power Consumption

表 3 shows the power consumption for the three video bridges with a 51.2-MHz pixel clock. During measurement, the Qt demo *Deform* was executed. This program is part of the standard SDK package for the Sitara platforms.

| VIDEO BRIDGE | CURRENT CONSUMPTION AT 3.3 V |

|--------------|------------------------------|

| SN65LVDS93B  | 39.5 mA                      |

| SN75LVDS83B  | 38.8 mA                      |

| DS90C385A    | 36.2 mA                      |

表 3. Current Consumption of LVDS Bridges

The voltage drop over the 200-m $\Omega$  shunt resistor R12 was measured to obtain the current consumption data.

## 3.3.2.2 LCD Backlight Power Consumption

Shunt resistor R14 is used to measure the current consumption of the LCD backlight. At full brightness, a current of 980 mA is measured over the 200-m $\Omega$  shunt resistor R14. Standard USB ports may supply a current of up to 500 mA only. A wall plug power supply with more than 1 A is recommended. The nominal input voltage for the backlight is 7 V. The overall power consumption is 4.9 W at 5 V and 4.6 W at 7 V. TI recommends operating at the nominal voltage to keep the power consumption at an optimum. Higher voltages than 5 V can be supplied by a custom USB cable with an adjustable lab power supply as source.

#### CAUTION

The TIDA-010013 has no reverse polarity and overvoltage protection. A wrongly applied voltage via the USB connector may cause permanent damage to the LCD and reference design board.

#### 3.3.2.3 Lab Results

www.ti.com.cn

图 7 shows the working setup with the *AM335x Starter Kit* with application *Deform* running on the processor.

图 7. Running Setup With AM335x Starter Kit

8 shows the setup with the *AM572x Evaluation Module*.

www.ti.com.cn

图 8. Running Setup With AM572x Evaluation Module

#### 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-010013.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-010013.

#### 4.3 PCB Layout Recommendations

Refer to the data sheet of the particular video bridge for layout recommendations.

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-010013.

#### 4.4 Altium Project

To download the Altium Designer® project files, see the design files at TIDA-010013.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-010013.

#### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-010013.

#### 5 Related Documentation

- 1. Texas Instruments, SN65LVDS93B 10 MHz 85 MHz 28-bit Flat Panel Display Link LVDS Serdes Transmitter Data Sheet

- 2. Texas Instruments, SN75LVDS83B FlatLink™ Transmitter

- 3. Texas Instruments, DS90C385A +3.3V Programmable LVDS Transmitter 24-Bit Flat Panel Display Link-87.5 MHz Data Sheet

- 4. Texas Instruments, AM335x Starter Kit Product Folder

- 5. Texas Instruments, AM335x Sitara™ Processors Silicon Errata

- 6. Texas Instruments, AM572x Evaluation Module

- 7. Texas Instruments, AM572x Sitara<sup>™</sup> Processors Technical Reference Manual

- 8. New Haven Display Intl, NHD-10.1-1024600AF-LSXV# TFT Color Liquid Crystal Display Module Product Specification

- 9. Himax, HX8282-A01 TXT LCD Source Driver with LVDS TCONF Data Sheet

#### 5.1 商标

E2E, Sitara are trademarks of Texas Instruments. Arm, Cortex are registered trademarks of ARM Limited. Altium Designer is a registered trademark of Altium LLC or its affiliated companies. Newhaven Display is a registered trademark of Newhaven Display International, Inc.

#### 6 About the Author

LARS LOTZENBURGER is a systems engineer at Texas Instruments, where he is responsible for developing reference design solutions for the industrial segment. Lars brings to this role his extensive experience in analog and digital circuit development, PCB design, and embedded programming. Lars earned his diploma in electrical engineering from the University of Applied Science in Mittweida, Saxony, Germany. He currently focuses on functional safety and human machine interface (HMI) applications for Industrial.

#### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在 帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用 的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知 识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包 含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能而设计。除特定 TI 资源的公开文档中明确列出的测试 外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他 法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任 何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信 息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许 可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、 无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

> 邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司