# TI Designs: TIDA-01411 2 类 POE PSE、6kV 雷电浪涌参考设计

# TEXAS INSTRUMENTS

#### 说明

此参考设计基于 TI 供电设备 (PSE) 控制器 TPS23861,为以太网供电 (PoE) PSE 系统提供雷电浪 涌保护解决方案。是否实施这种保护通常取决于 PSE 的目标运行环境和 PSE 的固有隔离特性。雷电浪涌保 护对系统来说是重要设计考虑因素,对工业 应用 (例 如网络录像机 (NVR)、数字录像机 (DVR))和电信 应用 (例如以太网交换机、网关)等应用来说也有重要作 用。

#### 资源

| TIDA-01411 |  |

|------------|--|

| TPS23861   |  |

| LM5019     |  |

| ISO7221    |  |

| ISO1541    |  |

设计文件夹 产品文件夹 产品文件夹 产品文件夹 产品文件夹 产品文件夹

#### 特性

- 通过 UNH-IOL PoE 一致性和互操作性以及 SIFO 1 类和 2 类测试套件

- 完全自主的模式免除了对数字接口的要求

- 自动检测和分类;自动接通和断开 PD

- 通过 6kV 共模和 4kV 差模雷电浪涌测试

- 4级雷电浪涌等级设计

#### 应用

- 监控网络视频录像机 (NVR) 和数字视频录像机 (DVR)

- 小型家庭和办公室路由器

- 以太网交换机

- 以太网供电 (PoE) 直通系统

- 住宅网关

- 小型蜂窝(微微、微、毫微微基站)

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

#### 1 System Description

As integrated circuits (ICs) continue to scale, they become more susceptible to damage from voltage transients. One of the most dangerous types of voltage transients is lightning surge, which can cause arcing or component degradation and lead to device failure. Designing effective protection circuitry is difficult due to the variability of both the magnitude and path of the surges. This reference design shows practical methods for designing protection circuitry for various lightning surge situations.

This reference design showcases robust lightning surge protection for POE PSE systems based on the TI TPS23861 PSE controller. This protection is realized through a variety of methods including: transient voltage suppressors (TVS), Bob Smith terminations, varistors, and grounding. Proper selection and implementation of these components aids in both the suppression and diversion of lightning surges to prevent component failure. A series of surge tests were performed to measure the success of the design. The stated goal during testing was to retain proper device functionality after applying up to 6 kV of common and differential voltage surges to the device.

#### 1.1 Key System Specifications

| PARAMETER                            | SPECIFICATIONS                                       |  |  |

|--------------------------------------|------------------------------------------------------|--|--|

| DC power supply                      | 54 V                                                 |  |  |

| PD classification                    | Class 4                                              |  |  |

| Surge waveform for common mode       | ±1 kV, 2 kV, 4 kV, and 6 kV;<br>1.2/50 μs, 10/700 μs |  |  |

| Surge waveform for differential mode | ±1 kV, 2 kV, 4 kV; 1.2/50 μs                         |  |  |

#### 表 1. Key System Specifications

System Overview

#### 2 System Overview

#### 2.1 Block Diagram

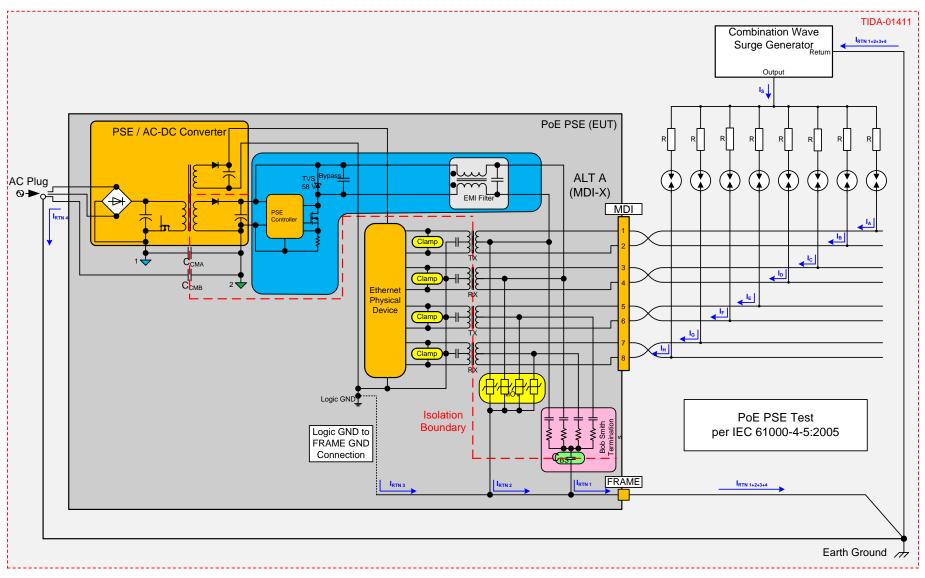

#### 图 1. Examples of Surge Current Paths Through Earthed PSE Application

ZHCU426A-December 2017-Revised January 2018

#### System Overview

Most (if not all) PSE applications include a dedicated connection to earth ground, as the previous 🕅 1 shows. Along with acting as a safety ground, this earth-ground connection can serve as a reference ground for internal PSE circuitry, such as Bob Smith cable terminations and the primary-side of an isolated AC/DC converter. These internal earth-ground connections can create paths for common-mode surge currents to flow from the generator, through the PSE, and back to the return of the generator (see 🕅 1).

Referring to 🕅 1, the surge current from the generator,  $I_S$ , divides into the eight-wire input of the PSE, as current paths  $I_A$  through  $I_H$  indicate. After entering the PSE, the surge current seeks any paths to earth ground to return to the generator. Two possible return paths are  $I_{RTN 1}$ , through the Bob Smith termination circuit block,  $I_{RTN 4}$ , and through the isolated AC/DC converter circuit block. The main conduits for these return paths are the highlighted  $C_{BS}$  capacitor in the Bob Smith termination block and the typically-used  $C_{CMB}$  common-mode noise capacitor in the AC/DC converter block, each of which crosses the isolation boundary. These two return paths plus  $I_{RTN 2}$  and  $I_{RTN 3}$  combine as  $I_{RTN 1+2+3+4}$ , which then returns back to the generator.

The currents indicate a positive surge from the surge generator, despite the fact that the PSE will be subjected to five positive and five negative surges, according to the IEC 61000-4-5 test procedure. Note that the surge current paths within each circuit block can vary depending on the surge polarity. For example, during a positive surge, some surge current flows through the port TVS to the positive rail of the 48-V power supply; conversely, during a negative surge, some surge current flows through the body diode of the port MOSFET.

The PSE controller block includes an electromagnetic interference (EMI) filter, which is normally required to meet conducted emissions requirements. This filter typically employs ferrite beads or a common-mode choke, which can help to reduce the amount of surge current that flows back to the converter. The shown PSE controller block also includes a 58-V TVS, which is typically placed across the port to protect against hot-plug transients and electrostatic discharge (ESD) events. This TVS device also contributes to the protection of the PSE controller during a lightning surge.

Although this reference design primarily focuses on lightning surge protection for the front end and power sections of the PSE, note that surge protection devices (SPD) may be required on the secondary-side data lines, as shown by the clamp blocks highlighted in 🔀 1. Several manufacturers, such as Bourns® and Littelfuse®, offer devices to protect the data lines. To maintain signal integrity, the type of device selected normally depends on the capacitance associated with the device and the data rate of the PoE system. Consult the data sheet of the manufacturer for proper selection of these devices.

The requirements for SPDs in a PSE application normally depends on the required surge test level and the inherent isolation properties of the PSE. The IEEE 802.3 standard specifies that the PSE must provide electrical isolation that withstands an electrical strength test of 1500 V<sub>RMS</sub>, 2250-V DC, or the 1500 V<sub>PK</sub> 10/700- $\mu$ s impulse test defined in the IEC 60950-1 standard. If the surge test level is below the inherent withstand strength of the PSE, then additional SPDs may not be required. Alternatively, if the PSE is to encounter surge test levels that exceed the withstand strength of the PSE, then the design will most likely require additional SPDs at the front end of the PSE to either clamp the surge voltage below the withstand rating of the PSE or crowbar the surge to earth ground.

# 2.2 Highlighted Products

#### 2.2.1 TPS23861

The TPS23861 is an easy-to-use, flexible, IEEE802.3at PSE solution. As shipped, the device automatically manages four 802.3at ports without the requirement of any external control.

The TPS23861 automatically detects powered devices (PDs) that have a valid signature, determines power requirements according to classification, and applies power. Two-event classification is supported for type-2 PDs. The TPS23861 supports DC disconnection and the external field-effect-transistor (FET) architecture allows designers to balance size, efficiency, and solution cost requirements.

The unique pin-out enables two-layer printed-circuit board (PCB) designs through logical grouping and clear upper- and lower-differentiation of I<sup>2</sup>C and power pins. This configuration delivers best-in-class thermal performance, Kelvin accuracy, and low-build cost.

In addition to automatic operation, the TPS23861 supports semi-auto mode through I<sup>2</sup>C control for precision monitoring and intelligent power management.

Compliance with the 400-ms TPON specification is ensured whether in semi-automatic or automatic mode.

The key features are as follows:

- IEEE 802.3at quad-port PSE controller

- Auto detect, classification

- Automatic mode available as shipped

- Optional I<sup>2</sup>C control and monitoring

- TSSOP 28 package 9.8 mm × 6.6 mm

#### 2.2.2 ISO7221BD

The ISO7221B is a dual-channel digital isolator. This device has a logic input and output buffer separated by TI's silicon-dioxide (SiO<sub>2</sub>) isolation barrier, providing galvanic isolation of up to 4000  $V_{PK}$  per  $V_{DE}$ . When used with isolated power supplies, this device blocks high voltage, isolates grounds, and prevents noise currents on a data bus or other circuits from entering the local ground and interfering with or damaging sensitive circuitry.

#### 2.2.3 ISO1541D

The ISO1541 device is a low-power, bidirectional isolator which is compatible with I<sup>2</sup>C interfaces. This device has logic input and output buffers which are separated by Texas Instrument's Capacitive Isolation technology using an SiO2 barrier. When used with isolated power supplies, this device blocks high voltages, isolates grounds, and prevent noise currents from entering the local ground and interfering with or damaging sensitive circuitry.

This isolation technology offers function, performance, size, and power consumption advantages when compared to optocouplers. The ISO1541 device enables the designer to implement a complete, isolated I<sup>2</sup>C interface within a small form factor.

#### 2.2.4 LM5019

The LM5019 is a 100-V, 100-mA synchronous step-down regulator with integrated high-side and low-side MOSFETs. The constant-on-time (COT) control scheme employed in the LM5019 requires no loop compensation, provides excellent transient response, and enables very-low step-down ratios. A high-voltage start-up regulator provides bias power for internal operation of the IC and for integrated gate drivers.

#### System Overview

A peak current limit protects against overload conditions. The undervoltage lockout (UVLO) circuit allows users to independently program the input undervoltage threshold and hysteresis. Other protection features include thermal shutdown and bias supply undervoltage lockout.

## 2.3 Design Considerations

#### 2.3.1 Overall Guidelines

Many guidelines apply to voltage transient protection for electronic systems. The following is a list of some practical rules along with circuits design strategies:

- The source of transient voltage can be differential-, common-mode type, or both.

- The main categories of protection techniques against transient voltages are shielding and grounding, filtering, isolation, and nonlinear devices.

- A well-designed circuit protection interface is usually the result of a good combination of blocking and diverting techniques.

- The selected voltage suppressor must have the speed and robustness (short-circuit current and waveform) required for the application. Shunt (line-to-earth GND) capacitors that may take direct transient hits must be rated for high voltage (≥ 2 kV). These capacitors must also have the following characteristics: low equivalent series resistance (ESR) at high frequency and low parasitic inductance.

- The protection circuit must not interfere with the normal behavior of the circuitry under protection.

- The protection circuit must be able to prevent any voltage transient from causing erratic behavior (repetitive or not) throughout the complete system—electrical fast transient (EFT) is one example. Use common-mode chokes when necessary.

#### 2.3.2 Basic Circuit Layout Rules

The basic rules of the circuit layout design are:

- Define a low-impedance path that diverts any transient current or voltage away from sensitive components. Do not allow ESD to find a way to earth GND by itself.

- Have a good, solid, and low-impedance earth ground connection onboard.

- Keep the transient current density and the current path impedances as low as possible by using multipoint grounds where the current is designed to flow, and single-point grounds where it is not.

- The loop within which the fast-rising currents must circulate should be a small area. For fast transients, use local ceramic capacitors whenever necessary, particularly when using clamping diodes on a power-supply rail.

- Create physical separation between high-voltage/current transients area, in close proximity to I/O connectors, and the sensitive circuitry. The high-current suppressors must be located in that I/O area, as well as the switches, LEDs, and displays

- Put all the connectors on one edge of the circuit, if possible. Place sensitive circuitry at the center of the PCB, if possible.

- Route each protected signal from the suppressor to the sensitive circuitry in parallel with its individual return signal to prevent any inadvertent transformer effect.

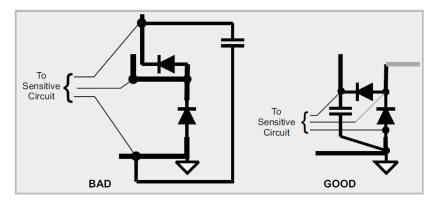

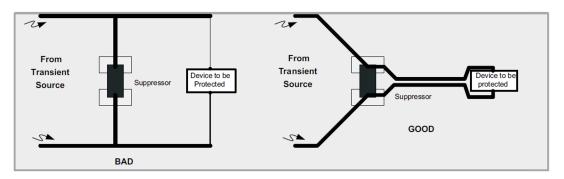

- Use a surface-mount package for suppressors. Use a four-terminal connection type to mitigate the parasitic inductance effect (see 图 2 and 图 3).

- Mitigate parasitic capacitances that are bypassing blocking series elements. However, having parasitic

inductance in series with blocking elements is not a problem.

图 2. Interconnection to Clamping Devices

图 3. Interconnection of Transient Voltage Suppressor on PCB Diagram

# 2.3.2.1 PCB Layout Considerations for TPS23861

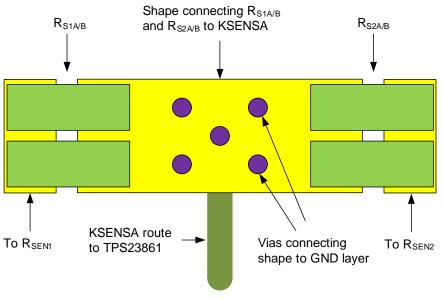

图 4. Kelvin Sense Layout Example

- Power pin bypass capacitors

- C<sub>VPWR</sub>: Place close to pin 28 (VPWR) and connect with low inductance traces and vias according to

5.

- C<sub>VDD</sub>: Place close to pin 1 (VDD) and connect with low inductance traces and vias according to 5.

#### **BOTTOM SIDE (not mirrored)**

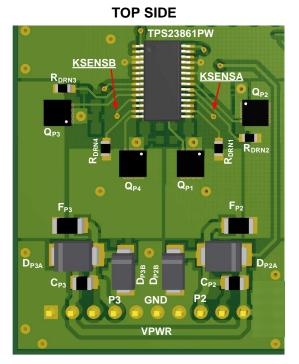

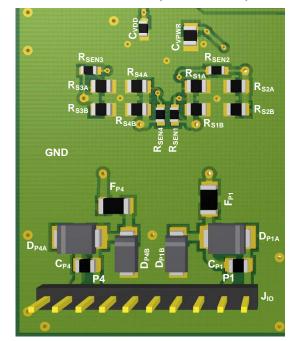

# 图 5. Four-Port Layout Example

- Per-port components

- R<sub>SnA</sub> / R<sub>SnB</sub>: Place according to 图 4 in a manner that facilitates a clean Kelvin connection with

KSENSEA/B.

- Q<sub>Pn</sub>: Place Q<sub>Pn</sub> around the TPS23861 as shown in **8** 5. Provide sufficient copper from Q<sub>Pn-D</sub> to F<sub>Pn</sub>.

- $R_{DRNn}$ : Place  $R_{DRNn}$  near to  $Q_{Pn-D}$ . Connect to DRAINn pins as shown in 图 5.

- $R_{SENn}$ : Place  $R_{SENn}$  near to  $Q_{Pn-S}$ . Connect to  $S_{ENn}$  pins as shown in  $\boxed{8}$  5.

- F<sub>Pn</sub>, C<sub>Pn</sub>, D<sub>PnA</sub>, D<sub>PnB</sub>: Place this circuit group near the RJ45 port connector (or port power interface if using a daughterboard type of interface as shown in <a>[8]</a> 5). Connect this circuit group to Q<sub>Pn-D</sub> / GND (TPS23861-AGND) using low inductance traces.

# 2.4 Choosing SPDs for High-Voltage Surge PSE Applications

This section expands on the PSE example introduced in 2.1  $\ddagger$  by relating the actual requirement and selection of SPDs to the various test levels associated with the IEC 61000-4-5:2005 symmetrical lines test.

The SPD block is shown to be metal oxide varistors (MOVs) that are used to clamp the surge voltage to earth ground, which creates an added current path,  $I_{RTN 2}$ , to return the surge current back to the generator when the MOVs are activated. Each MOV would have to be capable of handling the combined currents of two lines. The actual necessity for the MOVs depends on the test-level requirement and the withstand strength of the PSE.

This section also discusses a four-port PSE application with each port defined to meet a different surge level.  $\cancel{k}$  2 shows the high-level requirement summary.

|      |                  | TEST LEVELS                                                  |                        |                                          |                        |                         |                        |

|------|------------------|--------------------------------------------------------------|------------------------|------------------------------------------|------------------------|-------------------------|------------------------|

| DODT | INSTALLATION     | UNSYMMETRICALLY-<br>OPERATED CIRCUITS/LINES<br>COUPLING MODE |                        | SYMMETRICALLY-OPERATED<br>CIRCUITS/LINES |                        | WAVEFORM<br>(OCV-SCC)   |                        |

| PORT | CLASS            |                                                              |                        | COUPLING MODE                            |                        |                         |                        |

|      |                  | LINE-TO-LINE                                                 | ALL LINES<br>TO GROUND | LINE-TO-LINE                             | ALL LINES<br>TO GROUND |                         |                        |

| 4    | 2                | _                                                            | 1000                   | —                                        | 1000                   |                         |                        |

| 3    | 3                | —                                                            | 2000                   | —                                        | 2000                   | 10/700 μs -<br>5/320 μs | 1.2/50 μs -<br>8/20 μs |

| 2    | 4 <sup>(1)</sup> | 2000                                                         | 4000                   | —                                        | 4000                   |                         |                        |

| 1    | 5++              | —                                                            | 6000                   |                                          | 6000                   | ]                       |                        |

表 2. Requirements for Four Port Design

<sup>(1)</sup> The line-line can be implemented as a line-GND test for an unbalanced circuit or line.

The MOVs may not be required for test levels up to 1000 V because the IEEE 802.3 standard specifies that the PSE must have a withstand strength of at least 1500 V<sub>PK</sub> for the 10/700- $\mu$ s impulse test. This is the case for port 4 ( $\gtrsim$  2). Use the guidance provided in *Electrical Transient Immunity for Power-Over-Ethernet* for this case. If the PSE port has been designed with a withstand rating per the 1500-V<sub>RMS</sub> or 2250-V DC rating specified in the IEEE 802.3 standard then the MOVs may not be required for the 2000-V test level. This design example uses MOVs for port 3. The MOVs are a definite requirement to meet test levels that exceed the withstand strength of the PSE, which includes the 4000-V test level in most cases and the 6000-V level always. MOVs are also used for port 1 and port 2 to show the design and selection procedure.

Although the MOVs may not be required to meet some of the lower test levels, implementing them for all conditions can reduce the stress on sensitive components within the AC/DC converter and add to the overall robustness of the PSE. Consider the intended operating environment of the PSE should to assess the potential risk of damage and downtime of the PSE equipment against the added cost of the protection.

#### System Overview

When selecting the proper MOV, be sure to consider the allowable operating voltage, maximum clamping voltage, and surge current ratings. The repetitive surge capability (lifetime rating) of the MOV is equally important because it must survive ten repetitions (five positive and five negative) during the test. In general, the package size of the MOV is directly proportional to its energy handling and surge capability. While MOVs are available in a variety of package styles, this reference design focuses on the use of radial-leaded disc-type devices, which are available in various diameters ranging from 5 mm to 20 mm.

As the test results later verify, the chosen MOVs provide a significantly-higher lifetime rating than ten pulses, which is proven by performing surge testing well beyond the normal product surge lifetime.

The general safety section of the IEEE 802.3 standard specifies that the PoE equipment must conform to the safety requirements of the IEC 60950-1 standard. Section 6.1.2 of this IEC standard states the following regarding SPDs that are connected from telecommunications networks to earth:

6.1.2 Separation of the telecommunication network to earth

#### 6.1.2.1 Requirements

Except as specified in 6.1.2.2, there shall be insulation between circuitry intended to be connected to a telecommunications network and any parts or circuitry that will be earthed in some applications, either within the EUT or via other equipment.

Surge suppressors that bridge the insulation must have a minimum rated operating voltage Uop (for example, the sparkover voltage of a gas discharge tube) of Uop = Upeak +  $\Delta$ Usp +  $\Delta$ Usa where Upeak is one of the following values: for equipment intended to be installed in an area where the nominal voltage of the AC mains exceeds 130 V: 360 V for all other equipment: 180 V  $\Delta$ Usp ... shall be taken as 10% of the rated operating voltage of the component.

△Usa ... shall be taken as 10% of the rated operating voltage of the component.

Therefore, based on standard principle, the MOV used for the earthed PSE must have an allowable operating voltage of at least 216  $V_{RMS}$  when installed in an area where the nominal AC mains is less than 130 V and at least 432  $V_{RMS}$  when installed in an area where the nominal AC mains is greater than 130 V. This reference design assumes that the PSE is installed in an area where the nominal AC mains are less than 130 V, which requires an MOV with an allowable operating voltage of at least 230  $V_{RMS}$  (standard value).

Note that the IEC 60950-1 standard allows the removal of insulation-bridging surge suppressors during the steady-state electrical strength test of an SELV circuit. Additionally, the IEEE 802.3 standard specifies that the PSE of the PoE system must not introduce non-SELV power into the PoE wiring plant, which implies that the PSE is considered to be an SELV circuit.

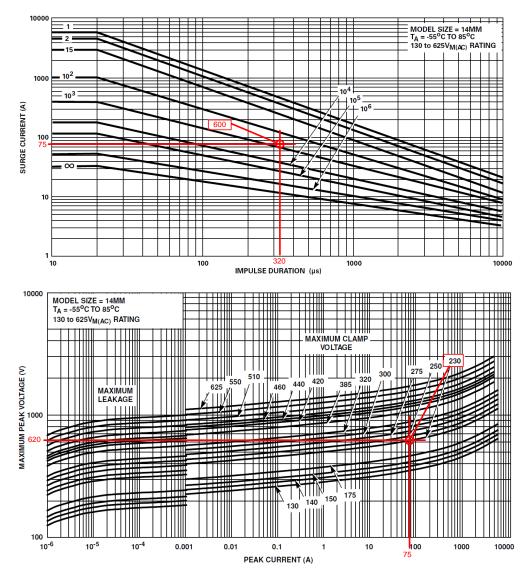

For this example, use the current levels for the two-line differential mode (DM), four-wire CDN shown in  $\gtrsim$  3. The Littelfuse UltraMOV® Varistor Series was chosen based on availability and because of the detailed repetitive surge capability curves within the device data sheet. The standard value for the 230-V<sub>RMS</sub> rating was chosen (VxxE230P, where xx = disc diameter). The selection process continues by using the repetitive surge curves provided for each MOV size. The repetitive surge curves indicate the maximum current versus the pulse-width rating of the MOV based on the number of expected surge pulses.

#### 表 3. Maximum Configuration—Two Center-Tap Currents: 10/700 and 1.2/50 Waveforms

| VPOC (V) | 4-LINE<br>CMIPCT-PSC (A) | 1-LINE<br>DMIPCT-PSC (A) | 2-LINE<br>DMIPCT-PSC (A) | 8-LINE<br>CMIPCT-PSC (A) | 1-LINE<br>DMIPCT-PSC (A) | 2-LINE<br>DMIPCT-PSC (A) |

|----------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| 500      | 6.25                     | 3.13                     | 6.25                     | 3.76                     | 1.88                     | 3.76                     |

10 2 类 PoE PSE、6kV 雷电浪涌参考设计

| VPOC (V) | 4-LINE<br>CMIPCT-PSC (A) | 1-LINE<br>DMIPCT-PSC (A) | 2-LINE<br>DMIPCT-PSC (A) | 8-LINE<br>CMIPCT-PSC (A) | 1-LINE<br>DMIPCT-PSC (A) | 2-LINE<br>DMIPCT-PSC (A) |

|----------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| 1000     | 12.50                    | 6.25                     | 12.50                    | 7.52                     | 3.76                     | 7.52                     |

| 1500     | 18.75                    | 9.38                     | 18.75                    | 11.28                    | 5.64                     | 11.28                    |

| 2000     | 25.00                    | 12.50                    | 25.00                    | 15.04                    | 7.52                     | 15.04                    |

| 4000     | 50.00                    | 25.00                    | 50.00                    | 30.08                    | 15.04                    | 30.08                    |

| 6000     | 75.00                    | 37.50                    | 75.00                    | 37.50                    | 18.75                    | 37.50                    |

#### 表 3. Maximum Configuration—Two Center-Tap Currents: 10/700 and 1.2/50 Waveforms (continued)

For the IEC 61000-4-5:2005 test, the MOV must be able to survive ten surge pulses with each current surge having an equivalent rectangular pulse width of 320  $\mu$ s, which is based on the 320- $\mu$ s time to half value associated with the 10/700- $\mu$ s to 5/320- $\mu$ s combination wave.

The Littlefuse V14E230P, V10E230P, and V07E230P were selected for port 1 (75 A), port 2 (50 A), and port 3 (25 A), respectively. For port 1, use a 320- $\mu$ s impulse duration and 75-A surge current (see  $\boxtimes$  6) to obtain approximately 600 repetitions. This configuration provides additional lifetime margin for extended testing and higher current levels such as the values in  $\gtrsim$  3. If the V10E230P MOV is used at a 320- $\mu$ s impulse duration and 75-A surge current, the number of repetitions drops to approximately 30.

图 6. Using MOV Repetitive Surge Capability and Maximum Clamping Voltage Curves

To finish the design for port 2 and port 3, see the Littelfuse data sheet for V10E230P and V07E230P. For port 2, at a 320- $\mu$ s impulse duration and 50-A surge current, there are approximately 100 repetitions. For port 3 (25 A), there are 300 repetitions. The surge voltage at port 2 (50 A) and port 3 (25 A) is 640 V and 630 V, respectively.

If the current waveform of the 1.2/50- $\mu$ s to 8/20- $\mu$ s combination wave generator sets the PSE surge requirement, the MOV surge current requirement is reduced by approximately ten times. This requirement can reduce the amount of PCB area and the cost associated with the larger MOVs.

#### 3 Hardware, Software, Testing Requirements, and Test Results

#### 3.1 Required Hardware and Software

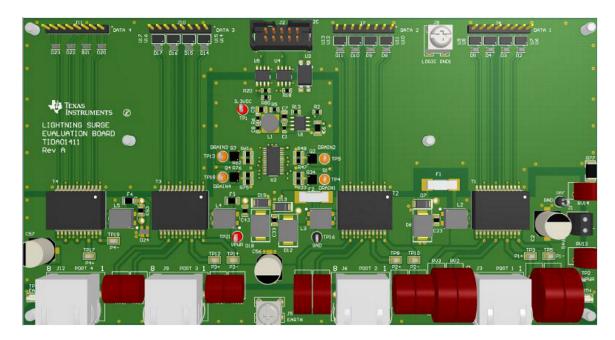

This section covers an overview of the TIDA-01411 design board and all the test connections required to evaluate the reference board.

#### 3.1.1 Hardware

To evaluate the lighting surge for PSE devices, the designer must first set up the complete system solution.

| ITEM                            | COMMENTS                                         | PART NUMBER    |

|---------------------------------|--------------------------------------------------|----------------|

| Lighting surge evaluation board | Four-port IEEE 802.3at compliant PSE TPS23861    | PR2189E1       |

| PD controller                   | Must be IEEE 802.3at compliant                   | TPS2378EVM-105 |

| USB TO GPIO                     | Connect USB port of PC to JTAG port of PSE board |                |

| Two CAT5 Ethernet cables        | Both < 100 m in length                           | _              |

| Power supply                    | Supply 54 V to PSE                               | _              |

| CDN-UTP                         | Coupling and decoupling network for test         | EMC PARTNER    |

| Transient 2000                  | SURGE generator                                  | EMC PARTNER    |

| PC with USB port                | Control PSE through GUI                          | _              |

#### 3.1.2 Software

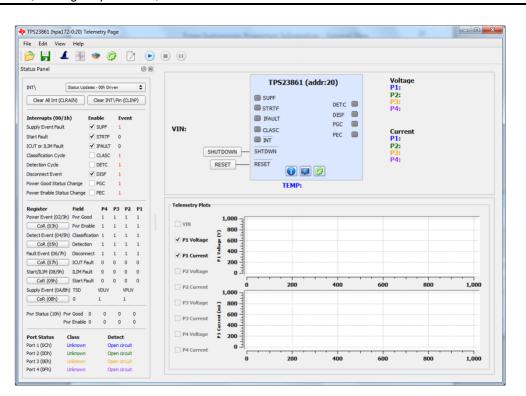

The Texas Instruments PI Commander graphical user interface (GUI) can be used with this reference design to provide real-time feedback on port telemetry and also control advanced PSE settings. Download PI Commander (PI Commander - TPS23861- setup.exe) from the TPS23861 product page: Software Section. For more information on how to connect and communicate with the TIDA-01411 design, see the section regarding TPS23891EVM-612 PI Commander GUI Setup in *TPS23861EVM-612 Auto-Mode Evaluation Module for TPS23861*.

图 7. TPS23861EVM GUI

# 3.2 Testing and Results

#### 3.2.1 Test Setup

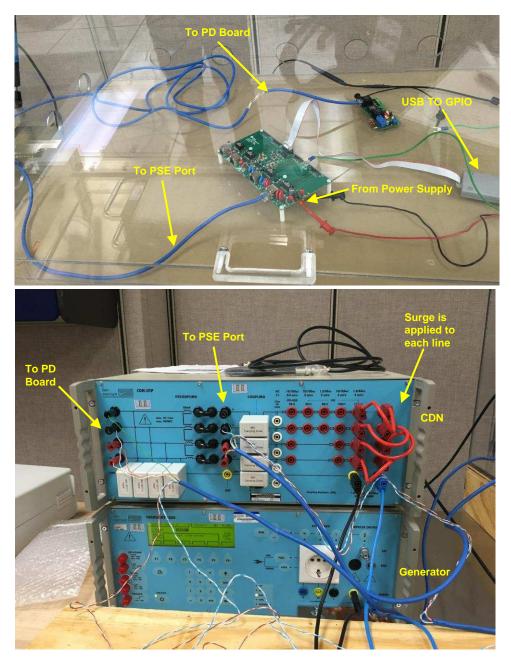

Image 8 shows a photo of the entire test system. The first step is to connect the USB-to-GPIO from the JTAG port of the PSE evaluation board to the USB port of the computer. Then connect the 54-V power supply and make sure that it is OFF before testing. Next, use a CAT5 Ethernet wire to connect from the PSE port to the coupling side of CDN-UTP and connect the PD to the decoupling side of CDN-UTP. The following step is to connect the surge generator output of the Transient 2000 to the CDN and apply surge to each line. After these steps, the user can begin lighting surge testing with a power on and configuration of the PSE.

图 8. PSE Surge Test Setup

## 3.2.2 Test Results

#### 3.2.2.1 Common Mode

| PORT             | DETECTION STATUS | CLASS STATUS | SURGE WAVEFORM  | PORT ON |

|------------------|------------------|--------------|-----------------|---------|

| 1 <sup>(1)</sup> | Open circuit     | Unknown      | ±6 kV 1.2/50 μs | Pass    |

| 2                | Resistance valid | Class 4      | ±4 kV 1.2/50 μs | Pass    |

$^{(1)}$  Surges applied to pair 1 and 2 followed by pair 3 and 6 using the surge generator in series with a 42- $\Omega$  resistor. Port tested is in forced ON state with DC disconnect disabled.

ZHCU426A–December 2017–Revised January 2018

|      |                  | •            | •               |         |

|------|------------------|--------------|-----------------|---------|

| PORT | DETECTION STATUS | CLASS STATUS | SURGE WAVEFORM  | PORT ON |

| 3    | Resistance valid | Class 4      | ±2 kV 1.2/50 μs | Pass    |

| 4    | Resistance valid | Class 4      | ±1 kV 1.2/50 μs | Pass    |

#### 表 4. Common Mode: 1.2/50-µs Waveform Test Results (continued)

## ${\it ${\bar{\pi}}$}$ 5. Common Mode: 10/700-µs Waveform Test Results

| PORT             | DETECTION STATUS | CLASS STATUS | SURGE WAVEFORM  | PORT ON |

|------------------|------------------|--------------|-----------------|---------|

| 1 <sup>(1)</sup> | Open circuit     | unknown      | ±6 kV 10/700 μs | Pass    |

| 2 <sup>(1)</sup> | Open circuit     | unknown      | ±4 kV 10/700 μs | Pass    |

| 3 <sup>(1)</sup> | Open circuit     | unknown      | ±2 kV 10/700 μs | Pass    |

| 4 <sup>(1)</sup> | Open circuit     | unknown      | ±1 kV 10/700 μs | Pass    |

<sup>(1)</sup> Surges applied to pair 1 and 2 followed by pair 3 and 6 using the surge generator in series with a 40- $\Omega$  resistor. Port tested is in forced ON state with DC disconnect disabled.

#### 3.2.2.2 Differential Mode (Single-Wire Differential)

#### 表 6. Single-Wire Differential Mode: 1.2/50-µs Waveform Test Results

| PORT             | DETECTION STATUS | CLASS STATUS | SURGE WAVEFORM  | PORT ON |

|------------------|------------------|--------------|-----------------|---------|

| 1 <sup>(1)</sup> | Resistance valid | Class 4      | ±4 kV 1.2/50 µs | Pass    |

| 2                | Resistance valid | Class 4      | ±4 kV 1.2/50 μs | Pass    |

| 3                | Resistance valid | Class 4      | ±2 kV 1.2/50 μs | Pass    |

| 4                | Resistance valid | Class 4      | ±1 kV 1.2/50 μs | Pass    |

<sup>(1)</sup> The surge generator used during testing had a  $\pm$ 4-kV maximum capability.

#### 3.2.2.3 Differential Mode (Single-Pair Differential)

#### 表 7. Single-Pair Differential Mode: 1.2/50-µs Waveform Test Results

| PORT             | DETECTION STATUS | CLASS STATUS | SURGE WAVEFORM  | PORT ON |

|------------------|------------------|--------------|-----------------|---------|

| 1 <sup>(1)</sup> | Resistance valid | Class 4      | ±4 kV 1.2/50 μs | Pass    |

| 2                | Resistance valid | Class 4      | ±4 kV 1.2/50 μs | Pass    |

| 3                | Resistance valid | Class 4      | ±2 kV 1.2/50 μs | Pass    |

| 4                | Resistance valid | Class 4      | ±1 kV 1.2/50 μs | Pass    |

<sup>(1)</sup> The surge generator used during testing had a  $\pm$ 4-kV maximum capability.

#### 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01411.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01411.

#### 4.3 PCB Layout Recommendations

- PCB spacings

- More than 80 mils from earth (and logic) ground ( > 4 kV based on 20 V/mil)

- More than 30 mils from Ethernet cable side nets (> 600 V)

- More than 20 mils from 54-V DC (VPWR) and port DRAINx nets

- Grounding

- System frame or earth ground-current shunting path for RJ45 housings

- PoE or 54-V DC power ground from DC power supply

- Logic or digital ground may be connected to earth ground through resistors

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01411.

#### 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01411.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01411.

#### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01411.

#### 5 Software Files

To download the software files, see the design files at TIDA-01411.

# 6 Related Documentation

- 1. Texas Instruments, *Lightning Surge Considerations for PoE Power Sourcing Equipment Devices*

- 2. Texas Instruments, *Electrical Transient Immunity for Power-Over-Ethernet*

- 3. Texas Instruments, TPS23861EVM-612: Auto-Mode Evaluation Module for TPS23861

- 4. Texas Instruments, TPS2378 EVM User's Guide

# 6.1 商标

Bourns is a registered trademark of Bourns, Inc.. Littelfuse, UltraMOV are registered trademarks of Littelfuse, Inc.. All other trademarks are the property of their respective owners.

ZHCU426A-December 2017-Revised January 2018

Page

修订历史记录

# 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

#### Changes from Original (December 2017) to A Revision

• 己更改 标题由 2 类 PoE PSE、60kV 雷电浪涌参考设计更改为 2 类 PoE PSE、6kV 雷电浪涌参考设计...... 1

#### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在 帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用 的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知 识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包 含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能而设计。除特定 TI 资源的公开文档中明确列出的测试 外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他 法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任 何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信 息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许 可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、 无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

> 邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司