# TI Designs: TIDA-01550 具有隔离 AFE 的多相分流计量参考设计

# TEXAS INSTRUMENTS

#### 说明

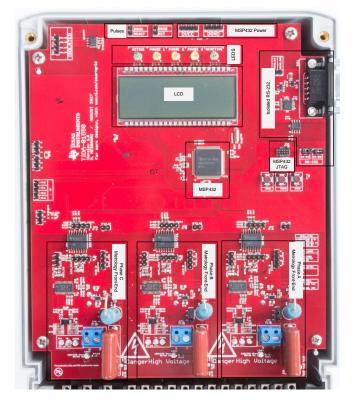

此参考设计通过使用计量模拟前端 (AFE) 实现了具有隔 离式分流传感器的 0.5% 级三相电能计量系统。计量 AFE 检测每个相位的电压和电流,计算相位的计量参 数,然后通过一个数字隔离式 UART 端口将计算的参数 发送到主机微控制器。该设计采用了用于隔离 UART 引 脚的电容隔离技术和用于为计量 AFE 提供电源的电容 压降电源,从而使得该无变压器设计能够抗磁篡改干 扰。而且,由于计量参数是在计量 AFE 本地进行计 算,而不是在主机微控制器上进行计算,因此计算计量 值时占用的主机 CPU 带宽更低。

#### 资源

| TIDA-01550  | 设计文件夹 |

|-------------|-------|

| ISO7731     | 产品文件夹 |

| MSP430i2041 | 产品文件夹 |

| TLV704      | 产品文件夹 |

| MSP432P4111 | 产品文件夹 |

| TRS3232E-Q1 | 产品文件夹 |

| ISO7721     | 产品文件夹 |

| TPS709      | 产品文件夹 |

|             |       |

# 特性

- 使用隔离式、低成本电流和电压测量 AFE 实现的具有电隔离分流的 0.5% 级三相计量

- 分布式计算:计量参数在每个相位本地计算并发送 到主机微控制器

- 5kV<sub>RMS</sub> 和 8kV 峰值的增强型隔离

- 抗磁干扰的电容压降高侧电源

- 相位序列检测

- 计量 AFE 无需使用外部晶振或时钟

#### 应用

- 电表

- 电能质量监测仪

ゐ

www.ti.com.cn

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

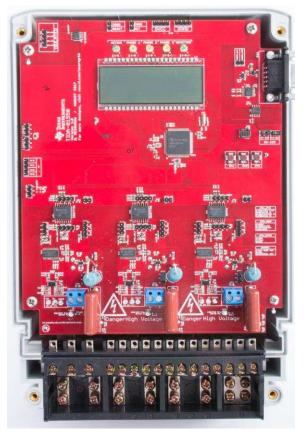

#### 1 System Description

Three-phase electricity meters measure the energy consumption at a business or industrial site. To properly sense energy consumption, voltage and current sensors translate mains voltage and current to a voltage range that an analog-to-digital converter (ADC) can sense. For three-phase electricity meters, it is necessary for the current sensors to be isolated so they can properly sense the energy consumption of multiple phases without damaging the ADC. As a result, current transformers, which inherently have isolation, have historically been used for the current sensors for three-phase electricity meters. One disadvantage of current transformers (and many transformers in general) is that they can be paralyzed by applying a strong enough magnetic field so that the sensed energy consumption would be less than the actual energy consumption. Due to this weakness of current transformers against magnetic fields, it is common for people to try to tamper with a meter by placing a strong magnet outside the electricity meter to try to paralyze the current transformers to steal electricity. This reference design prevents magnet tampering by using isolated shunts as current sensors instead of current transformers.

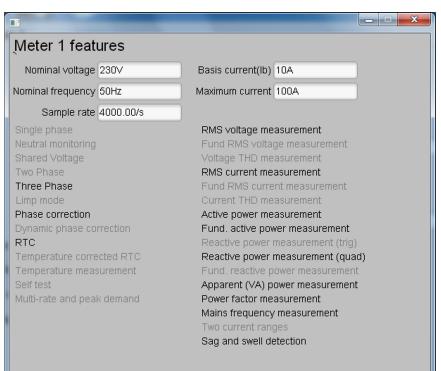

This reference design implements a class 0.5 three-phase energy measurement system with isolated shunt sensors by using programmable metrology analog front-end (AFE) microcontrollers. The metrology AFEs sense the voltage and current for each phase, calculates the metrology parameters for the phase, and then sends out the calculated parameters to a host microcontroller using a UART port. The key parameters calculated by the metrology AFE include:

- RMS current and voltage

- Active power, reactive power, and apparent power factor

- Frequency

- · Number of sag and swell occurrences

- Total number of sag and swell cycles

External digital isolators capacitively isolate the UART communication between the host microcontroller and the metrology AFE, which allows the host microcontroller to communicate to different metrology AFEs that are referenced with respect to different phases. Because the metrology AFEs measure both voltage and current and have their UART pins externally isolated, voltage sensing is isolated in addition to the required current sensing isolation necessary for implementing shunts in poly-phase systems. As a result, the host microcontroller is completely isolated from mains voltage. Also, because metrology parameters are calculated locally at the metrology AFEs instead of at the host microcontroller, less CPU bandwidth is needed from the host to calculate metrology parameters.

In this reference design, the host microcontroller determines phase sequence, drives the board's liquid crystal display (LCD), and communicates to a PC GUI through the board's isolated RS-232 circuitry. The host microcontroller also takes the metrology readings from the different metrology AFEs and aggregates these results. In addition, the host microcontroller accumulates the average active power readings sent by the metrology AFEs to calculate the total consumed active energy. Using the host microcontroller to accumulate the energy readings instead of the metrology AFEs enables the use of the metrology AFE's internal clock to calculate metrology parameters for many applications. Using the internal clock of the metrology AFE eliminates the need for external crystals or clocks for each metrology AFE, thereby

reducing system cost. By having the metrology AFEs run off their own clock instead of feeding a clock through the isolation boundary, the data rate of the signals sent through the isolation boundary are greatly reduced because only the actual metrology parameter values, which have a relatively low data rate, need to be sent to the host microcontroller. This low data rate reduces the current consumption of the digital isolators as well as reduces emissions.

Each metrology AFE is powered by a cap-drop supply that is also transformerless. Because a transformer is not used in this reference design (whether a power supply transformer or current transformer), this design is inherently magnetically immune, thereby preventing electricity theft due to magnetic tampering. Moreover, the high-side cap-drop power supply reduces the entire system cost, has inherent low conducted and radiated emissions, and reduces the current consumption drawn from the low-side power supply because the high-side is separately powered from mains instead of being derived from the low-side power supply.

Another advantage of using shunts is that it does not share the same degradation in metrology results that current transformers show when harmonics are present in a system. As a result, these isolated shunt current sensors can also be used for equipment that performs harmonic analysis such as power quality meters.

# 1.1 Key System Specifications

| PARAMETER                                     | SPECIFICATIONS                                                                                                                                                                      | DETAILS         |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Number of phases                              | Three                                                                                                                                                                               | 2.1 节           |

| Accuracy class                                | Class 0.5                                                                                                                                                                           | 节 3.2.3         |

| Current sensor                                | Shunt                                                                                                                                                                               | 节 2.3.1.3       |

| Voltage ADC type                              | Sigma delta (integrated within MSP430i2041 metrology AFE)                                                                                                                           | 节 2.3.1.3       |

| Sigma delta modulator clock                   | 1,024,000 Hz                                                                                                                                                                        | 节 2.3.2.1.2     |

| Sigma delta oversampling ratio (OSR)          | 256                                                                                                                                                                                 | 节 2.3.2.1.2     |

| Ratio of skipped samples to total samples     | 0/5                                                                                                                                                                                 | 节 2.3.2.1.2     |

| Effective sample rate                         | 4000 samples per second                                                                                                                                                             | 节 2.3.2.1.2     |

| Phase compensation implementation             | Hardware (sigma delta module feature)                                                                                                                                               | 节 2.3.2.3.2     |

| Metrology AFE clock speed                     | 16.384 MHz                                                                                                                                                                          | 节 2.3.2.1.1     |

| System nominal frequency                      | 50 Hz                                                                                                                                                                               | 节 2.3.2.3.1     |

| Measured parameters (updated every 50 cycles) | Active power, reactive power, apparent power; root mean square (RMS) current and voltage; power factor; line frequency; sag and swell duration; sag and swell number of occurrences | 节 2.3.2.2.1     |

| Isolation channels necessary                  | Two or three                                                                                                                                                                        | 2.1 节           |

| Host MCU clock speed                          | 48 MHz                                                                                                                                                                              | 节 2.3.2.1.4     |

| Utilized LEDs                                 | Total active energy and total reactive energy                                                                                                                                       | 节 2.3.2.4.3.2.1 |

| Metrology AFE power                           | Option 1: Power derived from mains using cap-drop supply;<br>Option 2: External power                                                                                               | 节 2.3.1.1       |

# 表 1. Key System Specifications

www.ti.com.cn

# 2 System Overview

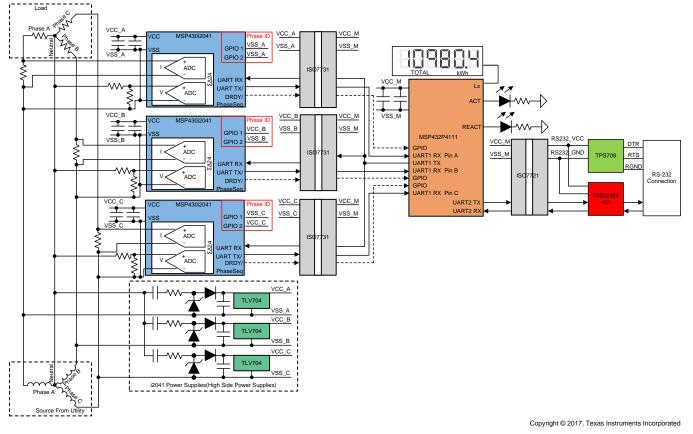

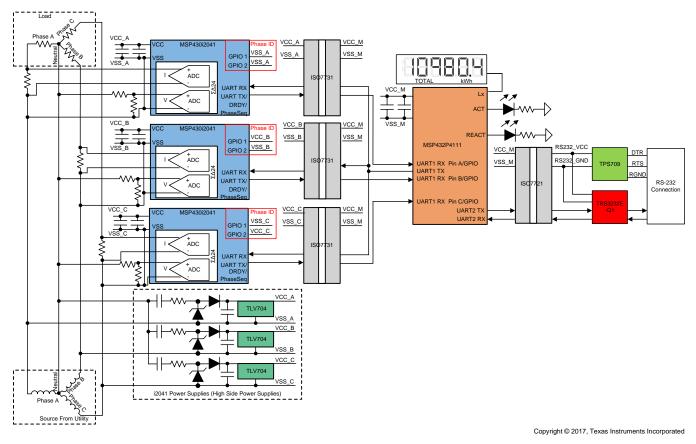

# 2.1 Block Diagram

图 1. TIDA-01550 Block Diagram, Three Isolated Channels

# 图 2. TIDA-01550 Block Diagram, Two Isolated Channels

I and I 2 depict a block diagram that shows the high-level interface used for a MSP430i20xx three-phase energy measurement application with isolated shunts. These figures show a three-phase, four-wire star connection to the AC mains. In this reference design, each phase has a shunt current sensor and a MSP430i20xx device. The MSP430i20xx device in this design is responsible for sensing the mains voltage, sensing the current by measuring the voltage drop across the shunt, calculating the metrology parameters (except energy), and sending it to the MSP432<sup>™</sup> host microcontroller in this design. The resistance of the shunt is selected based on the current range required for energy measurements and also the minimization of the maximum power dissipation of the shunt. The MSP430i20xx senses the mains voltage by using resistor dividers as the voltage sensor to ensure that the input voltage to the ADC fits within the ADC's input voltage range. Because the MSP430i20xx can accept negative voltages, level shifting the voltage from the resistor divider is not necessary. In this reference design, the superset four-channel MSP430i2041 device variant is used; however, to minimize cost, the two-channel MSP430i2020 variant can also be used. To measure temperature in addition to voltage and current, the three-channel MSP430i2030 device can be used instead.

Only one UART module on the MSP432 communicates with the three MSP430i2041 devices. Multiplexing one MSP432's UART module to communicate with the different MSP430i2041 devices is done by using an addressing scheme where the MSP432 provides the address of the MSP430i2041 device that it is talking to in the commands that the MSP432 sends. Whenever a command is sent by the MSP432 device, the MSP432 MCU sends it to all the MSP430i2041 devices, but only the addressed MSP430i2041 device responds. The address of the different MSP430i2041 devices is configured by providing the proper combination of voltages (VSS or VCC) on two designated phase identification GPIO pins of the

www.ti.com.cn

MSP430i2041 devices. Each device would have its own combination of voltages to ensure that each device has a unique Phase ID. Using the phase identification addressing scheme allows the different MSP430i2041 devices to communicate with the same MSP432 UART module without feeding in any external chip select lines either through the isolation boundary or to the isolator output enable pins. In addition, the phase identification addressing scheme allows the same firmware to be programmed onto the MSP430i2041 devices at the same time, thereby reducing programming time.

Each MSP430i2041 device updates its metrology readings after 50 mains cycles of data has been received. After new metrology readings have been received, a normally high data ready (DRDY) GPIO pin on the MSP430i2041 is asserted low to alert the MSP432 that new metrology parameters are ready. Because this GPIO pin assertion is done a fixed amount of time after the last zero crossing, the phase sequence can be detected by the MSP432 when the MSP430i2041 devices are synchronized by observing the order at which this GPIO pins are asserted. To synchronize the different MSP430i2041 devices, a sync command can be sent by the MSP432 device to make sure that the assertion of the different MSP430i2041 DRDY GPIO pins are synchronized from the same starting point. In this reference design, there is an option to have the DRDY functionality implemented on a dedicated pin as shown in 🕅 1 or to have it multiplexed with the UART TX pin as shown in 🕅 2. The two-channel configuration is only valid when the shared UART TX/DRDY pin on the MSP430i2041 is connected to a GPIO pin on the host microcontroller that has the ability to dynamically switch between being a UART RX pin to being an interruptible GPIO input pin. For two-channel mode, the pins on the host microcontroller that are connected to the DRDY pins of the different MSP430i2041 devices must also be able to be configured as the same UART module port through the use of port mapping.

Because each MSP430i2041 device is referenced with respect to a different phase, it is necessary to isolate the communication from the MSP430i2041 to the MSP432. In this design, this isolation is done by the ISO7731 devices; however, for the two channel configuration shown in 🕅 2, an ISO7721 device can be used instead to reduce cost. The low power consumption of these isolators enable power supplies with limited maximum current specifications such as cap-drop supplies to be used to power each phase. For proper operation of the isolators, the output channels of different isolators must not be connected to each other; however, the input channels can be directly connected to each other. As a result, although only one UART module is used, the isolated UART TX signal output from the different MSP430i2041 devices must not be physically connected to each other and fed into one RX pin for the MSP432 MCU. Instead of physically connecting together the different isolated UART TX signals from the MSP430i2041 devices, in this design each of these signals is fed into a different port mappable GPIO pin that has the ability to be configured as the RX functionality of the same UART module. An alternative approach, which is not used in this reference design, is to connect the different isolated UART TX signals to inputs of an OR/AND logic gate and to connect the output of this logic gate to one UART RX pin of the MSP432 MCU.

To power the MSP430i2041 devices and the high-side of the isolators, each phase has an external power supply. Because each MSP430i2041 and the high-side of its corresponding isolator must be referenced from a different line voltage, three different cap-drop supplies are used. Each implemented power supply provides power to the associated MSP430i2041 and isolator by using a half-bridge cap-drop power supply between the line of that phase and neutral.

This reference design uses the MSP432P4111 as the host microcontroller. The MSP432P4111 aggregates the data from the different MSP430i2041 devices. The MSP432P4111 also accumulates the power readings into energy, which allows the MSP430i2031 device to use its own internal clock so that external clock components such as clock generators are not necessary. The MSP432 MCU is responsible for outputting the active and reactive energy pulses used for accuracy measurement and calibration. In addition to isolated pulses, the design also supports isolated RS-232 communication through the use of the TPS70933, ISO7721, and TRS3232E-Q1 devices. For more information on the isolated RS-232 portion of the design, see the *Self-Powered Isolated RS-232 to UART Interface Reference Design*.

# 2.2 Highlighted Products

# 2.2.1 ISO7731

The ISO7731 device is a high-performance, triple-channel digital isolator with 5000-V<sub>RMS</sub> (DW package) and 3000-V<sub>RMS</sub> (DBQ package) isolation ratings per UL 1577. The ISO7731 device provides high electromagnetic immunity and low emissions at low power consumption, while isolating CMOS or LVCMOS digital I/Os. Each isolation channel has a logic input and output buffer separated by a silicon dioxide (SiO<sub>2</sub>) insulation barrier. This device comes with enable pins that can be used to put the respective outputs in high impedance for multi-master driving applications and to reduce power consumption. Through innovative chip design and layout techniques, the electromagnetic compatibility of the ISO7731 device has been significantly enhanced to ease system-level ESD, EFT, surge, and emissions compliance.

# 2.2.2 MSP430i2041

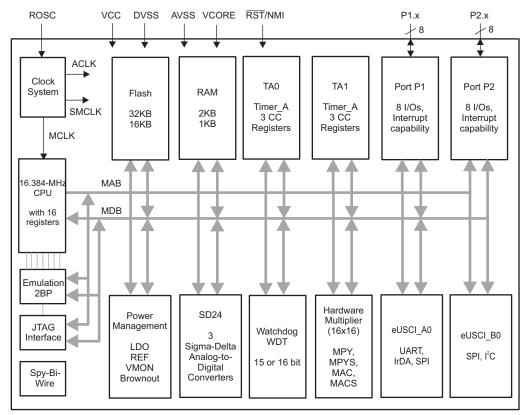

The MSP430i2041 metrology AFE device finds its application in power and energy measurement and has the necessary architecture to support it. The MSP430i2041 device1 has an internal 16.384-MHz DCO, which generates system clocks without an external crystal. The MSP430i2041 has four independent, 24-bit,  $\Sigma\Delta$  ADCs based on a second-order sigma-delta architecture that supports differential inputs. The sigma-delta module (referred to as SD24) operate independently, are capable of 24-bit results, and can be grouped together for simultaneous sampling of voltages and currents on the same trigger. In addition, each converter also has an integrated gain stage for amplification of low-output current sensors. The MSP430i2041 device also has a 16-bit × 16-bit hardware multiplier that can be used to further accelerate math intensive operations during metrology computations. 🕅 3 shows these features as well as additional ones for the MSP430i2041 metrology AFE. The key parameters calculated during measurements by the MSP430i2041 are as follows:

- RMS current and voltage

- Active and reactive power

- Power factor

- Frequency

- Sag duration

- Number of sag occurrences

- Swell duration

- Number of swell occurrences

Copyright © 2018 Texas Instruments Incorporated

图 3. Functional Block Diagram of MSP430i2041

#### 2.2.3 TLV704

The TLV70433 low-dropout (LDO) regulator is an ultra-low quiescent current devices designed for extremely power-sensitive applications. Quiescent current is virtually constant over the complete load current and ambient temperature range. These devices are an ideal power-management attachment to low-power microcontrollers such as the MSP430<sup>™</sup>. The TLV70433 operates over a wide operating input voltage of 2.5 V to 24 V. Thus, the device is an excellent choice for both battery-powered systems as well as industrial applications that undergo large line transients.

## 2.2.4 MSP432P4111

The SimpleLink<sup>™</sup> MSP432P4111 MCUs are optimized MCUs that deliver ultra-low-power performance with FPU and DSP extensions. This device has an Arm<sup>®</sup> 32-Bit Cortex<sup>®</sup>-M4F CPU with Floating-Point Unit and Memory Protection Unit, a real-time clock, LCD driver, port mappable GPIOs, an AES encryption and decryption accelerator, and multiple serial communication options. The MSP432P4111 device is part of the SimpleLink MCU platform, which consists of Wi-Fi<sup>®</sup>, *Bluetooth*<sup>®</sup> low energy, Sub-1 GHz, and host MCUs. All of these devices share a common, easy-to-use development environment with a single-core software development kit (SDK) and rich tool set.

# System Overview

## 2.2.5 TRS3232E-Q1

To properly interface with the RS-232 standard, a voltage translation system is required to convert between the 3.3-V domain on the board and from the 12 V on the port itself. To facilitate the translation, the design uses a TRS3232E-Q1 device. The TRS3232E-Q1 device is capable of driving the higher voltage signals on the RS-232 port from only the 3.3-V DVCC through a charge pump system.

The TRS3232E-Q1 device consists of two line drivers, two line receivers, and a dual charge-pump circuit with ±15-kV electrostatic discharge (ESD) protection pin-to-pin (serial-port connection pins, including GND). The device meets the requirements of the Telecommunications Industry Association and Electronic Industries Alliance TIA/EIA-232-F and provides the electrical interface between an asynchronous communication controller and the serial-port connector. The charge pump and four small external capacitors allow operation from a single 3-V to 5.5-V supply. The devices operate at data signaling rates up to 250 kbit/s and a maximum of 30-V/µs driver output slew rate.

# 2.2.6 ISO7721

To add isolation to the RS-232 connection to a PC, the isolated RS-232 portion of this reference design uses capacitive galvanic isolation, which has an inherent lifespan advantage over an opto-isolator. In particular, industrial devices are usually pressed into service for much longer periods of time than consumer electronics; therefore, maintenance of effective isolation over a period of 15 years or longer is important.

The variant of the ISO7721 used in the RS-232 circuitry of this reference design provides galvanic isolation up to 3.0 kV<sub>RMS</sub> for one minute per UL. This digital isolator has two isolated channels where one is a forward channel and the other is a reverse channel. Each isolation channel has a logic input and output buffer separated by a silicon dioxide (SiO<sub>2</sub>) insulation barrier. This chip supports a signaling rate of 100 Mbps. The chips can operate from a 3.3-V and 5-V supply and logic levels.

# 2.2.7 TPS709

To power the data terminal equipment (DTE) side of the isolation boundary and the RS-232 charge pump, there are two choices. The interface can either implement an isolated power supply or harvest power from the RS-232 line. Integrating a power supply adds cost and complexity to the system, which is difficult to justify in low-cost sensing applications.

To implement the second option of harvesting power from the RS-232 port itself, this reference design uses the flow control lines that are ignored in most embedded applications. The RS-232 specification (when properly implemented on a host computer or adapter cable), keeps the request to send (RTS) and data terminal ready (DTR) lines high when the port is active. As long as the host has the COM port open, these two lines retain voltage on them. This voltage can vary from 5 V to 12 V, depending on the driver implementation. The 5 V to 12 V is sufficient for the use requirements in this design.

The voltage is put through a diode arrangement to block signals from entering back into the pins. The voltage charges a capacitor to store energy. The capacitor releases this energy when the barrier and charge pump pull more current than what is instantaneously allowed. The TPS70933 is used to bring the line voltage down to a working voltage for the charge pump and isolation device.

The TPS70933 linear regulator is an ultra-low quiescent current devices designed for power-sensitive applications. A precision band-gap and error amplifier provides 2% accuracy over temperature. A quiescent current of only 1  $\mu$ A makes these devices ideal solutions for battery-powered, always-on systems that require very little idle-state power dissipation. These devices have thermal-shutdown, current-limit, and reverse-current protections for added safety. These regulators can be put into shutdown mode by pulling the EN pin low. The shutdown current in this mode goes down to 150 nA (typical).

# 2.3 System Design Theory

#### 2.3.1 Design Hardware Implementation

#### 2.3.1.1 High-Side Power Supply

To properly sense, calculate, and send metrology parameters, it is necessary for the MSP430i2041 and the high-side of the corresponding isolation device to be powered. Because each MSP430i2041 device and corresponding isolator are referenced from a different line voltage, a different high-side power supply is required for each power supply. In this reference design, there are two high-side power supply options: an onboard half-bridge cap-drop power supply or an off-board, custom power supply.

There are multiple advantages to using the onboard cap-drop high-side power supply. First, this cap-drop power supply does not have any magnetic components, so the power supply would be magnetically immune to magnetic fields instead of only being magnetically tolerant to a certain limit. Additionally, cap-drop supplies are relatively inexpensive compared to alternative power supply options. Also, LDO-based cap-drop power supplies inherently have low conducted and radiated emissions compared to SMPS power supplies. Finally, because the high-side power is derived directly from mains instead of from the host MCU's power supply, less current is drawn from the host MCU's power supply, thereby allowing the specifications on that power supply's maximum current drive to be relaxed.

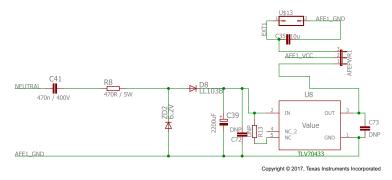

图 4 shows the design's implementation of the high-side power supply. In this implementation, a TLV70433-based, half-bridge, cap-drop power supply translates the mains voltage to the necessary 3.3 V needed to power the MSP430i2041 and the high-side of the ISO7731. As an alternative to using the onboard cap-drop power supply, the design has the option to instead power the MSP430i2041 and ISO7731 by providing the necessary 3.3 V from an external isolated voltage supply to the associated terminal block (U\$13 in 图 4).

图 4. High-Side Power Supply

Cap-drop power supplies have a limited maximum current so it is important that their load be low-power.  $\overline{x}$  2 shows a typical current consumption of 4.5 mA when the MSP430i2041 device is running in active mode at 16.384 MHz. Based on  $\overline{x}$  3, there is also a maximum additional current consumption of 250 µA per ADC converter turned on, resulting in an additional 500 µA of current drawn from the power supply to properly sense voltage and current.

| PARAMETER                  |                                         | TEST CONDITIONS                                                                                                                                                                                                                                                        |     | MIN | TYP | MAX | UNIT |

|----------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|------|

| I <sub>AM, 1.024MHz</sub>  | Active mode<br>current at<br>1.024 MHz  | $      f_{DCO} = 16.384 \text{ MHz}, \      f_{MCLK} = f_{SMCLK} = 1.024 \text{ MHz}, \\       f_{ACLK} = 32 \text{ kHz}, \\       Program executes from flash, \\       CPUOFF = 0, \ SCG0 = 0, \ SCG1 = 0, \ OSCOFF = 0 $                                            | 3 V |     | 1.6 |     | mA   |

| I <sub>AM, 8.192MHz</sub>  | Active mode<br>current at<br>8.192 MHz  | $      f_{\text{DCO}} = 16.384 \text{ MHz}, \      f_{\text{MCLK}} = f_{\text{SMCLK}} = 8.192 \text{ MHz}, \\       f_{\text{ACLK}} = 32 \text{ kHz}, \\       Program executes from flash, \\       CPUOFF = 0, \      SCG0 = 0, \      SCG1 = 0, \      OSCOFF = 0 $ | 3 V |     | 3.0 |     | mA   |

| I <sub>AM, 16.384MHz</sub> | Active mode<br>current at<br>16.384 MHz | $ \begin{array}{l} f_{DCO} = f_{MCLK} = f_{SMCLK} = 16.384 \mbox{ MHz}, \\ f_{ACLK} = 32 \mbox{ kHz}, \\ \mbox{Program executes from flash}, \\ \mbox{CPUOFF} = 0, \mbox{SCG0} = 0, \mbox{SCG1} = 0, \mbox{OSCOFF} = 0 \end{array} $                                   | 3 V |     | 4.5 |     | mA   |

#### 表 2. MSP430i2041 Active Mode Current Consumption<sup>(1) (2) (3)</sup>

<sup>(1)</sup> Over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

$^{(2)}$  All inputs are tied to 0 V or V<sub>cc</sub>. Outputs do not source or sink any current.

<sup>(3)</sup> All peripherals are inactive.

# 表 3. MSP430i2041 SD24 Current Consumption

| PARAMETER         |                                            | TEST CONDITIONS   |                      | V <sub>cc</sub> | MIN | TYP | MAX | UNIT |

|-------------------|--------------------------------------------|-------------------|----------------------|-----------------|-----|-----|-----|------|

| $V_{cc}$          | Supply voltage range                       | AVSS = DVSS = 0 V |                      |                 | 2.2 |     | 3.6 | V    |

|                   | Analog plus digital supply current per     | SD24OSRx =        | GAIN: 1, 2, 4, 8, 16 | 3 V             |     | 190 |     |      |

| I <sub>SD24</sub> | converter (reference current not included) | 256               | GAIN: 1, 16          | 3 V             |     |     | 250 | μA   |

This reference design uses a baud rate of 57600 baud. The current consumption of the isolators decreases as frequency decreases, which indicates that the maximum current consumption of the ISO7731 is less than the 3.4-mA maximum current consumption at 1 Mbps mentioned in 🕅 5. The capdrop in this implementation is designed to provide more than the 8.4 mA needed to power the MSP430i2041 core, the MSP430i2041 converters, and the digital isolators.

| PARAMETER                  | TEST CONDITIONS                                                                                                               |                                                                | SUPPLY<br>CURRENT | MIN | TYP | МАХ | UNIT |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------|-----|-----|-----|------|

| ISO7731                    |                                                                                                                               |                                                                |                   |     |     |     |      |

|                            | EN1 = EN2 = 0 V; V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup> (ISO7731);                                                  |                                                                | I <sub>CC1</sub>  |     | 0.8 | 1.2 | mA   |

| Supply ourront disable     | $V_1 = 0 \vee (ISO7731 \text{ with F suffix})$                                                                                |                                                                |                   |     | 0.7 | 1   | mA   |

| Supply current - disable   | $      EN1 = EN2 = 0 \forall; \forall_I = 0 \forall (ISO7731); \\ \forall_I = \forall_{CCI} (ISO7731 \text{ with F suffix}) $ |                                                                | I <sub>CC1</sub>  |     | 3   | 4.3 | mA   |

|                            |                                                                                                                               |                                                                | I <sub>CC2</sub>  |     | 1.8 | 2.6 | mA   |

|                            | $      EN1 = EN2 = V_{CCI}; V_I = V_{CCI} (ISO7731); \\ V_I = 0 \ V (ISO7731 \ with \ F \ suffix) $                           |                                                                | I <sub>CC1</sub>  |     | 1.3 | 1.7 | mA   |

|                            |                                                                                                                               |                                                                | I <sub>CC2</sub>  |     | 1.6 | 2.2 | mA   |

| Supply current - DC signal | EN1 = EN2 = V <sub>CCI</sub> ; V <sub>I</sub> = 0 V (ISO7731);                                                                | EN1 = EN2 = V <sub>CCI</sub> ; V <sub>I</sub> = 0 V (ISO7731); |                   |     | 3.5 | 5   | mA   |

|                            | $V_1 = V_{CCI}$ (ISO7731 with F suffix)                                                                                       |                                                                | I <sub>CC2</sub>  |     | 2.8 | 4.1 | mA   |

|                            |                                                                                                                               | 1 Mbps                                                         | I <sub>CC1</sub>  |     | 2.4 | 3.4 | mA   |

|                            |                                                                                                                               | 1 Mups                                                         | I <sub>CC2</sub>  |     | 2.2 | 3.3 | mA   |

# 图 5. ISO7731 Current Consumption

# 2.3.1.2 External Resistor and Oscillator For Metrology AFE Clock

The MSP430i2041 internal DCO supports two modes of operation. This device can operate with an internal resistor or an external resistor that is connected to ROSC pin of the device. The internal resistor option is the lowest cost option because it does not require any external components while the external resistor option provides the most accurate clock. When selecting the external resistor option, a recommended 20-k $\Omega$ , ±50-ppm resistor with 0.1% tolerance is recommended. This resistor is populated on this reference design in case it is desired to use external resistor option because the energy accumulation from power is done by the MSP432 host MCU and using the internal resistor option is the lowest cost option. For applications that require an accurate clock for precise measurement of other time dependent calculations besides energy (such as line frequency), the external resistor option can be used by modifying the metrology AFE firmware to select the external resistor option instead of the internal resistor option.

#### 2.3.1.3 Analog Inputs

The MSP430i2041's AFE circuitry, which consists of the  $\Sigma\Delta$  ADC within the MSP430i2041's SD24 module, is differential and requires that the input voltages at the pins do not exceed ±928 mV when a gain of 1 is used and ±58 mV when a gain of 16 is used. To meet this specification, the current and voltage inputs need to be scaled down. In addition, the SD24 ADCs allows a maximum negative voltage of -1 V. Therefore, the AC current signal from mains can be directly interfaced without the need for level shifters. This section describes the AFE circuitry used for the voltage and current channels.

#### 2.3.1.3.1 Voltage Front End Circuitry

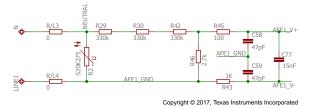

The voltage from the mains is usually 230 V or 120 V and must be scaled down within 928 mV. The AFE circuitry for voltage consists of spike protection variators followed by a voltage divider network, and a RC low-pass filter that acts like an antialiasing filter. For this design, footprints for suppressant inductors are also available. These inductor footprints are shown in  $\mathbb{K}$  6 as R/L3 and R/L4, and by default are populated with 0- $\Omega$  resistors.

图 6. MSP430i2041 Voltage Front-End Circuitry

If 6 shows the AFE circuitry for the voltage inputs for a mains voltage of 230 V. In this circuitry, the voltage is brought down to approximately 626-mV RMS, which is a 885-mV peak, and fed to the positive input of the convertor. The antialiasing resistors on the positive and negative sides are different because the input impedance to the positive terminal is much higher; therefore, a lower value resistor is used for the antialiasing filter. If this is not maintained, a relatively large phase shift appears between voltage and current samples.

# 2.3.1.3.2 Current Front-End Circuitry

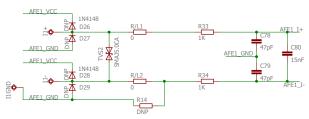

The AFE circuitry for current inputs is slightly different from the AFE circuitry for the voltage inputs. [8] 7 shows the AFE circuitry used for a current channel.

www.ti.com.cn

Copyright © 2017, Texas Instruments Incorporated

图 7. MSP430i2041 Current Front-End Circuitry

The AFE circuitry for current consists of diodes and transorbs for any additional transient voltage suppression, footprints (R/L1 and R/L2) that could be replaced with inductors for EMI suppression (these footprints are populated with  $0-\Omega$  resistors by default), and an antialiasing filter.

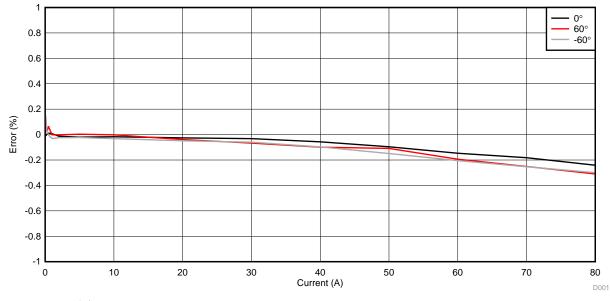

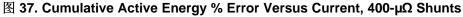

▲ 7 shows the three-terminal shunt used for current measurement to be connected at I1+, I1−, and I1GND. The value of this shunt is selected based on balancing maximizing the peak analog voltage input into the MSP430i2041 with minimizing the power dissipation of the shunt. In particular, for optimal accuracy, the peak DC voltage fed into the MSP430i2041 must be as close as possible to 58 mV without surpassing this voltage. This peak voltage is dependent on the rated maximum current of the system and the resistance of the selected shunt. For example, this reference design uses 400-µΩ shunts (for more information on the shunts used, see http://www.vishay.com/docs/30173/wsms3124.pdf). With these 400-µΩ shunts and a maximum RMS current of 90 A, the maximum DC voltage fed into the MSP430i2041 SD24 ADC is 90 ×  $\sqrt{2}$  × (400 × 10<sup>-6</sup>) = 51 mV. To minimize the power dissipation in the shunt, a smaller value shunt can also be used. This reference design also uses 220-µΩ shunts; however, by using smaller value shunts, the voltage fed into the MSP430i2041 ADC is also reduced. As a result, there is a tradeoff in accuracy. Based on the requirements of the system, the tradeoff in accuracy from using a shunt with a small resistance and the reduced power dissipation from choosing the smaller shunt must be taken into account when selecting the proper shunt value.

#### 2.3.2 Design Software Implementation

This section discusses the software for this reference design.  $\ddagger$  2.3.2.1 discusses the setup of various peripherals of the metrology and host processors.  $\ddagger$  2.3.2.2 and  $\ddagger$  2.3.2.3 describe the metrology software as two major processes: the foreground process and background process.  $\ddagger$  2.3.2.4 describes the application software.  $\ddagger$  2.3.2.5 describes the MSP430i2041 to MSP432 communication process.

#### 2.3.2.1 Peripheral Setup

# 2.3.2.1.1 MSP430i2041 Start-up Code

The INFO memory of each MSP430i2041 device stores device-specific calibration values. These values affect items such as clock accuracy, SD24 operation, and reference voltage operation. For proper functionality of this device, these values need to be loaded into the proper calibration and trim registers, as mentioned in the TLV and Start-Up Code section of the *MSP430i2xx Family User's Guide*. In addition, a decision whether to secure or unsecure the MSP430i2041 must be made in the first 64 MCLK cycles after RESET. Both of these functions are accomplished in the low\_level\_init function (in low\_level\_init.c), which runs before even the main function is called.

Because the device-specific peripheral calibration is stored in INFO memory, do not change the project settings to erase INFO memory as that erases these values. Also note that meter calibration data is stored in the same segment as the peripheral calibration information. As a result, do not delete the peripheral calibration values if performing meter calibration. This reference design stores the device-specific peripheral calibration data before erasing the INFO memory, and then rewrites INFO memory with this peripheral calibration factors as well as any new meter accuracy calibration factors.

#### 2.3.2.1.2 MSP430i2041 SD24 Setup

The MSP430i2041 has four sigma-delta data converters, which are used to measure the voltage and currents in the system. This reference design only uses two of the four sigma-delta converters. For the MSP430i2041, the clock to the SD24 ADCs ( $f_M$ ) is fixed at 1.024000 MHz. In the software, an OSR of 256 is chosen, which results in a sampling frequency of 4.000 ksps for the converters. At every sampling instance, the ADCs are configured to generate regular interrupts.

In the software, the following channel associations are used:

- A0.0+ and A0.0-  $\rightarrow$  Current

- A1.0+ and A1.0-  $\rightarrow$  Voltage

#### 2.3.2.1.3 MSP430i2041 AFE UART Setup

The MSP430i2041 is configured to communicate to the MSP432P4111 using a UART module configured for 8N1 at 57,600 baud. When the device is configured in two-channel mode, the UART TX pin is switched between UART TX functionality and DRDY GPIO functionality.

#### 2.3.2.1.4 MSP432P4111 Clock Setup

The MSP432 is configured to have its CPU clock (MCLK) set at 48 MHz and its subsystem master clock (SMCLK) set to 12 MHz. The clock source for MCLK and SMCLK is an external 48-MHz crystal. An external 32.768-kHz crystal is used as the clock source for the device's auxiliary clock (ACLK). This ACLK clock is set to a frequency of 32.768 kHz. The clock is configured using MSP432 driverlib functions.

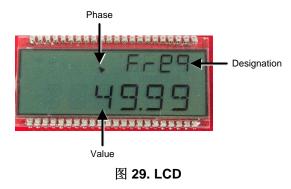

#### 2.3.2.1.5 MSP432P4111 LCD Controller

The LCD controller on the MSP432P4111 can support up to 8-mux displays and 320 segments or 4-mux displays and 176 segment displays. In the current design, the LCD controller is configured to work in 4-mux mode using 144 segments. The eight segment lines not used in this design's 4-mux mode are used for the port mapping functionality that allows multiplexing multiple TX signals from the MSP430i2041 to the RX signal of only one UART module. To use the full 176 segments in 4-mux mode, the port mapping functionality might not be able to be used to multiplex the different TX signals. Instead, external logic gates may need to be used to OR/AND the multiple TX signals to only one pin on the MSP432P4111. In this reference design, the LCD is configured for a refresh rate set to ACLK/64, which is 512 Hz. For contrast control, external resistors are added between the R23, R13, R03 pins and GND, as shown in 🕅 8. The LCD is configured primarily using MSP432 driverlib functions.

图 8. LCD External Resistors

# 2.3.2.1.6 MSP432P4111 Real Time Clock (RTC)

The MSP432's real-time clock module is configured to give precise one second interrupts. Based off of these one second interrupts, the time and date are updated in software, as necessary. The RTC is configured using MSP432 driverlib functions.

# 2.3.2.1.7 MSP432P4111 UART Setup for GUI Communication

The MSP432 MCU is configured to communicate to the PC GUI through the RS-232 connection on this reference design. The MSP432 MCU communicates to the PC GUI using a UART module configured for 8N1 at 9600 baud. The UART is configured using MSP432 driverlib functions.

# 2.3.2.1.8 MSP432P4111 Timer Setup

In this reference design, the MSP432 MCU uses Timer\_A1 to create interrupts at a rate of 4000 Hz. This timer accumulates active power readings into active energy and to keep track of necessary timeouts. In addition, the timer is used to space out requesting metrology parameters for different phases to ensure that there is enough time to receive metrology parameters of a phase before the next phase's metrology parameters are requested. The timer ensures that there is a fixed time delay from when a phase's new metrology readings are ready to when they are requested. The timer is configured using the MSP432 timer driver.

# 2.3.2.1.9 MSP432P4111 Port Mapping

The MSP432 MCU has a port mapping controller that allows a flexible mapping of digital functions to port pins. The set of digital functions that can be ported to other pins is dependent on the device. For the MSP432 device in particular, the EUSCIA1 UART module's TX and RX functionality are available to ports P2, P3, and P7. In this reference design, this port mapping feature provides flexibility in the PCB layout as well as multiplexing the three TX signals from the different MSP430i2041 devices to the RX signal of the same EUSCIA1 UART port. In this reference design, the three different TX signals are connected to different port mappable GPIO pins. Each of these pins have their port mapping functionality changed switched between "PMAP\_NONE" functionality, which disables mapping a digital function to a particular

pin, and "PMAP\_UCA1RXD", which enables communication to a corresponding metrology AFE. The design's software ensures that only one port mapping pin at a time is configured to PMAP\_UCA1RXD functionality. Whenever the MSP432 device requests data from a particular metrology AFE, the MCU sends the command to all the metrology AFEs and enables only the PMAP\_UCA1RXD functionality on the MSP432's port mapping GPIO pin that is connected to the desired MSP430i2041's UART TX pin.

When the host is configured for two-channel mode, the port mapping pins are also switched from port mapping functionality to interruptible GPIO pins. Because only the P2 and P3 ports of the MSP432 have both port mappable and interruptible GPIO input pins, this two-channel mode only works with ports P2 and P3 on the MSP432. In two-channel mode, the port mapping pins are configured as interruptible input pins majority of the time. The only time the port mapping pins are configured for the PMAP\_UCA1RXD functionality is when the MSP432 has sent a command to a specific MSP430i2041 device and it is expecting a response back. Once the requested data has been correctly received by the MSP432P4111 or there has been a timeout, the corresponding port mapping pin is configured back to be an interruptible GPIO pin.

Using the port mapping controller, the following mappings are used:

- PMAP\_UCA1TXD (EUSCIA1 UART TX) → Port P2.6

- PMAP\_UCA1RXD (EUSCIA1 UART RX) → Port P2.5 (Connected to the isolated UART Tx signal from Phase A's MSP430i2041)

- PMAP\_UCA1RXD (EUSCIA1 UART RX) → Port P2.3 (Connected to the isolated UART Tx signal from Phase B's MSP430i2041)

- PMAP\_UCA1RXD (EUSCIA1 UART RX) → Port P2.1 (Connected to the isolated UART Tx signal from Phase C's MSP430i2041)

The port mapping functionality is configured using the driverlib; however, the majority of the other GPIO pins are configured using the MSP432 GPIO driver.

#### 2.3.2.1.10 MSP432P4111 Direct Memory Access (DMA)

The direct memory access (DMA) module transfers packets from the MSP430i2041 to the MSP432P4111 with minimal bandwidth requirements from the MSP432's CPU. Only the third channel of the DMA is used. The DMA transfers each byte received from the MSP432's EUSCIA1 UART module's RX signal to memory until an entire packet of data has been received. Once an entire packet of data has been obtained, the DMA module triggers an interrupt to immediately parse any critical data.

# 2.3.2.1.11 MSP432P4111 Interrupt Priorities

The software has five interrupts that are priorities.  $\frac{1}{2}$  4 lists these interrupt priorities, with the smaller priority codes having higher interrupt priorities.

| INTERRUPT | SIGNIFICANCE                                                                                                          | PRIORITY CODE |

|-----------|-----------------------------------------------------------------------------------------------------------------------|---------------|

| TA1_0     | Update energy accumulation registers and timeout state                                                                | 0x20          |

| PORT2     | New metrology readings are now available for a particular MSP430i2041 device                                          | 0x40          |

| DMA1      | Received response packet from a MSP430i2041 device                                                                    | 0x60          |

| EUSCIA0   | UART transmit buffer empty for sending a packet to the PC GUI or new UART character has been received from the PC GUI | 0x80          |

| RTC       | A new second has elapsed every time this interrupt is triggered. Every two seconds, update the LCD.                   | 0x80          |

# 表 4. MSP432P4111 Interrupt Priorities

# 2.3.2.2 MSP430i2041 Metrology Foreground Process

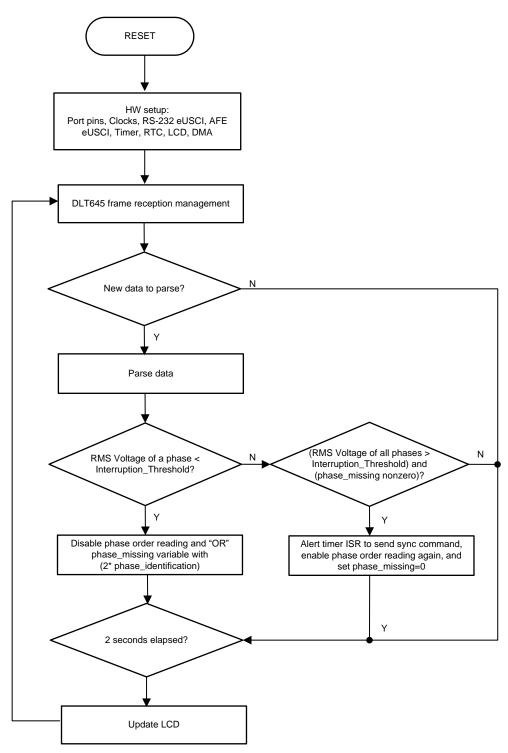

The foreground process includes the initial setup of the MSP430i2041 hardware and software immediately after a device RESET. 🔀 9 shows the flowchart for this process.

System Overview

图 9. Metrology Foreground Process

The initialization routines involve the setup of the ADC, clock system, general purpose input/output (port) pins, phase identification (whether a particular device is set to be Phase A, Phase B, or Phase C), and the USCI\_A0 for UART functionality. After the hardware is set up, any received frames from the MSP432P4111 are processed. Subsequently, the foreground process checks whether the background process has notified it to calculate new metering parameters. This notification is done through the assertion of the "PHASE\_STATUS\_NEW\_LOG" status flag whenever a frame of data is available for processing. The data frame consists of the processed dot products that were accumulated for 50 cycles in the background process.

The processed dot products include the  $V_{RMS}$ ,  $I_{RMS}$ , active power, and reactive power. These dot products are used by the foreground process to calculate the corresponding metrology readings in real world units. Processed voltage dot products are accumulated in 48-bit registers. In contrast, processed current dot products, active energy dot products, and reactive energy dot products are accumulated in separate 64-bit registers to further process and obtain the RMS and mean values. Using the foreground's calculated values of active and reactive power, the apparent power is calculated. The frequency (in Hertz) and power factor are also calculated using parameters calculated by the background process using the formulas in  $\ddagger$ 2.3.2.2.1. Once new metrology readings have been calculated, the DRDY pin is asserted low for a duration of approximately 5 ms, thereby alerting the MSP432 MCU that new metrology parameters are ready.

# 2.3.2.2.1 MSP430i2041 Metrology Formulas

This section briefly describes the formulas used for the voltage, current, and power calculations. As previously described, voltage and current samples are obtained at a sampling rate of 4000 Hz. All of the samples that are taken in 50 cycles are kept and used to obtain the RMS values for voltage and current for each phase. The RMS values are obtained by the following formulas:

$$V_{RMS,ph} = K_{v,ph} \times \sqrt{\frac{\sum_{n=1}^{Sample} v_{ph}(n) \times v_{ph}(n)}{Sample \ count} - v_{offset,ph}}}$$

(1)

$$I_{RMS,ph} = K_{i,ph} \times \sqrt{\frac{\sum_{n=1}^{Sample} i_{ph}(n) \times i_{ph}(n)}{Sample \ count} - i_{offset,ph}}}$$

(2)

where:

- ph = Phase parameters that are being calculated [that is, Phase A (= 1), B (= 2), or C (= 3)],

- V<sub>ph</sub>(n) = Voltage sample at a sample instant n,

- V<sub>offset,ph</sub> = Offset used to subtract effects of the additive white Gaussian noise from the voltage converter,

- I<sub>ph</sub>(n) = Each current sample at a sample instant n,

- I<sub>offset.ph</sub>= Offset used to subtract effects of the additive white Gaussian noise from the current converter,

- Sample count = Number of samples in 50 cycles,

- K<sub>v,ph</sub> = Scaling factor for voltage,

- K<sub>i,ph</sub> = Scaling factor for current.

Power and energy are calculated for a frame's worth of active and reactive energy samples. These samples are phase corrected and passed on to the foreground process, which uses the number of samples (sample count) to calculate phase active and reactive powers through the following formulas:

System Overview

$$P_{ACT,ph} = K_{ACT,ph} \frac{\sum_{n=1}^{Sample Count} v(n) \times i_{ph}(n)}{Sample Count} - P_{ACT_Offset,ph}$$

(3)

Sample Count

$$P_{\text{REACT, ph}} = K_{\text{REACT, ph}} - \frac{\sum_{n=1}^{n-1} V_{90, ph}(n) \times V_{ph}(n)}{\text{Sample Count}} - P_{\text{React}_Offset, ph}$$

(4)

$$P_{APP,ph}^{2} = \sqrt{P_{ACT,ph}^{2} + P_{REACT,ph}^{2}}$$

<sup>(5)</sup>

where:

- V<sub>90</sub>(n) = Voltage sample at a sample instant 'n' shifted by 90°,

- K<sub>ACT,ph</sub> = Scaling factor for active power,

- K<sub>REACT,ph</sub> = Scaling factor for reactive power,

- P<sub>ACT\_offset,ph</sub> = Offset used to subtract effects of crosstalk on the active power measurements from other phases and the neutral,

- P<sub>REACT\_offset,ph</sub> = Offset used to subtract effects of crosstalk on the reactive power measurements from other phases and the neutral.

Note that for reactive energy, the 90° phase shift approach is used for two reasons:

- 1. This approach allows accurate measurement of the reactive power for very small currents.

- 2. This approach conforms to the measurement method specified by IEC and ANSI standards.

The calculated mains frequency calculates the 90 degrees-shifted voltage sample. Because the frequency of the mains varies, first measure the mains frequency accurately to phase shift the voltage samples accordingly.

To get an exact 90° phase shift, interpolation is used between two samples. For these two samples, a voltage sample slightly more than 90 degrees before the current sample and a voltage sample slightly less than 90 degrees before the current sample are used. The application's phase shift implementation consists of an integer part and a fractional part. The integer part is realized by providing an N samples delay. The fractional part is realized by a one-tap FIR filter. In the software, a lookup table provides the filter coefficients that are used to create the fractional delays.

The background process also calculates the frequency in terms of samples per mains cycle. The foreground process then converts this samples per mains cycle unit to Hertz using  $\Delta \pm 6$ :

Frequency

$$(Hz) = \frac{\text{Sample Rate (samples / second)}}{\text{Frequency (samples / cycle)}}$$

(6)

After the active power and apparent power have been calculated, the absolute value of the power factor is calculated. In the system's internal representation of power factor, a positive power factor corresponds to a capacitive load; a negative power factor corresponds to an inductive load. The sign of the internal representation of power factor is determined by whether the current leads or lags voltage, which is determined in the background process. Therefore, the internal representation of power factor is calculated using  $\Delta \vec{x}$  7:

(7)

$$\label{eq:Internal Representation of Power Factor} = \begin{cases} \frac{\mathsf{P}_{Act}}{\mathsf{P}_{Apparent}}, \text{ if capacitive load} \\ -\frac{\mathsf{P}_{Act}}{\mathsf{P}_{Apparent}}, \text{ if inductive load} \end{cases}$$

#### MSP430i2041 Metrology Background Process 2.3.2.3

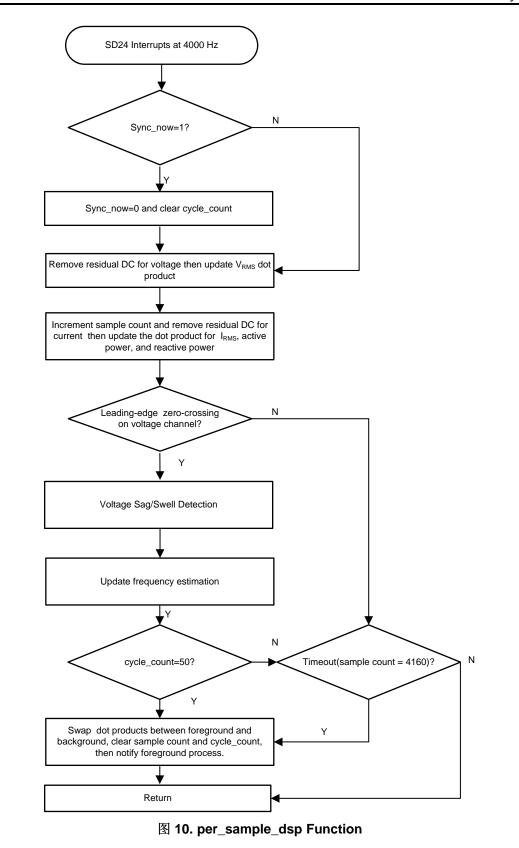

The background function deals mainly with timing critical events in software. This function uses the SD24 interrupt as a trigger to collect voltage and current samples. The SD24 interrupt is generated when a new voltage sample is ready. Once the voltage sample is obtained, sample processing is done on the previously obtained voltage and current samples. This sample processing is done by the "per sample dsp()" function.

#### 2.3.2.3.1 per sample dsp

The flowchart for the per\_sample\_dsp function is shown in 8 10. In this function, the per\_sample\_dsp function calculates intermediate dot product results that are fed into the foreground process for the calculation of metrology readings. Because 16-bit voltage samples are used, the voltage samples are further processed and accumulated in dedicated 48-bit registers. In contrast, because 24-bit current samples are used, the current samples are processed and accumulated in dedicated 64-bit registers. Perphase active power and reactive power are also accumulated in 64-bit registers.

After sufficient samples have been accumulated, the foreground function is triggered to calculate the final values of  $V_{RMS}$ ,  $I_{RMS}$ , active, reactive, and apparent powers, active, reactive, and apparent energy, frequency, and power factor. The foreground process is triggered to calculate new parameters every 50 cycles. If mains voltage is not available, a timeout is set to trigger the foreground process to calculate new metrology readings after 4160 samples. To ensure that the assertion of the DRDY GPIO pin is synchronized among all the MSP430i2041 devices, a sync command is sent by the MSP432P4111 to all of the MSP430i2041 devices. This sync command clears the current count of the cycle\_count variable used to trigger the foreground process. The MSP432 device sends this sync command whenever a phase's mains voltage becomes available after it was previously unavailable.

In the software, there are two sets of dot products: at any given time, one is used by the foreground for calculation and the other used as the working set by the background. After the background process has sufficient samples, it swaps the two dot products so that the foreground uses the newly acquired dot products that the background process just calculated and the background process uses a new empty set to calculate the next set of dot products.

Whenever there is a leading-edge zero-crossing (- to + voltage transition) on a voltage channel, the per sample dsp function is also responsible for updating the corresponding phase's frequency (in samples/cycle) and voltage sag and swell conditions. For the sag conditions, whenever the RMS voltage is below a certain user-defined threshold percentage, the number of mains cycles where this condition persists is logged as the sag duration. The sag threshold is based on the settings of the SAG THRESHOLD and MAINS NOMINAL VOLTAGE macros within the metrology-template.h file. An event is defined as being a sag when the RMS voltage is below the following value:

$\frac{(100 - SAG_THRESHOLD)}{100} \times MAINS_NOMINAL_VOLTAGE$

www.ti.com.cn

The number of occurrences where there was a sag condition is logged as the sag events count. Note that the sag duration corresponds to the total number of cycles in a sag condition since reset and is therefore not cleared for every sag event. Also, when the RMS voltage is above a certain threshold percentage, swell events and duration are logged in a similar way; except then an event is defined as being a swell event when the calculated RMS voltage is above the following value:

$\left(\frac{(100 + SAG_THRESHOLD)}{100}\right) \times MAINS_NOMINAL_VOLTAGE$

(9)

#### 2.3.2.3.1.1 Voltage and Current Signals

The output of each SD24 converter is a signed integer and any stray DC or offset value on these converters is removed using a DC tracking filter. Separate DC estimates for all voltages and currents are obtained using the filter and voltage and current samples, respectively. These estimates are then subtracted from each voltage and current sample.

The resulting instantaneous voltage and current samples are used to generate the following intermediate dot product results:

- Accumulated squared values of voltages and currents, which is used for V<sub>RMS</sub> and I<sub>RMS</sub> calculations, respectively

- Accumulated energy samples to calculate active powers

- Accumulated energy samples using current and 90° phase shifted voltage to calculate reactive powers

These accumulated values are processed by the foreground process.

#### 2.3.2.3.1.2 Frequency Measurement and Cycle Tracking

The instantaneous voltage of each phase is accumulated in 48-bit registers. In contrast, the instantaneous current, active power, and reactive power are accumulated in 64-bit registers. A cycle tracking counter and sample counter keep track of the number of samples accumulated. When approximately 50 cycles worth of samples have been accumulated, the background process switches the foreground and background then notifies the foreground process to produce the average results such as RMS and power values.

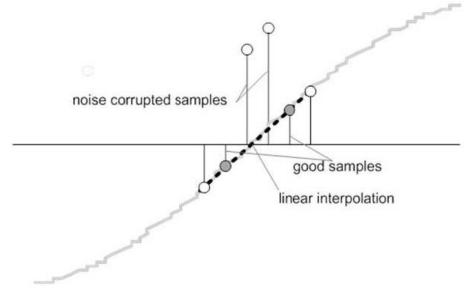

For frequency measurements, a straight line interpolation is used between the zero crossing voltage samples. 🛽 11 shows the samples near a zero cross and the process of linear interpolation.

#### 图 11. Frequency Measurement

Because noise spikes can also cause errors, the application uses a rate of change check to filter out the possible erroneous signals and makes sure that the two points are interpolated from are genuine zero crossing points. For example, with two negative samples, a noise spike can make one of them positive and therefore make the negative and positive pair looks as if there is a zero crossing.

(10)

The resultant cycle-to-cycle timing goes through a weak low-pass filter to further smooth out cycle-to-cycle variations. This results in a stable and accurate frequency measurement that is tolerant of noise.

#### 2.3.2.3.2 Phase Compensation

To ensure accurate measurements, the relative phase shift between voltage and current samples must be compensated. This phase shift can be caused by the passive components of the voltage and current input circuit. The SD24 converters have programmable delay registers (SD24PREx) that can be applied to any current or voltage channel. This built-in feature (PRELOAD) is used to provide the phase compensation required.

The fractional delay resolution of the preload register is a function of input frequency ( $f_{IN}$ ), OSR, and the sampling frequency ( $f_{s}$ ):

$\text{Delay resolution}_{\text{Deg}} = \frac{360^{\circ} \times f_{\text{IN}}}{\text{OSR} \times f_{s}} = \frac{360^{\circ} \times f_{\text{IN}}}{f_{\text{M}}}$

In this application, for an input frequency of 50 Hz, OSR of 256, and sampling frequency of 4000, the resolution for every bit in the preload register is approximately 0.02° with a maximum of 4.48° (maximum of 255 steps).

# 2.3.2.4 MSP432P4111 Host Software

# 2.3.2.4.1 Peripheral Setup and Idle Tasks

After the MSP432 MCU resets, the device initializes its peripherals. The initialization routines involve the setup of the GPIO port pins and associated port map controller; clock system; eUSCI\_A0 UART module for communication to a PC GUI using RS-232; eUSCI\_A1 UART module for communication to the different MSP430i2041 metrology AFEs; timer; RTC for keeping track of time; LCD; and DMA for streamlining communication from the metrology AFEs.

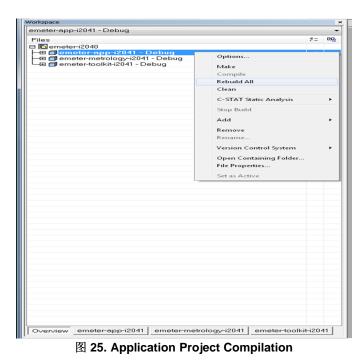

Once the MSP432P4111 has completed setup of its peripherals, the device enters a loop where it performs low-priority tasks until it is interrupted by hardware interrupts. (12) shows a flowchart of the peripheral setup and the idle tasks performed.

The first task performed in the loop is to process any received frames from the GUI. Next, the application checks to see if there is new, noncritical data from any of the MSP430i2041 devices that need to be parsed (any critical data is parsed in the DMA interrupt service routine itself instead of in this loop). If there is new data available to parse, the data is parsed and used to update the MSP432P4111's internal variables if necessary. When there are new metrology parameters to parse and the RMS voltage is

parsed, a check is made to determine if the RMS voltage reading of the phase is sufficiently larger than a defined interruption threshold. If the RMS voltage for the phase is below this threshold, then the phase is determined to be missing so the phase order calculations are disabled. If the RMS voltage for all phases is above the interruption threshold after one or more phases were previously declared as missing, a sync command is sent to all the MSP430i2041 devices and the phase order calculations are enabled again. Finally, the application checks to see if a new 2-second interval has elapsed since the last time the LCD has been updated. The RTC keeps track of when a new 2-second interval has occurred and alerts this LCD idle task of this new 2-second interval so that the LCD can be updated to display a new metrology parameter.

# 2.3.2.4.2 Port 2 ISR

Whenever any of the MSP430i2041 devices has just calculated new metrology parameters, the MSP430i2041 asserts a DRDY GPIO pin low to alert the MSP432 MCU that new parameters are now ready. The assertion of this MSP430i2041 GPIO pin specifically triggers the MSP432 Port 2 ISR. In this ISR, the application keeps track of the relative order of when the different DRDY pins are asserted. When each phase's line voltage is available, this order of when the different DRDY pins are asserted determine the phase sequence. In addition, the timer's count when a particular MSP430i2041's DRDY pin was asserted is logged. This timer count is used by the timer ISR to determine the intentional delay that must be added before the MSP432 actually requests a phase's metrology parameters. In this reference design, the intentional delay from DRDY assertion to request of metrology parameters is 0 ms for phase A, 20 ms for phase B, and 40 ms for phase C. This delay ensures that there is enough time to get the metrology parameters from a phase. In addition to using the timer count for adding intentional delays for metrology parameters, this timer count also determines when a particular phase times out.

# 2.3.2.4.3 Timer ISR

The timer ISR is triggered at a rate of 4000 Hz. Every time this ISR is called, the timer\_count\_update and energy\_processing functions are called. The following two sections go over these functions.

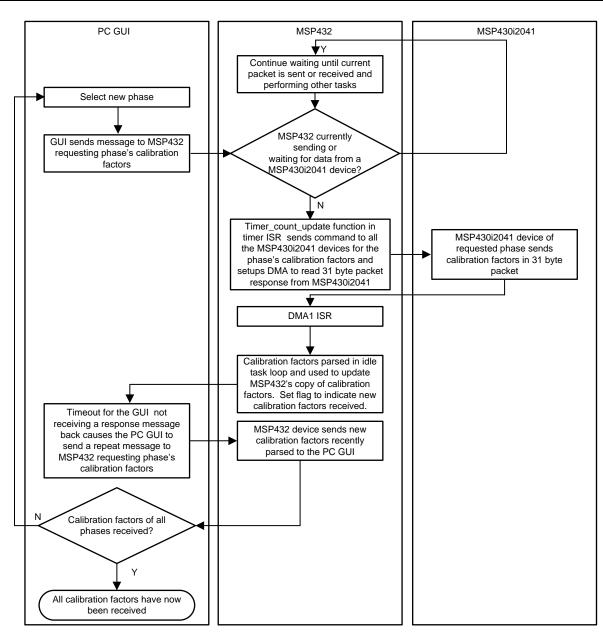

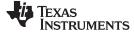

#### 2.3.2.4.3.1 timer\_count\_update

The timer\_count\_update function serves two purposes. The first purpose is to send commands to the MSP430i2041 devices at the proper point in time. Whenever there is a request to send a sync command to all the MSP430i2041 devices for ensuring correct phase sequence measurements, the timer\_count\_update function is where this actual sync command is sent to the MSP430i2041 devices. In addition, this function is where the MSP432P4111 sends the commands to request metrology parameters from any MSP430i2041 device that has indicated through its DRDY GPIO pin that a new frame of data has been calculated. To ensure that there is enough time to transfer the data packets from each MSP430i2041 device, there is an intentional delay added from when the DRDY GPIO pin was asserted to when the timer\_count\_update function requests the metrology parameters for a phase. The intentional delay from DRDY assertion to request of metrology parameters is 0 ms for phase A, 20 ms for phase B, and 40 ms for phase C. Whenever there is a request to get the calibration factors from a MSP430i2041 device, the function is also where the actual request command for the calibration factor is sent to the MSP430i2041.

www.ti.com.cn

The second purpose of the timer\_count\_update function is to keep track of timeouts and to take the appropriate action when there is a timeout. The first set of timeouts managed by this function are triggered when the previous set of metrology readings for a phase has been received more than approximately 1.05 seconds ago. This timeout considers the scenario where the DRDY pin has been asserted by the MSP430i2041 and the MSP432 device has made a request for the new metrology parameters but it has not received a valid response from the MSP430i2041. In addition, this timeout also considers the scenario where the DRDY pin has not been asserted at all. This reference design has a separate timeout for each individual phase. Whenever a timeout occurs for a particular phase, the metrology parameters for that associated phase are set to 0 and a flag is asserted to let the application know that phase is missing. The second set of timeouts managed by the timer\_count\_update function determine if a request has been sent to an MSP430i2041 device but a response has not been received within 0.25 seconds from when the request was sent to specified MSP430i2041 device.

When a request for metrology readings or calibration factors has been sent to a specified MSP430i2041, any other requests for metrology readings or calibration factors are not made until the specified MSP430i2041 either gets the requested data or the specified command timeout for that phase occurs. Each time the MSP432P4111 requests a parameter from a specified MSP430i2041 device, the corresponding MSP432 UART RX pin that is connected to that MSP430i2041 device is enabled by modifying the port mapping controller to output the UART RX functionality on this pin. Simultaneously, the UART RX functionality is disabled from the UART RX pins for the other MSP430i2041 devices. If the two-channel mode is selected in this design, there is an additional step of also enabling the UART RX pin from GPIO mode to peripheral mode. If the system is in two-channel mode and the MSP430i2041 gets a requested response from a specified MSP430i2041 device or there is a timeout for the request sent to the MSP430i2041, the shared DRDY/UART RX pin of the specified MSP430i2041 is set from UART RX pin mode to GPIO mode. Switching to GPIO mode enables the MSP432 MCU to detect the next time the MSP430i2041 has calculated new metrology parameters.

# 2.3.2.4.3.2 energy\_processing

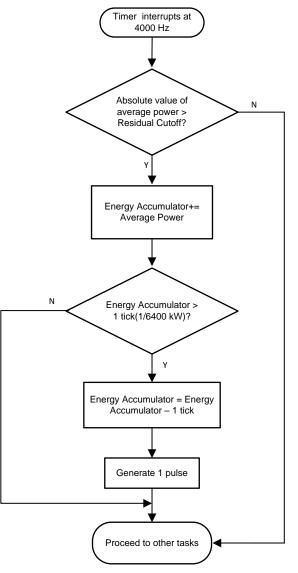

#### 2.3.2.4.3.2.1 Pulse Generation

In electricity meters, the active energy consumed is normally measured in fraction of kilowatt-hour (kWh) pulses. This information can be used to calibrate any meter for accurate measurement. The meter is responsible for generating pulses proportional to the energy consumed.

This application uses average power to generate these energy pulses. If the absolute value of the average power is greater than the residual power cutoff value set in software, the average power is accumulated during every timer interrupt, thereby spreading the accumulated energy from the previous frame of data evenly for each interrupt in the current 50 cycles frame. This is equivalent to converting it to energy. When the accumulated energy crosses a threshold, a pulse is generated. The amount of energy above this threshold is kept and new energy value is added on top of it in the next interrupt cycle.

The residual power cutoff value is used to set the cutoff power reading at which the meter must not register power readings. If the absolute value of a power reading is below this cutoff value, then the power is not accumulated for the energy pulses. Additionally, if any phase's power reading is below this power cutoff value, then the corresponding cumulative energy reading used for pulse generation does not accumulate that phase's power reading.

The threshold determines the energy "tick" specified by meter manufacturers and is a constant. A tick is usually defined in pulses per kWh or just in kWh. One pulse is generated for every energy tick. For example, in this application, the number of pulses generated per kWh is set to 6400 for active and reactive energies. The energy tick in this case is 1 kWh/6400. Energy pulses are generated and available on a header and also through LEDs on the board. General-purpose I/O (port) pins are used to produce the pulses.

In the reference design, the LEDs that are labeled "Active" and "Reactive" correspond to the aggregate active energy consumption, respectively. The number of pulses per kWh and each pulse duration can be configured in software. 🕅 13 shows the flow diagram for pulse generation. This flow diagram is valid for active and reactive energy.

图 13. Pulse Generation

The average power is in units of 0.001 W and the 1 kWh threshold is defined as:

1-kWh threshold =  $(1 / 0.001) \times 1$  kW × (number of interrupts per second) × (number of seconds in one hour) = 1000000 × 4000 × 3600 = D18C2E28000

#### 2.3.2.4.3.2.2 Energy Buffers

In addition to outputting energy pulses to indicate energy consumption, this reference design also stores the total consumed energy readings into separate buffers, which can be seen from the PC GUI. These buffers store the total amount of energy consumed since a system reset. The energy stored in these energy buffers are accumulated in a similar method as the energy used for pulse generation except a different energy tick is used. Instead of each tick corresponding to 1 kWh/6400 as is the case for pulse generation, the internal tick value corresponds to 0.1 Wh. This value means that the energy buffers in the MSP432P4111 software is in units of 0.1 Wh.

Similar to the energy used for pulse generation, the residual power cutoff value is used to set the cutoff power reading at which the meter must not register power readings. If the absolute value of a power reading is below this cutoff value, then the power is not accumulated into the energy buffers. Additionally, if any phase's power reading is below this power cutoff value, then the corresponding cumulative energy buffers does not accumulate that phase's power reading.

In this reference design, there are four sets of buffers that are available: one for each phase and one for the cumulative of the phases. Within each set of buffers, the following energies are accumulated:

- 1. Active import energy (active energy when active energy  $\geq 0$ )

- 2. Active export energy (active energy when active energy < 0)

- 3. React. Quad I energy (reactive energy when reactive energy  $\geq$  0 and active power  $\geq$  0; inductive load)

- React. Quad II energy (reactive energy when reactive energy ≥ 0 and active power < 0; capacitive generator)

- 5. React. Quad III energy (reactive energy when reactive energy < 0 and active power < 0; inductive generator)

- React. Quad IV energy (reactive energy when reactive energy < 0 and active power ≥ 0; capacitive load)

- 7. App. import energy (apparent energy when active energy  $\geq 0$ )

- 8. App. export energy (apparent energy when active energy < 0)

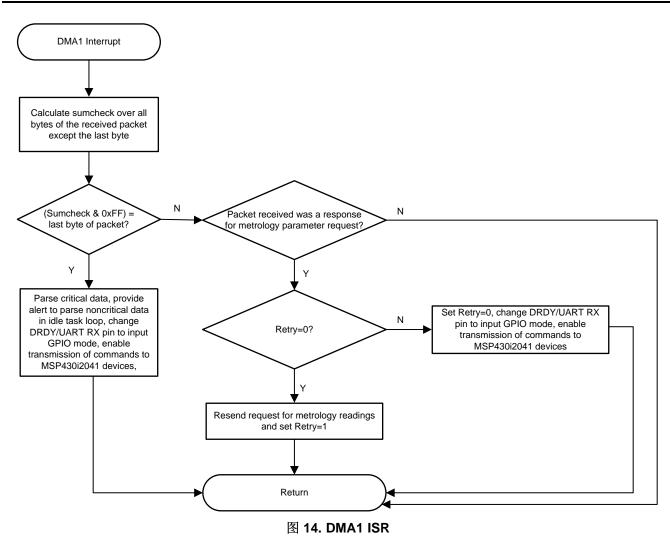

# 2.3.2.4.4 DMA1 ISR

When the MSP432P4111 sends a request for metrology parameters or calibration factors to an MSP430i2041 device, the DMA module is used to place the packet response from the MSP430i2041 in memory without CPU intervention. Once an entire packet is received, the DMA1 interrupt is triggered. 14 shows the flowchart of the DMA1 ISR. In this ISR, the application calculates a checksum and compares it to the checksum value in the packet sent. The checksum is calculated by adding each element in the packet except the final byte, which is the checksum, and then taking a logical OR of the calculated checksum with 0xFF. If the checksum passes, any critical portions of the packet are parsed in the ISR, an alert is made to the idle task to parse other portions of the packet, the DRDY/UART RX pin is configured back to a GPIO pin when in two-channel mode, and transmission of other commands to the MSP430i2041 devices is enabled again.

When a request for metrology parameters is sent to an MSP430i2041 device and the received packet does not pass the checksum check, the MSP432 MCU sends a duplicate request for the packet. If the packet received does not pass the checksum check for a second consecutive time, no further requests are sent for metrology parameters until the MSP430i2041 alerts the MSP432P4111 of new metrology parameters being ready through its DRDY GPIO pin.

www.ti.com.cn

#### 2.3.2.5 MSP430i2041-to-MSP432P4111 Communication

The MSP432P4111 can send five primary commands to the MSP430i2041 devices. These commands obtain metrology readings for a phase, perform metrology calibration, and synchronize the different MSP430i2041 devices for phase sequence detection. When the MSP430i2041 receives a command from the MSP432 device and is in two-channel mode, the MSP430i2041 configures its shared DRDY/UART TX pin from GPIO mode to UART mode. Based on the received command from the MSP432 MCU, the MSP430i2041 device performs any required actions and, if necessary, sends a response packet back to the MSP432P4111.

For specifically receiving a phase's metrology parameters from a particular MSP430i2041 device, the HOST\_CMD\_GET\_READINGS\_n command is sent by the MSP432 MCU, where the n value corresponds to the phase and has a value of either 1 (for phase A), 2 (for phase B) or 3 (for phase C). The n value is used by the MSP432 device to request the parameters for a specific phase by having the different HOST\_CMD\_GET\_READINGS\_n commands have different command byte values. For example, if the

MSP432 device wants the metrology parameters for Phase A, the MSP432 device sends the HOST\_CMD\_GET\_READINGS\_1 command to all the MSP430i2041 devices. The device that has a phase ID (as configured by the voltages present on the two phase-identification GPIO pins) that corresponds to Phase A then responds with its metrology parameters while the other phases ignore the request.