## TI Designs: TIDA-01461 EtherCAT P<sup>®</sup>— 单根电缆供电和 EtherCAT<sup>®</sup>参考设计

# TEXAS INSTRUMENTS

#### 说明

此参考设计展示了电源耦合在 EtherCAT P®供电设备电路中的物理实现方式。此外,它也可用于 EtherCAT P 电缆外的耦合电源。本设计符合 EtherCAT P 官方实施指南的所有要求。其中包括反极性保护、 浪涌电流限制和连续电流限制等特性,这些特性均以德州仪器 (TI) 半导体为基础。

EtherCAT P 将 EtherCAT®通信和电源传输合并在一根 电缆上。四芯电缆可提供两组 24V 和高达 3A 的隔离电 源。同时该电缆还将来自 EtherCAT 器件的数据传输到 其他器件。这种方式节省了 EtherCAT 网络器件在工厂 进行安装和布线的成本。

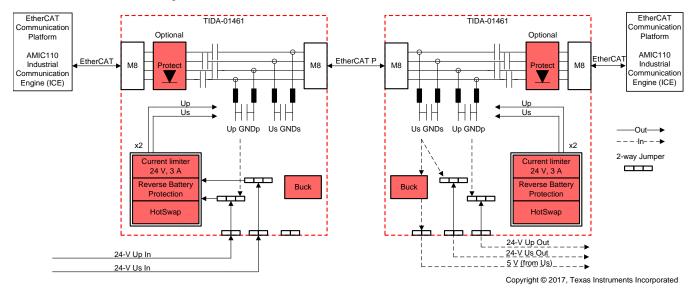

为了实现 EtherCAT 通信,本参考设计可通过一根以太 网电缆连接至支持 EtherCAT 的通信平台,如 AMIC110 工业通信引擎 (ICE)。要演示电源传输功能,可以使用 一根 EtherCAT P 电缆连接两个设计电路板。将 EtherCAT 主器件连接到第一个参考设计,EtherCAT 从 属器件连接到第二个参考设计,构成一个完整的 EtherCAT P 演示系统。

#### 资源

| TIDA-01461  | 设计文件夹 |

|-------------|-------|

| LM5050-1    | 产品文件夹 |

| CSD18540Q5B | 产品文件夹 |

| LM5069      | 产品文件夹 |

| TPD2E2U06   | 产品文件夹 |

| LMZ35003    | 产品文件夹 |

| TVS3300     | 产品文件夹 |

| AMIC110 ICE | 工具文件夹 |

|             |       |

咨询我们的 E2E™ 专家

## 特性

- 通过单根电缆进行 EtherCAT®通信和供电

- 设计符合 EtherCAT P®实施指南

- 反极性保护

- 浪涌电流限制和连续电流限制

- 可调节过压和欠压锁定

- 可通过以太网电缆连接至任何 EtherCAT 通信平台

- 额外 5V/12V 输出方便使用德州仪器 (TI) AMIC110 ICE 进行评估

#### 应用

- 远程 IO

- 通信模块

- 远程传感器和传动器

- 电机驱动器

#### System Description

ゐ

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

## 1 System Description

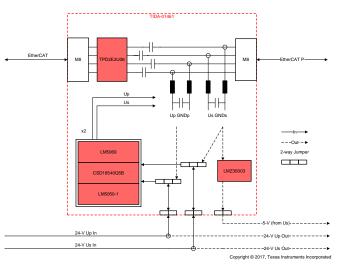

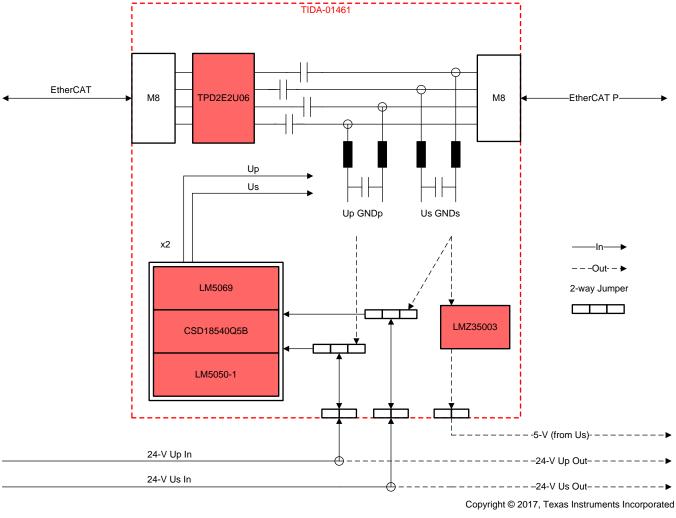

This reference design implements the power couple in circuitry of an EtherCAT P® power sourcing device (PSD), meaning that the actual EtherCAT® communication controller, PHY, and Ethernet transformer are not part of the design. To connect an EtherCAT communication platform, the board has an Ethernet connector assembled. To connect two design boards, an EtherCAT P connector is assembled.

The reference design is designed to meet the requirements specified in the *EtherCAT and EtherCAT P Slave Implementation Guide* from the EtherCAT technology group.

EtherCAT P combines EtherCAT communication and power transfer on one cable. Four wires provide two isolated power supplies, named Us and Up, each providing 24 V and up to 3 A. The isolation rating between the two power rails must be at least 500 V. The isolation rating of the two power rails against field earth or protected earth is 500 V as well.

The same four wires used for power transfer are used for EtherCAT communication. To couple power in to the data lines, this design uses one second-order LC filter per 24-V supply that act as a low-pass filters. To block the 24 V from the Ethernet transformer, one additional capacitor per data line is put in series between the Ethernet transformer and the power couple in circuitry. This circuitry couples power in as well as couples power out.

Us powers the system of an EtherCAT P device (for example, its EtherCAT communication controller, PHYs, microcontrollers, supervisors, and so on, as well as all internal and external sensors). Up powers all internal and external actors like motors or relays. This separation is useful for systems that need two independent power supplies. Furthermore, it gives for example the ability to shut down the motor of a system while still being able to monitor sensor outputs and transmit data to an EtherCAT master.

An EtherCAT P PSD must fulfill several requirements for Us and Up before those power rails are coupled in to the data lines. 表 1 lists these requirements and they can also be read in the official EtherCAT P implementation guide ". This implementation guide also gives detailed information about the EtherCAT P technology itself.

This reference design implements the protection features of a PSD, such as reverse polarity protection, inrush current limit, current limit, undervoltage lockout (UVLO), and overvoltage lockout (OVLO) with semiconductor components. In this design guide and the schematic, this part is called "power input protection". This block exists for both Us and Up.

For EtherCAT communication, the reference design can be connected to an EtherCAT capable communication platform like the AMIC110 ICE with an Ethernet cable at connector J4. Two reference design boards can be connected with an EtherCAT P cable at connector J5. Connecting an EtherCAT master to the first reference design and an EtherCAT slave to the second reference design results in a complete EtherCAT P demonstration system.

Note that to couple power in, connectors J2, J3 for Up and J8, J9 for Us must be set according to the mode, couple in - couple out, which is used in this reference design. This mode can be set with two jumpers per connector. To couple power in, connect pins 3–5 and 4–6. To couple power out, the two jumpers must connect pins 3-1 and 4-2 of the connectors. With this, it is possible to use the reference design for both couple in and couple out. The input voltage for Up is connected at J1, and the input voltage for Us is connected at J7. The output voltages are available at the same connectors.

To facilitate the usage of the AMIC110 ICE, an additional 5-V buck module is available on the board. Following the implementation guide, this 5-V supply is derived from the Us power rail. In case a 12-V output is needed, remove jumper J11 to change the feedback voltage of the LMZ35003 buck module, which results in an output voltage of 12 V. The LMZ35003 buck module is not part of the actual EtherCAT P implementation.

#### 1.1 Key System Specifications

Unless specified otherwise, all parameters are valid for both 24-V power rails, Us and Up.

## 表 1. Key System Specifications

| PARAMETER                                          | SPECIFICATIONS                                                   | DETAILS   |

|----------------------------------------------------|------------------------------------------------------------------|-----------|

| Input supply voltage                               | 24 V + 20%, - 15%                                                | 节 2.3.2.1 |

| Maximum continuous current                         | 3 A                                                              | 节 2.3.2.3 |

| Maximum peak current                               | 7 A                                                              | 节 2.3.2.5 |

| Undervoltage lockout (UVLO)                        | 23.0 V to 23.5 V, adjustable to 20.4 V to 20.9 V with jumper J10 | 节 2.3.2.1 |

| Overvoltage lockout (OVLO)                         | 28.0 V to 28.8 V                                                 | 节 2.3.2.1 |

| Isolation voltage rating (Us-Up)                   | 500 V                                                            | 1 节       |

| Isolation voltage rating (Us: PE/FE and Up: PE/FE) | 500 V                                                            | 1 节       |

| V <sub>out</sub> of LMZ35003                       | 5 V, adjustable to 12 V with jumper J11                          | 1 节       |

| I <sub>out</sub> of LMZ35003                       | 2.5 A                                                            | 节 2.2.5   |

## 2 System Overview

### 2.1 Block Diagram

图 1. Block Diagram of TIDA-01461

#### 2.2 Highlighted Products

#### 2.2.1 LM5050-1

The LM5050-1/LM5050-1 High Side OR-ing FET Controller operates in conjunction with an external MOSFET as an ideal diode rectifier when connected in series with a power source. This ORing controller allows MOSFETs to replace diode rectifiers in power distribution networks thus reducing both power loss and voltage drops.

The LM5050-1/LM5050-1 controller provides a MOSFET gate drive with charge pump for an external N-Channel MOSFET and a fast response comparator to turn off the MOSFET when current flows in the reverse direction. The LM5050-1 can connect power supplies ranging from 5 V to 75 V and can withstand transients up to 100 V.

#### 2.2.2 CSD18540Q5B

This 1.8-mΩ, 60-V, NexFET<sup>™</sup> power MOSFET minimizes losses in power conversion applications with a SON 5-mm × 6-mm package.

#### 2.2.3 LM5069

The LM5069 positive hot swap controller provides intelligent control of the power supply connections during insertion and removal of circuit cards from a live system backplane or other hot power sources. The LM5069 provides in-rush current control to limit system voltage droop and transients. The current limit and power dissipation in the external series pass N-Channel MOSFET are programmable, ensuring operation within the safe operating area (SOA). The POWER GOOD output indicates when the output voltage is within 1.25 V of the input voltage. The input UVLO and OVLO levels and hysteresis are programmable as well as the initial insertion delay time and fault detection time. The LM5069-1 latches off after a fault detection, while the LM5069-2 automatically restarts at a fixed duty cycle. The LM5069 controller is available in a 10-pin VSSOP package.

#### 2.2.4 TPD2E2U06

The TPD2E2U06 is a dual-channel, low-capacitance TVS diode ESD protection device. The device offers  $\pm 25$ -kV contact and  $\pm 30$ -kV air-gap ESD protection in accordance with the IEC 61000-4-2 standard. The 1.5-pF line capacitance of the TPD2E2U06 makes the device suitable for a wide range of applications. Typical application interfaces are USB 2.0, LVDS, and I<sup>2</sup>C<sup>TM</sup>.

#### 2.2.5 LMZ35003

The LMZ35003 SIMPLE SWITCHER® power converter is an easy-to-use integrated power solution that combines a 2.5-A DC/DC converter with a shielded inductor and passives into a low-profile, QFN package. This total power solution allows as few as five external components and eliminates the loop compensation and magnetics part selection process.

#### 2.2.6 TVS3300

The TVS3300 is a transient voltage suppressor that provides robust protection for electronic circuits exposed to high transient voltage events. Unlike a traditional TVS diode, the TVS3300 precision clamp triggers at a lower breakdown voltage and regulates to maintain a flat clamping voltage throughout a transient overvoltage event. The lower clamping voltage combined with a low dynamic resistance enables a unique TVS protection solution that can lower the voltage a system is exposed during a surge event by up to 30% in unidirectional configuration and up to 20% in bidirectional configuration when compared to traditional TVS diodes.

#### 2.3 System Design Theory

This reference design is only used to couple power in and couple power out from the EtherCAT data lines. Therefore, two boards must be connected to two EtherCAT devices. In case the EtherCAT slave is supposed to feed power further along a line network, another board can be connected to couple power in again. This application is also tested in  $\ddagger$  3.2.1.2.

Before Us and Up are coupled in to the data lines, both voltages need to pass the power input protection circuitry. This circuitry makes sure that the voltages are applied correctly, are within the allowed voltage levels, and that the maximum continuous current is not exceeded. These features are explained in more detail in the following subsections.

图 2. System Block Diagram With Two AMIC110 ICEs and Two TIDA-01461 Boards

#### 2.3.1 Reverse Polarity Protection

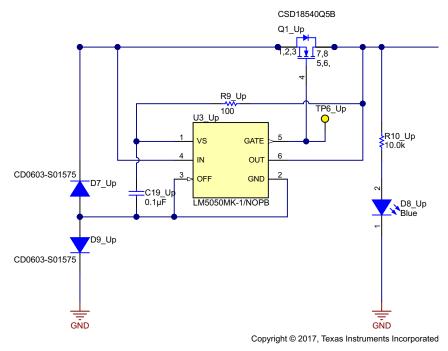

Reverse polarity protection is realized with the LM5050-1 and MOSFET Q1. 🛛 3 shows the relevant part of the schematic. In case the voltage is applied in a reverse way, Q1 stays in a high-impedance mode. In case the voltage is applied correctly, the LM5050-1 works as follows:

The LM5050-1 regulates the gate-to-source voltage of MOSFET Q1. If the MOSFET current decreases to the point that the voltage across the MOSFET falls below the voltage regulation point of 22 mV (typical), the GATE pin voltage decreases until the voltage across Q1 is regulated at 22 mV. If the source-to-drain voltage is greater than 22 mV, the gate-to-source voltage increases and eventually reaches the Zener clamp level of the 12-V GATE to IN pin.

图 3. Schematic of Reverse Polarity Protection With LM5050-1

If the MOSFET current reverses, possibly due to failure of the input supply, such that the voltage across the LM5050-1 IN and OUT pins is more negative than –28 mV (typical), the LM5050-1 quickly discharges the gate of Q1 through a strong GATE to IN pin discharge transistor. If the input supply fails abruptly, as would occur if the supply was shorted directly to ground, a reverse current temporarily flows through the MOSFET until the gate can be fully discharged. This reverse current is sourced from the load capacitance and from the parallel connected supplies. The LM5050-1 responds to a voltage reversal condition typically within 25 ns. The actual time required to turn off the MOSFET depends on the charge held by the gate capacitance of the MOSFET being used. A fast turnoff time minimizes voltage disturbances at the output as well as the current transients from the redundant supplies.

#### System Overview

#### 2.3.2 Power Input Protection Circuit

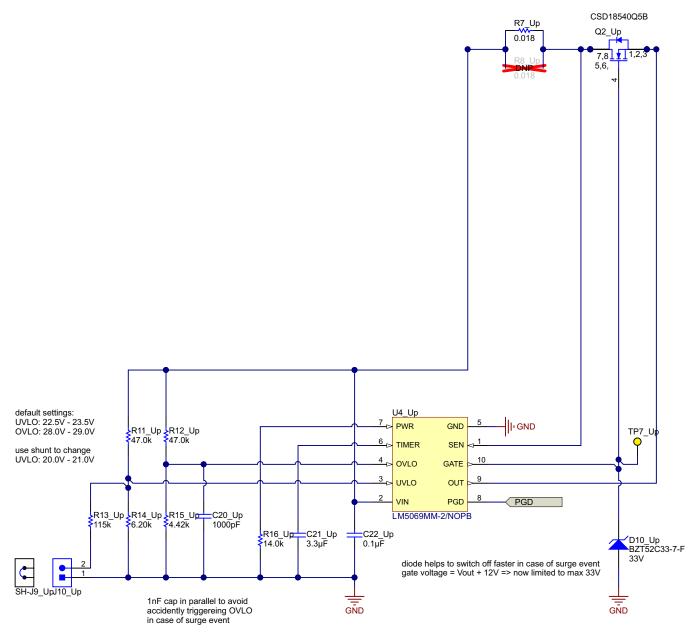

The power input protection circuit is implemented using the LM5069 controller. This circuit includes UVLO, OVLO, current limit, power limit and in-rush current limit. 🛛 4 shows the relevant part of the schematic.

Copyright © 2017, Texas Instruments Incorporated

#### 图 4. Schematic of UVLO, OVLO, Current Limit, Power Limit, and In-Rush Current Limit With LM5069

#### 2.3.2.1 Undervoltage and Overvoltage Lockout

EtherCAT P devices need to operate between voltage levels of 24 V + 20% - 15%. MOSFET Q2 is enables when the input voltage is within the operating range defined by the programmable UVLO and OVLO levels. These levels can be defined using resistors R11 to R15. By default, jumper J10 is set. Following the EtherCAT P implementation guide, the UVLO is set to 23.0 V to 23.5 V, and the OVLO is set to 28.0 V to 28.8 V.

If wanted by the device manufacturer, the UVLO levels can be set lower. Lower voltage levels can for example occur in an EtherCAT P network, if a device is connected over a long cable. Today, EtherCAT P cables exist in 50-m lengths. If a device is now drawing 3A of current, this will results in a non negligible voltage drop across the 50-m cable. To address lower UVLO levels, jumper J10 can be removed so that the UVLO is changed to 20.4 V to 20.9 V. Moreover, this change gives additional flexibility to the user while testing the design.

For details on how to select the resistors for the UVLO and OVLO levels, refer to the UVLO and OVLO sections in *LM5069 Positive High-Voltage Hot Swap and In-Rush Current Controller With Power Limiting*.

### 2.3.2.2 Power-up Sequence of LM5069

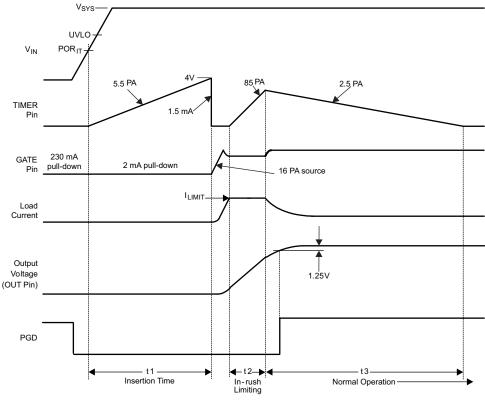

The power-up of the LM5069 circuitry works as follows. As the voltage at  $V_{in}$  initially increases, MOSFET Q2 is held off by an internal 230-mA pulldown current at the GATE pin. The strong pulldown current at the GATE pin prevents an inadvertent turnon as the MOSFET's gate-to-drain (Miller) capacitance is charged. Additionally, the TIMER pin is initially held at ground.

When the  $V_{in}$  voltage reaches a threshold of 7.6 V, the insertion time begins. During the insertion time, the capacitor at the TIMER pin is charged by a 5.5-µA current source, and Q2 is held off by a 2-mA pulldown current at the GATE pin regardless of the  $V_{in}$  voltage. The insertion time delay allows ringing and transients at  $V_{in}$  to settle before Q2 can be enabled. The insertion time ends when the TIMER pin voltage reaches 4 V. Then the capacitor is quickly discharged by an internal 1.5-mA pulldown current.

After the insertion time, the LM5069 control circuitry is enabled when  $V_{in}$  reaches a threshold of 8.4 V. The GATE pin then switches on Q2 when the UVLO threshold is exceeded, the UVLO pin > 2.5 V. If  $V_{in}$  is above the UVLO threshold at the end of the insertion time, Q2 switches on. The GATE pin charge pump sources 16 µA to charge the gate capacitance of Q2. The maximum gate-to-source voltage of Q2 is limited by an internal 12-V Zener diode.

Taken from the LM5069 data sheet, 🛽 5 shows an example for the power-up sequence.

图 5. Power-up Sequence (Current Limit Only) of LM5069

#### 2.3.2.3 **Current Limit**

The current limit threshold is reached when the voltage across the sense resistors R7 and R8 (VIN to SENSE) reaches 55 mV (typical). In the current limiting condition, the GATE voltage is controlled to limit the current in MOSFET Q2. While the current limit circuit is active, the LM5069 internal fault timer becomes active. The fault timer is running while the external capacitor at the TIMER pin is charged by a 85-µA source. If the fault condition subsides before the TIMER pin reaches 4 V, the LM5069 returns to normal operating mode and the capacitor at the TIMER pin is discharged by a 2.5-µA current sink.

For more information on the fault timer, see  $\ddagger$  2.3.2.6.

The continuous current must be limited to 3 A per supply. Using 公式 1, the resistance of the parallel circuit of R7 and R8 is calculated to 18.3 m $\Omega$ .

R s e n s e = V s e n s e I l i m = 55 m V 3 A = 18 . 3 m  $\Omega$

In the default assembly variant of the design, only R7 is used. Therefore, R7 is selected to 18 m $\Omega$ . The footprint of R8 can be used to adjust the parallel resistance.

#### 2.3.2.4 Power Limit

In general, a lower power limit P<sub>lim</sub> is preferred to reduce the stress on MOSFET Q2. However, when the LM5069 device is set to a very low power limit setting, it has to regulate the MOSFET current and hence the voltage across the sense resistor V<sub>sense</sub> to a very low value. V<sub>sense</sub> can be computed as shown in  $\Delta \pi$ 2.

```

Vsense = Plim x Rsense VDS

```

ZHCU391-December 2017

(2)

(1)

## TEXAS INSTRUMENTS

www.ti.com.cn

To avoid significant degradation of the power limiting accuracy, a V<sub>sense</sub> of less than 5 mV is not recommended. Based on this requirement the minimum allowed power limit  $P_{lim,min}$  can be computed as in 公式 3.

Plim, min = V sense, min × Vin, max R sense = 5 m V × 28.8 V 18 m  $\Omega$  = 8 W (3)

Based on this requirement, the minimum allowed  $R_{power}$  to set the current limit can be computed with  $\Delta \mathfrak{A}$ .

Rpower=1.3×105×RsensePlim-1.18mV×VDSRsense

$R_{power}$  is at a minimum when  $V_{DS} = V_{in,max} = 28.8 \text{ V}$ .  $R_{power}$  is then calculated to 14.3 k $\Omega$  and selected to 14 k $\Omega$ .

#### 2.3.2.5 In-Rush Current Limit

In case of an in-rush current event, the voltage drop across R7 and R8 must not be higher than 105 mV. Otherwise, the gate of Q2 is pulled down with a 230-mA current sink. To make sure the current is never exceeding 7 A, the minimum resistance must be at least 15 m $\Omega$  (see  $\Delta \pm 5$ ). This resistance is given by the selected sense resistor of 18 m $\Omega$ .

R s e n s e , m i n = 105 m V 7 A = 15 m  $\Omega$

(5)

(4)

(6)

## 2.3.2.6 Fault Timer

System Overview

The LM5069 internal fault timer starts running when the LM5069 is in power limit or current limit, which can be the case during power-up. Thus the timer must be sized large enough to prevent a time-out during power-up. According to the EtherCAT P implementation guide, an EtherCAT P PSD must be able to load 2200  $\mu$ F. Therefore, C<sub>out</sub> is set to 2200  $\mu$ F.

It is assumed that in case of a hot swap, the board starts in power limit and transitions into current limit. In that case, the estimated start time can be calculated with  $\triangle$  $<math> \triangle$   $\triangle$   $\triangle$ . tstart = Cout2 × Vin, max2 Plim + Plim llim 2 = 2200 µ F 2 × 28.8 V 2 8 W + 8 W 3 A 2 = 115 m s

This start-time assumes a constant, typical current limit and power limit values. The actual startup time is slightly longer, as the power limit is a function of  $V_{DS}$  and decreases as the output voltage increases. To ensure that the timer never times out during power-up, TI recommends setting the minimum fault time  $t_{fault}$  to be greater than the start time  $t_{start}$  by adding an additional margin of 50% of the fault time. This margin accounts for the variation in power limit, timer current, and timer capacitance. As a result, capacitor  $C_{timer}$  is calculated to 3.7 µF and finally selected to 3.3 µF.

$Ctimer = tstart \times itimer, typ V timer, typ \times 1.5 = 115 m s \times 85 \mu A 4 V \times 1.5 = 3.7 \mu F$ (7)

This results in a actual fault time  $t_{fault}$  of 155 ms, which is the typical time that the LM5069 shuts off MOSFET Q2.

tfault = C timer x v timer, typitimer, typ =  $3.3 \mu$ F x  $4 \vee 85 \mu$ A = 155 m s (8)

Now that the power limit and fault timer are chosen, check if the MOSFET stays within its SOA. During a hot-short, the circuit breaker trips and the LM5069 restarts into a power limit until this timer runs out. In the worst case,  $V_{DS}$  equals the maximum input voltage  $V_{in,max}$  of 28.8 V.  $I_{DS}$  equals  $P_{iim} / V_{in,max} = 280$  mA, and the stress event lasts for  $t_{fault} = 155$  ms. The SOA in CSD18540Q5B the data sheet states that the device can handle up to 2.5 A at  $V_{DS} = 30$  V for 100 ms. Therefore, it is assumed that the MOSFET can also handle 230 mA for 155 ms and that it can be used for this reference design.

With  $C_{timer} = 3.3 \ \mu\text{F}$ , the insertion time of the power-up sequence of the design is expected to take 2.4 s (see  $\Delta \pm 9$  and  $\pm 2.3.2.2$ ). 3.3  $\mu$  F x 4 V 5.5  $\mu$  A = 2.4 s

(9)

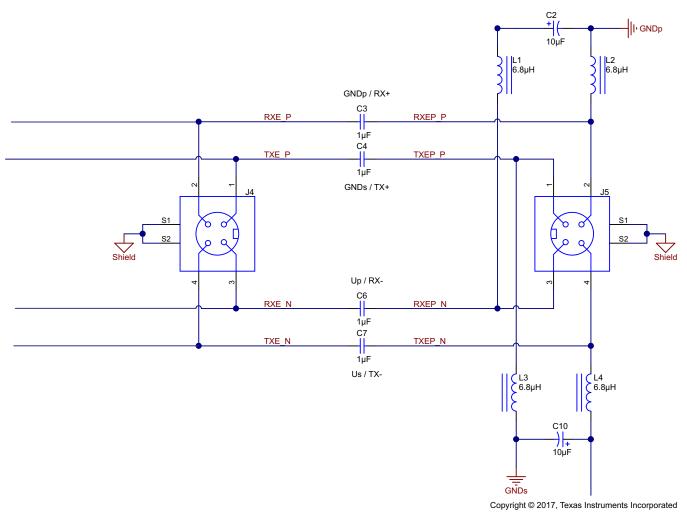

#### 2.3.3 Power Couple In-Couple Out Circuitry

To couple the 24 V in the data lines, one LC filter per 24-V rail is used. 图 6 shows the relevant part of the schematic. The upper LC filter couples in Up, and the lower LC filter couples in Us. Furthermore, the DC voltage blocking caps C3, C4, C6, and C7 of the data lines can be seen. These caps are necessary to protect the Ethernet transformer from the 24-V rails and prevent a short circuit across the windings of the Ethernet transformer.

#### 图 6. Schematic of Power Couple In-Couple Out Circuitry

The LC filter act as a second-order, low-pass filter for the communication lines. Following the EtherCAT P implementation guide, L is selected to 6.8 µH and C is selected to 10 µF. This results in a cutoff frequency of the LC filter of 19.3 kHz (see 公式 10). (10)

fcutoff =  $12 \pi LC$  =  $12 \pi 6 . 8 uH \times 10 uF$  = 19 . 3 kHz

System Overview

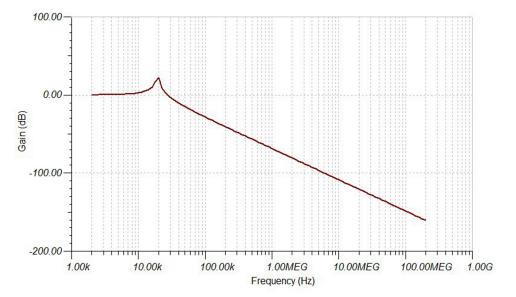

图 7 shows the bode plot of a second-order LC low-pass filter with L = 6.8  $\mu$ H and C = 10  $\mu$ F. 表 2 shows the attenuation at selected frequencies.

图 7. Bode Plot of Second-Order LC Low-Pass Filter (L = 6.8  $\mu$ H and C = 10  $\mu$ F)

| FREQUENCY   | 200 kHz   | 2 MHz     | 20 MHz     | 125 MHz    |

|-------------|-----------|-----------|------------|------------|

| ATTENUATION | –40.54 dB | –80.62 dB | –120.62 dB | –152.45 dB |

#### 表 2. Attenuation of LC Filter for Selected Frequencies

EtherCAT uses 100Base-TX to transfer data. 100Base-TX is operating at a frequency of 125 MHz. Therefore, the LC filter is attenuating the AC signals of the EtherCAT communication by about –152 dB. As a result, the EtherCAT communication signal is only decoupled a little from the data lines. However, the DC power signal can be coupled in to the data lines without big losses. However, it must be ensured that the selected inductor L can handle the maximum current of 3A continuously.

The same circuitry as shown in [8] 6 is used to couple power out. Make sure that jumpers J2, J3 and J7, J8 on the board are set for power couple out. The power protection circuitry is then bypassed and the output voltage is available at connectors J1 and J7. The additional 5-V supply is available at connector J6.

#### 2.3.4 Additional Protection on Power and Data Lines

For additional protection against ESD events on the data lines, ESD diodes are put in between the Ethernet connector and the EtherCAT P connector.

For additional protection on the power lines, a TVS diode rated for IEC 61000-4-2 (ESD minimum level 4), IEC 61000-4-4 (EFT), and IEC 61000-4-5 (surge) is placed after the power input connectors J1 and J7. Furthermore, a bidirectional TVS diode formed out of two TVS3300 devices is placed after the EtherCAT P connector to couple power out.

This additional protection is not hard requirement of the implementation guide. However, it is recommended to take precautions against any ESD, EFT, or surge events that might occur in the system.

## 3 Hardware, Testing Requirements, and Test Results

#### 3.1 Required Hardware

- Power supply: GW INSTEK GPS4303

- Scope: Tektronix MSO4034

- Multimeter: FLUKE 45

- Electronic load: PCE Power Control, Chroma 63102

- Laptop with TwinCAT® software

- Four TIDA-01461 reference designs

- Two AMIC110 ICE boards

### 3.2 Testing and Results

#### 3.2.1 Test Setup

To characterize the design, two test setups are used: one to test the power functionality, and one to test the communication. The two setups are explained in the following two subsections.

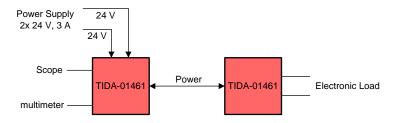

#### 3.2.1.1 Power Test Setup

To test the power transfer between two boards over an EtherCAT P cable:

- 1. Connect the power supply with two 24-V outputs to the first design board. Each output must be capable of providing a current of 3 A.

- 2. Use an EtherCAT P cable to connect the first design board to the second.

- 3. Connect the outputs of the second design board an electronic load that can draw up to 3 A per channel.

- 4. Use a scope to measure the overcurrent protection and to observe the start-up sequence.

- 图 8 shows a block diagram of the power test setup.

Copyright © 2017, Texas Instruments Incorporated

## 图 8. Power Test Setup

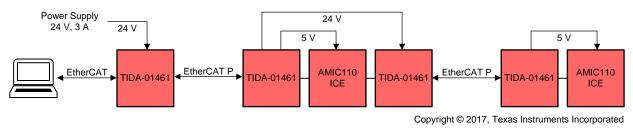

#### 3.2.1.2 Communication Test Setup

To test the communication between an EtherCAT master and an EtherCAT slave in a daisy chain:

- 1. Connect the power supply to the first design board.

- 2. Use a battery-powered laptop that is running TwinCAT as an EtherCAT master.

- 3. Connect the laptop to the first design board using an Ethernet cable.

- 4. Connect the first design board to a second design board with an EtherCAT P cable.

- 5. Use the 5-V output of the second design board to power the first AMIC110 ICE board.

- 6. Connect this AMIC110 ICE board to the second and third design board with an Ethernet cable.

- 7. Connect the third and fourth design board with another EtherCAT P cable.

- 8. Connect the fourth design board to the second AMIC110 ICE board with an Ethernet cable.

- 9. Use the 5-V output of the fourth design board to power the second AMIC110 ICE board.

8 9 shows a block diagram of the communication test setup.

图 9. Communication Test Setup

#### 3.2.2 Test Results

#### 3.2.2.1 **Reverse Polarity Protection**

If any of the two 24-V rails is applied in a reverse way, Q1 does not switch on. This information is also indicated by a red LED at each input of the 24-V rails.

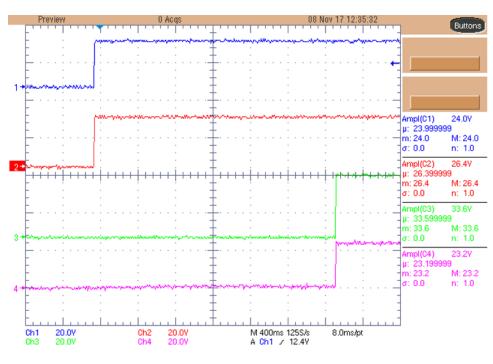

#### 3.2.2.2 **Power-up Sequence**

The power test setup described in  $\ddagger$  3.2.1.1 is used to test this sequence.

10 shows a screen shot of the power-up sequence of one 24-V supply. As both 24-V supplies are built up in an identical way, this behavior is valid for both supplies.

Channel 1 is the voltage level of V<sub>in</sub>. Channel 2 is the voltage level of GQ1, which is the signal at the gate of Q1. Channel 3 is the voltage level of GQ2, which is the signal at the gate of Q2. Channel 4 is the voltage level of Vout.

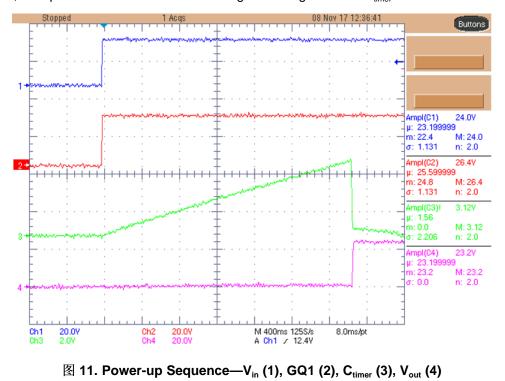

图 10. Power-up Sequence—V<sub>in</sub> (1), GQ1 (2), GQ2 (3), V<sub>out</sub> (4)

Q1 is enabled directly after the voltage is applied. Then the power-up sequence of the LM5069 device starts. As expected in  $\ddagger$  2.3.2.6, the power-up takes around 2.5 s. 🕅 11 shows the same power-up sequence, except that channel 3 is now showing the voltage level at C<sub>timer</sub>.

#### 3.2.2.3 Current Limit

The power test setup described in  $\ddagger$  3.2.1.1 is used to test the current limit.

The multimeter measures the voltage drop across the resistor  $R_{sense}$  while the electronic load is slowly increased. At a current of 2.86 A, the LM5069 turns off MOSFET Q2 and current is blocked. This results in a voltage drop of 2.86 A × 0.018 m $\Omega$  = 51.5 mV. This value complies with the voltage drop tolerances of 48.5 mV to 61.5 mV, as specified in the LM5069 data sheet.

#### 3.2.2.4 Short-Circuit Behavior

The power test setup described in  $\ddagger$  3.2.1.1 is used to test the short-circuit behavior. However, this time the electronic load is disconnected and a short-circuit is done at the output of the second design board.

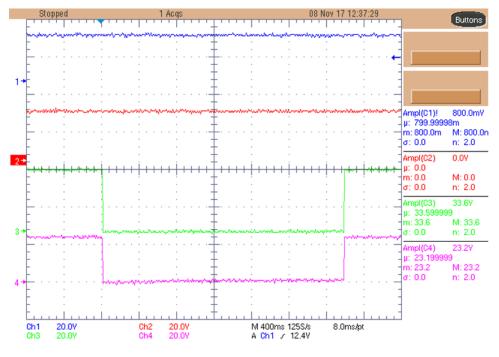

12 shows a screen shot of the short-circuit behavior of one 24-V supply. As both 24-V supplies are built up in an identical way, this behavior is valid for both supplies.

Channel 1 is the voltage level of V<sub>in</sub>. Channel 2 is the voltage level of GQ1, which is the signal at the gate of Q1. Channel 3 is the voltage level of GQ2, which is the signal at the gate of Q2. Channel 4 is the voltage level of  $V_{out}$ .

图 12. Short-Circuit Behavior—V<sub>in</sub> (1), GQ1 (2), GQ2 (3), V<sub>out</sub> (4)

Q2 is disabled directly when the short circuit is happening. Then the power-up sequence of the LM5069 device starts. Like in the normal power-up sequence, this takes again around 2.5 s.

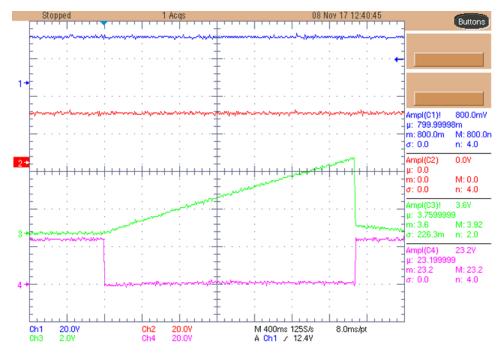

$\mathbb{E}$  13 shows the same power-up sequence, except that channel 3 is now showing the voltage level at C<sub>timer</sub>.

图 13. Short-Circuit Behavior—V<sub>in</sub> (1), GQ1 (2), C<sub>timer</sub> (3), V<sub>out</sub> (4)

#### 3.2.2.5 Undervoltage and Overvoltage Lockout

The power test setup described in  $\ddagger$  3.2.1.1 is used to test the UVLO and OVLO. The multimeter measures the voltage after Q1.

First, the input voltage is set to 24 V and then decreased slowly. At an input voltage of 22.5 V, the LM5069 turns off MOSFET Q2 and blocks the current from flowing. The input voltage must be increased to 23.5 V before MOSFET Q2 is turned on again.

Now, the input voltage is set to 24 V again and increased slowly. At an input voltage of 28.8 V, the LM5069 turns off MOSFET Q2 and blocks the current. The input voltage must be decreased to 28.0 V before MOSFET Q2 is turned on again.

#### 3.2.2.6 Communication

The communication test setup described in  $\ddagger$  3.2.1.2 is used to test the communication. The laptop acts as an EtherCAT master and is running TwinCAT. In TwinCAT, the two connected AMIC110 ICE boards are detected. Then, the setup runs for several minutes and the number of transmit and receive errors are counted. 🚯 14 shows a screen shot of the TwinCAT software after the setup runs for several minutes. Zero frames were lost and zero Tx/Rx errors occurred.

| Actual Sta | ate:    | OP              |              | Counter                     | Cyclic       |     | Queu       | bed     |

|------------|---------|-----------------|--------------|-----------------------------|--------------|-----|------------|---------|

| Init       | Pre-Op  | Safe-Op         | Ор           | Send Frames<br>Frames / sec | 74657<br>497 |     | 3442<br>19 |         |

| Clea       | ar CRC  | Clear F         | rames        | Lost Frames                 | 0            |     | 0          |         |

|            |         |                 |              | Tx/Rx Errors                | 0            | /   | 0          |         |

|            |         |                 |              | TXRXEII0IS                  |              | /   | •          |         |

| lumber     | Box Nam | ne              | Addr         | Туре                        |              | Out |            | E-Bus ( |

| Number     |         | ne<br>(ESC-001) | Addr<br>1001 |                             |              |     |            | E-Bus ( |

图 14. TwinCAT—Lost Frames and Tx/Rx Errors After Several Minutes Operation

#### 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01461.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01461 .

#### 4.3 PCB Layout Recommendations

This reference design is not layout optimized because in a final EtherCAT PSD, all communication and power circuitry are implemented on one board. However, this reference design only implements the power couple in-couple out circuitry. Therefore, for PCB layout recommendations, refer to the official *EtherCAT* and *EtherCAT P Slave Implementation Guide*.

Nevertheless, special care has been taken so that the line impedances and lengths of the EtherCAT lines from connector J4 to connector J5 match.

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01461.

#### 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01461.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01461.

#### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01461.

## 5 Software Files

To download the software files, see the design files at TIDA-01461.

#### 6 Related Documentation

1. EtherCAT Technology Group, EtherCAT and EtherCAT P Slave Implementation Guide

#### 6.1 商标

E2E, NexFET are trademarks of Texas Instruments. SIMPLE SWITCHER is a registered trademark of Texas Instruments. EtherCAT P, EtherCAT, 通过单根电缆进行 EtherCAT, TwinCAT are registered trademarks of Beckhoff Automation GmbH. I<sup>2</sup>C is a trademark of NXP Semiconductors. All other trademarks are the property of their respective owners.

About the Author

#### www.ti.com.cn

#### 7 About the Author

**TOBIAS PUETZ** is a systems engineer in the Texas Instruments Factory Automation and Control team, where he is focusing on PLC and robotics. Tobias brings to this role his expertise in various sensing technologies as well as power design. Tobias earned his master's degree in electrical engineering and information technology at the Karlsruhe Institute of Technology (KIT), Germany in 2014.

#### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在 帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用 的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知 识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包 含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能而设计。除特定 TI 资源的公开文档中明确列出的测试 外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他 法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任 何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信 息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许 可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、 无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

> 邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司