Jayden Li

Kian Lin

FAE/East China

## 摘要

锂电池包根据保护 FETs 的位置不同，可分为高边保护和低边保护方案。高边保护方案相比于低边保护方案，因为在保护触发后 AFE 和 MCU 仍然共地，仍然能够和 MCU 端实现通信，所以越来越多的电池包选择高边保护方案。短路保护作为电池包最严格的测试项之一，在研发测试过程中经常会出现放电 MOS-DFET 损坏的现象，而开发者在实际开发时发现高边驱动的电池包往往比低边驱动更加挑战。本文将介绍为什么高边保护方案的短路保护驱动比低边保护方案更加的挑战，并希望本文能够对读者高边驱动的设计有所启发。

## 内容

|                         |   |

|-------------------------|---|

| 1 低边/高边保护方案简介.....      | 2 |

| 2 短路保护导致 DFET 过压损坏..... | 3 |

| 2.1 低边保护方案.....         | 3 |

| 2.2 高边保护方案.....         | 3 |

| 2.3 小结.....             | 4 |

| 3 短路保护导致 DFET 过热损坏..... | 4 |

| 3.1 低边保护方案.....         | 5 |

| 3.2 高边保护方案.....         | 6 |

| 3.3 小结.....             | 6 |

| 4 总结.....               | 7 |

| 5 参考文献.....             | 7 |

## 1 低边/高边保护方案简介

根据保护 FETs 的位置，我们可以将电池包分为低边保护方案 图 1-1 和高边保护方案 图 1-2。

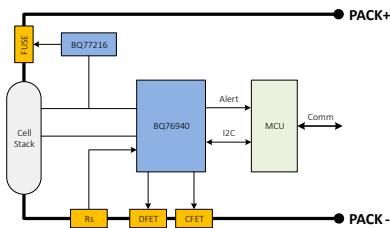

图 1-1 所示为低边保护架构的示意图，充电管 CFET 以及放电管 DFET 都放置于 B- 和 PACK- 之间，位于电池包的低边侧。TI 的 BQ769x0 , BQ7690x 系列 AFE 均集成了低边驱动。

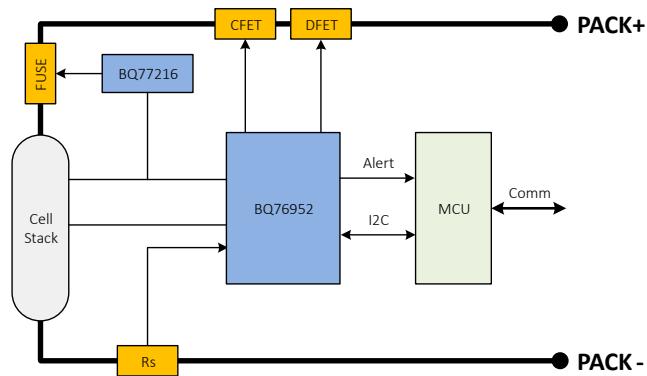

图 1-2 所示为高边保护架构的示意图，充电管 CFET 以及放电管 DFET 则都放置于 B+ 和 PACK+ 之间，位于电池包的高边侧。TI 的 BQ769x2 系列 AFE 集成了高边驱动。

图 1-1. 低边保护方案

图 1-2. 高边保护方案

对于低边保护方案，当 CFET , DFET 关断的时候，电池包的地和系统端的地不再共地，所以一旦有保护被触发关闭充放电 FETs，电池端和系统端不再能够实现直接通信。若想继续实现通信，则需要采用隔离通信，这不仅会增加成本，同时也会增加功耗，尤其是欠压保护时，过大的通讯功耗对于原本就欠压的电池包更是雪上加霜。因此低边方案主要应用于对成本更为敏感的没有复杂通信的产品中。

相比较低边保护，高边保护方案即使在保护被触发后，电池包和系统端仍然是共地的，因此仍然可以实现相互之间的通信，而无需增加隔离通信，且触发保护后断开电池正端，系统也更加安全。

## 2 短路保护导致 DFET 过压损坏

因为真实电路并不是理想电路，功率回路中总是存在一些寄生电感。而短路保护的时候，短路电流会非常大，在保护瞬间，DFET 关断，电流急剧变化则会产生很高的感应电压。该感应电压施加到 DFET 上就会导致 DFET 过压损坏。

### 2.1 低边保护方案

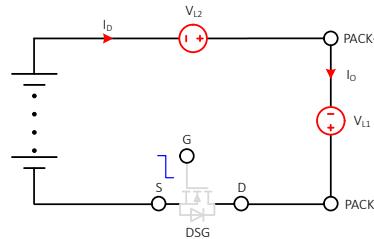

为了简化分析，本文分别将负载侧和电池侧的寄生电感等效为 L1 和 L2。

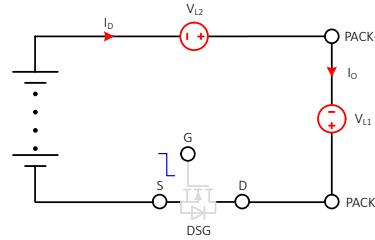

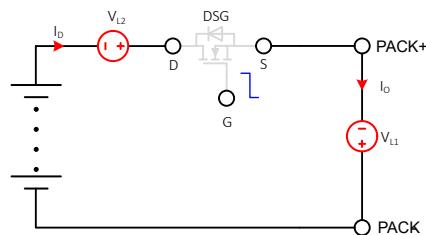

图 2-1 所示为低边保护方案中，DFET 短路保护关断后的等效电路。

图 2-1. 低边保护方案-放电管 DFET 关断等效电路

在短路保护之后，DSG 关断，流过 L1 的电流没有续流回路，快速从  $I_o$  减小至零，则在 L1 上就会感应到很大的感应电压：

$$V_{L1} = L1 \frac{dI_o}{dt} \quad (1)$$

而流过 L2 的电流同样因为没有续流回路，所以流过 L2 的电流也会快速从  $I_o$  减小至零，则在 L2 上也会感应到很大的感应电压：

$$V_{L2} = L2 \frac{dI_o}{dt} \quad (2)$$

因此 DS 两端电压可以用如下表达式表达：

$$V_{DS\_LS} = V_{L1} + V_{L2} + V_{bat} = L1 \frac{dI_o}{dt} + L2 \frac{dI_o}{dt} + V_{bat} \quad (3)$$

### 2.2 高边保护方案

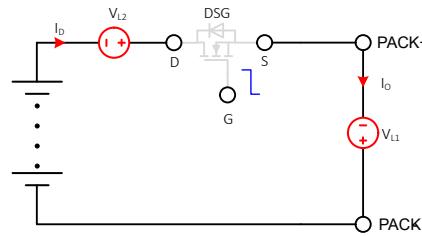

图 2-2 所示为高边保护方案中，DFET 短路保护关断后的等效电路。

图 2-2. 高边保护方案-放电管 DFET 关断等效电路

和低边保护方案相似，DS 两端电压可以用如下表达式表达：

$$V_{DS\_HS} = V_{L1} + V_{L2} + V_{bat} = L1 \frac{dI_o}{dt} + L2 \frac{dI_o}{dt} + V_{bat} \quad (4)$$

## 2.3 小结

从上述分析可知，高边保护方案和低边保护方案在短路保护时 DFET 所承受的电压应力是一致的。

## 3 短路保护导致 DFET 过热损坏

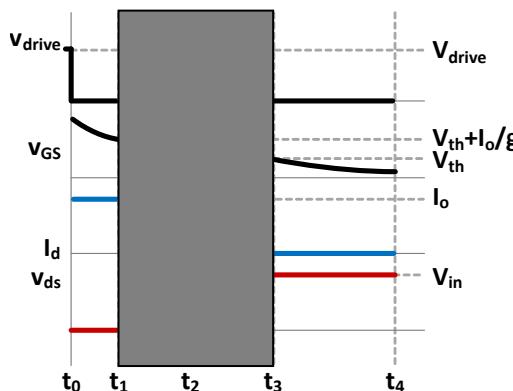

忽略寄生电感的影响，DFET 在关断时的主要波形如图 3-1 所示，主要可以分为四个模态。而其中因为模态一 ( $t_0-t_1$ ) 的 DS 电压为零，模态四 ( $t_3-t_4$ ) 的电流为零，因此这两个模态都不会产生功耗，所以真正产生功耗的只有模态二和模态三。下面对模态二和模态三分别进行分析。

图 3-1. 放电 MOS 关断主要波形

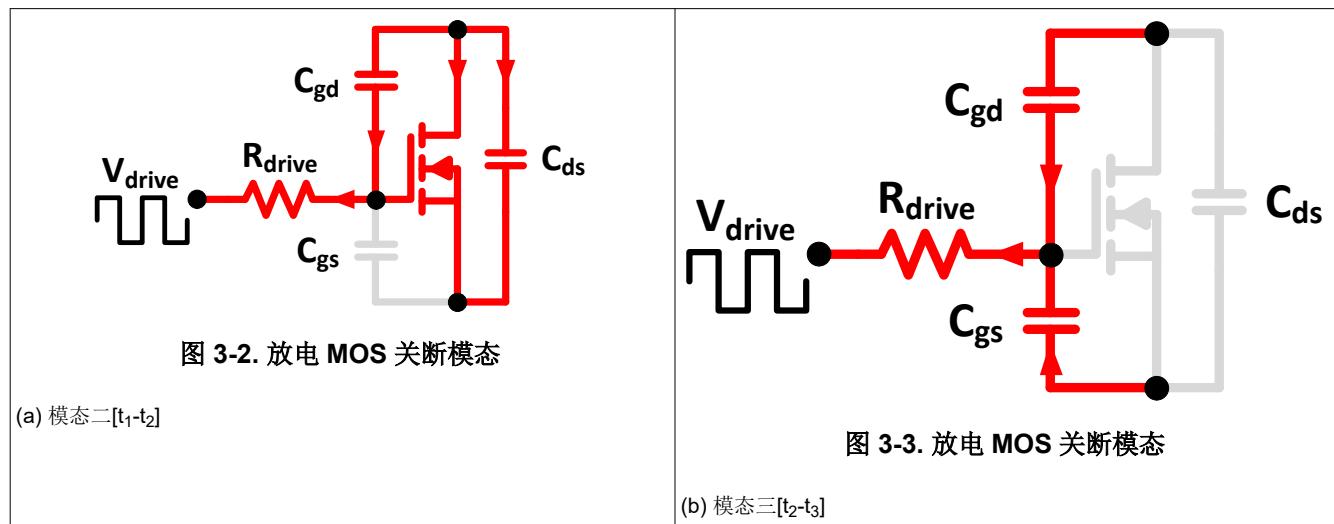

[模态二:  $t_1-t_2$ ]: 该阶段为 MOS 管的米勒平台，如图 3-2 所示，结电容  $C_{gd}$  和  $C_{ds}$  通过驱动电阻  $R_{drive}$  充电， $V_{DS}$  电压升高， $t_2$  时刻， $V_{DS}$  达到  $V_{bat}+V_{FD1}$ ，模态二结束。该模态中，流过放电 MOS 管的电流保持为  $I_o$ ，结电容的充电速度取决于  $R_{drive}$  的大小， $R_{drive}$  越小，充电速度越快，模态二的时间越短。

[模态三:  $t_2-t_3$ ]: 如图 3-3 所示， $t_2$  时刻，放电 MOS 进入模态三，流过放电 MOS 管的电流从  $I_o$  开始减小， $C_{gs}$  经过  $R_{drive}$  放电， $C_{gd}$  经过  $R_{drive}$  充电， $V_{GS}$  开始减小。 $t_3$  时刻，流过放电 MOS 的电流减小至零， $V_{GS}$  减小至开启电压  $V_{th}$ ，模态三结束。该模态中，结电容的充放电速度同样取决于  $R_{drive}$  的大小， $R_{drive}$  越小，充放电速度越快，模态三的时间越短。

根据上述分析，放电 MOS 在关断瞬间产生的损耗可以用如下表达式表达：

$$P_{loss} = \frac{1}{2} \times V_{in} \times I_o \times (t_3 - t_1) \quad (5)$$

从上述表达式可知， $t_3-t_1$  的时间越长，放电 MOS 在保护瞬间所产生的损耗就越大，发热就越严重。

### 3.1 低边保护方案

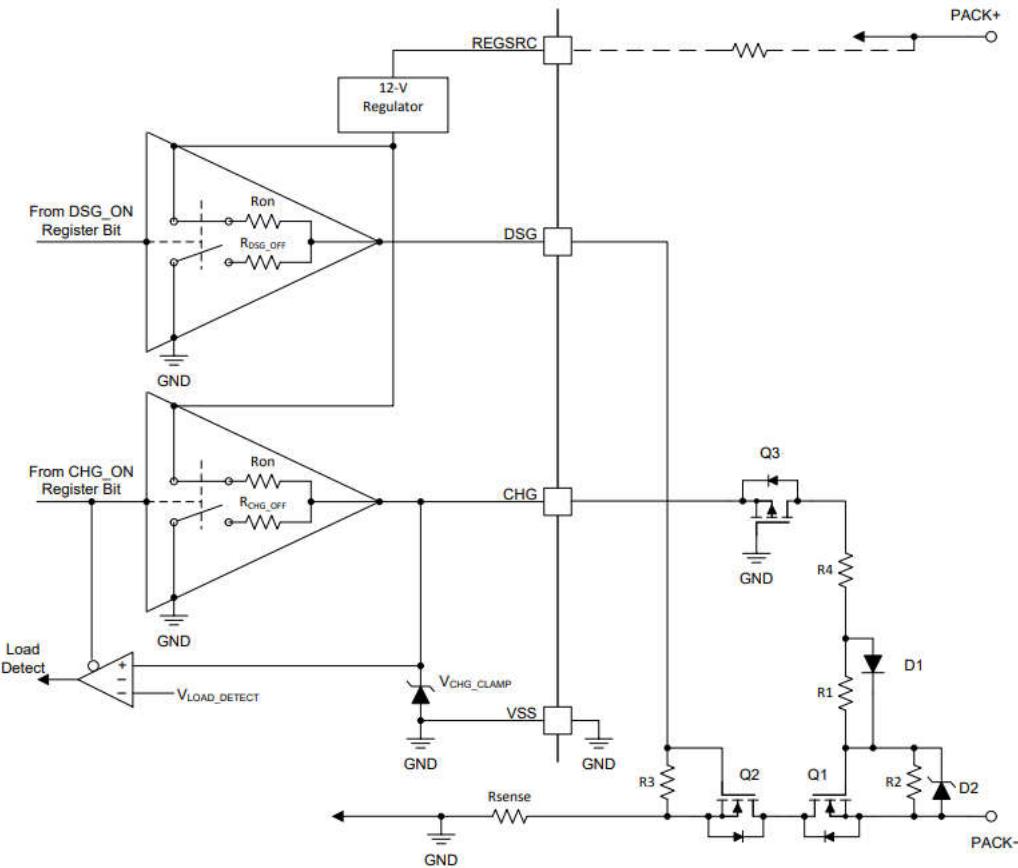

对于低边保护方案，以 BQ76940 为例，DFET 在关断瞬间，G 极电压  $V_G$  被内置二极管钳位在 -0.3V 左右，S 极电压  $V_S$  被钳位在 BAT- 也等于 0V。

图 3-4. 低边保护方案-放电管 DFET 关断等效电路

图 3-5 所示为 BQ76940 DSG Pin 等效电路，当 AFE 关断 DFET 时，DSG Pin 通过 AFE 内部的  $R_{DSG\_OFF}$  拉地，因此关断的时间只取决于 DFET 的结电容以及放电电阻  $R_{DSG\_OFF}=2.5\text{KOhm}$ 。

当 DFET 的 G 极电压下降到满足以下条件即可彻底关断 DFET。

$$V_G < V_{GSth_{DFET}} \quad (6)$$

图 3-5. BQ76940 DSG 引脚等效图

当然用户也可以通过 DSG Pin 与 DFET 的 G 极放置一个额外的电阻进一步调节关断速度。

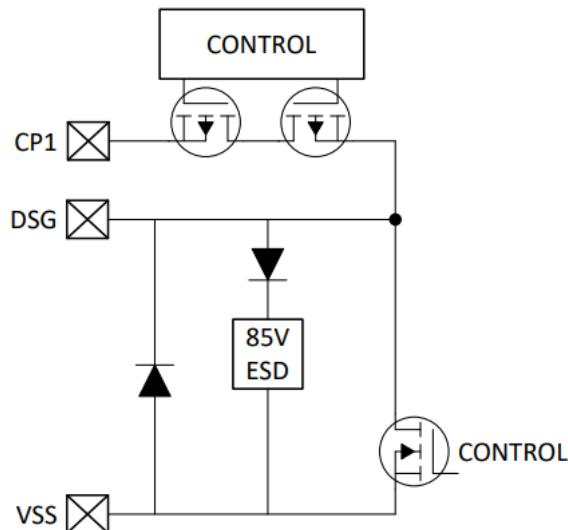

### 3.2 高边保护方案

对于高边保护方案，以 BQ76952 为例，DFET 在关断时，G 极对地放电，电压  $V_G$  会被内置二极管钳位在-0.3V 左右，但 S 极电压  $V_S$  却因为寄生电感的大小而被拉低至  $-V_{L1}$ ，因此即使 G 极已经对地放电至-0.3V，GS 电压  $V_{GS}$  仍然等于  $V_{L1}-0.3V$ ，而只要满足以下条件：

$$V_{L1} - 0.3V > V_{GSThDEET} \quad (7)$$

DFET 就无法完全关断。

而 GS 电压因为无法通过 DSG Pin 来泄放结电容上的电压，而只能通过 DFET 的 GS 两端所并联的电阻来泄放，但是该电阻主要是用来避免 GS 端的静电聚集，防止误开通，所以该电阻通常会取比较大，因为较小的 GS 电阻会增加 BQ76952 充电泵的直流负载，而 BQ76952 不建议较大直流负载，所以该 GS 电阻通常为兆欧级电阻，如参考文献 3 和参考文献 4 中都选用的 10 兆欧，所以结电容的充放电电流都是 uA 级别，所以整个关断时间就会很慢，从而在关断过程中产生大量的热损耗，导致 DFET 过热损坏。

图 3-6. 高边保护方案-放电管 DFET 关断等效电路

图 3-7. BQ76952 DSG 引脚等效图

### 3.3 小结

总而言之，相比低边保护方案，高边保护方案由于 DFET 的 S 极与 P+ 相连，不被钳位，因此在短路保护时会被负载侧寄生电感的感应电压拉低至负压从而导致 DFET 关断缓慢，从而更容易过热损坏。

## 4 总结

短路保护作为最严格的测试项之一，无论是低边保护方案还是高边保护方案都面临 DFET 损坏的风险。该风险主要源自过压和过热两个原因：

过压损坏：低边保护方案和高边保护方案在短路保护时 DFET 所承受的电压应力一样。

过热损坏：高边保护方案在短路保护时 DFET 关断更慢，发热更严重，更容易过热损坏。

关于短路保护时的驱动设计，可以查看参考文献 2 和参考文献 5。

## 5 参考文献

1. 具有精确电池测量和高侧 MOSFET 控制功能的 10 节至 16 节串联电池组参考设计 (TIDA-010208)

2. 高串数锂电池包短路保护电路的设计及考虑因素 (ZHCAAJ0)

3. BQ76952 3-Series to 16-Series High Accuracy Battery Monitor and Protector for Li-Ion, Li-Polymer, and LiFePO<sub>4</sub> Battery Packs datasheet (SLUSE13A)

4. BQ76952 Technical Reference Manual (SLUUBY2A)

5. 基于 BQ76952 的电池包短路保护 DSG FET 损坏原因及优化方法 (ZHCAB67)

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2026 , 德州仪器 (TI) 公司

最后更新日期 : 2025 年 10 月