## Application Note

**MCU+SDK 的 xSPI 定制闪存调试指南**

Vaibhav Kumar, Nikhil Jain

**摘要**

本应用手册提供了有关使用 MCU+SDK 在 TI Sitara™ 处理器上启动定制闪存器件的指导。本文档解决了开发人员在定制电路板（使用的闪存器件不同于 TI 评估模块 (EVM) 上提供的闪存器件）上所面临的挑战。

本文档概述了集成、配置和验证新闪存器件以验证能否在 TI 软件生态系统中可靠运行所需的步骤。目标受众包括工程师和开发人员，他们正在设计定制硬件，并需要通过 SPI/QSPI/OSPI 接口启用闪存通信。

阅读本应用手册有助于缩短启动时间并大幅减少常见集成问题，从而加快定制闪存配置的开发和调试速度。

**内容**

|                                  |    |

|----------------------------------|----|

| <b>1 简介</b>                      | 2  |

| <b>2 术语</b>                      | 2  |

| <b>3 了解引导模式和闪存兼容性</b>            | 2  |

| <b>4 闪存集成和 SysConfig 设置</b>      | 3  |

| 4.1 FLASH 参数                     | 4  |

| 4.2 OSPI 参数                      | 8  |

| <b>5 常见启动问题和调试</b>               | 9  |

| 5.1 引导失败                         | 9  |

| 5.2 已知勘误表                        | 9  |

| 5.3 闪存初始化失败                      | 9  |

| 5.4 闪存读取失败                       | 10 |

| 5.5 闪存编程故障                       | 10 |

| <b>6 请求 OSPI 和 FLASH 支持的检查清单</b> | 11 |

| <b>7 摘要</b>                      | 11 |

| <b>8 参考资料</b>                    | 11 |

**商标**

Sitara™ is a trademark of Texas Instruments.

所有商标均为其各自所有者的财产。

## 1 简介

在嵌入式系统中，外部闪存存储器广泛用于存储引导加载程序和应用程序代码。AM64x、AM62x、AM62P 和 AM62Dx 等 Sitara 处理器支持多个串行接口（如 OSPI 和 QSPI），用于连接外部 NOR/NAND 闪存器件。在使用 MCU+SDK 启动定制电路板期间，用户在连接新闪存器件时通常会面临一些挑战，例如配置 SysConfig 参数、读取器件 ID 或启用 PHY 模式。

本应用手册介绍了如何使用 SysConfig 配置闪存参数，解释常见错误日志以及解决闪存识别和 PHY 启用期间出现的问题。

## 2 术语

QSPI：四线串行外设接口

OSPI：八线串行外设接口

xSPI：扩展串行外设接口

NVCR：非易失性配置寄存器

VCR：易失性配置寄存器

DDR：双倍数据速率

SDR：单倍数据速率

QE：四路使能位

DAC：直接存取控制器

## 3 了解引导模式和闪存兼容性

可以在此处的技术参考手册中找到 ROM 支持的串行 NOR/NAND 闪存的各种引导模式。每种引导模式都描述了 ROM 用于发出读取命令的协议。协议因各种引导模式而异。例如，对于 SPI（协议 1S-1S-1S）引导模式，ROM 发出读取命令 0x03（8 位），后跟 3 字节（24 位）地址且无虚拟周期。

如果根据引导模式的说明，则认为闪存支持引导。闪存支持以下参数：

1. 协议。

2. 读取命令。

3. 读取命令和地址的字节数（3 字节/4 字节）。

4. 读取的虚拟周期数。

对于定制闪存，要获取这些值，请参阅闪存特定数据表。在闪存数据表中，这些值包含在名为 *Command Set*、*Command Table*、*Instruction Set*、*Instruction Table*、*Transaction Set*、*Transaction Table* 的部分下。

## 4 闪存集成和 SysConfig 设置

SysConfig 是一款配置工具，旨在简化硬件和软件配置挑战，从而加速软件开发。

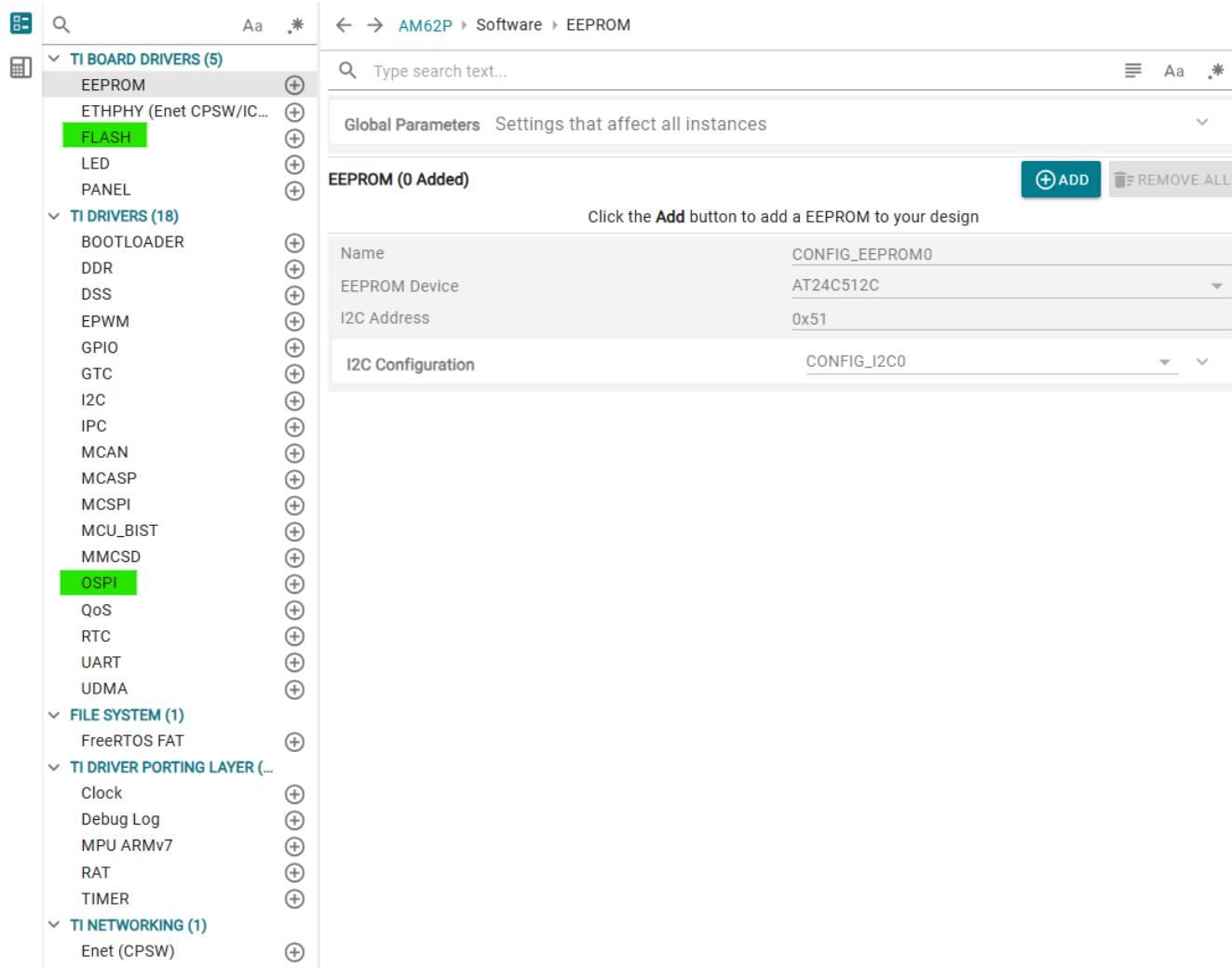

在 MCU+SDK 中，对于定制闪存，需要修改的部分如 图 4-1 中所示。

图 4-1. 显示 FLASH 和 OSPI 部分的 SysConfig GUI

要获取定制闪存配置值，请按照[此处](#)的指南进行操作。本指南目前适用于串行 NOR 闪存。对于串行 NAND 闪存，必须从闪存数据表中获取配置值。

获得这些值后，可以用获得的值填充 FLASH 部分。这些值可以手动填充，也可以以 json 格式上传。使用闪存数表中所述的值运行 OSPI 闪存诊断示例，验证获得的值。以下各节展示了 FLASH 和 OSPI 部分中的各种参数。

## 4.1 FLASH 参数

对于每个参数，单击 ? 可了解相关说明。

有关图 4-2 的说明：

- 闪存器件**：如果闪存不是 TI EVM 上的默认闪存之一，请选择定制闪存。

- 闪存名称**：写入正在使用的闪存的名称，例如 *W25Q512JV*。

- 协议**：从列出的协议中选择闪存也支持的协议之一。这将分别配置要用于命令、地址和数据的行数。它还指定数据速率，即 DDR ( 双倍数据速率 ) 或 SDR ( 单倍数据速率 )。例如，4S-4D-4D 表示 4 行分别用于命令、地址和数据。对于命令，数据在上升沿/下降沿锁存，但对于地址和数据，数据在上升沿和下降沿均锁存。

图 4-2. 基本闪存配置

有关图 4-3 的说明：

- 闪存 JEDEC 制造 ID**：特定制造商的此值相同。

- 闪存 JEDEC 器件 ID**：该值因同一制造商的闪存型号而异。例如，Winbond 闪存对于分别在 1.8V 和 3.6V 电压下运行的闪存，具有不同的器件 ID。还有其他一些参数具有不同的闪存器件，这些参数可在闪存数据表中找到。

- 虚拟时钟 (CMD) 和虚拟时钟 (读取)**：虚拟时钟用于同步闪存读取。也可以从闪存数据表中获取这些值。注意指定为虚拟周期/虚拟时钟的部分。请注意，该字段指定在 OSPI 控制器端设置的值。要在闪存结束时设置虚拟周期/时钟值，需要对闪存配置寄存器进行写入。请参阅**虚拟周期配置**字段。

- 四路使能类型**：一些 QSPI 闪存具有 QE ( 四路使能 ) 位。对于 1S-1S-4S、4S-4S-4S 和 4S-4D-4D 等协议，需要启用该位。

- QPI 序列和 OPI 序列**：要分别启用 4-4-4 模式和 8-8-8 模式，请使用这些字段。

- 有关闪存的块大小和扇区大小，请参阅闪存数据表。可从诊断日志中获取相同的命令，但最好从数据表中进行验证。

- SysConfig** 允许用户设置扇区大小和块大小，如果闪存支持不同的扇区/块大小，用户可以根据应用指定特定的扇区/块大小。

- (3B) 和 (4B) 是指闪存的 3 字节和 4 字节寻址模式。这基本上指定了必须发送多少个地址字节。对于小于 16MB 的闪存，只需 3 个字节寻址即可满足整个闪存区域的需求。

|                                      |          |

|--------------------------------------|----------|

| <b>Basic Flash Configuration</b>     |          |

| Flash Size In Bytes                  | 67108864 |

| Flash Page Size In Bytes             | 256      |

| Flash JEDEC Manufacturer ID          | 0x34     |

| Flash JEDEC Device ID                | 0x5B1A   |

| <b>Erase Configurations</b>          |          |

| Flash Block Size In Bytes            | 262144   |

| Flash Sector Size In Bytes           | 4096     |

| Block Erase CMD (3B)                 | 0xDC     |

| Block Erase CMD (4B)                 | 0xDC     |

| Sector Erase CMD (3B)                | 0x21     |

| Sector Erase CMD (4B)                | 0x21     |

| <b>Protocol Enable Configuration</b> |          |

| Read Command                         | 0xEE     |

| Write/Page Program Command           | 0x12     |

| Mode Clocks (CMD)                    | 0        |

| Mode Clocks (READ)                   | 0        |

| Dummy Clocks (CMD)                   | 4        |

| Dummy Clocks (READ)                  | 21       |

| Quad Enable Type                     | 0        |

| Octal Enable Type                    | 0        |

| QPI Sequence                         | 0x00     |

| OPI Sequence                         | 0x00     |

图 4-3. 基本闪存擦除和协议配置

有关图 4-4 的说明：

- 协议配置**：协议通常指定用于命令、地址和数据的行数。为了使闪存以特定协议运行，该部分需要被填满。

- 虚拟周期配置**：为了使闪存以特定协议运行，闪存配置寄存器需要配置虚拟周期。这是闪存侧设置，OSPI 控制器的设置在 **虚拟时钟 (读取)** 字段下定义。

- STR/DTR 配置**：可以设置此位以使闪存在 SDR/DDR 模式下运行。

|                                  |                                     |

|----------------------------------|-------------------------------------|

| <b>Protocol Configuration</b>    |                                     |

| Config Is Using Addressed Reg    | <input checked="" type="checkbox"/> |

| Address Of Config Reg            | 0x00800006                          |

| CMD To Read Config Reg           | 0x65                                |

| CMD To Write To Config Reg       | 0x71                                |

| <b>Register Data</b>             |                                     |

| <b>Dummy Cycle Configuration</b> |                                     |

| <b>STR/DTR Configuration</b>     |                                     |

图 4-4. 协议、虚拟周期和 STR/DTR 配置

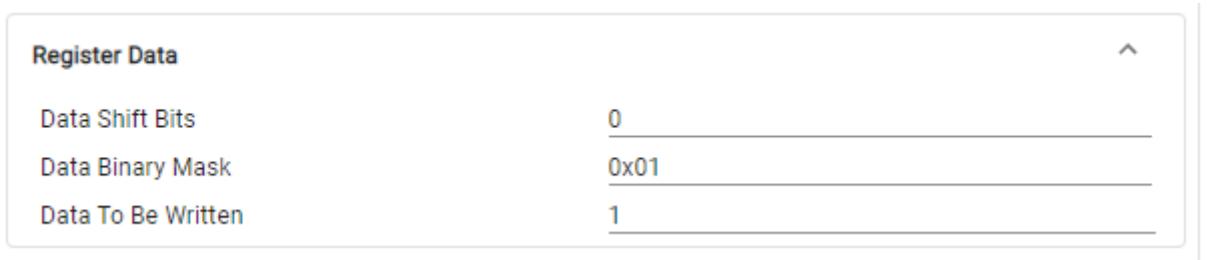

有关图 4-5 的说明：

让我们仔细了解这一点。假设配置寄存器的值为 10111101b。如果位[5:2]需要更新为 1001b，则数据移位位、数据二进制掩码和要写入的数据中的值将分别为 2、0x3C 和 9。使用逻辑  $(value \& \sim(Data\ Binary\ Mask))$  对原始值 10111101b 执行掩码操作。这样会得到值 10000001b。现在，将按  $(value | (Data\ To\ Be\ Written \ll Data\ Shift\ Bits))$  执行移位操作。最终值变为 10100101b，因此会写入配置寄存器。

图 4-5. 寄存器数据字段配置

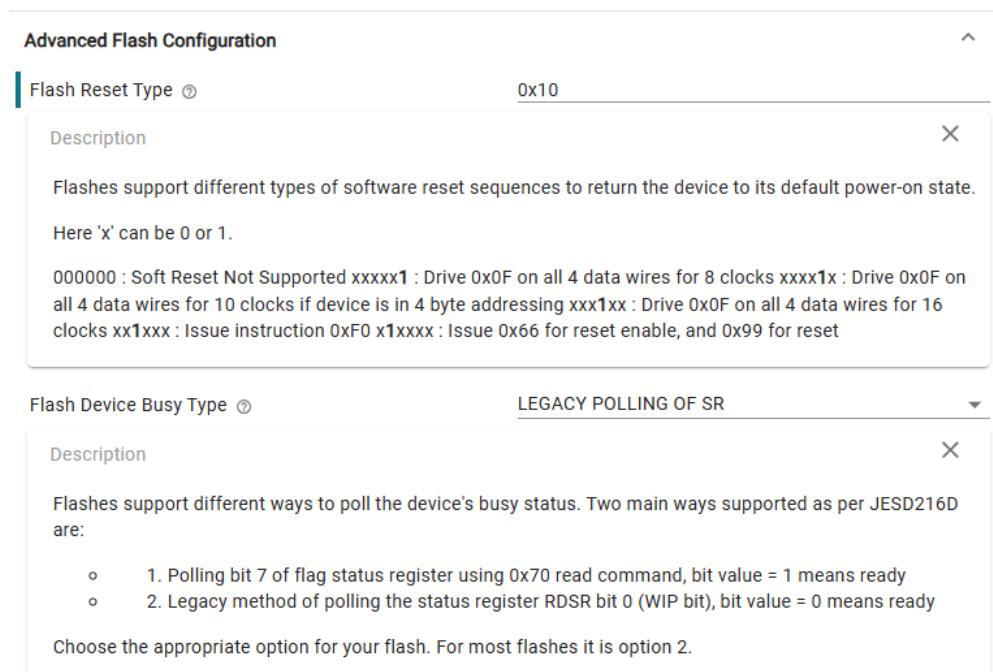

有关图 4-6 的说明：

字段一目了然。可以参考闪存数据表来设置正确的值。

图 4-6. 高级闪存配置

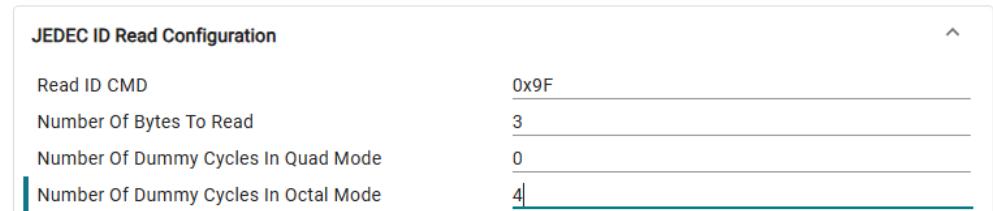

有关图 4-7 的说明：

可以在闪存数据表中找到所有这些值。请参阅“闪存数据表”中的“读取器件 ID/读取制造 ID 事务表”。

图 4-7. JEDEC ID 读取配置

有关图 4-8 的说明：

1. **WIP 位** 和 **WEL 位**：这些位指的是闪存状态寄存器中的“正在写入”和“写入使能锁存”位。

2. **四字节寻址**：如前所述，如果闪存大小大于 16MB，则需要执行此操作，并且闪存支持用于 (4B) 寻址的特定命令。

3. **命令扩展类型**：假设要发送的命令为 0x9F。因此，在以下情况下：

- a. **NONE**：发送 0x9F。

- b. **REPEAT**：发送 0x9F, 0x9F。

- c. **INVERSE**：发送 0x9F, 0x60 ( 0x9F 的反码 )。

4. **Quirks** 函数用于定义自定义 API，该 API 会对闪存的配置寄存器进行其他更改。目前，它定义为 *Flash\_quirkSansionUNHYSADisable*。此函数基本上会在 TI EVM 上禁用 *flash(S28HS512T)* 的混合模式。

|                                                                           |                                               |

|---------------------------------------------------------------------------|-----------------------------------------------|

| Write Enable CMD                                                          | 0x06                                          |

| Read Status Register CMD                                                  | 0x05                                          |

| WIP Bit                                                                   | 0                                             |

| WEL Bit                                                                   | 1                                             |

| WIP Read CMD (xSPI)                                                       | 0x65                                          |

| WIP Status Reg Addr (xSPI)                                                | 0x00800000                                    |

| WIP Bit (xSPI)                                                            | 0                                             |

| Chip Erase Command                                                        | 0xC7                                          |

| Flash Busy Timeout                                                        | 256000000                                     |

| Page Program Timeout                                                      | 512                                           |

| Enable 4 Byte Addressing                                                  | <input checked="" type="checkbox"/>           |

| <b>Four Byte Addressing</b> <span style="float: right;">^</span>          |                                               |

| Supported Addressing Modes                                                | 1                                             |

| 4 Byte Addressing Enable Sequence                                         | 0xA1                                          |

| Command Extension Type                                                    | REPEAT                                        |

| <b>Automatically Configure Flash</b> <span style="float: right;">^</span> |                                               |

| Load Flash Config From JSON                                               | <input type="button" value="LOAD FROM JSON"/> |

| Quirks Function                                                           | <i>Flash_quirkSansionUNHYSADisable</i>        |

图 4-8. 高级闪存配置 (续)

#### 4.1.1 建议的方法

**MCU+ SDK** 提供了默认示例，可在以下路径中找到这些示例：**MCU\_PLUS\_SDK\_INSTALL\_PATH/examples/drivers/ospi**。一个此类示例是 **OSPI Flash IO**。如需有关此示例的更多详情，请单击 [此处](#)。

成功运行此示例可确保所有基本闪存操作 ( 擦除，写入和读取 ) 都正常运行。这还可确认控制器和闪存器件之间的协议配置设置正确，以及 **SysConfig** 中配置的闪存参数按预期运行。

通过 **OSPI Flash IO** 示例验证闪存参数和协议的特定组合后，这些经过验证的设置便可重复用于其他应用，例如 **UART Uniflash**、引导加载程序 ( 如 **SBL OSPI** ) 和类似项目。

总之，**OSPI Flash IO** 示例用作测试和配置闪存参数的可靠参考点，然后可将其应用于多个应用。

## 4.2 OSPI 参数

对于每个参数，单击 ? 可了解相关说明。

有关图 4-9 的说明：

1. **输入时钟频率 (Hz)**：这是基准时钟频率 (RCLK)。

2. **输入时钟分频器**：这是用于对基准时钟频率进行分频的分频器。OSPI 输出时钟 = 输入时钟频率/输入时钟分频器。

3. **芯片选择**：默认情况下，CS0 供 OSPI 控制器使用。

4. **协议**：此字段从 FLASH 部分的 **协议** 中填充。

5. **启用 DMA**：当事务大小大于 1KB 时，会进行 DMA 传输。

6. **启用 PHY 模式**：启用 PHY 模式（对于大于 50MHz 的时钟）。未选中时，将使用 TAP 模式。

**OSPI (1 of 1 Added)**

ADD

REMOVE ALL

|  CONFIG_OSPI0 |   |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                                                           | CONFIG_OSPI0                                                                                                                                                            |

| Input Clock Frequency (Hz)                                                                     | 166666666                                                                                                                                                               |

| Input Clock Divider                                                                            | 4                                                                                                                                                                       |

| Chip Select                                                                                    | CS0                                                                                                                                                                     |

| Protocol                                                                                       | 8D-8D-8D                                                                                                                                                                |

| Enable DMA                                                                                     | <input type="checkbox"/>                                                                                                                                                |

| Enable PHY Mode                                                                                | <input type="checkbox"/>                                                                                                                                                |

| Show Advanced Config                                                                           | <input type="checkbox"/>                                                                                                                                                |

| Instance Added By Bootloader                                                                   | <input type="checkbox"/>                                                                                                                                                |

图 4-9. OSPI 配置

## 5 常见启动问题和调试

使用 MCU+SDK 处理闪存时的一些常见问题如下所示。

### 5.1 引导失败

出现与 ROM 发出 3 字节地址且闪存保持 4 字节寻址模式相关的引导失败很常见。要了解有关这方面的更多信息，请参阅 AM62P TRM 中的图 5-1。

When using a OSPI\xSPI\QSPI\SPI flash device greater than 128Mb which supports 3-byte and 4-byte addressing modes, a flash device package with a RESET signal must be used. The reason is that the ROM only uses 3 byte addressing mode (address is 24bits). To address the full memory address range, software will typically switch to 4-byte addressing mode. If a reset to the processor occurs (eg, due to a warm reset), the ROM will execute expecting 3-byte addressing mode, but the flash will have been left in 4-byte addressing mode. In order for the flash device to return to 3-byte addressing mode, it must be reset using this signal. This typically can be achieved by using the RESET signal on the flash memory device. The ROM does not issue a software reset command.

图 5-1. 关于复位信号的 AM62P TRM 部分

某些串行 NAND 闪存无法在串行 NAND 引导模式下引导，因为闪存中的参数页未存储在偏移地址 0x1 处。对于串行 NAND 闪存，参数页必须位于偏移地址 0x1 处，才能在串行 NAND 引导模式下成功引导。有关参数页偏移的信息可以从闪存数据表中获得。

对于串行 NOR 闪存，请始终确保验证引导模式说明中的命令。[了解引导模式和闪存兼容性](#) 中对此进行了介绍。

使用 QSPI NOR 闪存时，常见引导模式是 QSPI 引导模式。请注意，对于 QSPI 引导模式，除了使引导模式说明与闪存数据表相符之外，还必须检查 QE 位。QE 是四路使能位。为了使 ROM 正确发出 1S-1S-4S，QSPI 闪存必须已设置 QE 位，因为 ROM 未设置该位。有些 QSPI 闪存默认情况下在出厂时设置了 QE 位。对于未设置 QE 位的 QSPI 闪存，TI 建议在 QSPI 引导模式下在引导之前设置 QE 位。

### 5.2 已知勘误表

一些 TI Sitara 处理器提供关于引导和闪存的已知勘误表。有关处理器特定勘误表的链接，请参阅 [参考](#)。

1. i2351：所有 TI Sitara™ 处理器。

2. i2307：AM64x、AM62x 处理器。

3. i2366：AM62Ax、AM64x、AM62Dx、AM62x 处理器。

4. i2420：AM62Ax、AM64x、AM62Dx、AM62x 处理器。

5. i2189：所有 TI Sitara 处理器。

6. i2249：所有 TI Sitara 处理器。

7. i2383：所有 TI Sitara 处理器。

### 5.3 闪存初始化失败

在某些情况下，在 Flash\_norOspiOpen 函数中会看到挂起，而在大多数情况下，会打印一个日志，表示 *FLASH open failed for instance 0 !!!*。这表明闪存尚未正确初始化。要通过此步骤，请参阅以下提示。

#### 5.3.1 FLASH 和 OSPI SysConfig 值

重新访问 OSPI 和 FLASH 值，并查看是否有任何值写入错误。

#### 5.3.2 闪存器件和制造 ID 读取失败

要调试读取 ID 故障，请通读以下 [常见问题解答](#)。

#### 5.3.3 PHY 故障

有两种与 PHY 调优相关的故障。选中 **Enable PHY Mode** 后，可能会遇到这两种故障。开始之前，请了解 [OSPI PHY 调优](#) 和 [PHY 调优攻击向量](#)。

第一个故障是：“PHY enabling failed!!! Continuing without PHY...”；第二个故障是无法计算 OTP（最优调优点）。第一个故障发生在攻击向量已闪存但未正确读取时。因此，这反过来又指向第 5.3.1 节和第 5.3.2 节。第二个故障发生在 PHY 调优算法返回故障后。要调试此故障，可以考虑执行以下步骤：

1. 默认情况下，在 `flash_nor_ospic.c` 文件中，调用 `OSPI_phyTuneDDR`。如果在 STR 中配置了所使用的协议，则必须调用函数 `OSPI_phyTuneSDR`。

2. 要调试 PHY 调优故障，TI 建议生成 PHY 调优图。请参阅[此处的常见问题解答](#)。当发生 PHY 故障时，该图可用作参考，以查看 OTP 点的标记位置。

## 5.4 闪存读取失败

在某些情况下会发生闪存读取失败。这些情况包括：

1. 当 OSPI 控制器处于 DAC 状态时，使用特定地址范围映射闪存内容。图 5-2 显示了可用地址范围。默认情况下选择 0x60000000。当 MPU 区域 0x60000000 标记为缓存时会发生读取失败。这是用于闪存直接内存映射的区域。在软件中，这是通过将寄存器 0xFC40000 中的第 7 位 DAC 位设置为 1 来实现的。因此，0x60000000 不需要标记为“缓存”。

2. `SysConfig` 中的读取命令集对于所配置的协议不正确。一些闪存针对 3 字节和 4 字节寻址具有不同的读取命令。

3. 假设闪存上的数据为 *00h 01h 02h 03h …*，缓冲区中的读取值为 *01h 02h 03h 04h …*。这指向第 5.3.1 节，其中用于读取的虚拟时钟关闭值为 1。

4. DMA 相关问题包括由于读取缓冲区未缓存对齐而导致无法正确读取数据。

| Address Range             | Size   | Description                      |

|---------------------------|--------|----------------------------------|

| 0x400000000 - 0x4FFFFFFF  | 4 GB   | External Memory Space (Region 0) |

| 0x060000000 - 0x067FFFFFF | 128 MB | Boot Space (Region 1)            |

| 0x500000000 - 0x5FFFFFFF  | 4 GB   | External Memory Space (Region 3) |

图 5-2. FSS 内存区域

## 5.5 闪存编程故障

闪存擦除和写入失败的原因如下：

1. 在执行写入操作之前，没有擦除发出写入操作的扇区或块。

2. 对于配置的协议，`SysConfig` 中的写入/擦除命令集不正确。一些闪存具有用于 3 字节和 4 字节寻址的不同命令。

3. 定义的闪存程序和闪存繁忙超时过低。

4. 如图 5-2 中所述，默认选择的地址范围 0x60000000 必须标记为严格排序、而不是缓存。将区域标记为缓存会导致写入失败。

## 6 请求 OSPI 和 FLASH 支持的检查清单

在 [TI E2E™ 论坛](#) 上发布与 OSPI/闪存相关的问题之前，如果能解决以下问题，会很有帮助：

1. 使用了哪款 TI 处理器？

2. 使用的 MCU+ SDK 版本是什么？

3. 测试是在定制电路板还是在 TI EVM 上完成的？

4. 命名定制闪存器件并附上数据表。

5. 是否已通过闪存数据表对 [SysConfig](#) 中的值进行了验证？

6. 按照[此处](#)的调试指南共享故障日志或故障点。

7. 指向本应用手册中的特定部分，进一步了解在测试电路板上观察到的故障。

## 7 摘要

本应用手册为使用 MCU+ SDK 将定制 xSPI 闪存器件与 TI Sitara 处理器进行集成的开发人员提供实用的调试参考。本文档大致介绍了用于诊断和解决引导故障、闪存读取/写入/擦除问题以及器件整体启动挑战的系统方法。其中包括逐步检查、配置指南和验证提示，可帮助工程师快速找出根本原因并加快自定义 DUT 上的系统启动。通过整合常见故障场景和成熟的调试工作流，本指南可帮助减少集成工作量、并实现定制 NOR 或 NAND 闪存的可靠运行。

## 8 参考资料

1. 德州仪器 (TI) , [AM62Px Sitara 处理器](#)，数据表。

2. 德州仪器 (TI) , [AM62Px MCU+ SDK](#)。

3. Infineon Technologie , [S28HS512T 数据表](#)。

4. 德州仪器 (TI) , [AM62Px Sitara 处理器技术参考手册](#)，技术参考手册。

5. 德州仪器 (TI) , [AM62x 处理器器件](#)，勘误表。

6. 德州仪器 (TI) , [AM62Dx Sitara 处理器器件勘误表](#)，勘误表。

7. 德州仪器 (TI) , [AM64x/AM243x 处理器器件](#)，勘误表。

8. 德州仪器 (TI) , [AM62L Sitara 处理器器件勘误表](#)，勘误表。

9. 德州仪器 (TI) , [AM62A 处理器器件勘误表](#)，勘误表。

10. 德州仪器 (TI) , [AM62P Sitara 处理器器件勘误表](#)，勘误表。

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025，德州仪器 (TI) 公司

最后更新日期：2025 年 10 月