*Application Note*

# 高速并行接口的电路板设计和仿真指南

*Sitara MPU Hardware Applications*

## 摘要

本应用手册包含适用于高速并行接口电路板设计和仿真的指南。

## 内容

|                       |   |

|-----------------------|---|

| <b>1 简介</b>           | 2 |

| <b>2 电路板设计和布局指南</b>   | 2 |

| 2.1 通用板设计指南           | 2 |

| 2.2 针对信号完整性的附加电路板设计指南 | 2 |

| 2.3 设计示例              | 4 |

| <b>3 电路板设计仿真</b>      | 4 |

| 3.1 电路板模型提取           | 4 |

| 3.2 仿真设置              | 5 |

| <b>4 总结</b>           | 6 |

| <b>5 参考资料</b>         | 6 |

## 商标

所有商标均为其各自所有者的财产。

## 1 简介

本文档包含适用于高速并行接口电路板设计和仿真的信息。这些接口包括采用 LVC MOS I/O 缓冲器的接口。如需了解受支持的数据速率，请参阅特定于器件的数据手册。这包括八路串行外设接口 (OSPI)、RGMII ( 简化千兆位媒体独立接口 ) 等接口。这些接口通常通过在相应器件上使用 LVC MOS ( 低压互补金属氧化物半导体 ) IO 缓冲器来实现。高速并行接口规范遵循 JEDEC 标准、例如 RGMII EIA/JESD 8-6 1995。

## 2 电路板设计和布局指南

### 2.1 通用板设计指南

为了验证信号性能是否良好，必须遵循以下通用电路板设计指南：

- 所有信号都需要接地基准（强烈建议在两侧都实现）。

- 避免在信号参考平面中出现穿过平面分割点的情况。

- 在去耦电容器和电源引脚之间使用尽可能宽的布线。

- 通过保持阻抗匹配来最大限度地减少码间串扰 (ISI)。

- 通过隔离敏感信号（如选通和时钟）以及使用适当的 PCB 堆叠方式来最大限度地减少串扰。

- 每当信号改变层和参考平面时，通过添加过拼接孔来避免返回路径不连续。

- 通过适当的隔离和正确使用去耦电容器来更大限度地降参考低电压噪声。

- 保持信号布线残桩长度尽可能短。

- 为时钟和选通网额外增大间距以最大限度地减少串扰。

- 为所有信号以及所有旁路和去耦电容器保持一个公共接地（也称为 GND）基准。

- 评估时序限制时，需要考虑微带线和带状线网之间的传播延迟差异。

- 过孔之间的耦合会是产生 PCB 级串扰的重要原因。过孔的尺寸和间距很重要。对于高速接口，应考虑 GND 屏蔽过孔。这种过孔耦合是推荐在最靠近处理器的层上路由数据信号的一个因素。

- 过孔残桩会影响信号完整性。使用过孔背钻可提高信号完整性，并且在某些情况下是必需的。

### 2.2 针对信号完整性的附加电路板设计指南

- 影响信号完整性的因素众多，这是一个系统级优化挑战。

- 有各种选项用于解决信号质量。建议的选项列在 [信号质量选项](#) 中。

表 2-1. 信号质量选项

| 选项 | 建议                | 这有何帮助？                              |

|----|-------------------|-------------------------------------|

| A  | 添加串联端接            | 有助于减少反射并有助于提高信号质量。                  |

| B  | 添加负载电容器           | 这有助于减少返回反射。两端的平衡电容器可减少整体反射。         |

| C  | 布线长度增加            | 防止在信号仍在转换时异相反射影响入射信号。               |

| D  | 增加驱动强度以及 A、B、C 组合 | 更好的上升/下降并改善整体眼图以及 A、B、C 的组合，从而减少反射。 |

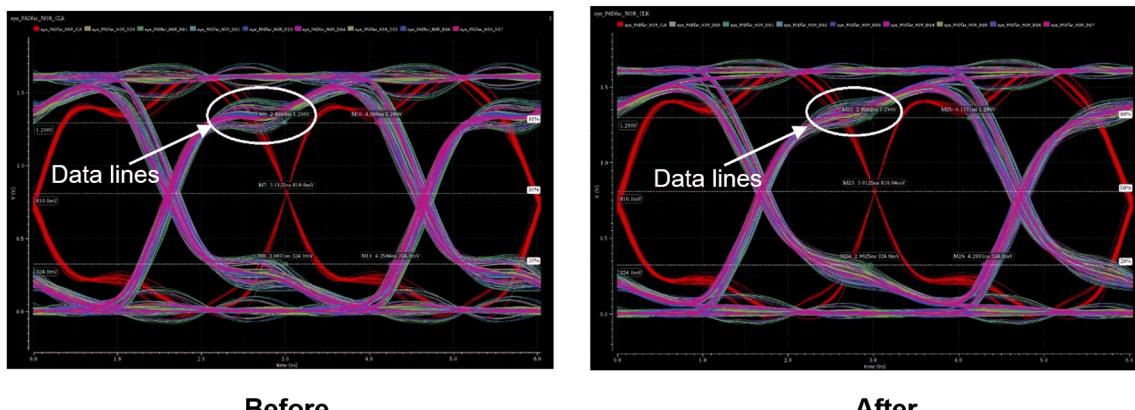

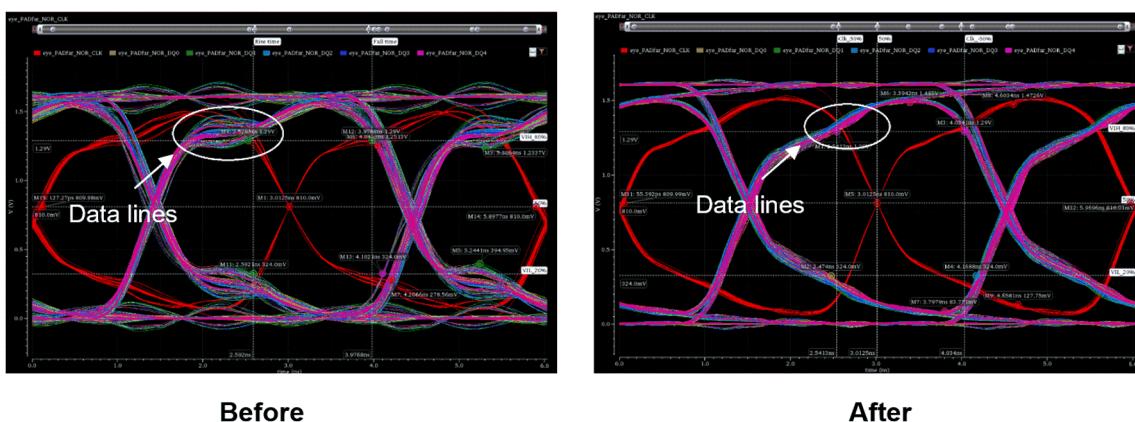

图 2-1. 数据线上添加了串联终端

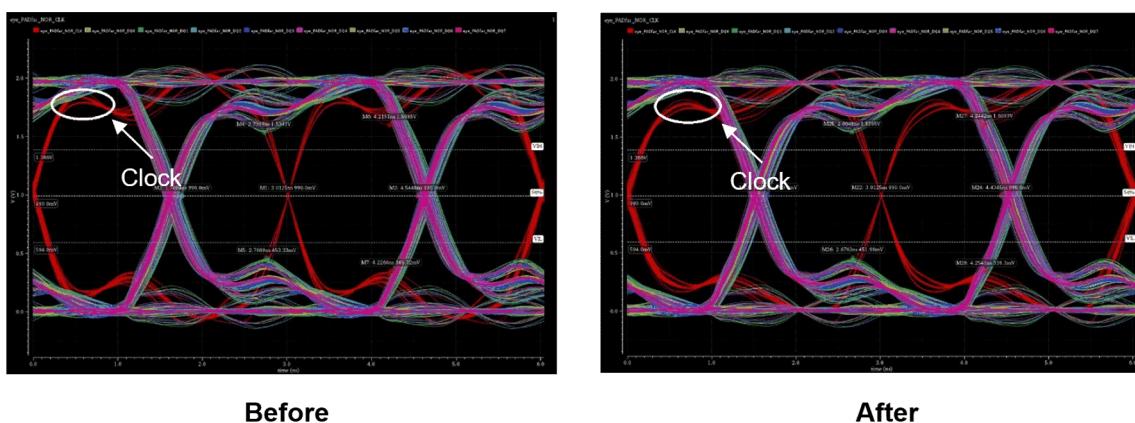

图 2-2. 时钟上添加了负载电容器

图 2-3. 数据线上的 A 和 B 的组合

## 2.3 设计示例

本节为电路板设计提供了一些提高信号质量的指导：

**Cload** 表示外设（封装、IO 等）的总容性负载。

对于约  $2\text{pF}$  的 **Cload**：

选项 1：使布线长度非常短（约 0.5 英寸至 0.6 英寸），在布线中间插入一个小电阻器（使用  $10\Omega$  或  $22\Omega$ ）。

选项 2：如果布线长度无法缩短到 0.5 英寸，并且布线长度介于 1 英寸和 5 英寸之间，请尝试以下选项。

- 按选项 1 所示在布线中间插入电阻器

- 在 **PHY BGA** 附近添加一个小型集总电容器（使用不同值的  $1\text{pF}$ 、 $2\text{pF}$ 、 $3\text{pF}$  等）。

选项 3：如果选项 1 和 2 不可行，请将布线长度增加到 **PHY** 规范允许的最大值（6 英寸）。除了增加布线长度外，还可以添加与选项 2b 类似的小型集总电容器。

请注意，这些可能是有助于提高信号质量的建议。选项 1 应提供出色的整体信号质量，但客户必须仿真和评估其中哪一种选项更适合特定系统。

## 3 电路板设计仿真

### 3.1 电路板模型提取

下列板级提取指导原则适用于任何 **EDA** 提取工具，而非特定的工具。在完成 **s** 参数的提取后，立即执行 [节 3.2](#) 中概述的步骤。运行 **IBIS** 仿真之前，必须执行这些步骤来检查设计。

- 对于信号提取，**2.5D** 提取就足够了。

- 检查电路板堆叠，以获取准确的层厚度和材料特性。

- 如果在提取之前切断电路板布局布线（以减少仿真时间），请在离信号和电源网至少 0.25 英寸的位置定义切断边界。

- 使用 **s** 参数或 **RLC** 封装模型（供应商通常会提供）进行进一步仿真。

#### 3.1.1 IBIS 模型仿真

本节概述了验证这些高速并行接口的方法。使用 **IBIS** 模型和提取的 **PCB** 模型进行通道仿真，并结合目标数据攻击位模式来生成信号波形和眼图。需要检查这些结果是否符合器件数据表中定义的设置/保持时间、转换率、时钟高电平和低电平等。需要根据 **VIH/VIL** 电压电平执行其他回铃检查。

## 3.2 仿真设置

按照以下步骤设置 IBIS 仿真：

- 提取电路板上信号的 S 参数文件。

- 由于运行时间限制，3D 提取工具是首选的但不可行。如果需要考虑运行时限制，则允许使用 2.5D 提取工具来提取电路板信号。

- 在 TI.com 的产品页面下获取 SoC IBIS 模型。

- 从 PHY 供应商处获取器件 IBIS 模型。该 IBIS 模型必须包含器件的封装、RLC 模型。

- 按照您选择的仿真器中所示，构建仿真网表。

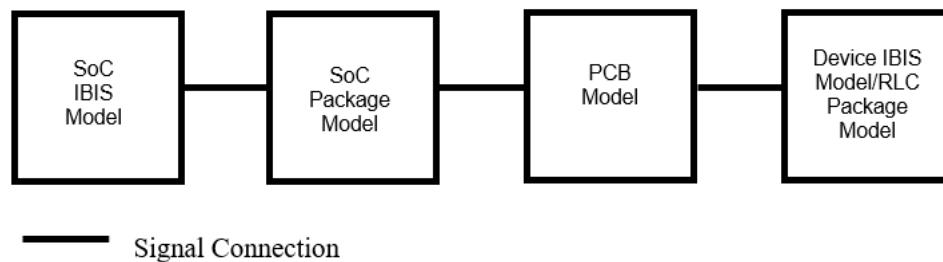

- 设置 SoC IBIS 模型、电路板模型和器件 IBIS 模型。

- 构建将要仿真的过程、电压、温度角。

- 建议针对 IBIS 模型支持的所有过程、电压和温度进行仿真：

- 典型值

- 最小

- 最大

- 在波形分析工具中分析结果，并使用器件数据表规范中的通过/失败检查来评估结果质量。

图 3-1. 典型的系统级仿真设置

## 4 总结

本应用报告说明了如何规划、布线和仿真 PCB 以实现成功的高速并行接口运行。如前所述、客户必须仿真和评估其中哪些选项（或已使用的任何其他选项）最适合特定系统。

## 5 参考资料

1. 德州仪器 (TI) , [AM62Px eMMC HS400 电路板设计和仿真指南](#)，应用手册。

2. 简化千兆位媒体独立接口 (RGMII)- EIA/JESD 8-6 1995。

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025，德州仪器 (TI) 公司

最后更新日期：2025 年 10 月