## Application Note

使用 **TLC69699-Q1** 连接 IC 解决 **TLC696x1/2/4/8-Q1** 长 CCSI 菊花链难题

Fanbin Meng, Gracie Guo

## 摘要

局部调光背光用途广泛，在汽车显示应用中越来越受欢迎，可提供出色的用户体验，如更佳的图像对比度。

TLC696xx-Q1 系列是 TI 的 16 通道汽车级局部调光 LED 驱动器，支持直接和 2/4/8 时分多路复用控制。

最新的显示背光板可实现数千个 LED，以获得更高的对比度和更薄的模组厚度。调光区域越多，单个菊花链中需要的局部调光 LED 驱动器越多。在长串联的连续时钟串行接口 (CCSI) 配置下，TLC696xx-Q1 系列可能会面临时钟占空比增加的难题，这限制了最大级联数量。

本应用手册解释了时钟占空比增加问题的根本原因，并提出了一种基于 TLC69699-Q1 连接 IC 支持更多级联驱动器的有效设计。

## 内容

|                               |           |

|-------------------------------|-----------|

| <b>1 简介</b>                   | <b>2</b>  |

| <b>2 长 CCSI 菊花链难题</b>         | <b>3</b>  |

| 2.1 CCSI CLK_O 占空比增加问题        | 3         |

| 2.2 CCSI 频率设计注意事项             | 5         |

| <b>3 TLC69699-Q1 连接 IC 设计</b> | <b>6</b>  |

| 3.1 CLK_O 占空比和数据速率的 CCSI 控制   | 7         |

| 3.2 具有故障信号的优化型故障回读方案          | 8         |

| 3.3 TXFIFO 配置                 | 9         |

| <b>4 总结</b>                   | <b>10</b> |

| <b>5 参考资料</b>                 | <b>10</b> |

## 商标

所有商标均为其各自所有者的财产。

## 1 简介

局部调光背光设计根据亮度、对比度和模块厚度要求，选择不同的调光区域。更大的 LED 调光区域需要更多 LED 驱动器。TI TLC696xx-Q1 系列提供直接驱动和时分多路复用选项，以满足客户对调光区域的需求。TLC696x1-Q1 是 16 通道直接驱动 LED 驱动器，而 TLC696xx-Q1 可支持 2/4/8 时分多路复用矩阵，实现最多 32/64/128 个调光区域控制。

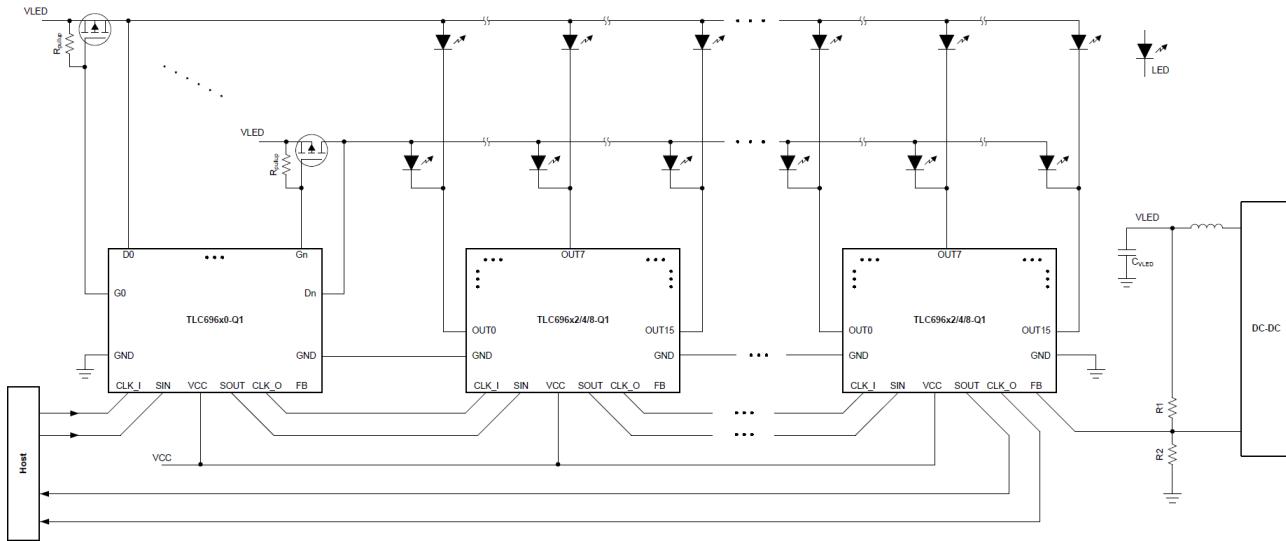

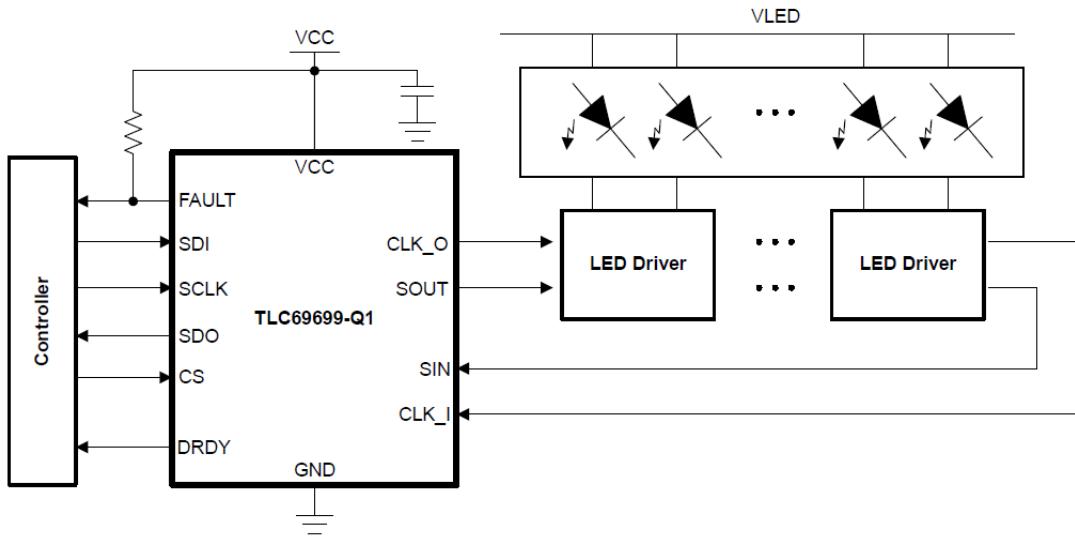

通常，局部调光 LED 驱动器必须将所有 LED 驱动器连接在单一 SPI 回路中，以实现简单的亮度控制。星型连接 SPI 接口的信号完整性难题会限制最大级联数量。TI TLC696xx-Q1 系列与传统的 SPI 接口不同，采用具有内置缓冲器的两线制 CCSI 来增强信号质量。如图 1-1 所示，TLC696x0-Q1 通过菊花链中的两线制接口连接到 TLC696xx-Q1。CLK\_I (时钟输入) 和 SIN (数据输入) 通过内部缓冲器，重新生成为 CLK\_O (时钟输出) 和 SOUT (数据输出)，然后传递到下一个器件。此类连接可以提高信号完整性，并降低系统电路板布局的复杂性。

图 1-1. 时分多路复用方案下的 TLC696x2/4/8-Q1 CCSI 连接

## 2 长 CCSI 菊花链难题

TLC696xx-Q1 系列 CCSI 接口通过内置缓冲器提高时钟信号质量，但最大级联器件数受 CCSI CLK\_O 占空比增加问题的限制。菊花链器件末端的 CLK\_O 波形可能违反长菊花链应用中的 CCSI 时序要求。

### 2.1 CCSI CLK\_O 占空比增加问题

TLC696xx-Q1 系列的 I/O 电压旨在兼容 1.8V 和 3.3V 电压，以连接到不同类型的主控器件（如时序控制器）。对于传统接口的逻辑电平设计，逻辑低电压必须以  $0.3 \times VCC$  为基准，逻辑高电压应以  $0.7 \times VCC$  为基准，且实际逻辑高电平和低电平值必须以施加到器件的实际 VCC 为基准。TLC696xx-Q1 系列的 SIN/CLK\_I 逻辑低电平和高电平是指  $VCC=1.8V$  的固定值，如表 2-1 所列。

表 2-1. TLC696xx-Q1 输入逻辑电平电压阈值

| 参数        |                   | 最小值  | 典型值 | 最大值  | 单位 |

|-----------|-------------------|------|-----|------|----|

| 逻辑接口      |                   |      |     |      |    |

| VLOGIC_IL | 低电平输入电压、SIN、CLK_I |      |     | 0.54 | V  |

| VLOGIC_H  | 高电平输入电压、SIN、CLK_I | 1.26 |     |      | V  |

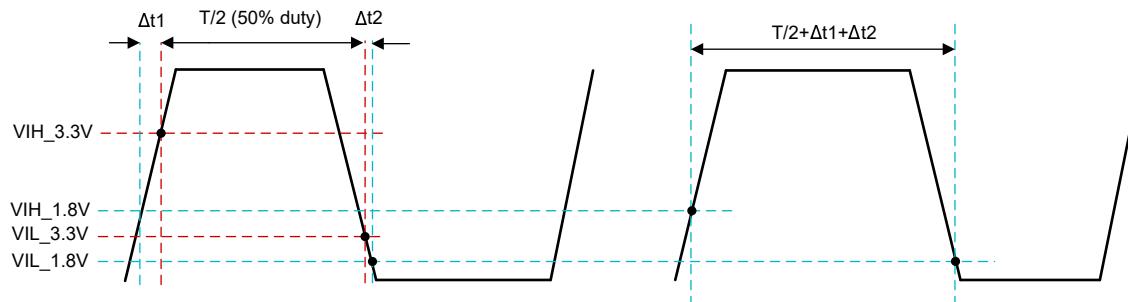

在固定阈值下，TLC696xx-Q1 系列在 VCC 电压等于 3.3V 时，会表现出 CLK\_O 占空比增加的行为。图 2-1 显示了第一个 LED 驱动器内部缓冲器的输入和输出信号，左侧是第一个器件的输入信号，右侧是输出信号。假设主机器件支持发送 3.3V/50% 占空比的时钟信号，TLC696xx-Q1 预期会在上升沿到达  $VIH_{3.3V}$  时识别逻辑高电平，在下降沿到达  $VIL_{3.3V}$  时识别逻辑低电平，但实际上 TLC696xx-Q1 系列会更早识别逻辑高电平 ( $\Delta t1$ )，并更晚识别逻辑低电平 ( $\Delta t2$ )。对于 50% 占空比的时钟输入，其逻辑高电平周期会被识别为  $T/2+\Delta t1+\Delta t2$ ，因此 LED 驱动器再生的时钟信号相比输入信号具有更高的占空比。

图 2-1. TLC696x1/2/4/8-Q1 输入和输出时钟信号占空比增加

时钟占空比会在整个菊花链中增加，因此最大可级联数量的限制因素之一就是 CLK\_I 的最短低电平时间。如 TLC696xx-Q1 系列所示，需要至少 18ns 的 CLK\_I 低电平时间才能识别有效的时钟信号。这样的情况可能会恶化，例如信号的转换率较慢或信号频率较高 (T/2 较小) 时。

表 2-2. TLC696xx-Q1 最小 CLK\_I 低电平时间要求

| 参数       |             | 最小值 | 典型值 | 最大值 | 单位 |

|----------|-------------|-----|-----|-----|----|

| SPI 时序要求 |             |     |     |     |    |

| Tw(h)    | CLK_I 高电平时间 | 18  |     |     | ns |

| Tw(L)    | CLK_I 低电平时间 | 18  |     |     | ns |

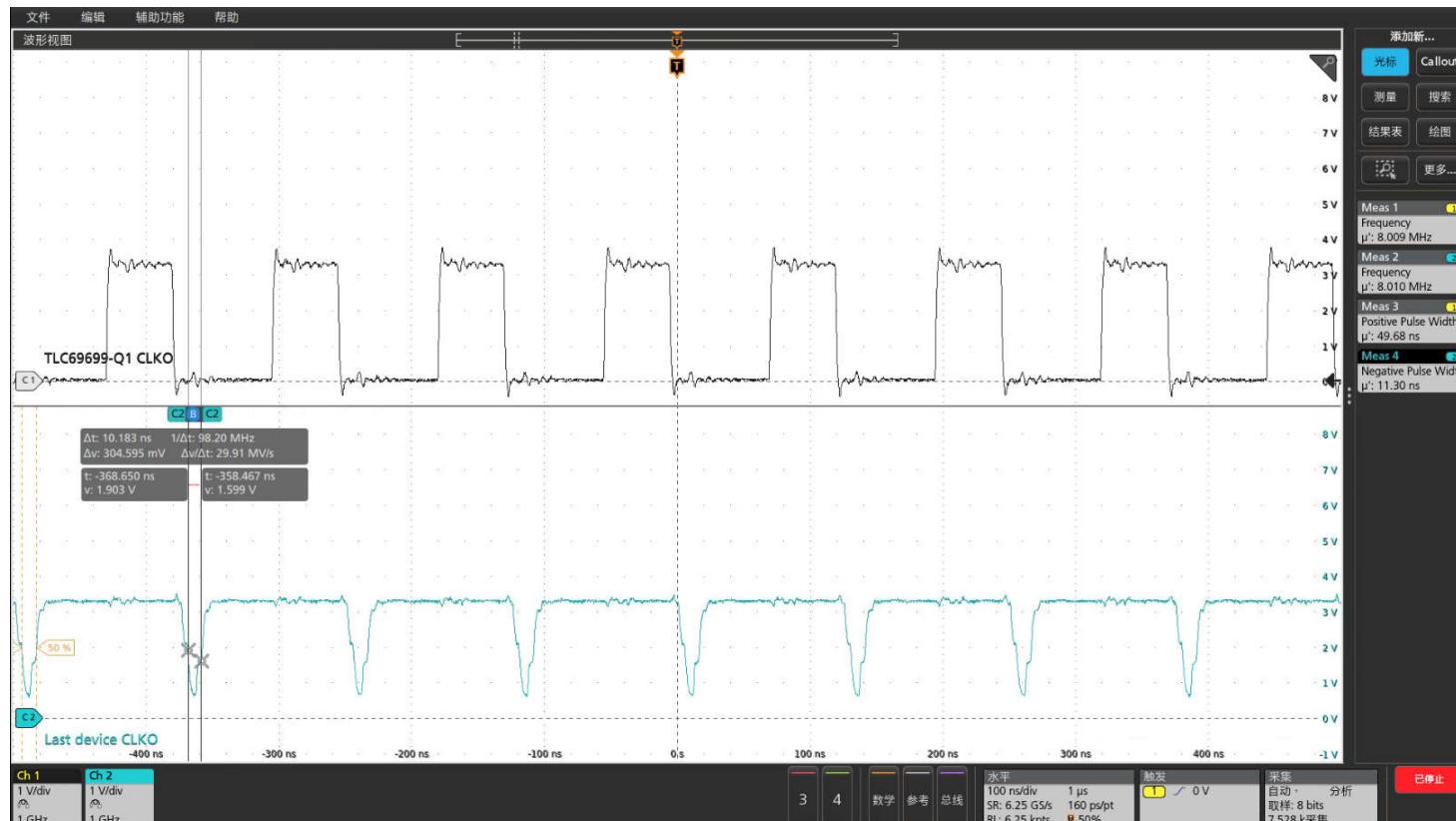

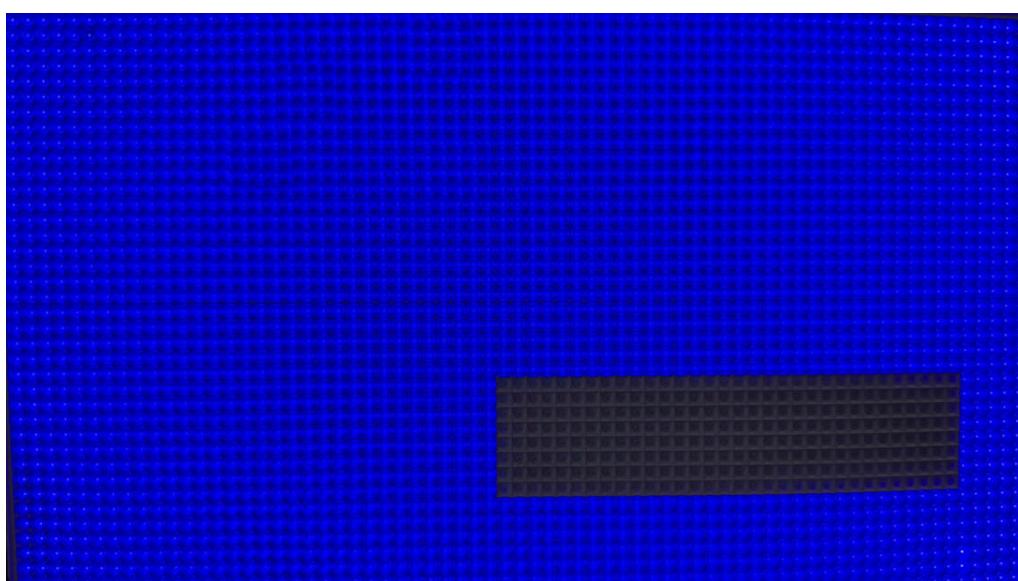

图 2-2 展示了一个 15.6 英寸显示屏背光设计示例，该示例在单个菊花链中具有一个 FET 控制器 (TLC69610-Q1) 和 43 片式 LED 驱动器 (TLC69614-Q1)，可支持多达 2730 个调光区域。如图 2-2 所示，当 CCSI 时钟频率为 MHz，顶部是第一个器件的输入，底部是最后一个器件的 CLK\_O 时，占空比会在菊花链中增加，其中 CLK 低电平时间为 10ns。菊花链中最后一个器件的 CLK\_O 无法满足正确回读诊断操作的最小 CLK\_I 低电平时间要求。最后六个器件的时钟低电平时间均未满足 18ns 的要求，这与实际 LED 背光板点亮时的状态一致。（最后六个器件控制实际 LED 映射中黑色区域的调光区域），如图 2-3 中所示。

图 2-2. 第 38 个 LED 驱动器的 CLK\_O

图 2-3. LED 电路板启动

## 2.2 CCSI 频率设计注意事项

调整 CCSI 频率是解决 **CLK\_O** 占空比增加问题并支持更多级联器件的有效方法。如果主机控制器的转换率相同，则可以假定每个 LED 驱动器上增加的时间 ( $\Delta t_1 + \Delta t_2$ ) 为固定值，因此较低的 CCSI 频率允许更长的逻辑低电平周期 ( $T/2$ )。较低的 CCSI 频率必须传递更多菊花链式 LED 驱动器，直到 **CLK** 低电平时间达到最小限值。

TLC696xx-Q1 系列 CCSI 频率与某些系统级性能（包括 EMI 和音频噪声消除）相关。本应用手册重点介绍计算所需最小 CCSI 频率的基本规则，即在单帧内显示并传输所需的亮度数据。表 2-3 列出了 43 片式 LED 驱动器的级联系统设计要求，这是计算所需频率的示例。

**表 2-3. 43 片式 LED 驱动器级联系统的设计要求**

| 参数    | 详细要求        |

|-------|-------------|

| 器件型号  | TLC69614-Q1 |

| 行编号   | 4           |

| 帧速率   | 60 帧/秒      |

| 亮度分辨率 | 12 位        |

| 芯片数量  | 43 片        |

PWM 亮度显示的最低频率：

$$F_{\text{Min\_Display}} = (\text{帧速率}) \times (2^{\text{亮度分辨率}}) \times (\text{行数}) = 0.98\text{MHz}$$

传输亮度的最小频率（请参阅数据表中的亮度写入命令）：

$$F_{\text{Min\_Transmission}} = (\text{帧速率}) \times [16 \times 3 + 16 \times (\text{芯片数量}) + 16 + (\text{芯片数量}) \times 16 \times (\text{行数}) \times 16 + 16] = 2.75\text{MHz}$$

计算得出的 TLC696x4-Q1 最小 CCSI 频率为 2.75MHz，可在单帧内传输并显示 LED 区域亮度数据。但在大多数应用中，需要选择更高的 CCSI 频率，以为 TCON 局部调光算法计算和 LED 驱动器故障诊断预留更多时间。这就是 TCON 选择 8MHz 作为启动该系统的起点的原因。在接下来的章节，将讨论如何在不影响系统级要求的前提下，进一步降低所需的 CCSI 频率。

### 3 TLC69699-Q1 连接 IC 设计

TLC69699-Q1 是 SPI 与连续时钟串行接口 (CCSI) 之间的 SPI 兼容型 IC 连接。这是为了解决某些 SPI 接口 TCON 的 CCSI 兼容性难题，如图 3-1 中所示。在主机控制器和原始 LED 驱动器菊花链之间添加额外的 TLC69699-Q1 有助于通过三种方式解决 CLK\_O 占空比增加的限制：

1. 降低 CLK\_I 的高电平占空比，然后转发到第一个 LED 驱动器；

2. 借助故障中断功能，节省每帧轮询 LOD、LSD、TSD 和状态的时间；

3. 降低内部 TXFIFO 中的 CCSI 输出频率。

图 3-1. TLC69699-Q1 典型应用

### 3.1 CLK\_O 占空比和数据速率的 CCSI 控制

TLC69699-Q1 提供两种占空比控制选项。除了传统的 50% 占空比选项外，用户还可以强制将 CLK\_O 的高电平脉冲宽度固定为 50ns。如表 3-1 中所，示通过将 CCSI\_DC\_CTRL 与 CCSI\_DATA\_RATE 结合使用，CLKO 高电平脉冲持续时间可以从 50% 减少到较低的百分比。因此，即使存在 CLKO 占空比累积，也可以从一开始就加长低电平脉冲持续时间，从而增加菊花链器件数量。

**表 3-1. CCSICTRL 寄存器字段说明**

| 位   | 字段             | 类型  | 复位  | 说明                                                                                                                                                                                                                                                                                                                      |

|-----|----------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | CCSI_DC_CTRL   | R/W | 0x0 | CCSI 的占空比控制<br>0x0 = CLK_O 的占空比为 50%，但 CCSI_DATA_RATE[3:0] = 4b'1110 (33.33%) 和 CCSI_DATA_RATE[3:0] = 4b'1100 (40%) 除外<br>0x1 = CLK_O 高电平脉冲持续时间保持在 50ns，但 CCSI_DATA_RATE[3:0] = 4b'111X 除外 (此时为 25ns)                                                                                                                   |

| 5-4 | RESERVED       | R/W | 0x0 | 保留                                                                                                                                                                                                                                                                                                                      |

| 3-0 | CCSI_DATA_RATE | R/W | 0x0 | CCSI 的数据速率<br>0x0 = 1Mbit/s<br>0x1 = 1.25Mbit/s<br>0x2 = 1.43Mbit/s<br>0x3 = 1.67Mbit/s<br>0x4 = 2Mbit/s<br>0x5 = 2.22Mbit/s<br>0x6 = 2.5Mbit/s<br>0x7 = 2.86Mbit/s<br>0x8 = 3.33Mbit/s<br>0x9 = 4Mbit/s<br>0xA = 5Mbit/s<br>0xB = 6.67Mbit/s<br>0xC = 8Mbit/s<br>0xD = 10Mbit/s<br>0xE = 13.33Mbit/s<br>0xF = 20Mbit/s |

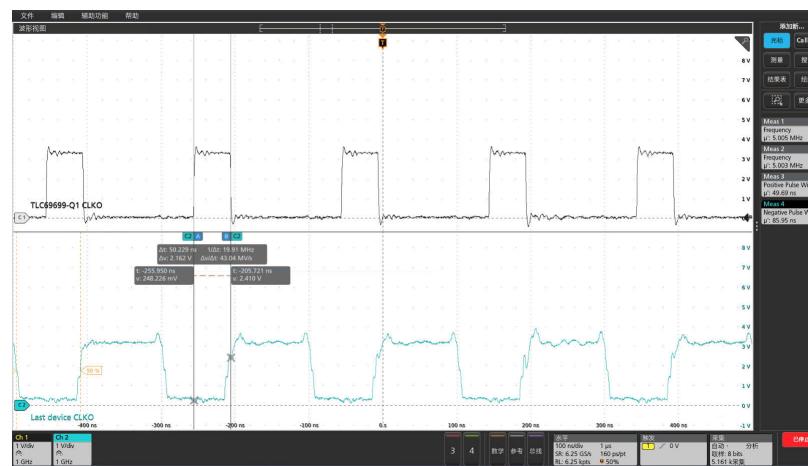

图 3-2 展示了在 5MHz CCSI 数据速率下的测试结果，此时将 CLK\_O 的高电平脉冲持续时间强制固定为 50ns，这意味着菊花链中的第一个 LED 驱动器可以接收到占空比较低的输入时钟。最后一个 LED 驱动器的低电平脉冲持续时间可达到 85.9ns，从而在 18ns 的最低要求中保留了足够的裕度。

**图 3-2. TLC69699-Q1 的 CLK\_O 和 CCSI = 5MHz 时的最后一个 LED 驱动器，CLK\_O 高电平脉冲持续时间 = 50ns**

### 3.2 具有故障信号的优化型故障回读方案

TLC696xx-Q1 系列支持诊断功能，包括 LED 短路检测 (LSD)、LED 开路检测 (LOD) 和热关断检测 (TSD)。如图 3-3 所示，FC27 寄存器记录当前芯片故障状态，FC26 寄存器记录之前的芯片故障状态，包括芯片索引和故障类型。在没有额外 TLC69699-Q1 器件的正常系统中，主机控制器需要在每帧读取最后一个 LED 驱动器器件的 FC26 和 FC27 寄存器，以检测在主机未配备 UART 回读功能的情况下，菊花链中是否存在故障。

#### 8.5.29 FC27 Register (Offset = 1Bh) [reset = 0000h]

FC27 is shown in Figure 8-60 and described in Table 8-40.

[Return to Summary Table.](#)

Figure 8-60. FC27 Register

| 15       | 14               | 13 | 12 | 11 | 10 | 9 | 8 |

|----------|------------------|----|----|----|----|---|---|

| RESERVED | RESERVED         |    |    |    |    |   |   |

| R/W-0h   | R/W-0h           |    |    |    |    |   |   |

| 7        | 6                | 5  | 4  | 3  | 2  | 1 | 0 |

| RESERVED | CURR_CHIP_STATUS |    |    |    |    |   |   |

| R/W-0h   | R-0h             |    |    |    |    |   |   |

Table 8-40. FC27 Register Field Descriptions

| Bit  | Field            | Type | Reset | Description                                                     |

|------|------------------|------|-------|-----------------------------------------------------------------|

| 15   | RESERVED         | R/W  | 0h    | This bit is reserved and must be 0.                             |

| 14-7 | RESERVED         | R/W  | 0h    | These bit are reserved.                                         |

| 6-0  | CURR_CHIP_STATUS | R    | 0h    | CURR_CHIP_STATUS [6:0] = {INT, FB_OVF, TSD, LSD, LOD, INC, DEC} |

图 3-3. TLC696xx-Q1 FC26/27 寄存器芯片状态

#### 8.5.28 FC26 Register (Offset = 1Ah) [reset = 0000h]

FC26 is shown in Figure 8-59 and described in Table 8-39.

[Return to Summary Table.](#)

Figure 8-59. FC26 Register

| 15               | 14               | 13 | 12 | 11 | 10 | 9 | 8 |

|------------------|------------------|----|----|----|----|---|---|

| RESERVED         | PREV_CHIP_STATUS |    |    |    |    |   |   |

| R/W-0h           | R-0h             |    |    |    |    |   |   |

| 7                | 6                | 5  | 4  | 3  | 2  | 1 | 0 |

| PREV_CHIP_STATUS |                  |    |    |    |    |   |   |

| R-0h             |                  |    |    |    |    |   |   |

Table 8-39. FC26 Register Field Descriptions

| Bit  | Field            | Type | Reset | Description                                                                        |

|------|------------------|------|-------|------------------------------------------------------------------------------------|

| 15   | RESERVED         | R/W  | 0h    | This bit is reserved and must be 0.                                                |

| 14-0 | PREV_CHIP_STATUS | R    | 0h    | PREV_CHIP_STATUS [14, 13, 12, 11, 10, [9:0]] = {TSD, LSD, LOD, INC, DEC, chip_idx} |

图 3-4. FC26 寄存器和字段说明

TLC69699-Q1 实现了故障中断引脚以指示系统中的多种故障类型，包括 DAISY\_CHAIN\_FAULT，该故障表示菊花链中的一个或多个器件报告了 LOD、LSD 和 TSD 错误。主机控制器可以检测 TLC69699-Q1 的故障中断状态并读取 TLC696xx-Q1 的 FC26/FC27 寄存器，以进一步找到芯片索引和故障类型。将 DAISY\_CHAIN\_FAULT 映射到故障中断信号可以节省每帧读取 FC26/27 的额外时间，这有助于有效降低 CCSI 频率。

借助 DAISY\_CHAIN\_FAULT 中断功能，可以取消为故障轮询预留的时间。因此，在这个 43 片级联的情况下，TCON 可以将 SPI 频率从 8MHz 降低到 5.2MHz。下一节将详细介绍 SPI 频率的设置。

### 3.3 TXFIFO 配置

#### TXFIFO 配置

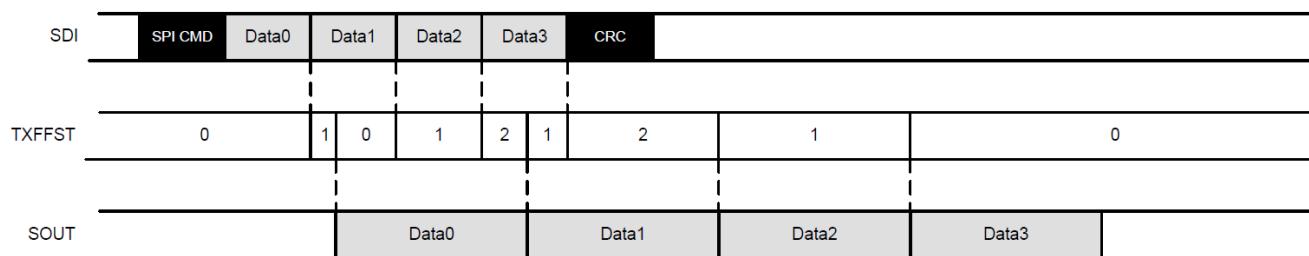

TLC69699-Q1 具有传输和接收 FIFO，这意味着传输 FIFO (TXFIFO) 是由 SPI 外设接收并由 CCSI 控制器传输的数据。两个 FIFO 都是 16 位宽的先进先出存储器缓冲区。FIFO 用于存储数据字，以满足数据在 SPI 时钟域和 CCSI 时钟域之间传输时的时序要求。当 SPI 时钟域以高于 CCSI 时钟域的频率运行时，TXFIFO 会存储尚未由 CCSI 控制器传输的 SPI 外设接收到的数据。计数器 (TXFFST) 会跟踪当前存储在 TXFIFO 中的字数，最大 TXFFST 值可设置为 0x1FF。图 3-5 中描述了 SPI 外设以高于 CCSI 控制器的时钟频率运行的示例，只要正确防止 FIFO 溢出，就会设置一个低于 SPI 频率的 CCSI 频率。

图 3-5. 以高于 CCSI 控制器的频率运行的 SPI 外设示例

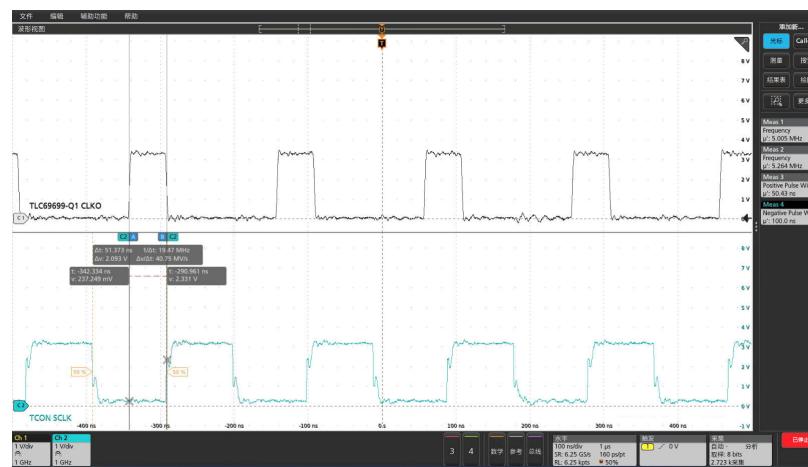

TCON 现在可以将 SPI 频率从 8MHz 降低到 5.2MHz，TLC69699-Q1 TXFIFO 有助于进一步将 CCSI 频率降低到 5MHz 或更低，如图 3-6 所示，底部波形是 5.2MHz 时的 TCON SPI 输出，顶部是 5MHz 时的 TLC69699-Q1 CCSI 输出。只要正确防止 FIFO 溢出，就可以使用 CCSI\_DATA\_RATE 为 TLC69699-Q1 设置较低的 CCSI 输出频率。

图 3-6. 使用 TXFIFO 进行 TLC69699-Q1 输入和输出频率控制

## 4 总结

TLC696xx-Q1 系列在 3.3V I/O 电压下会表现出 CLK\_O 占空比增加的行为，因此最小时钟低电平时间限制了级联的最大 LED 驱动器数量。TLC69699-Q1 通过 CCSI 占空比控制、优化的故障回读方案以及 TXFIFO 功能，可以降低所需的 CCSI 频率，从而在单条长菊链中级联更多 TLC696xx-Q1 驱动器。

## 5 参考资料

1. 德州仪器 (TI) , [适用于 TLC696xx-Q1 器件系列的 TLC69699-Q1 汽车级 SPI 兼容型连接](#) , 数据表。

2. 德州仪器 (TI) , [TLC696x2/4/8-Q1 16 通道、2/4/8 时分多路复用汽车级局部调光背光 LED 驱动器](#) , 数据表。

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，TI 对此概不负责。

TI 提供的产品受 [TI 的销售条款](#) 或 [ti.com](#) 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址：Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

版权所有 © 2025, 德州仪器 (TI) 公司