*Application Note***TDP142 配置指南**

Jae Yoon

**摘要**

TDP142 是一款线性转接驱动器，支持高达 HBR3 (8.1Gbps) 的 DisplayPort 1.4。在这些较高的数据速率下，信号完整性问题会对系统布线长度造成限制。TDP142 提供 16 个接收线性均衡级别，用于补偿因码间串扰 (ISI) 而产生的电路板损耗。本文档旨在提供有关如何在源端/接收端应用中使用 TDP142 的通用指南。

**内容**

|                               |          |

|-------------------------------|----------|

| <b>1 简介</b>                   | <b>2</b> |

| <b>2 器件配置</b>                 | <b>2</b> |

| <b>3 均衡选择</b>                 | <b>3</b> |

| <b>4 均衡选择示例</b>               | <b>4</b> |

| <b>5 AUXP/N 和 SNOOPENZ 配置</b> | <b>5</b> |

| <b>6 布局指南</b>                 | <b>6</b> |

| 6.1 GND 拼接                    | 7        |

| 6.2 交流耦合电容器                   | 7        |

| 6.3 布局示例                      | 8        |

| <b>7 总结</b>                   | <b>8</b> |

| <b>8 参考资料</b>                 | <b>9</b> |

**商标**

DisplayPort™ is a trademark of Texas Instruments.

所有商标均为其各自所有者的财产。

## 1 简介

TDP142 是一款 DisplayPort™ 线性转接驱动器，用于支持每通道高达 HBR3 (8.1Gbps) 的速率。此外，对于 DP 链路训练过程具有透明性，因此 TDP142 是一款不受位置影响的器件，适用于发送端、接收端或线缆的应用。DisplayPort 标准定义了在兼容接收器必须运行的通道末端的最小眼图高度和宽度。较长的布线长度会增加 ISI，从而导致关闭眼图的通道损耗，并且眼图高度和宽度不再符合要求，接收器因此无法可靠地恢复该通道上的数据。TDP142 提供均衡增益，以补偿因 ISI 而产生的电路板迹线损耗并恢复到合规的眼图。

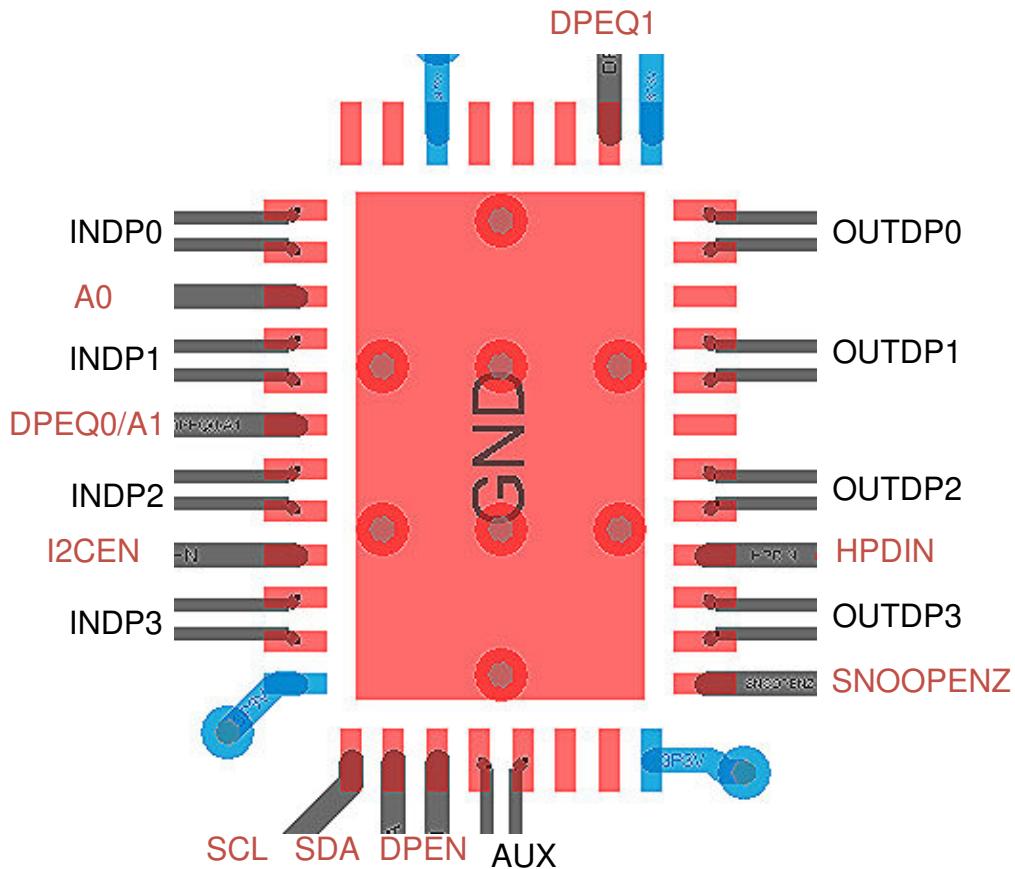

## 2 器件配置

TDP142 支持 GPIO 和 I2C 模式下的配置模式。表 2-1 详细说明了 TDP142 的 4 级控制引脚设置。表 2-2 详细说明了基于引脚设置的 TDP142 模式配置。如果器件配置为 GPIO 模式，请参阅表 2-2 了解用于启用 DisplayPort 和 AUX 监测功能的引脚配置，并参阅表 3-1 了解 DPEQ1 和 DPEQ0 引脚配置，以更改均衡设置。有关通过 I2C 实现的配置详细信息和寄存器映射，请参阅 [TDP142 DisplayPort™ 8.1Gbps 线性转接驱动器](#) 数据表。

**表 2-1. 4 级控制引脚设置**

| 电平 | 设置                                                |

|----|---------------------------------------------------|

| 0  | 选项 1：将 $1k\Omega$ 、5% 连接到 GND。<br>选项 2：直接连接到 GND。 |

| R  | 将 $20k\Omega$ 5% 连接至 GND。                         |

| F  | 悬空（使引脚保持开路状态）                                     |

| 1  | 选项 1：将 $1k\Omega$ 5% 连接至 VCC。<br>选项 2：直接连接到 VCC   |

**表 2-2. TDP142 模式配置**

| I2C_EN | 配置             |

|--------|----------------|

| F      | I2C 在 1.8V 时启用 |

| 1      | I2C 在 3.3V 时启用 |

| 0      | GPIO 模式        |

**表 2-3. TDP142 GPIO 模式配置**

| DPEN/HPDIN | SNOOPENZ/RSVD8 | 配置             |

|------------|----------------|----------------|

| 1          | -              | 启用 DisplayPort |

| 0          | -              | 禁用 DisplayPort |

| -          | 1              | 启用 AUX 监测      |

| -          | 0              | 禁用 AUX 监测      |

### 3 均衡选择

通过用于源端/接收端应用的 TDP142，系统能够通过 DisplayPort 1.4 的发送器电气合规性测试和 DisplayPort 1.4 的接收器抖动容差合规性测试。TDP142 通过应用补偿通道插入损耗的均衡来恢复从源端和接收端传入的数据。

可以根据 TDP142 接收器之前通道（前置通道）的插入损耗量和 TDP142 之后通道（后置通道）的一些插入损耗来设置均衡。在 GPIO 或引脚搭接模式下，通过配置 DPEQ[1:0] 引脚来全局设置每个通道的 EQ 值。在 I2C 模式下，通过对等效寄存器进行编程，可以根据单个通道的损耗独立设置每个通道的 EQ 值。有关均衡值的详细信息，请参阅表 3-1。表 3-2 中给出了典型的 FR4 布线损耗。

表 3-1. TDP142 均衡

| 均衡设置编号 | 所有 DisplayPort 通道 |            |                       |

|--------|-------------------|------------|-----------------------|

|        | DPEQ1 引脚电平        | DPEQ0 引脚电平 | 4.05GHz 时的 EQ 增益 (dB) |

| 0      | 0                 | 0          | 1.0                   |

| 1      | 0                 | R          | 3.3                   |

| 2      | 0                 | F          | 4.9                   |

| 3      | 0                 | 1          | 6.5                   |

| 4      | R                 | 0          | 7.5                   |

| 5      | R                 | R          | 8.6                   |

| 6      | R                 | F          | 9.5                   |

| 7      | R                 | 1          | 10.4                  |

| 8      | F                 | 0          | 11.1                  |

| 9      | F                 | R          | 11.7                  |

| 10     | F                 | F          | 12.3                  |

| 11     | F                 | 1          | 12.8                  |

| 12     | 1                 | 0          | 13.2                  |

| 13     | 1                 | R          | 13.6                  |

| 14     | 1                 | F          | 14.0                  |

| 15     | 1                 | 1          | 14.4                  |

表 3-2. FR4 布线损耗示例

| 4mil 宽 FR4 PCB 布线长度 ( 英寸 ) | 2.5GHz 时的损耗 ( 0.49dB/英寸 ) (dB) | 4.05GHz 时的损耗 ( 0.73dB/英寸 ) (dB) | 5GHz 时的损耗 ( 0.87dB/英寸 ) (dB) |

|----------------------------|--------------------------------|---------------------------------|------------------------------|

| 1                          | 0.5                            | 0.7                             | 0.9                          |

| 2                          | 1                              | 1.5                             | 1.7                          |

| 3                          | 1.5                            | 2.2                             | 2.6                          |

| 4                          | 2                              | 2.9                             | 3.5                          |

| 5                          | 2.5                            | 3.7                             | 4.3                          |

| 6                          | 2.9                            | 4.4                             | 5.2                          |

| 7                          | 3.4                            | 5.1                             | 6.1                          |

| 8                          | 3.9                            | 5.9                             | 7                            |

| 9                          | 4.4                            | 6.6                             | 7.8                          |

| 10                         | 4.9                            | 7.3                             | 8.7                          |

## 4 均衡选择示例

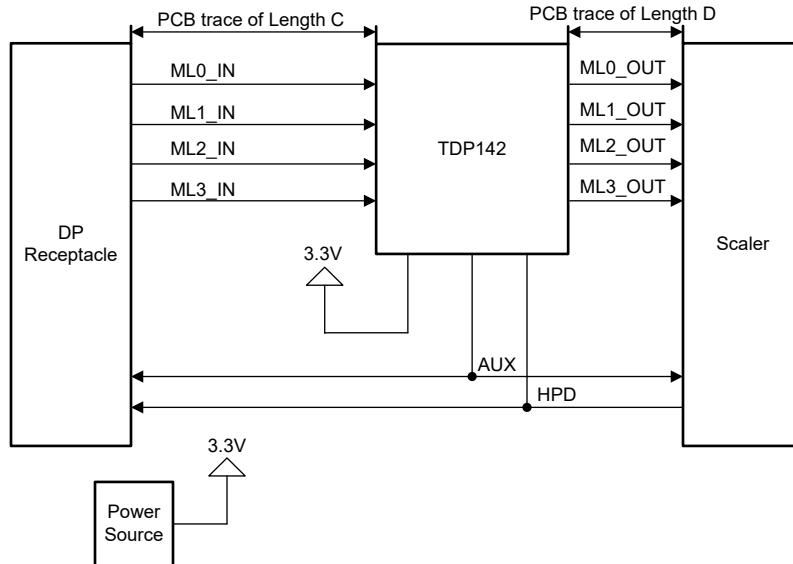

图 4-1. TDP142 接收端均衡示例

本节讨论了一个为不同布线长度选择均衡的示例。图 4-1 展示了 TDP142 的接收端应用示例。以下方法用于为该接收端应用选择均衡值：

- 长度 C 的 PCB 布线 = 8 英寸 FR4 PCB 布线 ( 4.05GHz 时损耗为 5.9dB )。使用的 DPEQ 设置 = 5 号设置 (6.5dB)。

布局质量及 DP 驱动器和接收器质量等其他因素可能需要将均衡设置调整到更高或更低，以获得出色性能。建议使用上述方法，根据系统板布线长度选择初始配置设置。

## 5 AUXP/N 和 SNOOPENZ 配置

TDP142 使用 AUXp 和 AUXn 引脚来监测 AUX。当流量在 DisplayPort 发送端和 DisplayPort 接收端之间遍历时，AUX 监测使 TDP142 能够监控本机 AUX 流量。TDP142 会监测对 DisplayPort 接收端的 DPCD 寄存器 0x00101 (LANE\_COUNT\_SET) 和 0x00600 (SET\_POWER\_STATE) 的本机 AUX 写入。TDP142 会根据写入 LANE\_COUNT\_SET 的值禁用/启用各通道。当 SET\_POWER\_STATE 位于 D3 中时，TDP142 会禁用所有通道。否则，活动通道基于 LANE\_COUNT\_SET 的值。

在 GPIO 模式下，通过搭接 SNOOPENZ 引脚低电平来启用 AUX 监测，可以直接下拉至 GND，也可以使用 1k 下拉电阻器下拉至 GND。在 I2C 模式下，AUX 监测默认启用。可以通过向寄存器 0x13 的位 7 写入 1 来禁用 AUX 监测。

禁用 AUX 监测后，所有四个 DisplayPort 通道均在 GPIO 模式下处于活动状态。在 I2C 模式下，可以通过写入寄存器 0x13 的位 [3:0] 来启用或禁用每个通道。

对于发送端，AUXP 需要有一个  $100\text{k}\Omega$  的下拉电阻器，AUXN 需要有一个  $100\text{k}\Omega$  的上拉电阻器。对于接收端，AUXp 将 1M 上拉至 3.3V，AUXn 将 1M 下拉至 GND。这些电阻器必须位于  $100\text{nF}$  电容器的 TDP142 侧。

对于支持双模 DisplayPort 的应用：SNOOPENZ 引脚必须通过 SN74AHC125 等缓冲器连接到 DisplayPort 插座上的 CONFIG1。需要使用缓冲器的原因是，当双模适配器插入 DisplayPort 插座时，SNOOPENZ 引脚上的内部下拉电阻太强，无法寄存有效的 VIH。

## 6 布局指南

需要使用以下布局指南将高速 DisplayPort 信号路由至 TDP142 以及从 TDP142 路由高速 DisplayPort 信号。

- INDP 和 OUTDP 对必须采用受控  $100\ \Omega$  差分阻抗 ( $\pm 10\%$ ) 进行布线。

- 使差分对远离其他高速信号。

- 对内布线需要保持在 5mil 以内。

- 根据 [DisplayPort 设计指南](#)，DisplayPort 通道对间路由需要保持在 2 个单位间隔以内。

- 差分对长度匹配需要在不匹配位置附近。

- 每对需要至少间隔信号布线宽度的 3 倍。

- 需要尽量减少使用弯曲的差分布线。使用弯曲时，左右弯曲数量需要尽可能相等，弯曲角度需要  $\geq 135^\circ$ 。这样可以尽可能减少由弯曲引起的任何长度不匹配，并尽可能降低弯曲对 EMI 造成的影响。

- 在同一层布线所有差分信号对。

- 尽量减少过孔数量，建议将过孔数量保持在 2 个或以下。

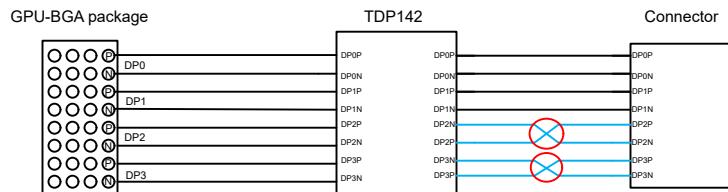

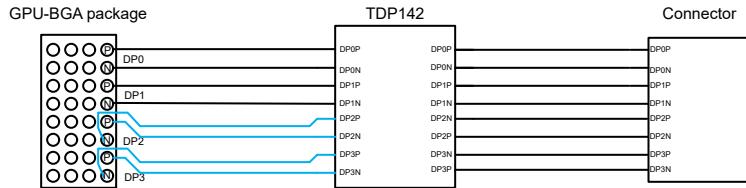

- 由于器件输出引脚和连接器之间的接线不匹配，布局可能会在 OUTDP2 和 OUTDP3 上出现信号交叉。其中一种设计是当 GPU 采用 BGA 封装时，在器件的输入端进行极性交换。这样可以尽量减少所使用的 VIAS 的数量。请参阅 [图 6-1](#) 和 [图 6-2](#)。

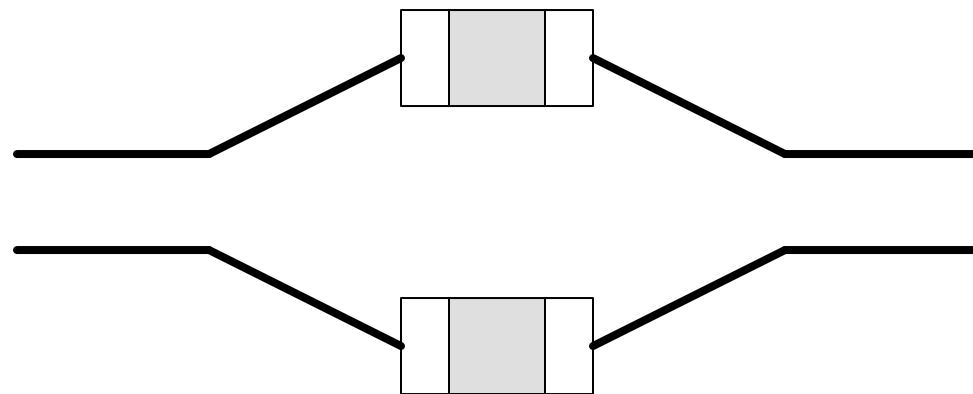

图 6-1. 输出上的信号交叉处理

图 6-2. INDP2 和 INDP3 极性交换

- 在靠近地平面的层上保留差分布线。

- 请勿在任何拆分上平面布线差分对。

- 如果使用穿孔连接器，则将高速信号排布在连接器的另一侧，使连接器引脚不会在传输线路上产生残桩。

- 测试点需要串联并对称放置，以避免阻抗不连续。

## 6.1 GND 拼接

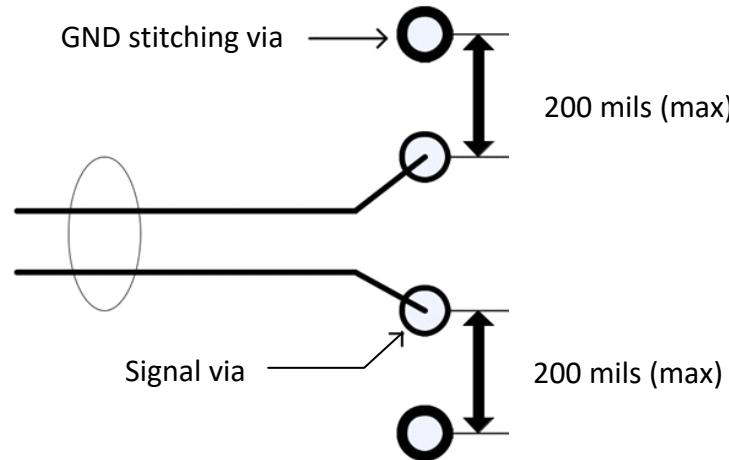

整个高速信号布线从发起到终止需要一直使用相同的 GND 参考平面。如果无法维持相同的 GND 参考平面，则将两个 GND 平面的过孔拼接在一起，以确保获得连续的接地和均匀的阻抗。在信号转换过孔周围的 200mil ( 中心距 , 越靠近越好 ) 内对称地放置这些拼接过孔。有关 GND 拼接过孔的示例，请参阅图 6-3。

图 6-3. GND 拼接过孔示例

## 6.2 交流耦合电容器

放置交流耦合电容器时，建议的元件尺寸为 0201。使用的最大元件尺寸需要为 0402。布局期间，交流耦合电容器需要靠近器件的发送器引脚并实现对称放置，以确保出色的信号质量并最大限度地减少反射。将交流耦合电容器尽可能靠近器件放置或放置在发送器侧。图 6-4 展示了如何确保交流耦合电容器布局对称性。

图 6-4. 交流耦合电容器布局对称性示例

### 备注

向高速布线添加测试点可能导致阻抗不连续，从而对信号性能产生负面影响。如果使用测试点，需要将测试点串联并对称放置。这些测试点的布置方式不得使差分对上产生残桩。

## 6.3 布局示例

图 6-5. 布局示例

## 7 总结

本文档提供了在系统中设置和配置 TDP142 所需的工具。如需更多信息，请参阅本文档以及 [TDP142 DisplayPort™ 8.1 Gbps 线性转接驱动器](#) 和 [TDP142 原理图检查清单](#)。

## 8 参考资料

- 德州仪器 (TI) , [TDP142 DisplayPort™ 8.1Gbps 线性转接驱动器](#) 数据表

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#))、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025 , 德州仪器 (TI) 公司

最后更新日期 : 2025 年 10 月