## Technical White Paper

# 使用热增强型封装提高高环境温度环境下的热性能

Charles Wang

## 摘要

在当今的通信设备和企业市场中，为了满足 SoC 和 FPGA 不断发展而带来的需求，对功率的要求不断提高。这一趋势推动了直流/直流降压开关稳压器和功率级的额定功率提高，以及有限布板空间中的密度增加。在转换过程，直流/直流稳压器会因功率损耗而自然会产生热量。如果在配备源天线系统、基带单元或小型蜂窝基站等设施的高环境温度中运行，还会导致器件内不可避免地出现温度上升。降压转换器和功率级的结温必须在供应商规定的结温范围内，才能保持在安全工作区 (SOA) 内并防止相邻器件发热。随着器件结温随环境温度升高，给定器件安全输出所需的电流量降低。对于高环境温度不可避免但功率要求较高的系统而言，这属于重大限制。因此，必须优化散热性能，从而减少散热限制并提高整体系统效率。

本技术白皮书介绍了常见的散热方法、什么是热增强型封装 (TEP)，以及 TEP 如何在几乎没有缺点的情况下改善散热。后续讨论将聚焦于如何通过现有封装进行散热、PCB 布局如何影响散热，以及 TEP 如何开启 IC 散热的新方式。

## 内容

|                 |   |

|-----------------|---|

| 1 了解热性能.....    | 2 |

| 2 散热方法.....     | 2 |

| 2.1 可路由引线框..... | 3 |

| 3 热增强型封装.....   | 4 |

| 4 SOA 比较.....   | 6 |

| 5 结论.....       | 7 |

## 商标

所有商标均为其各自所有者的财产。

## 1 了解热性能

直流/直流降压转换器和功率级效率与功率损耗成反比。最大限度降低功率损耗是最大限度提高系统效率的关键所在。功率损耗的两个主要来源包括控制器的开关损耗以及功率级内高侧和低侧 MOSFET 的传导损耗。随着输出电流增加，传导损耗对整体功率耗散的影响增大，而开关损耗的影响减小。

传导损耗表现为热能耗散，这会导致器件结温升高，因而与热性能直接相关。高环境温度会导致额外的结温升高，使安全运行的余地更小。

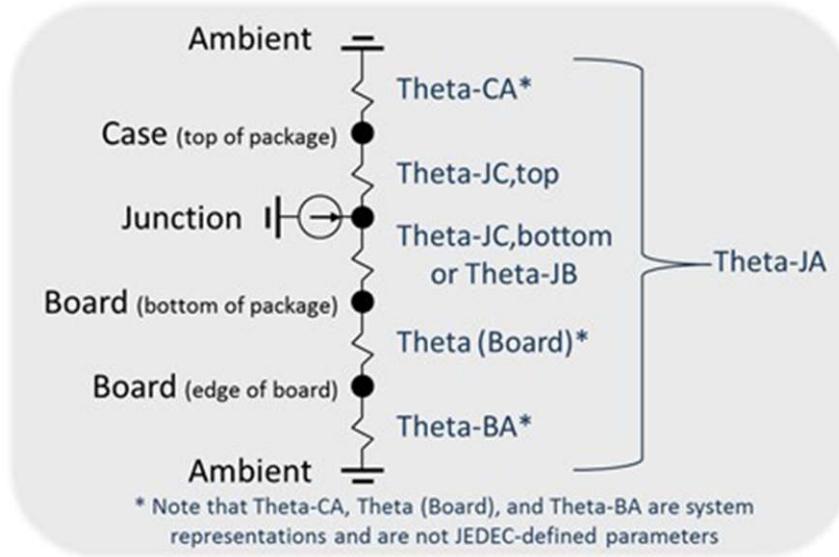

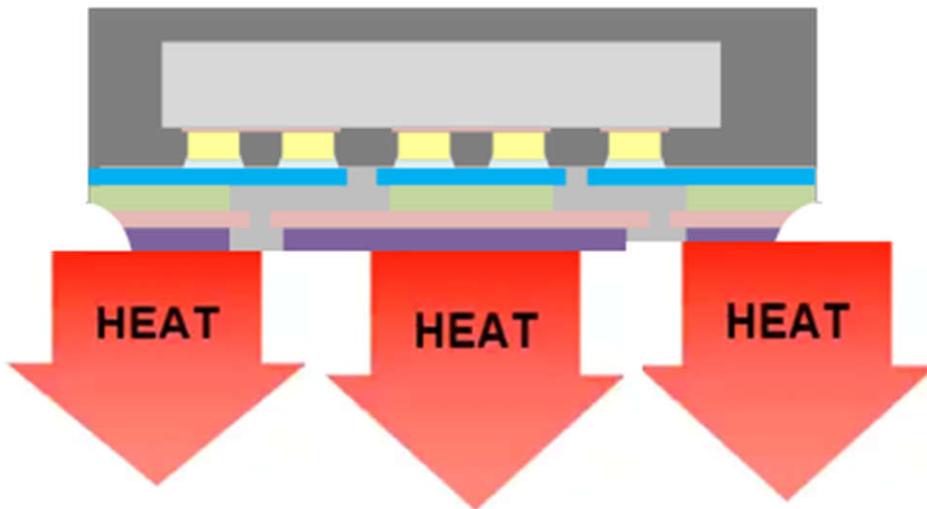

结至环境热阻  $R_{\theta JA}$  用于测量 FET 结温与周围环境之间的热阻，是最常用的热性能指标。如 图 1-1 所示，它可以分为两部分：结温通过器件顶部表面到周围环境所产生的向上热阻，以及结温依次通过器件底部、PCB 电路板，最后到周围介质所产生的向下热阻。

图 1-1.  $R_{\theta JA}$  断开

散热中影响最大的部分是通过封装底部散热，这正是当今大多数散热方法都侧重于 PCB 布局的原因。然而，优化顶部散热也可以降低总体  $R_{\theta JA}$ 。本文档说明了如何为器件使用热增强型封装，从而将顶部的结至外壳  $\theta_{JC}(top)$  降低至接近零。

需要注意的是，尽管在许多数据表中， $R_{\theta JA}$  为设定值，但该值是按照标准布局测得的，通常遵循 JEDEC 标准。虽然硅芯片设计本身会影响热性能，但 PCB 设计和封装技术对器件散热效率的影响要大得多。

## 2 散热方法

为了解决通过器件底部来优化  $R_{\theta JA}$  的问题，最常见的方法是高效管理整个 PCB 中的热流，以实现均匀流动。充分扩大整个 PCB 中的导电区域是充分提高散热能力的关键所在，包括充分增加布线厚度、层厚度和电路板尺寸。

$V_{OUT}$ 、GND、SW 和  $V_{IN}$  都是降压转换器的节点，建议增加布线厚度和覆铜宽度。增加 PCB 内的层数并充分增加层厚是另一种充分增大铜面积的方法。例如，与 4 层电路板相比，6 层电路板用于散热的铜面积更大。使用较厚的电路板层也能达到此效果。

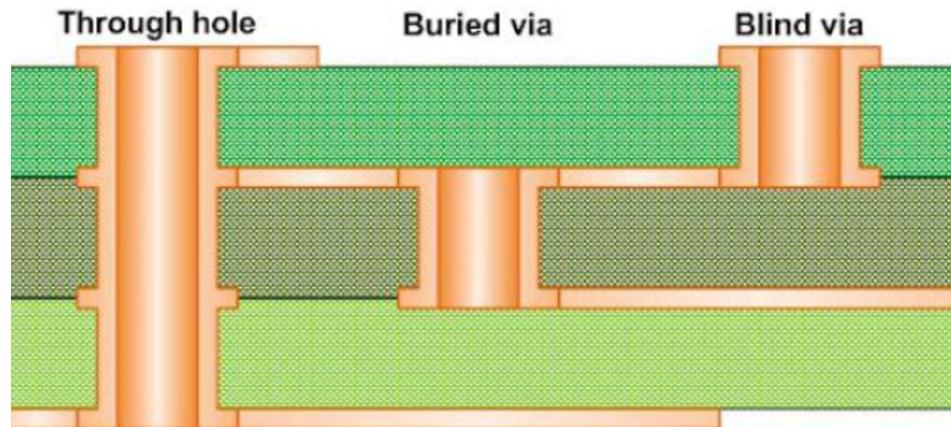

若要充分利用多层的优势，还需要使用正确的散热孔。如 图 2-1 中所示，连接外层和内层的盲孔可以将散热限制在电路板的一侧。连接内层的埋孔可以将散热限制在电路板内层，而通孔会穿过所有 PCB 层，使热量从顶部、内层和电路板底部散发出去。

图 2-1. 散热孔类型

充分增加传导表面积可以接触更多环境空气，从而实现更好的散热。

## 2.1 可路由引线框

虽然优化 PCB 布局对整体系统散热影响的非常大，但也必须仔细选择 IC 本身的封装，以优化散热性。封装内的引线框结构对于将热量从裸晶传导至 PCB 及其周围环境有着重大影响。

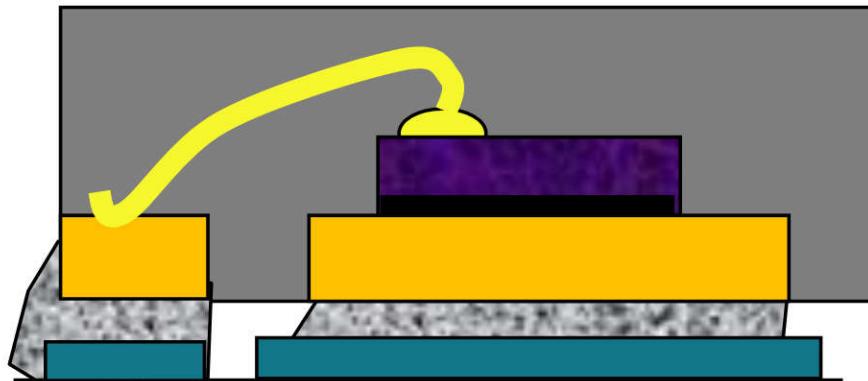

封装技术取得的最新进展使得封装的散热效率得以大幅提高。在如 图 2-2 所示的传统引线键合 QFN 封装中，将裸晶连接到外部引脚的键合线会增加电阻，从而造成额外的传导损耗。由于与 PCB 的接触有限，这种传导损耗会在封装内产生热量，而这种热量不会以最佳方式从封装外散发出去。

图 2-2. 引线键合 QFN 封装

如 [图 2-3](#) 所示，HotRod™ QFN 封装指的是翻转芯片并使用铜柱和金或锡焊料将引脚直接放置在引线框上。这消除了对键合线的需求，从而降低传导损耗并增加导体与 PCB 的接触。然而，单层引线框中的引脚排列设计通常会限制接地焊盘尺寸，导致封装内的热传导面积减小。

图 2-3. HotRod QFN 封装

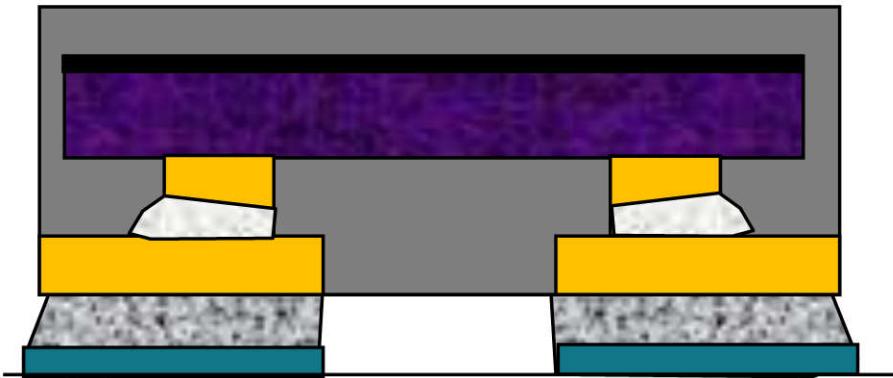

为了实现更灵活的引脚排列设计，可路由引线框 QFN（最新的封装技术）将引线框分成三层基板，并采用内层布线连接，如 [图 2-4](#) 所示。如此以来，为采用此封装的大多数器件在引线框的最底层上设计出最大的接地焊盘面积便可成为现实，从而与 PCB 进行更好的热传导接触。

图 2-4. 可路由引线框封装

### 3 热增强型封装

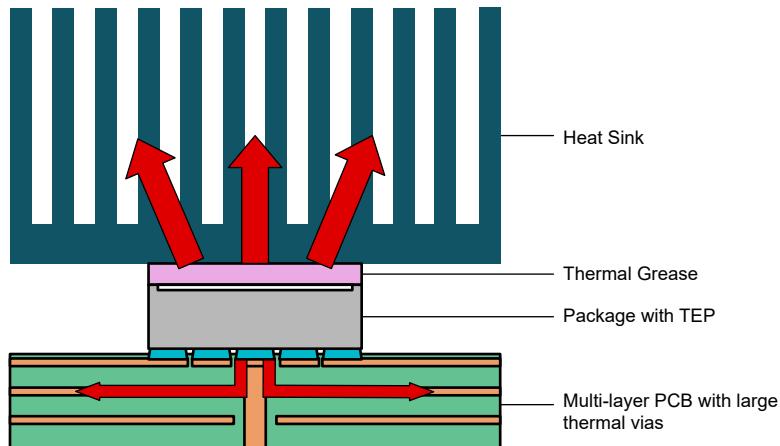

为了通过封装顶部进行冷却，通常使用散热器将热量从 IC 封装传递到周围环境。电路板设计，尤其是包含资源密集型计算芯片组的电路板设计，通常选择在整个电路板上安装散热器，以最大限度地扩大电路板接触流体介质的表面积。流体介质可以是环境静态空气、环境气流，也可以是液体介质（例如水、制冷剂或油）。[图 3-1](#) 直观展示了元件放置情况的图表。

图 3-1. 带散热器的转换器

在器件顶部涂抹热膏，以均匀地覆盖传导表面。然后，连接散热器，以最大限度地增加用于散热的表面积。由于大多数电源管理 IC 都是使用模塑化合物超模压封装而成的，因此需要对封装技术进行微调，以优化散热器的热传递功能。

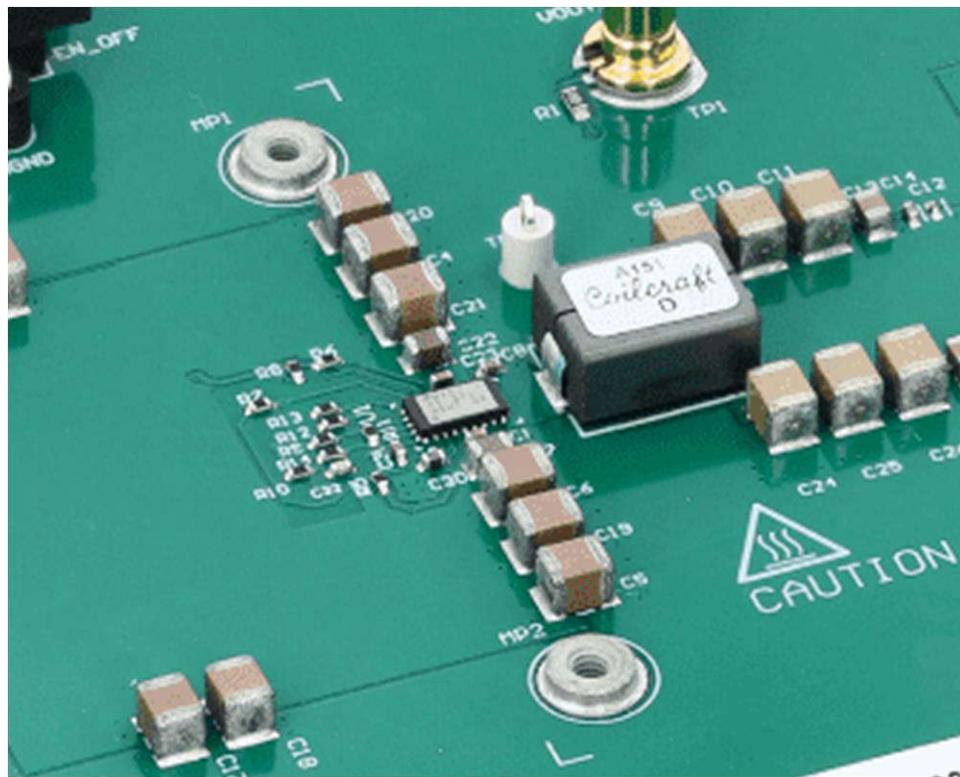

热增强型封装 (TEP) 技术使内部裸晶在封装的顶部露出来，以便直接接触热膏和散热器，从而通过封装的顶部实现更好的热传导。TEP 指采用选择性“薄膜辅助”模具工艺的封装技术，在成型过程中使用一层薄膜来防止模塑材料流到裸晶上。工艺流程几乎与标准超模压工艺相同，只是不需要利用顶部模塑化合物即可让裸晶露出来。图 3-2 展示了从 TPS543B25TEVM 的顶部拍摄的 TEP 降压转换器 TPS543B25T 照片。

图 3-2. TPS543B25T 电路板照片

去除顶部模塑化合物后，TPS543B25T 的  $\theta_{JC}(\text{top})$  为  $0.2^{\circ}\text{C}/\text{W}$ ，比同一器件 TPS543B25 的超模压版本降低了  $0.6^{\circ}\text{C}/\text{W}$ 。在应用散热器的情况下，这会导致总热阻降低，如表 3-1 所示。

表 3-1. TPS543B25T 与 TPS543B25 的  $R_{\theta JA}$  比较

| 器件                            | $R_{\theta JA}$ (°C/W) |

|-------------------------------|------------------------|

| TPS543B25                     | 12.3                   |

| 带散热器的 TPS543B25               | 12.16                  |

| 不带散热器的 TPS543B25T             | 11.8                   |

| 带散热器的 TPS543B25T              | 10.2                   |

| 带散热器、有气流的 TPS543B25T (200LFM) | 7                      |

与不带散热器、采用标准封装的器件相比，带散热器、采用 TEP 的器件可以将热阻降低约 2.1°C/W。如果应用了气流，则热阻会进一步降低 3.2°C/W。

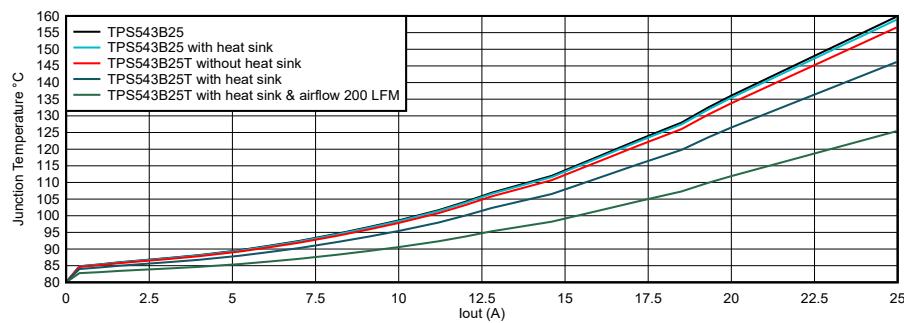

当器件处于负载状态时，较低的热阻可使温升显著降低，尤其是在电流较高的情况下。图 3-3 显示的是在 80°C 环境温度 ( $T_A$ ) 下，TPS543B25T 和 TPS543B25 在负载范围内的结温 ( $T_J$ )。两者都是在 TPS543B25EVM 上进行的测试。通过将测得的 PG 二极管功率损耗乘以热阻，可以估算出温升。 $T_J$  的计算方法是将温升与 80°C  $T_A$  相加。请注意，TPS543B25 和 TPS543B25T 的额定最大结温为 150°C。

图 3-3. TPS543B25T 与 TPS543B25 在负载范围内的  $T_J$

在满载状态下，应用了散热器的 TPS543B25T 的  $T_J$  比 TPS543B25 低 13.7°C，并且在有气流的情况下可以再额外降低 20.8°C。

## 4 SOA 比较

负载范围内较低的结温可拓宽给定器件的 SOA，从而在高环境温度下实现更高的电流输出。

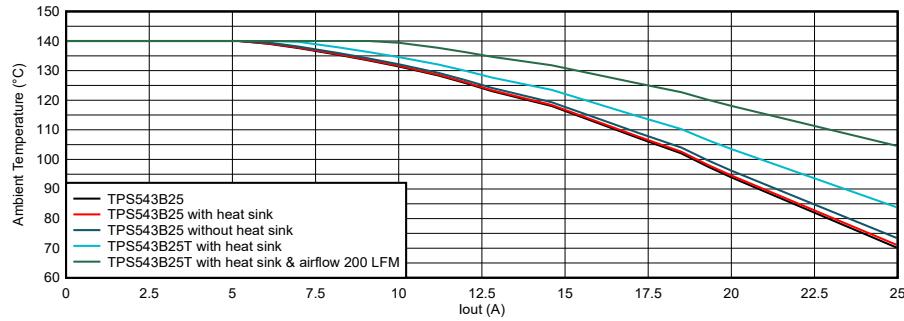

图 4-1 展示了 TPS543B25 降压转换器的 SOA 曲线与 TPS543B25T 的 SOA 曲线。

图 4-1. TPS543B25T 与 TPS543B25 的 SOA 曲线比较

在高于 70°C 的  $T_A$  条件下，标准封装 TPS543B25 无法满载输出。在超模压封装中使用散热器所带来的好处也是微乎其微。在高达 83°C  $T_A$  和高达 105°C  $T_A$  的条件下，通过增加气流，带有散热器的 TPS543B25T 可安全地满载输出。

由于 TEP 在 SOA 中具有优势以及结温会随着输出电流的增加而升高，我们也能够根据这些数据推断出，在更高电流 (>25A) 的器件中，尤其是当环境温度更高 (环境温度超过 85°C) 时，TEP 将会更具优势。

请注意，未使用散热器时，**TPS543B25** 和 **TPS543B25T** 的 SOA 之间没有显著差异。外露裸晶只能通过散热器将热量传导至环境中。此外，无论是否带散热器，标准封装的 SOA 之间也没有显著差异，从而证实了顶部模塑化合物会阻碍散热。

## 5 结论

受结温升高影响，高环境温度会显著限制电信和数据中心应用中直流/直流降压转换器和功率级的功率输出。优化散热是充分提高整体系统效率和优化成本的关键所在。热增强型封装 (TEP) 为设计人员提供了一种通过外露裸晶来将热量散发到周围环境中的新方法。此封装方法与通过 PCB 和引线框进行散热的所有传统方法相结合，共同组成针对热性能进行优化全面的综合解决方案。

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，TI 对此概不负责。

TI 提供的产品受 [TI 的销售条款](#) 或 [ti.com](#) 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址：Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

版权所有 © 2025, 德州仪器 (TI) 公司