# VR 稳定性判定方法基于

Nison Wang

North West China OEM Team

## 摘要

主板供电是服务器中非常重要的部分，它负责将电源模块 PSU 输出的 12V 电压转化为 CPU、内存、PCH、BMC 及其他电路所需的适当电压<sup>[1]</sup>。这部分电路由多个不同的 VR 电路组成，以为不同的设备提供不同的电压。VR 电路一般采用 DCAP+控制架构，具有输出精度高、动态均流性能好、瞬态响应快的优点<sup>[2]</sup>。

本文首先介绍了 DCAP+控制架构的基本原理，然后提出了一种简单实用的稳定性判定方法，并通过实验进行验证。本文同步验证了波特图对于 DCAP+控制架构稳定性判定的局限性，最后研究了环路稳定性对 IMON 和 OCP 的影响，并提出了 OCP 阈值设置方法。

## 目录

|                           |    |

|---------------------------|----|

| 1 DCAP+控制架构的基本原理 .....    | 1  |

| 2 DCAP+稳定性判定方法及实验验证 ..... | 3  |

| 3 小结 .....                | 10 |

| 参考文献 .....                | 10 |

## 图例

|                                |   |

|--------------------------------|---|

| 图 1 DCAP+控制架构框图 .....          | 2 |

| 图 2 DCAP+环路波形 .....            | 3 |

| 图 3 瞬态响应波形 .....               | 4 |

| 图 4 环路 1 和环路 2 的 Code 设置 ..... | 4 |

| 图 5 环路 1 产生的瞬态响应 .....         | 5 |

| 图 6 环路 2 产生的瞬态响应 .....         | 5 |

## 1 DCAP+控制架构的基本原理

TI DCDC 的控制模式主要有 DCAP, DCAP2, DCAP3, DCAP4 和 DCAP+等。其优劣势对比如下<sup>[3]</sup>:

表 1 控制模式的优劣势对比

|      | 优势                                  | 劣势                                         |

|------|-------------------------------------|--------------------------------------------|

| DCAP | 如果输出电容的 ESR 足够，无需外部环路补偿；对负载变化的响应比较快 | 准固定开关频率，SW 抖动较大；输出电压需要纹波分量作为反馈，因此需要输出电容具有一 |

|       |                                                         |                                                      |

|-------|---------------------------------------------------------|------------------------------------------------------|

|       |                                                         | 定的 ESR 或加外部纹波注入电路；对输出噪声敏感； $V_{FB}$ 纹波产生的偏移电压会降低输出精度 |

| DCAP2 | 相较于 DCAP，可以使用陶瓷输出电容来实现低纹波，无需外部纹波注入电路                    | 模拟斜坡产生的偏移电压会降低输出精度                                   |

| DCAP3 | 相较于 DCAP2，应用了新的斜坡生成电路，采样和保持电路可以消除模拟斜坡引入的偏移电压；负载调整率有所提高  | 在输出电压电压较高时，瞬态响应较差                                    |

| DCAP4 | 相较于 DCAP3，在整个输出电压范围内实现最佳瞬态响应，无需调整斜坡设置或外部补偿              | 未集成 DC load line (DCLL) 功能                           |

| DCAP+ | 集成了误差放大器，输出电压精度高；真正的电流模式控制，可实现动态电流共享；瞬态响应非常快速；可以实现 DCLL | 需要外置或内置电流检测电路                                        |

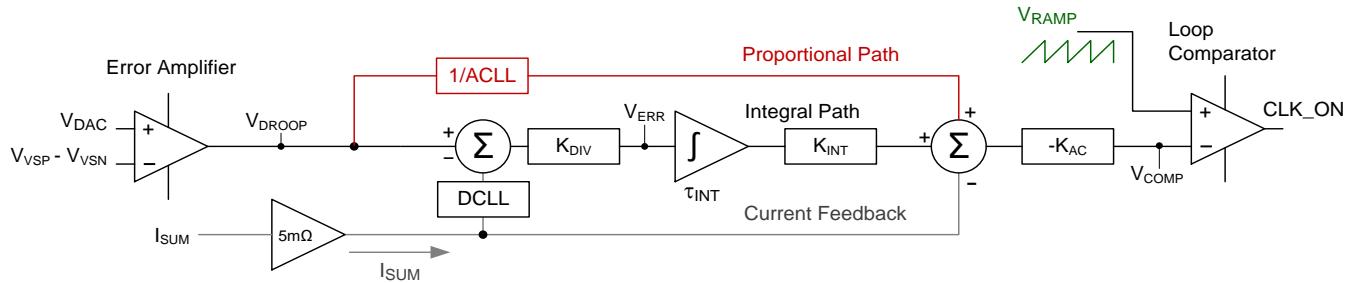

图 1 为 DCAP+控制架构框图<sup>[4]</sup>。总电感电流  $I_{SUM}$  是以电压或者电流的形式（取决于 Power Stage 是电压型还是电流型）从 Power Stage 传递给 VR Controller，但是在 VR Controller 内部都会转变为电压信号，由于  $I_{SUM}$  与真实的总电感电流有  $5\text{mV/A}$  的关系，因此在 VR Controller 的控制环路中，需要把  $I_{SUM}$  除以  $5\text{m}\Omega$  才能得到真实的总电感电流。

图 1 DCAP+控制架构框图

Intel 规定 VR controller 必须具有 DC load line (DCLL) 的功能，这样当负载电流较低时，VR 电路的输出电压高；随着负载电流的增大，VR 电路的输出电压线性下降，这样处理有两个主要优点：

- (1) 当负载电流较高时，降低输出电压，可以降低系统的功耗。

- (2) 可以增加负载瞬态变化时允许的下冲 (Undershoot) 和过冲 (Overshoot)。

$V_{COMP}$  信号由三个信号路径的总和生成，然后由交流增益  $K_{AC}$  缩放：

- **比例路径：**误差放大器从  $V_{DAC}$  设置的输出电压参考中减去检测到的实际输出电压 ( $V_{VSP}-V_{VSN}$ )，产生  $V_{DROOP}$ ，增益由交流负载线 (ACLL) 设置。降低 ACLL 会增加比例路径增益，从而提供更快的瞬态响应，但是将 ACLL 设置得过低会导致相位裕度不足。

- **积分路径：**将  $V_{DROOP}$  与理想压降 ( $I_{SUM} \times DCLL$ ) 进行比较，生成误差电压  $V_{ERR}$ 。积分器调整  $V_{COMP}$  的设定点，将输出电压误差降至零。积分环节具有极高的直流增益，使电源具有出色的输出精度和 DCLL。积分时间常数  $\tau_{INT}$  影响瞬态响应后输出电压的稳定时间，增加  $\tau_{INT}$  可提高相位裕度。积分路径增益  $K_{INT}$  用于设置积分路径的增益。

- **电流反馈：**总相电流  $I_{SUM}$  直接用于生成  $V_{COMP}$ ，并在积分路径中用于设置 DCLL。

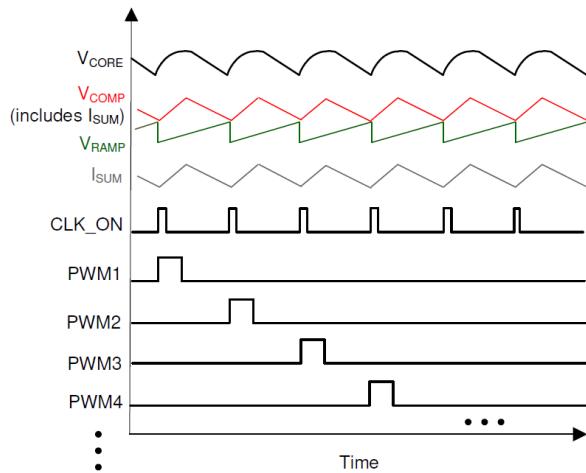

补偿斜坡信号  $V_{RAMP}$  的斜率与相数和设定的开关频率成比例。当  $V_{RAMP}$  和  $V_{COMP}$  信号相交时，比较器就会触发一个新脉冲，新脉冲会按照 VR Code 中设定好的触发顺序分配给每一相，如图 2 所示<sup>[4]</sup>。每一相的导通时间不是一成不变的，VR controller 会根据输出电压设定点、开关频率设定点和均流误差自动调整每个相的导通时间。

图 2 DCAP+环路波形

DCAP+控制架构的开关频率是动态变化的，因此可以实现快速的负载瞬态性能。当负载突然增大时，输出电压立即下降，环路快速调整  $V_{COMP}$  以使 PWM 脉冲更频繁地触发，从而导致电感电流快速增加，当电感平均电流达到新的负载电流时，电路进入稳态工作，PWM 开关频率恢复到稳态频率。当负载突然释放时，输出电压立即上升，环路快速调整  $V_{COMP}$  以使 PWM 脉冲延迟发出，直到电感平均电流达到新的负载电流。然后电路进入稳态工作，PWM 开关频率恢复到稳态频率。

## 2 DCAP+稳定性判定方法及实验验证

### 2.1 DCAP+稳定性判定方法

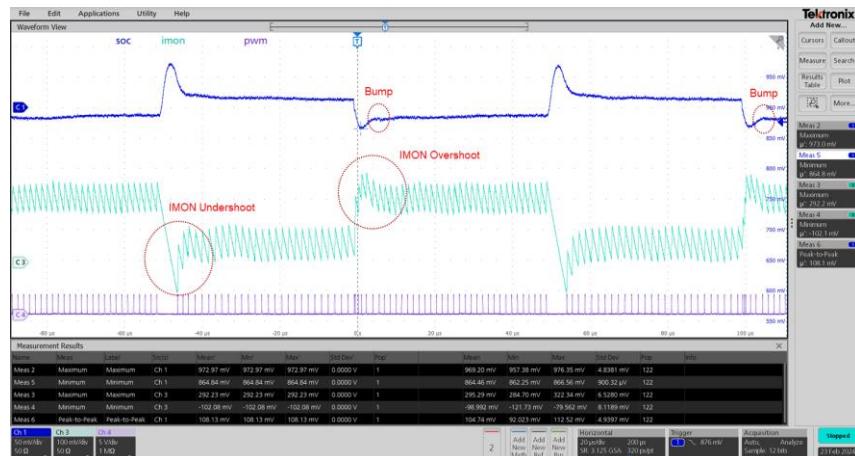

本文建议用测量瞬态响应的方法去判断 DCAP+控制架构的稳定性，图 3 为典型的瞬态响应波形<sup>[5]</sup>，可以发现在瞬态恢复的过程中有可能会产生 Bump，因此稳定性判定标准为：只要 Bump 的数量为 0，就可以认为 VR 电源是稳定的。瞬态响应的测试条件为：负载阶跃和负载变化率参考 Intel 或者 AMD 最严苛的要求，负载占空比选择 50%，负载扫描频率选择 1kHz~10kHz 即可。

图 3 瞬态响应波形

## 2.2 稳定性实验验证

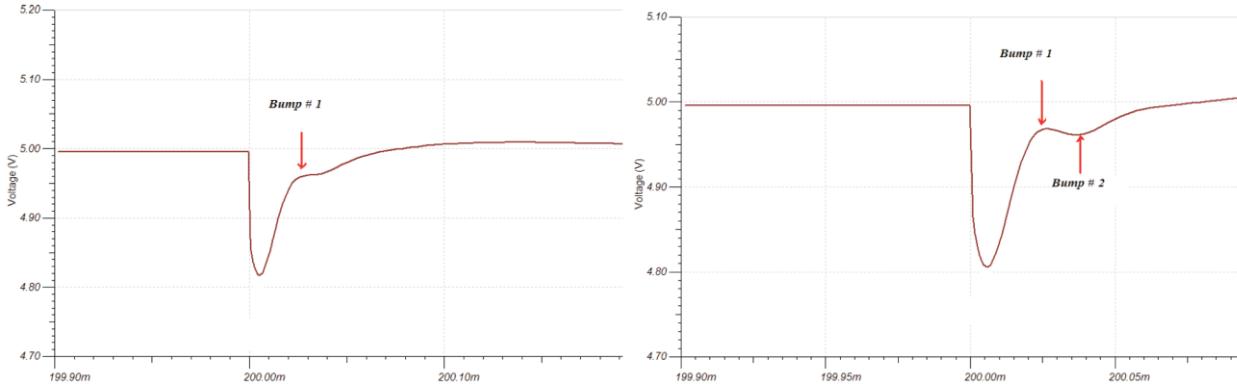

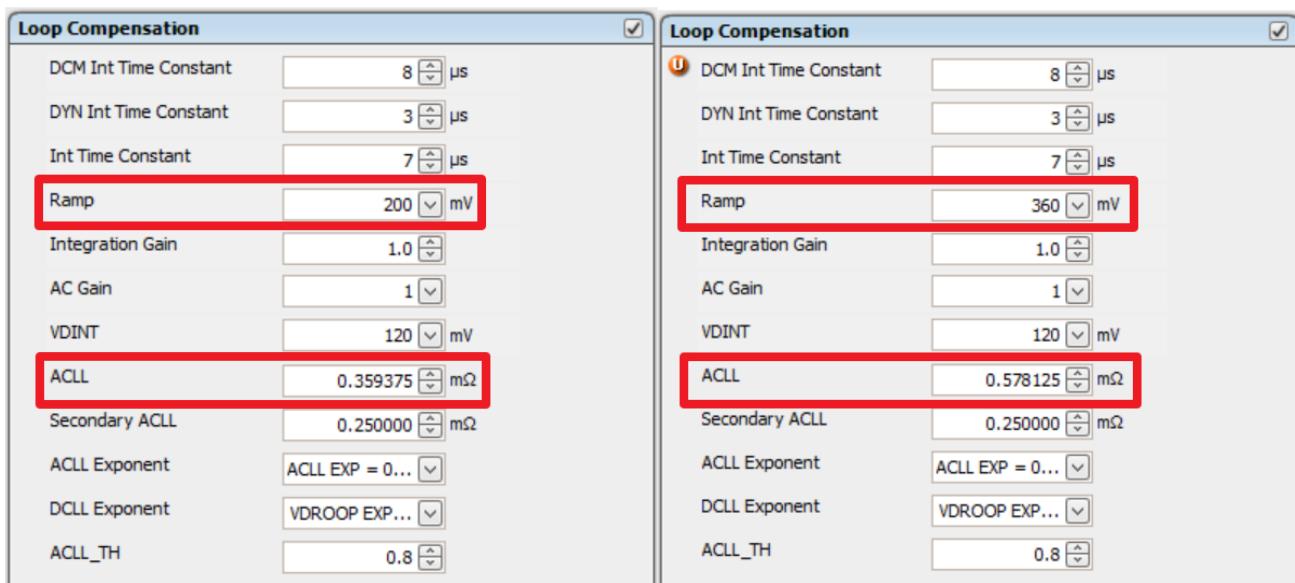

基于 AMD SP5 Genoa 平台的 SOC Rail (3 Phase, TDC 为 105A, EDC 为 130A) 进行验证, VR Controller 为 TPS536C5, Power Stage 为 CSD95410。瞬态响应测试条件为: 负载变化时间 1000ns, 电流阶跃 85A-130A-35A, 占空比 50%, 负载频率 10kHz。图 4 为两套环路参数, 左图为环路 1, 右图为环路 2, 其只有 Ramp 和 ACLL 有区别。根据图 1, Ramp 与 Jitter 息息相关, Ramp 越大, 环路抗噪声能力越强, Jitter 越小, 环路越稳定, 但是 overshoot 可能会变大。ACLL 作用于比例路径, 降低 ACLL 会增加比例路径增益, 从而提供更快的瞬态响应, 但是将 ACLL 设置得过低会导致相位裕度不足, 稳定性变差。实测发现: 如果选择环路 1 的配置, 在做如上瞬态响应测试时很容易触发 OCP, 原因是负载突然增加时, 响应速度过快, PWM 脉冲密集发出, 导致电感瞬时电流急剧增加从而触发 OCP, 说明此时环路是不稳定的, 此时的瞬态响应波形如图 5 所示, CH1 为输出电压波形, CH3 为某一个 Phase 的 IMON 波形, CH4 为此 Phase 的 PWM 波形, 发现输出电压确实会有一个 Bump, 也会有比较大的 IMON Overshoot。因此必须对环路参数进行优化以消除 Bump, 环路 2 为优化后的参数, 实测发现不会触发 OCP, 此时的瞬态响应如图 6 所示, 瞬态响应非常平滑, 没有 Bump。因此证明本文提出的稳定性判据合理。

图 4 环路 1 和环路 2 的 Code 设置

图 5 环路 1 产生的瞬态响应

图 6 环路 2 产生的瞬态响应

### 2.3 波特图的局限性

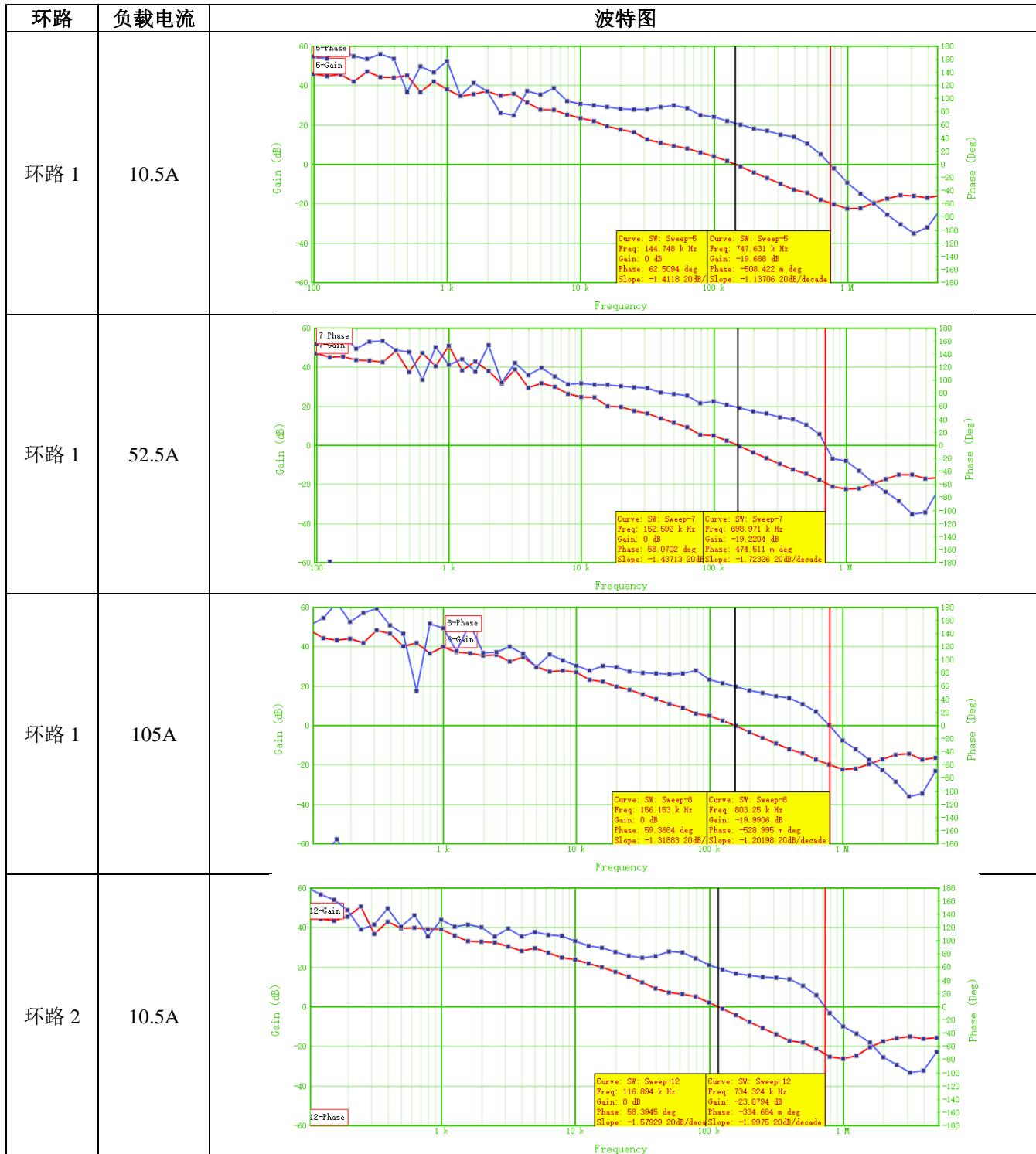

波特图是常用的小信号线性控制环路分析工具，但是 DCAP、DCAP2、DCAP3、DCAP4 和 DCAP+从根本上来说都是非线性、半滞后、大信号控制架构，虽然可以将受控交流信号源添加到反馈环路中，并测量反馈输入点和输出电压点的幅度比（增益）和时间滞后（相位）响应，以生成波特图，但是测量结果可能受信号注入技术、信号电平和具体的 DCAP 控制模式影响，参考价值不大，因此本文才建议使用上一章节的大信号分析技术来代替这些线性小信号分析工具<sup>[6]</sup>。

基于 AMD SP5 Genoa 平台的 SOC Rail，对环路 1 和环路 2 的波特图进行测量，如表 2 所示，其相位裕度、幅值裕度和穿越频率总结如表 3。可以发现：如果按照传统的稳定性判定标准，那么两个环路都是稳定的。且在不同负载条件下，环路 2 的相位裕度比环路 1 要小，而且穿越频率比环路 1 要大，这说明环路 1 的响应速度又快又稳定，这显然是不符合逻辑的，因此证明了波特图在判断 DCAP+控制架构的稳定性上具有一定的局限性。

**表 2 不稳定环路和稳定环路的波特图对比**

表 3 不稳定环路和稳定环路的波特图结果对比

| 负载电流  | 对比项      | 环路 1 | 环路 2 |

|-------|----------|------|------|

| 10.5A | 相位裕度/deg | 63   | 58   |

|       | 幅值裕度/dB  | 20   | 24   |

|       | 穿越频率/kHz | 145  | 117  |

| 52.5A | 相位裕度/deg | 58   | 48   |

|       | 幅值裕度/dB  | 19   | 24   |

|       | 穿越频率/kHz | 153  | 117  |

| 105A  | 相位裕度/deg | 59   | 51   |

|       | 幅值裕度/dB  | 20   | 24   |

|       | 穿越频率/kHz | 156  | 119  |

## 2.4 稳定性对 IMON 和 OCP 的影响

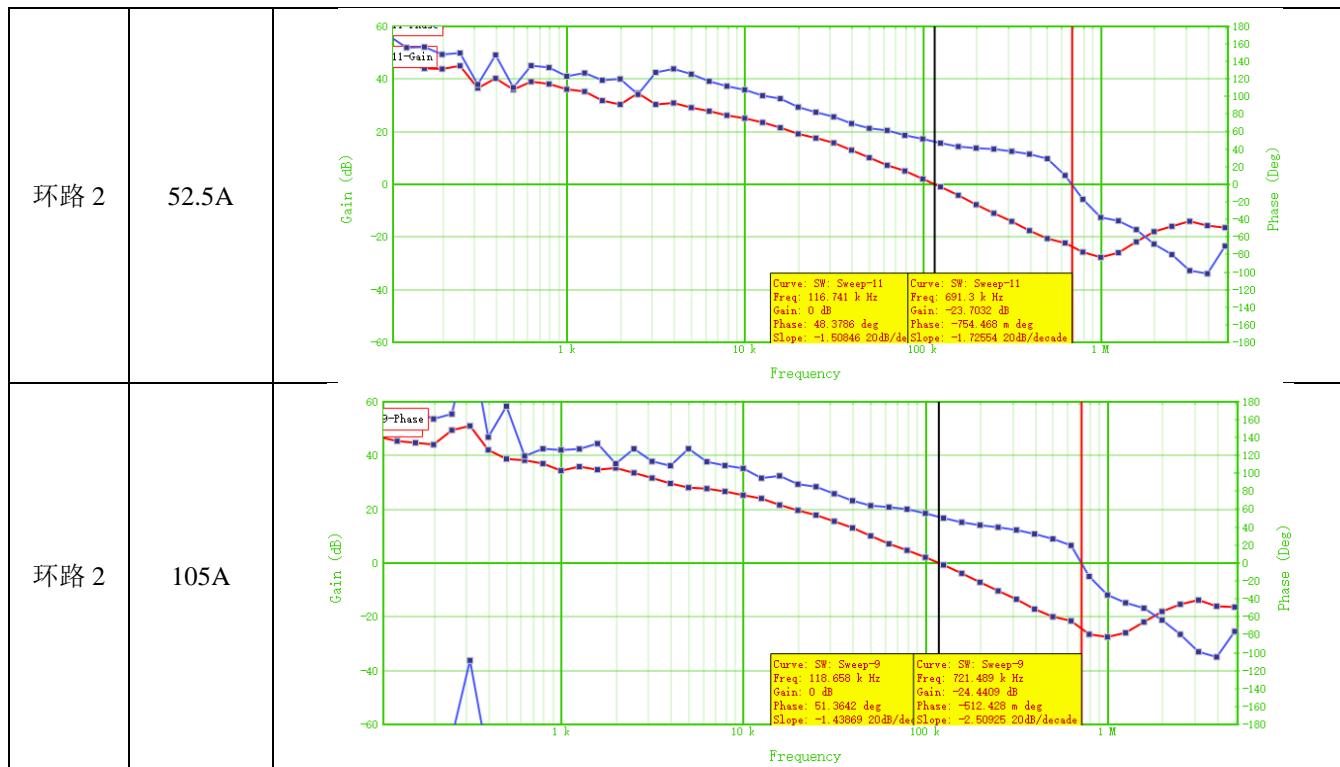

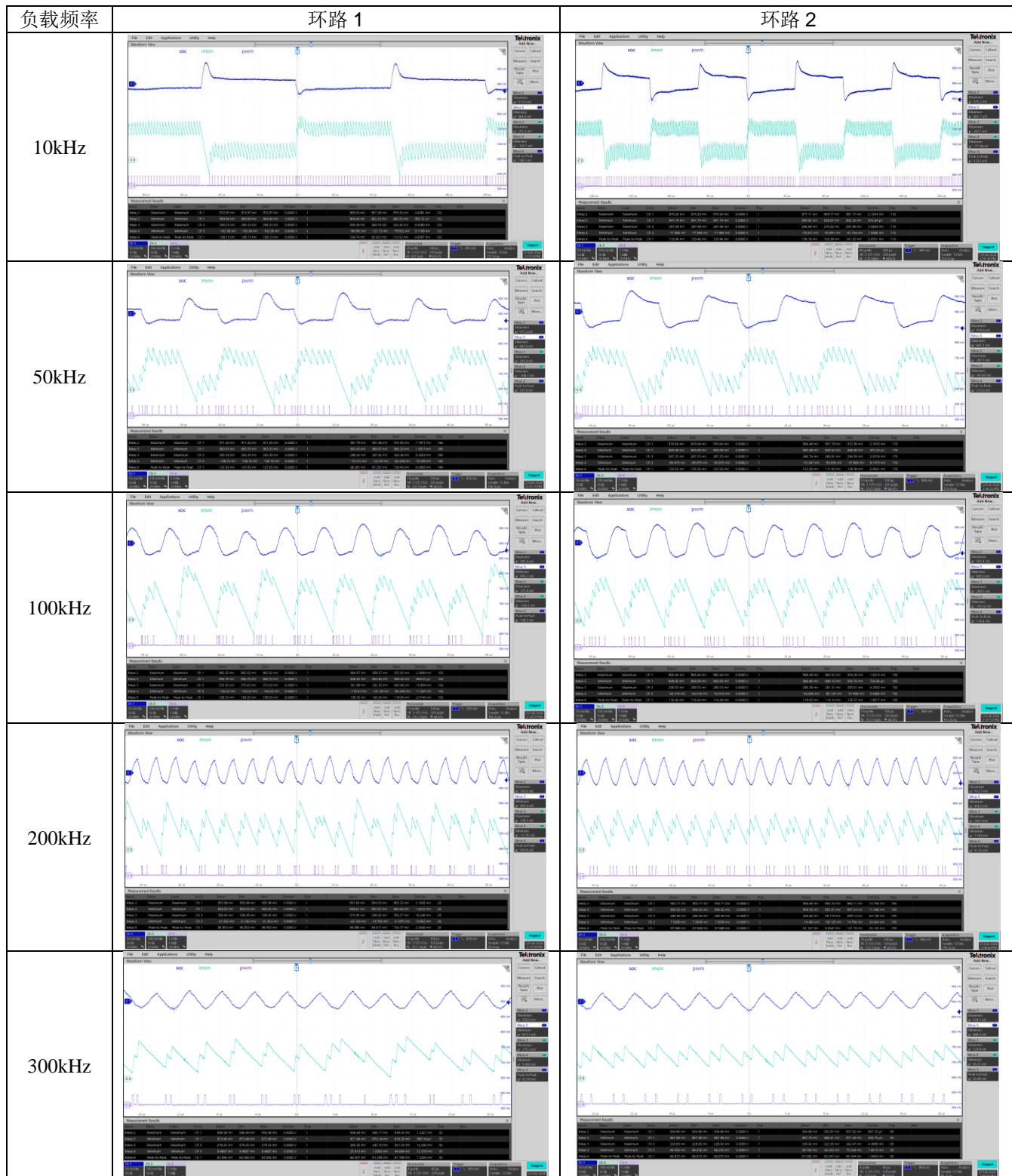

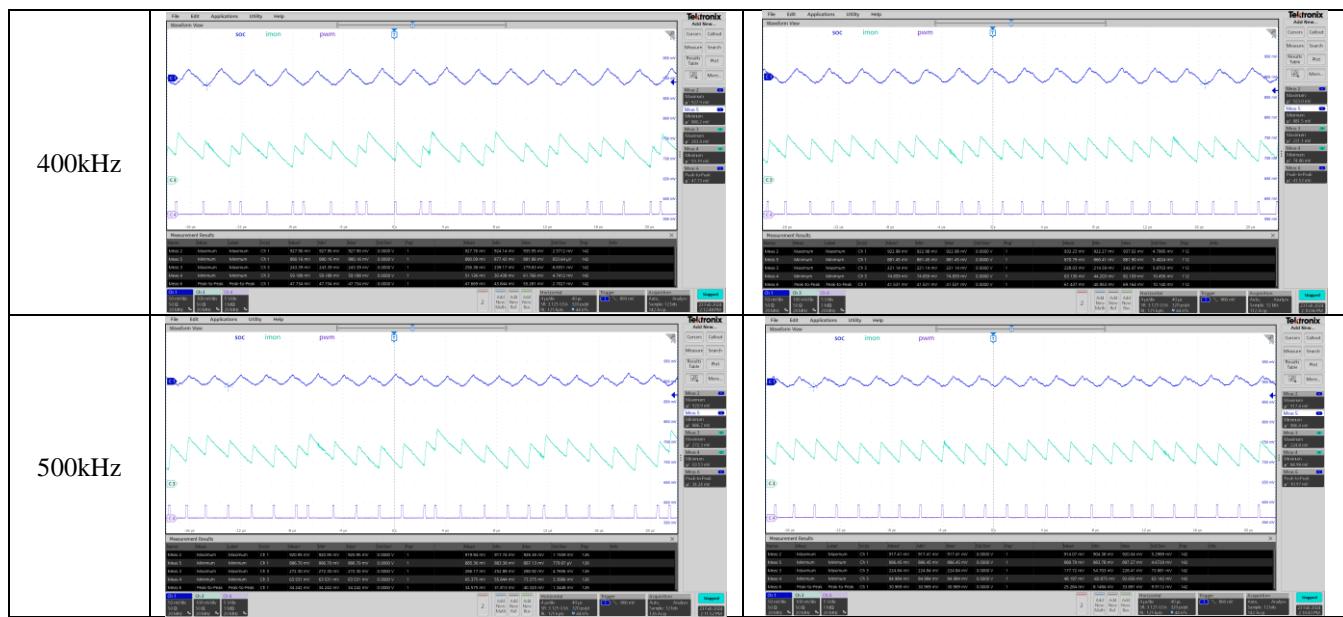

基于 AMD SP5 Genoa 平台的 SOC Rail，在不同负载频率点对环路 1 和环路 2 的瞬态波形进行测量，如表 4 所示，CH1 为输出电压波形，CH3 为某一个 Phase 的 IMON 波形，CH4 为此 Phase 的 PWM 波形。可以发现：在负载发生瞬态变化时，环路 2 的 PWM 脉冲更加均匀，因此其 IMON 的 Overshoot 和 Undershoot 更小，其输出电压的恢复过程越平滑。以 200kHz 为例，观察每个负载周期，环路 1 的输出电压纹波高低不平，PWM 疏密不一，IMON 过冲和下冲非常大，甚至出现了负电流，IMON 过冲很容易导致 OCP。而反观环路 2，每个负载周期的输出电压纹波都几乎一致，PWM 也非常均匀，没有出现连打的情况，因此其 IMON 的过冲和下冲都比较小，不容易触发 OCP。

**表 4 环路 1 和环路 2 的瞬态波形对比**

环路不稳定会导致 IMON 的 Overshoot 过大, 从而有可能触发 OCP, 导致服务器关机, 产生严重后果。在负载瞬态变化时对 IMON 峰值进行测试, 累计 10s 取最大值, 将数据总结表 5。发现环路 2 的 IMON 峰值要明显低于环路 1, 因此在 OCP 阈值一定时, 环路 2 更不容易触发 OCP。在负载频率为 100kHz 时, 不管是对于环路 1 还是环路 2, 其单 Phase IMON 峰值在所有频点中都是最大的, 因此是最容易触发 OCP 的, 但是此时环路 2 的单 Phase 的电感电流比环路 1 低 19.6A, 可以极大减小触发 OCP 的风险。

表 5 环路 1 和环路 2 的 IMON 峰值对比

| 负载频率   | 单 Phase IMON 峰值 (环路 1) /mV | 单 Phase 电感电流峰值 (环路 1) /A | 单 Phase IMON 峰值 (环路 2) /mV | 单 Phase 电感电流峰值 (环路 2) /A | 单 Phase 电感电流峰值差值 (环路 1-环路 2) /A |

|--------|----------------------------|--------------------------|----------------------------|--------------------------|---------------------------------|

| 1kHz   | 320                        | 64                       | 290                        | 58                       | 6                               |

| 5kHz   | 316                        | 63.2                     | 284                        | 56.8                     | 6.4                             |

| 10kHz  | 322                        | 64.4                     | 297                        | 59.4                     | 5                               |

| 50kHz  | 324                        | 64.8                     | 294                        | 58.8                     | 6                               |

| 100kHz | 403                        | 80.6                     | 305                        | 61                       | 19.6                            |

| 200kHz | 356                        | 71.2                     | 299                        | 59.8                     | 11.4                            |

| 300kHz | 301                        | 60.2                     | 242                        | 48.4                     | 11.8                            |

| 400kHz | 280                        | 56                       | 242                        | 48.4                     | 7.6                             |

| 500kHz | 281                        | 56.2                     | 228                        | 45.6                     | 10.6                            |

## 2.5 VR OCP 设定方法

除了环路不稳定, 触发 OCP 的另一个原因为 OCP 阈值设置不合理。本文提出如下两种方法:

- (1) 用示波器检测某个 Rail 每个 Phase 的 IMON 波形, 带宽设置为 20MHz 即可, 然后通过示波器的 Math 功能做加和, 示波器设置为余辉显示模式。运行 AMD 或者 Intel 的瞬态测试 Test Plan, 运行结束后读取 Math 的最大值, 然后除以 5mV/A 得到瞬态过程中最大的总电感电流  $I_{Lmax}$ , OCF 设置为 1.1-1.2 倍的  $I_{Lmax}$  即可。由于示波器的通道数一般为 4 个, 所以对于 5Phase 及 5Phase 以上的 Rail, 此方法将不太适用。

- (2) 按照 TI EVM 的 OCP 阈值设定, 由于实际项目与 EVM 必然会有差异, 所以需要验证此值是否合理。

首先运行 AMD 或者 Intel 的瞬态测试 Test Plan, 如果触发了 OCP, 则需要提高阈值, 直到不触发 OCP 为止, 在此基础上将阈值设置为 1.1-1.2 倍以保证足够裕量。

### 3 小结

VR 电路一般采用 DCAP+控制架构, 本文首先介绍了 DCAP+控制架构的基本原理, 然后提出了一种简单的稳定性判定方法, 然后通过实验证明其有效性。本文同步测量了波特图, 发现对于 DCAP+稳定性的判定有局限性, 最后针对环路稳定性对 IMON 以及 OCP 的影响, 提出了 OCP 阈值设置的合理方法。

### 参考文献

- [1]. 服务器 Power 电路设计. <https://cloud.tencent.com/developer/news/391988>

- [2]. D-CAP+™ Control for Multiphase, Step-Down Voltage Regulators for Powering Microprocessors <https://www.ti.com/cn/lit/an/slva867/slva867.pdf>

- [3]. Introducing D-CAP4™/D-CAP+, the next generation D-CAP adaptive on-time control mode for buck converters. <https://ti.com/>

- [4]. TPS536C9T Datasheet. <https://ti.com/>

- [5]. Simplifying Stability Checks. <https://www.ti.com/lit/an/slva381b/slva381b.pdf>

- [6]. DCAP Stability Letter. <https://ti.com/>

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，TI 对此概不负责。

TI 提供的产品受 [TI 的销售条款](#) 或 [ti.com](#) 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址：Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

版权所有 © 2025, 德州仪器 (TI) 公司