*Application Note***DP83822 疑难解答指南**

*Avtar Dhaliwal, Jae Yoon*

**摘要**

本应用手册提供了评估新应用和确认预期功能的建议流程。这些分步建议可以帮助简化 DP83822 设计的电路板启动和初始评估。

**内容**

|                                |    |

|--------------------------------|----|

| <b>1 DP83822 应用概述</b>          | 2  |

| <b>2 排查 PHY 应用问题</b>           | 3  |

| 2.1 原理图和布局检查清单                 | 3  |

| 2.2 器件运行状况检查                   | 3  |

| 2.2.1 电源斜坡时序检查                 | 3  |

| 2.2.2 电压检查                     | 5  |

| 2.2.3 探测 RESET_N 信号            | 5  |

| 2.2.4 探测 RBIAS 引脚              | 5  |

| 2.2.5 探测 XI 时钟                 | 6  |

| 2.2.6 在初始化期间探测搭接引脚             | 7  |

| 2.2.7 探测串行管理接口 ( MDC、MDIO ) 信号 | 8  |

| 2.3 MDI 运行状况检查                 | 11 |

| 2.3.1 磁性元件                     | 11 |

| 2.3.2 探测 MDI 信号                | 13 |

| 2.3.3 链路质量检查                   | 14 |

| 2.3.4 调试光纤连接                   | 15 |

| 2.3.5 调试帧起始检测                  | 17 |

| 2.3.6 合规性                      | 17 |

| 2.4 MII 运行状况检查                 | 17 |

| 2.4.1 MII 检查                   | 17 |

| 2.4.2 RMII 检查                  | 19 |

| 2.4.3 RGMII 检查                 | 22 |

| 2.5 环回和 PRBS                   | 25 |

| 2.5.1 环回模式                     | 25 |

| 2.5.2 通过 MAC 发送和接收数据包          | 26 |

| 2.5.3 通过 BIST 发送和接收数据包         | 27 |

| <b>3 工具和参考</b>                 | 28 |

| 3.1 DP83822 寄存器访问              | 28 |

| 3.2 Linux 上的软件和驱动程序调试          | 29 |

| 3.2.1 普通端子输出和解决方案              | 29 |

| <b>4 总结</b>                    | 31 |

| <b>5 参考资料</b>                  | 31 |

| <b>6 修订历史记录</b>                | 32 |

**商标**

所有商标均为其各自所有者的财产。

## 1 DP83822 应用概述

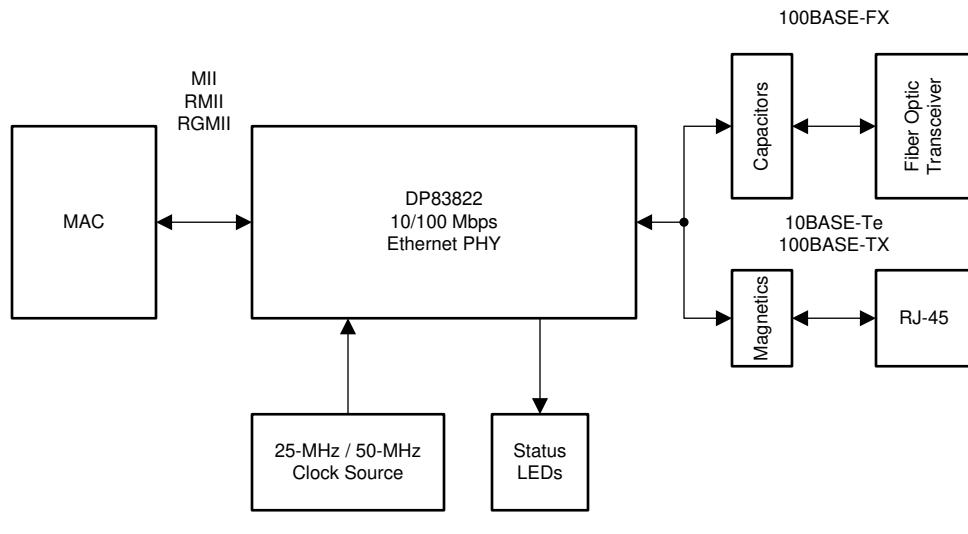

DP83822 是一款超稳健、低功耗单端口 10/100Mbps 以太网 PHY，旨在用于恶劣的工业环境。DP83822 提供通过标准双绞线电缆发送和接收数据或者连接到外部光纤收发器所需的所有物理层功能。此外，DP83822 可通过标准 MII、RMII 或 RGMII 接口灵活地连接到 MAC 上。

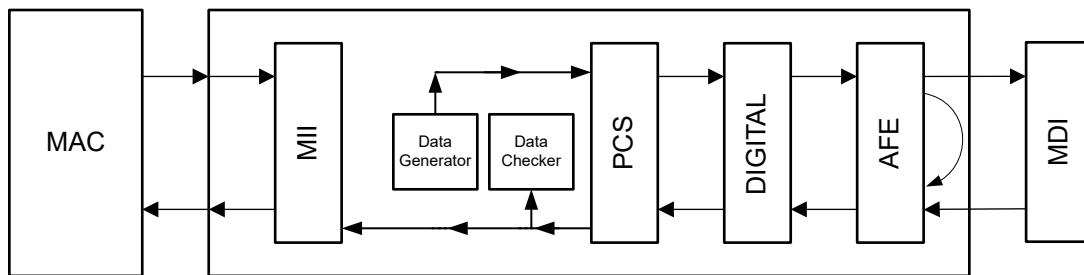

图 1-1 是典型 DP83822 应用的简化系统方框图。

Copyright © 2016, Texas Instruments Incorporated

图 1-1. DP83822 方框图

DP83822 将连接到以太网 MAC 和 MDI。通过变压器和连接器（用于铜缆应用）或电容器和收发器（用于光纤应用）与 MDI 连接。

## 2 排查 PHY 应用问题

以下各节从较高层次介绍调试方法，尝试从具有广泛影响的应用特性开始，然后致力于研究设计的更重点方面。

本文档旨在解决常见的以太网问题，例如：

- 无法存取寄存器

- 无法获取链路或间歇性链路

- 链路但发现数据包错误

- 无法 ping

德州仪器 (TI) 建议，非另有说明，否则建议按顺序完成以下各节。

### 2.1 原理图和布局检查清单

[DP83822 原理图检查清单](#)与 [DP838XX 布局检查清单](#)是 TI 文件，将使用 DP83822 原理图进行设计的最佳实践编译到单个易于使用的文档中。德州仪器 (TI) 建议浏览本文档以了解 PHY 工作所需的连接和元件的更详细说明。

以下各节可以介绍 PHY 上电并正确初始化后的预期行为。如果与预期行为有任何偏差，则可能会因外设电路不正确而导致误差。

### 2.2 器件运行状况检查

本节深入介绍器件运行状况检查，该检查可确保器件已正确通电并初始化。如果 DP83822 发生如下情况，可以跳过此部分：

- 连接到链路伙伴时正在连接 ( LED 指示或寄存器状态 ) 或在以太网电缆未连接时显示 FLP 信号，以及

- 正在响应寄存器访问 ( 如果适用 )

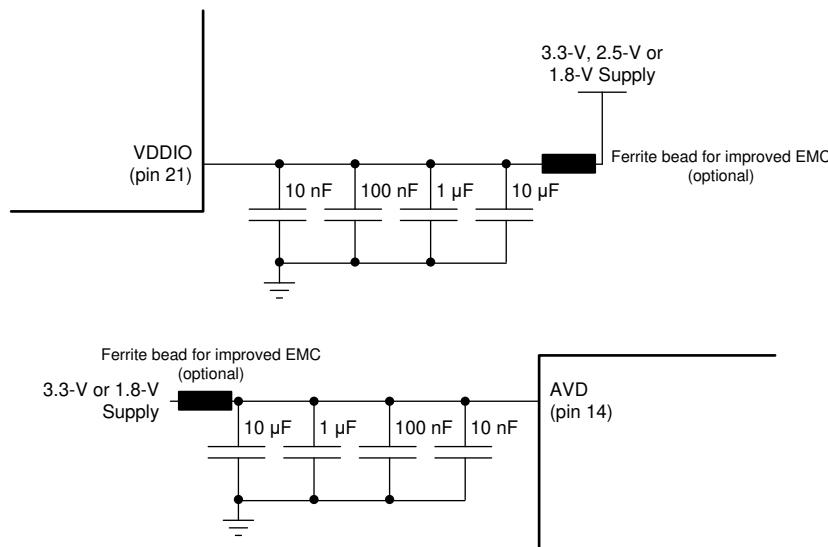

#### 2.2.1 电源斜坡时序检查

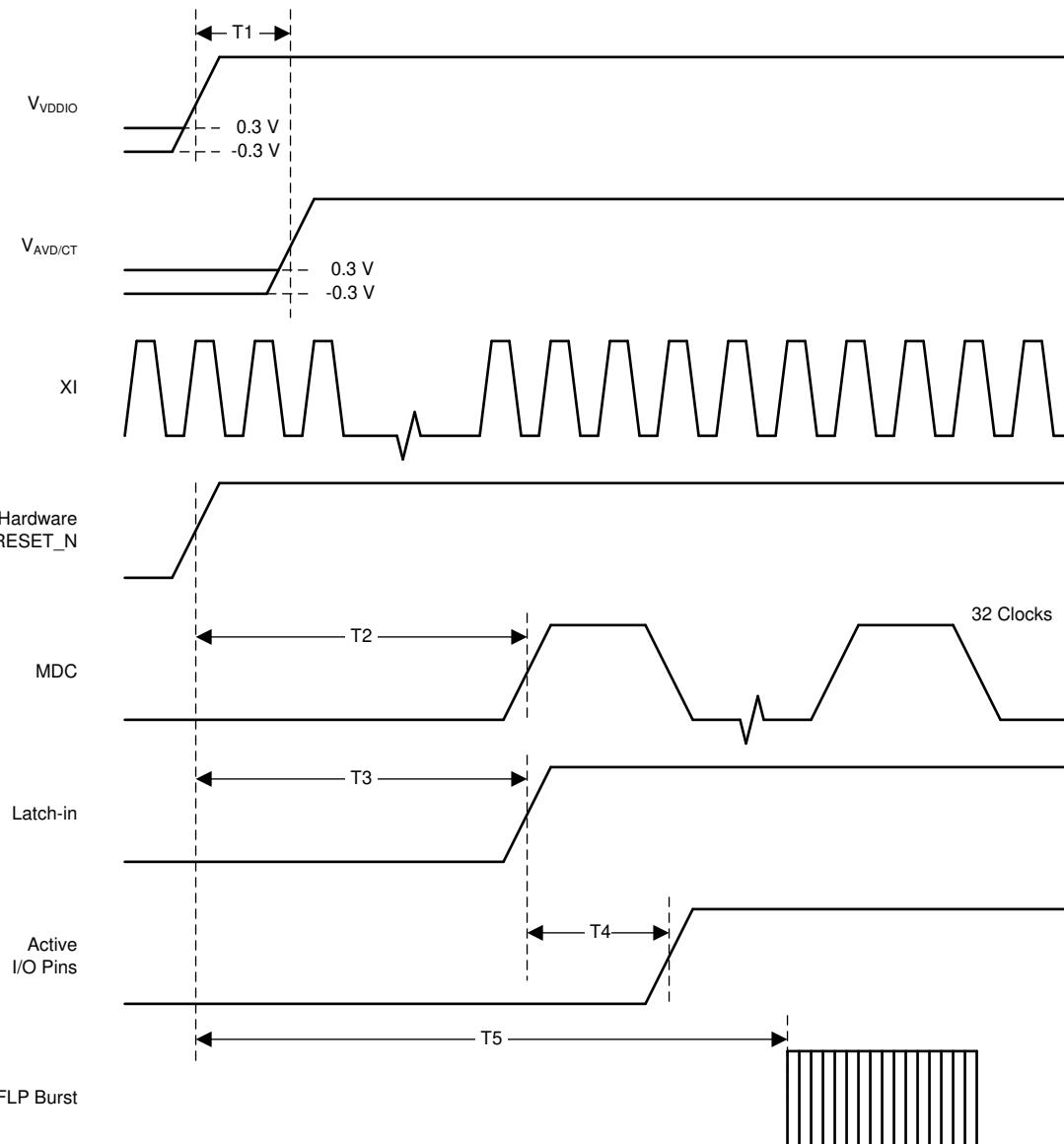

确保根据建议的电源斜坡时序序列为器件供电。为器件加电并探测 PHY 的电压轨以确保电压处于 [表 2-1](#) 中定义的限制范围内。验证上电电压参数时序是否在 [表 2-2](#) 和 [图 2-1](#) 中定义的限制范围内。

**表 2-1. PHY 电源电压规格**

|           | 说明              | 最小值   | 典型值 | 最大值   | 单位 |

|-----------|-----------------|-------|-----|-------|----|

| VDDIO     | 电源电压 I/O = 1.8V | 1.71  | 1.8 | 1.89  | V  |

|           | 电源电压 I/O = 2.5V | 2.375 | 2.5 | 2.625 |    |

|           | 电源电压 I/O = 3.3V | 3.15  | 3.3 | 3.45  |    |

| AVD       | 电源电压模拟 = 3.3V   | 3.15  | 3.3 | 3.45  | V  |

|           | 电源电压模拟 = 1.8V   | 1.71  | 1.8 | 1.89  |    |

| 中心抽头 (CT) | 电源电压中心抽头 = 3.3V | 3.15  | 3.3 | 3.45  | V  |

|           | 电源电压中心抽头 = 1.8V | 1.71  | 1.8 | 1.89  |    |

**表 2-2. 时序要求：上电时序**

| 参数 | 测试条件                                                                        | 最小值                        | 典型值  | 最大值 | 单位 |

|----|-----------------------------------------------------------------------------|----------------------------|------|-----|----|

| T1 | VDDIO ( 数字电源 ) 斜坡后的 AVD ( 模拟电源 ) 斜坡延迟。<br>在电源斜坡之前，AVD 和 VDDIO 电位不得超过 0.3V 。 | 从电压斜坡开始的时间                 | -100 | 100 | ms |

|    | VDDIO 斜坡时间                                                                  |                            |      | 100 | ms |

|    | AVD 斜坡时间                                                                    |                            |      | 100 | ms |

| T2 | MDC 前导码之前的上电后稳定时间，用于访问寄存器。<br>在这最长等待时间之后的任何时间进入的 MDC 前导码都有效。                | MDIO 被拉至高电平，用于 32 位串行管理初始化 |      | 200 | ms |

| T3 | 上电所需的硬件配置锁存时间                                                               |                            |      | 200 | ms |

| T4 | 硬件配置引脚转换为输出驱动器                                                              |                            |      | 64  | ns |

表 2-2. 时序要求：上电时序（续）

| 参数                | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|-------------------|------|-----|-----|-----|----|

| T5 上电后的快速链路脉冲传输延迟 |      |     | 1.5 |     | s  |

图 2-1. 上电时序

**备注**

如果 DP83822 存在链路建立问题，并且 AVD 在 3.3V 下运行，请检查寄存器 0x0421 以查看 AVD 电平和 VDDIO 电平与所需输出匹配。寄存器 0x0421 bit[2]=1 表示 3.3V AVD。对于 3.3V VDDIO，寄存器 0x0421 bit[1:0]=11。如果寄存器 0x0421 与所需的结果不匹配，请将 0x041F 寄存器写入所需的电压电平。对于 3.3V AVD，写入寄存器 0x041F bit[12]=1；对于 3.3V VDDIO，写入 bit[11:10]=11。寄存器 0x0421 和 0x041F 是扩展寄存器，请务必遵循[扩展寄存器访问](#)。

**2.2.1.1 XI 时钟不稳定时的电源斜坡**

确保稳定的 XI 时钟在 PHY 上电时可用。如果没有稳定的 XI 时钟可用，PHY 将不会正确初始化。如果无法实现这一点，请将 PHY 保持在复位状态，直到 PHY 上电后 XI 稳定。如果在 DP83822 上电时探测到 XI 时钟不稳定，请参阅[表 2-3](#) 和 [图 2-2](#)，了解详细的时序要求和时序图。

表 2-3. 时序要求：在 XI 时钟不稳定时上电

| 参数            | 最小值 | 标称值 | 最大值 | 单位 |

|---------------|-----|-----|-----|----|

| T1 XI 稳定后复位应用 | 1   |     |     | us |

| T2 复位脉冲宽度     | 10  |     |     | us |

图 2-2. 在 XI 输入不稳定时上电

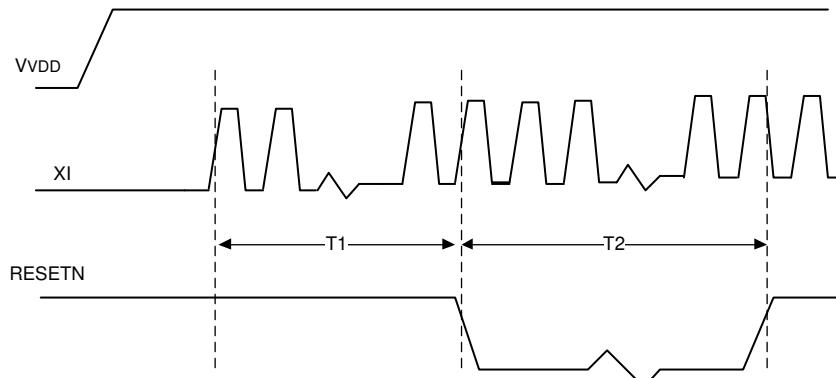

### 2.2.2 电压检查

DP83822 需要有充足的电力，还需要采用以下该器件特有的去耦方案：

- 每个电源轨：

- 1x 10nF、1x 100nF、1x 1uF、1x 10uF

图 2-3. 电源去耦建议

### 2.2.3 探测 RESET\_N 信号

复位引脚为低电平有效。务必确认控制器未将 RESET\_N 信号驱动为低电平。否则，器件将保持复位状态，并且不会响应。

### 2.2.4 探测 RBIAS 引脚

RBIAS 电阻器用于在 PHY 中产生内部偏置电流和电压。它的额定容差为 1%，因此 PHY 能够满足严格的 IEEE 802.3 规范。首选是具有单个元件而不是多个串联元件，因为容差范围可能会增加。

测量 RBIAS 电阻两端电压的直流值，并确认电压为 1V。

为电路板断电并验证 Rbias 电阻器值是否为  $4.87k\Omega \pm 1\%$ 。

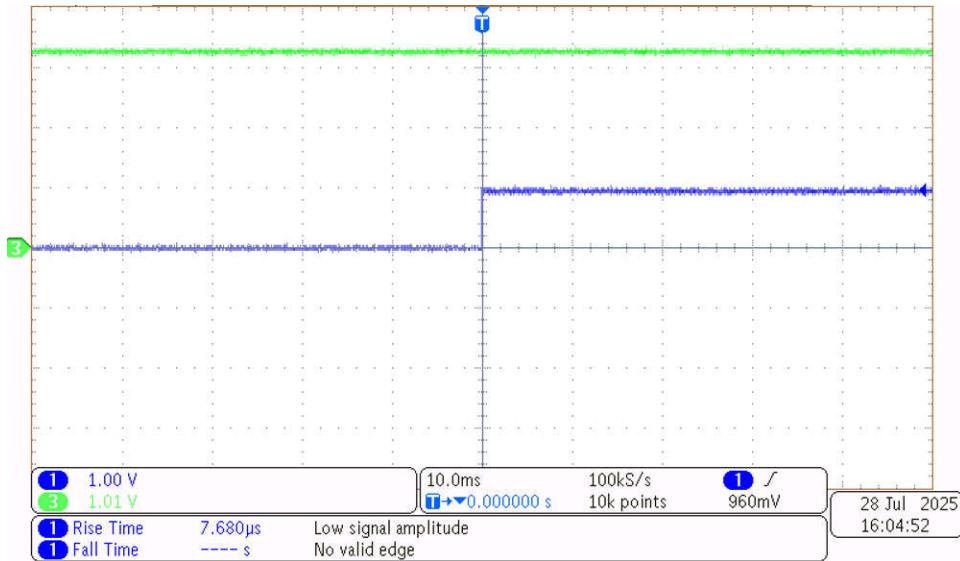

绿色表示 AVD，蓝色表示 Rbias。器件正确斜升后，Rbias 应变为高电平并保持在 1V 的高电平。

图 2-4. AVD 上电期间的 DP83822 Rbias 信号

### 2.2.5 探测 XI 时钟

以下指南是兼容晶体的主要参考规格。

表 2-4. 25MHz 晶体规格

| 参数   | 测试条件         | 最小值  | 典型值 | 最大值 | 单位  |

|------|--------------|------|-----|-----|-----|

| 频率   |              |      | 25  |     | MHz |

| 频率容差 | 包括工作温度、老化等因素 | -100 | 100 | 100 | ppm |

| 负载电容 |              | 10   | 40  | 40  | pF  |

**表 2-5. 25MHz 振荡器规格**

| 参数        | 测试条件           | 最小值  | 典型值 | 最大值 | 单位   |

|-----------|----------------|------|-----|-----|------|

| 频率        |                |      | 25  |     | MHz  |

| 频率容差      | 包括工作温度、老化等因素   | -100 |     | 100 | ppm  |

| 上升/下降时间   | 10% - 90%      |      |     | 8   | nsec |

| 抖动 ( 短期 ) | Cycle-to-cycle |      | 50  | 100 | psec |

| 抖动 ( 长期 ) | 10ms 内的累积      |      |     | 1   | nsec |

| 对称性       | 占空比            | 40   |     | 60  | %    |

| 负载电容      |                |      | 15  | 30  | pF   |

**表 2-6. 50MHz 振荡器规格**

| 参数        | 测试条件           | 最小值  | 典型值 | 最大值 | 单位   |

|-----------|----------------|------|-----|-----|------|

| 频率        |                | 50   |     |     | MHz  |

| 频率容差      | 包括工作温度、老化等因素   | -100 |     | 100 | ppm  |

| 上升/下降时间   | 10% - 90%      |      |     | 8   | nsec |

| 抖动 ( 短期 ) | Cycle-to-cycle |      | 50  |     | psec |

| 抖动 ( 长期 ) | 10ms 内的累积      |      |     | 1   | nsec |

| 对称性       | 占空比            | 40   |     | 60  | %    |

| 负载电容      |                |      | 15  | 30  | pF   |

验证频率和信号完整性。为了确保链路完整性，建议参考时钟采用以下模式：

- MII/RGMII 和 RMII 主模式

- $25\text{MHz} \pm 100\text{ppm}$

- RMII 从模式

- $50\text{MHz} \pm 100\text{ppm}$

## 2.2.6 在初始化期间探测搭接引脚

可以使用 [节 2.1](#) 中所述的 strap 工具来验证 strap 配置。

上电或硬件复位时会通过 RESET 引脚，或寄存器 0x001F 的位 15 对自举配置进行采样。

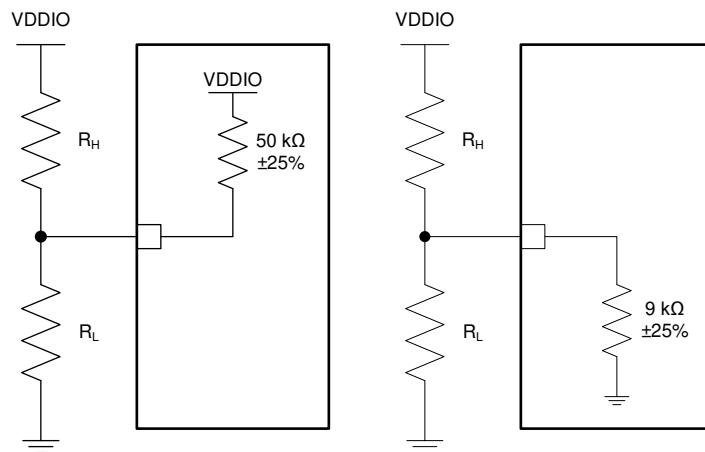

确保线路上的任何其他元件都不需要影响该网络设置的直流偏置。应使用建议值的上拉电阻器和下拉电阻器来设置自举引脚输入和电源的电压比，从而选择一种可能的模式。

然而，在某些情况下，电路板上的其他器件（例如，MAC）将意外地拉动或驱动这些引脚。可以从寄存器 0x467 (SOR1) 和 0x468 (SOR2) 读取 strap 配置值，这些寄存器是扩展寄存器，只能使用[扩展寄存器访问](#)进行访问。

建议使用以下电阻器进行自举。如果寄存器值与预期的自举配置不匹配，可以在上电期间以及上电后 RESET\_N 信号有效时进行测量。

图 2-5. 自举电路

表 2-7. 建议 4 级 Strap 配置电阻比

| 模式 (1)      | 理想 $R_H$ (kΩ) | 理想 $R_L$ (kΩ) |

|-------------|---------------|---------------|

| 下拉引脚 (9kΩ)  |               |               |

| 1 (默认值)     | 断开            | 断开            |

| 2           | 10            | 2.49          |

| 3           | 5.76          | 2.49          |

| 4           | 2.49          | 断开            |

| 上拉引脚 (50kΩ) |               |               |

| 1           | 断开            | 1.96          |

| 2           | 13            | 1.96          |

| 3           | 6.2           | 1.96          |

| 4 (默认值)     | 断开            | 断开            |

(1) 建议使用容差为 1% 的自举电阻器。

### 2.2.7 探测串行管理接口 (MDC、MDIO) 信号

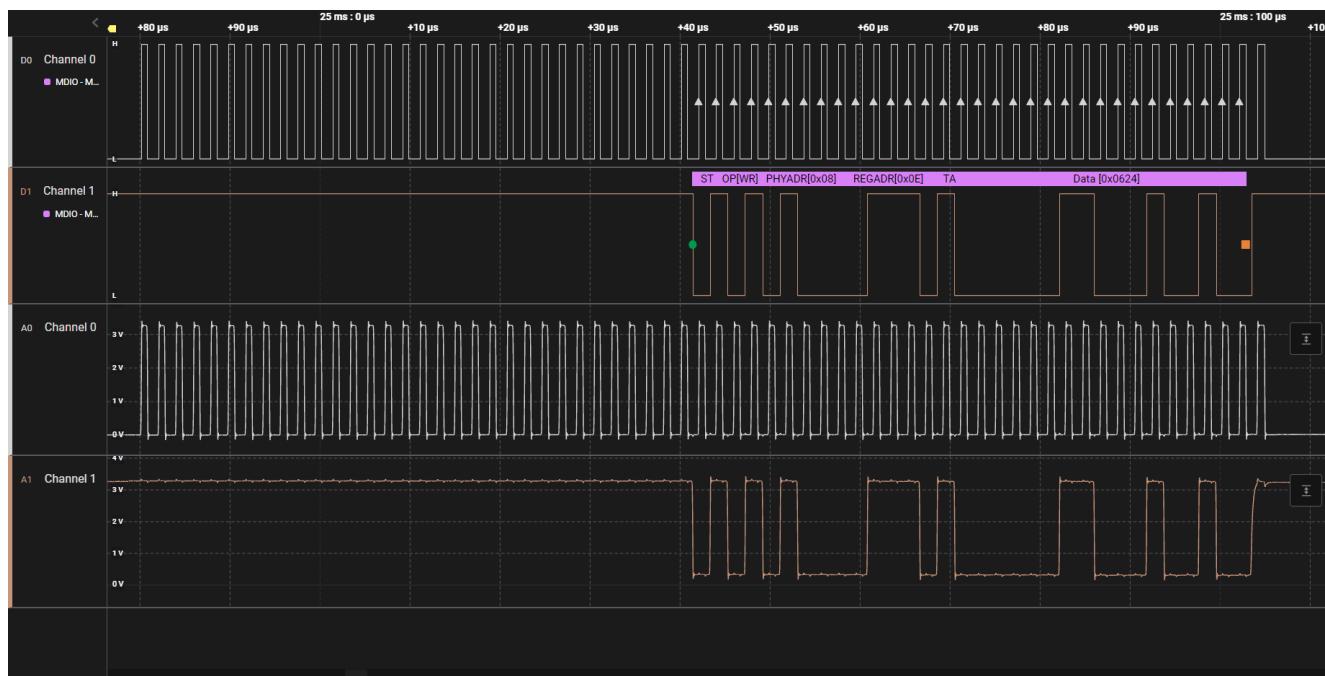

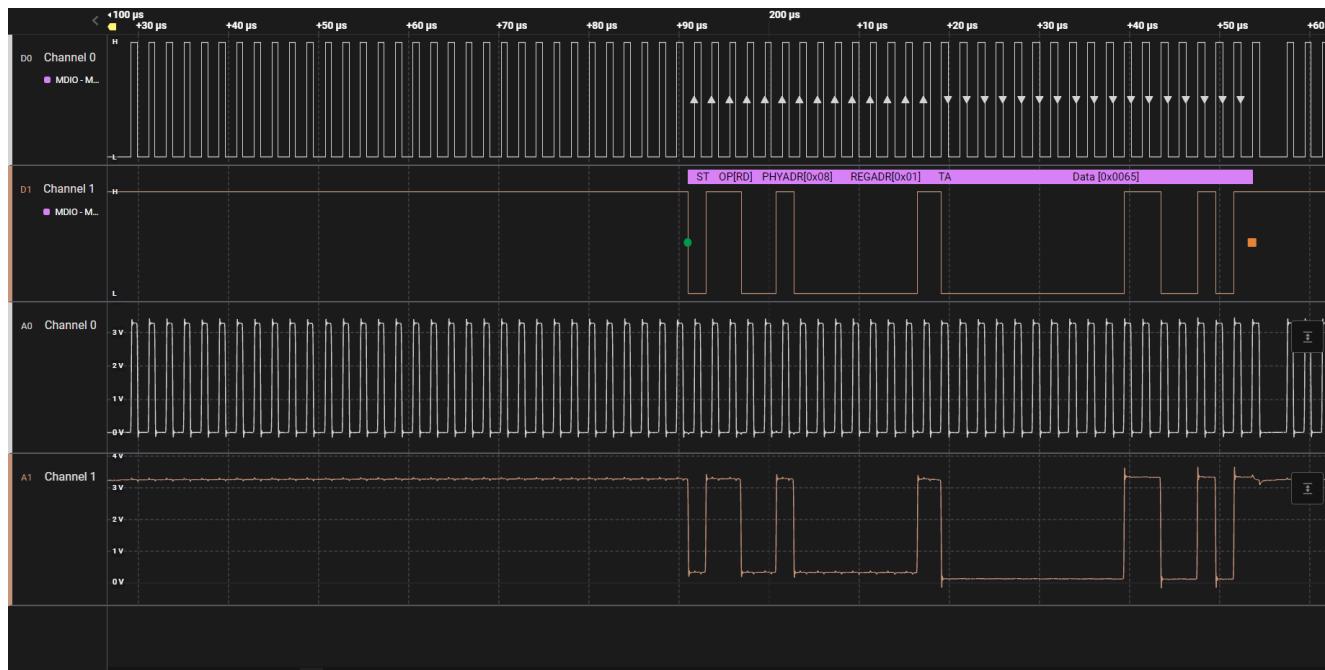

如果适用，串行工作站管理接口可用于在调试期间提供有价值的状态字段。但是，请验证此通信是否准确以避免复合问题。MDIO 应通过  $2.2\text{k}\Omega$  上拉电阻上拉至 VDDIO。探测 MDIO 以确认默认电压。

尝试写入和读取寄存器。使用数据表验证 MDIO 数据序列，确保 MDIO 读取访问时序正确。

表 2-8. SMI 协议结构

| SMI 协议 | <idle><start><op code><device addr><reg addr><turnaround><data><idle> |

|--------|-----------------------------------------------------------------------|

| 读取寄存器  | <idle><01><10><AAAAAA><RRRRRR><Z0><XXXX XXXX XXXX XXXX><idle>         |

| 写入寄存器  | <idle><01><01><AAAAAA><RRRRRR><10><XXXX XXXX XXXX XXXX><idle>         |

图 2-6. MDC/MDIO 写入示例

图 2-7. MDC/MDIO 读取示例

### 2.2.7.1 读取并检查寄存器值

如果 SMI 总线正常工作，则读取寄存器并验证器件特定数据表中显示的默认值。

| 寄存器地址  | 具有自动协商功能的寄存器值 |         |

|--------|---------------|---------|

|        | 10Mbps        | 100Mbps |

| 0x0000 | 3100          | 3100    |

| 0x0001 | 786D          | 786D    |

| 0x0002 | 2000          | 2000    |

| 0x0003 | A240          | A240    |

| 0x0004 | 0061          | C1E1    |

| 0x0005 | C1E1          | C1E1    |

| 0x0010 | 4117          | 4715    |

| 0x0014 | 0000          | 0000    |

| 0x0015 | 0000          | 0000    |

| 0x0017 | 0041          | 0041    |

| 0x0019 | 8021          | 8C21    |

在 PHY 以给定速度链接的情况下，使用这些值作为参考来识别预期运行的任何变化。请注意，并非所有寄存器都需要相同，例如。

- 寄存器 0x0005 的值取决于链路伙伴的能力。

- 寄存器 0x0010 的 MSB 中的“4”或“0”差异是由于位 14 MDI/MDIX 模式造成的，不会产生任何影响。显着差异是作为 LSB 的“7”或“5”，这会告知您速度状态。

**示例：**在以 10Mbps 的速率为 PHY 供电并链接之后，寄存器 0x0010 以值 0x0017 读取，这意味着位 [4, 2, 1, 0] 是高电平。这些位会确认：自协商完成、全双工、10Mbps 模式以及建立了有效链路。

对于表中显示的任何不同于预期值的值，重复此过程将有助于诊断 PHY 的确切状态来解决遇到的任何问题。

### 2.2.7.1.1 扩展寄存器访问

要在扩展寄存器空间中读取和写入寄存器，请参阅以下过程：

MMD “1F” 寄存器的写入过程：

写入 reg<000D> = 0x001F

写入 reg<000E> = <address>

写入 reg<000D> = 0x401F

写入 reg<000E> = <value>

MMD “1F” 寄存器的读取过程：

写入 reg<000D> = 0x001F

写入 reg<000E> = <address>

写入 reg<000D> = 0x401F

读取 reg<000E>

在写入操作之后，若要写入扩展寄存器组中的寄存器并自动将地址寄存器递增到下一更高值：

MMD “1F” 寄存器的写入（有后增量）过程：

写入 reg<000D> = 0x001F

写入 reg<000E> = <address>

写入 reg<000D> = 0x401F

写入 reg<000E> = 0x0C50

写入 reg<000E> = <value>

在读取操作之后，若要读取扩展寄存器组中的寄存器并自动将地址寄存器递增到下一更高值：

MMD “1F” 寄存器的读取（有后增量）过程：

写入 reg<000D> = 0x001F

写入 reg<000E> = <address>

写入 reg<000D> = 0x801F

读取 reg<000E>

读取 reg<000E>

---

#### 备注

上述写入和读取过程通常用于地址大于 0x001F 的寄存器，但该过程通常也可用于任何地址。

---

## 2.3 MDI 运行状况检查

本节深入介绍器件运行状况检查，用于确保器件的 MDI 部分正常运行。如果 DP83822 发生如下情况，可以跳过此部分：

- 当通过器件发送流量时，已链接并通过 Reg 0x15 报告无数据包错误

### 2.3.1 磁性元件

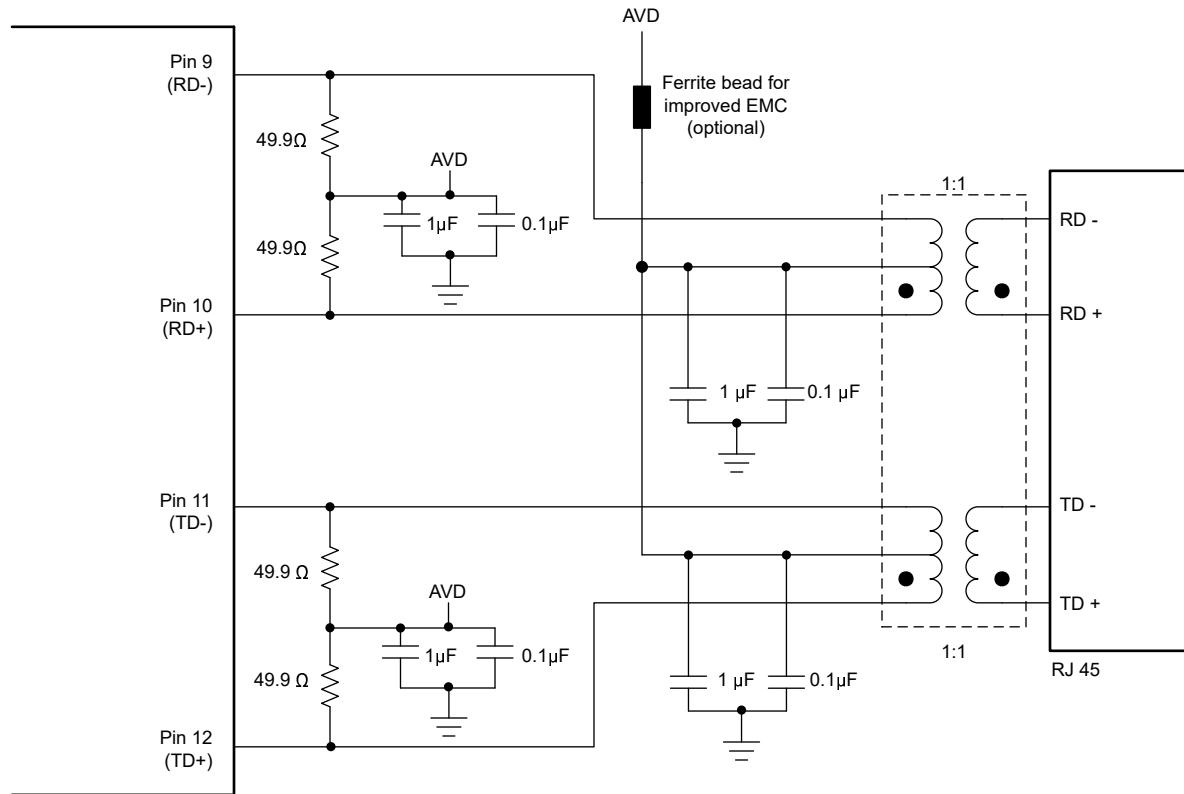

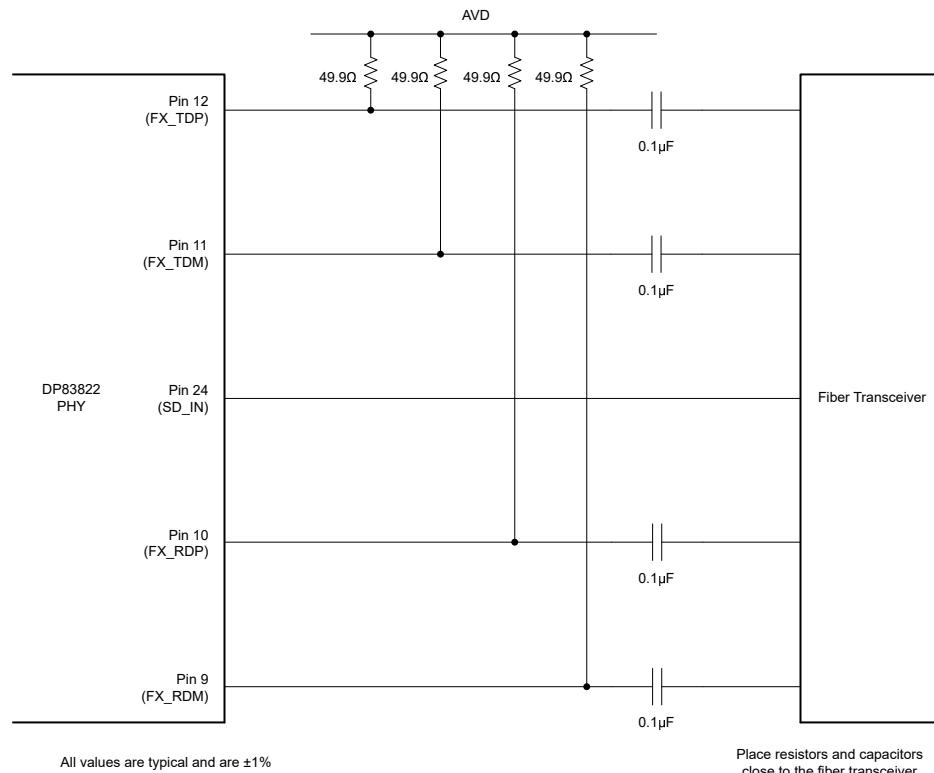

由于 DP83822 是电流模式驱动器，因此请确保 MDI 线路通过  $49.9\Omega$  电阻器下拉至 AVD。请参阅 [图 2-8](#)

图 2-8. DP83822 TPI 网络电路

以下指南是兼容磁性元件的主要参考规格：

表 2-9. 磁隔离要求

| 参数       | 测试条件         | 典型值  | 单位   |

|----------|--------------|------|------|

| 匝数比      | ±2% 容差       | 1:1  | -    |

| 插入损耗     | 1MHz-100MHz  | -1   | dB   |

| 回波损耗     | 1MHz-30MHz   | -16  | dB   |

|          | 30MHz-60MHz  | -12  | dB   |

|          | 60MHz-80MHz  | -10  | dB   |

| 差分至共模抑制比 | 1MHz-50MHz   | -30  | dB   |

|          | 50MHz-150MHz | -20  | dB   |

| 串扰       | 30MHz        | -35  | dB   |

|          | 60MHz        | -30  | dB   |

| 隔离       | HPOT         | 1500 | Vrms |

如果无法满足这些确切要求，可以提供以下容差。

- 匝数比

- 理想情况下为 2%，但 3% 也可以接受。

- 电感

- 优先选择高电感。通常看到的数字约为  $350 \mu H$ 。

- 插入损耗

- 与数据表中规定的每个范围的指定值相比，该值应尽可能接近 0dB。如果规格给出 -1dB 的典型值，建议找到具有 -1dB、-0.9dB、…的元件。

- 回波损耗

- 不高于数据表中指定的幅度。如果规格给出 -16dB 的典型值，建议找到具有 -16dB、-17dB、…的元件。

### 2.3.2 探测 MDI 信号

在默认配置中，可以启用自动协商和自动 MDIX。链路脉冲需要在通道发送 (TD\_P、TD\_M) 上可见，并且偶尔会切换到接收对 (RD\_P、RD\_M)。如果设置为 MDI，则此脉冲仅在发送对上可用，而如果在 MDI-X 模式下设置，此脉冲仅在接收对上可用。

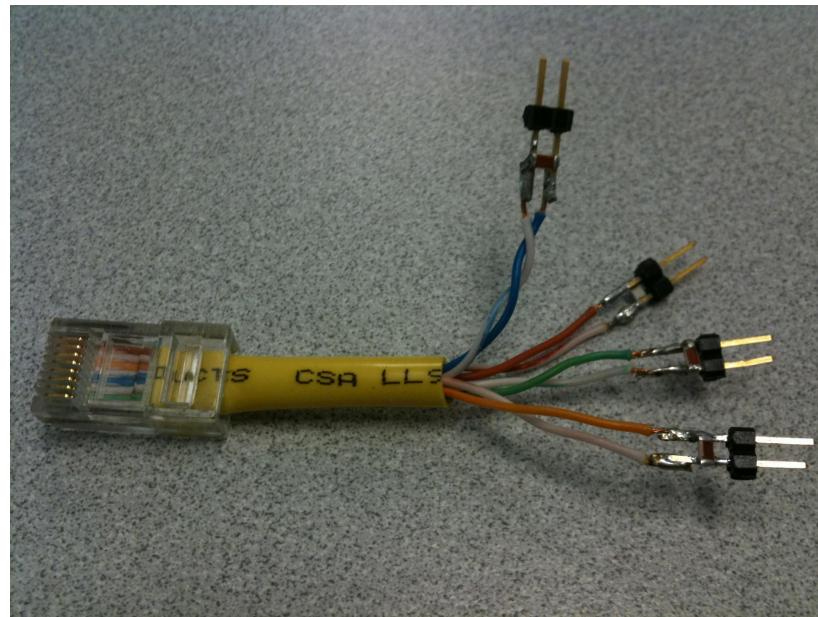

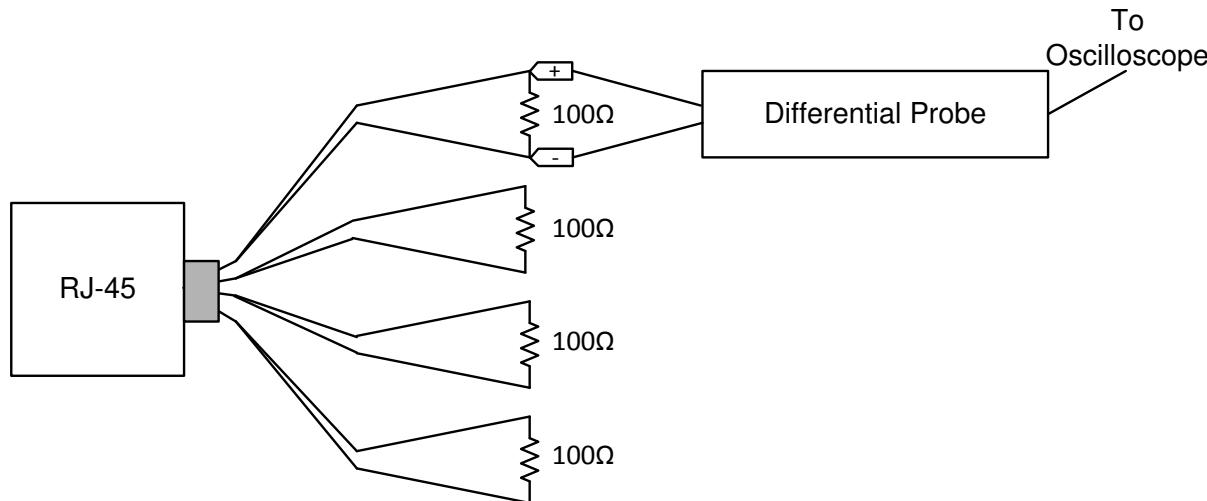

具有  $100\Omega$  终端的短以太网电缆可用于测量 MDI 信号。端接电缆如 图 2-9 所示。图 2-10 展示了使用端接电缆进行测量的连接图。

图 2-9. 用于 MDI 信号测量的  $100\Omega$  端接电缆

图 2-10. 100M 端接电缆的连接图

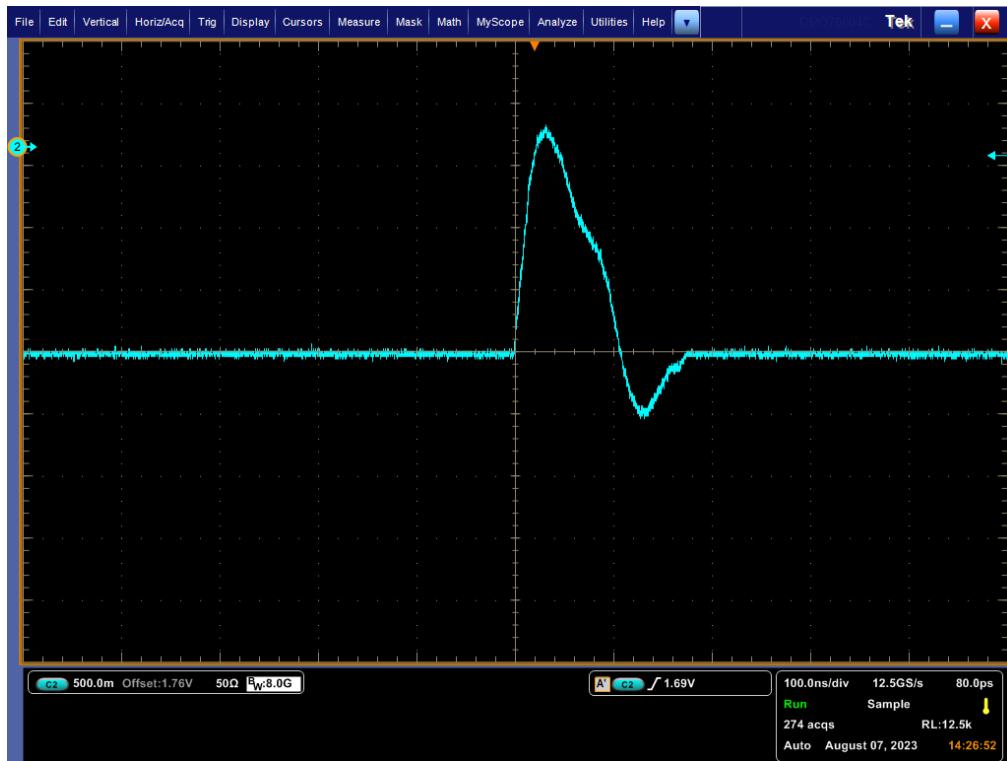

链路脉冲的标称宽度为  $100\text{ns}$ ，每  $16\text{ms}$  发生一次。图 2-11 显示了正确的链路脉冲。

图 2-11. DP83822 链路脉冲

### 2.3.3 链路质量检查

建立有效链路后，确认密钥状态寄存器值并直观验证链路 LED 是否亮起，链路仍可能出现数据包错误。

链路问题可能有以下几种原因：

- 链路伙伴传输问题

- 电缆长度和质量

- 25MHz 参考时钟的时钟质量

- MDI 信号质量

PHY 通电并连接到链路伙伴后，可以读取以下寄存器以确定链路的运行状况：

表 2-10. 链路质量 MSE 寄存器

| 通道 | 寄存器地址 |

|----|-------|

| A  | 0x218 |

对于给定的通道，读取寄存器值以确定 MSE（均方误差），并参阅 表 2-11 来确定链路质量。

表 2-11. MSE 链路质量范围

| 链路质量 | 寄存器内容         |

|------|---------------|

| 非常好  | < 0x20A       |

| 良好   | 0x20A - 0x33B |

| 不佳   | > 0x33B       |

也可以在 PHY 上执行时域反射法 (TDR) 测试，以检测线路连接内的问题以及故障发生位置。有关不同 TDR 配置和测试模式以及如何在 PHY 上运行 TDR 测试的详细信息，请参阅 [如何使用 DP83822 的 TDR 功能](#)。

### 2.3.4 调试光纤连接

光纤网络电路显示了 100Mbps 光纤网络的推荐电路。确认电路是否满足预期应用的要求。

所有电阻和电容应尽可能靠近光纤收发器放置。

图 2-12. 光纤网络电路

#### 备注

有关 PECL 和 LVPECL 应用以及所需的推荐附加电容器和电阻器，请参阅 [DP83822 EVM 用户指南](#)。

#### 备注

SFP 光纤收发器通常具有集成的交流耦合电容器。可能不需要添加外部电容器。

DP83822 提供符合 IEEE 802.3 标准的 100BASE-FX 运行。硬件自举或寄存器配置可用于启用 100BASE-FX 运行。

DP83822IF 和 DP83822HF 是 DP83822 支持光纤功能的型号。寄存器 0x0001[2] 指示铜缆和光纤运行模式的链路状态。在光纤中，当链路状态发生变化时，此位不会切换。必须在读取寄存器 0x0001 之前执行软复位（设置寄存器 0x001F = 0x4000），以确保正确的链路状态更改更新。

DP83822 具有信号检测引脚。此引脚连接到业界通用光纤收发器。使用 FX\_EN 自举启用 100BASE-FX 运行时，AMDIEN 自举将变为 SD\_EN 自举。有关光纤自举配置，请参阅 [表 2-12](#)。

#### 备注

100BASE-FX 信号检测引脚 (LED\_1) 极性由光纤通用配置寄存器 (FIBER GENCFG，寄存器 0x0465) 中的 bit[0] 控制。请参阅 [表 2-13](#)。默认情况下，信号检测为高电平有效极性。

**备注**

TI 建议将光收发器的信号检测引脚连接到 LED\_1 引脚，并在 100BASE-FX 模式下使用 SD\_EN 自举引脚启用它。设计中未使用 LED\_1 引脚，如果光纤模块和 DP83822 之间的电气链路中断、断开或以其他方式中断，则只能通过 MDIO/MDC 接口启动软复位来恢复链路。

**表 2-12. 光纤自举配置**

| 引脚名称  | 引脚编号 | PU/PD | 模式    | 说明                                                                                                            |

|-------|------|-------|-------|---------------------------------------------------------------------------------------------------------------|

| COL   | 29   | PU    | 2 或 3 | FX_EN：启用 100BASE-FX                                                                                           |

| RX_ER | 28   | PU    | 3 或 4 | SD_EN：如果启用了 FX_EN，则当设置为“1”时，会在 LED_1 上启用高电平有效 100BASE-FX 信号检测。可以使用光纤通用配置寄存器 ( FIBER GENCFG，寄存器 0x0465 ) 更改极性。 |

**表 2-13. 0x0465 光纤通用配置寄存器 (FIBER GENCFG)**

| 位 | 名称                | 类型  | 默认值 | 功能                                                                                                                                                                                                        |

|---|-------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 100Base-FX 信号极性检测 | R/W | 0   | 100Base-FX 信号极性检测：1 = 信号检测为低电平有效 0 = 信号检测为高电平有效。当设置为高电平有效时，如果 SD 引脚检测到低电平状态 ( SD = “0” )，链路将会断开。当设置为低电平有效时，如果 SD 引脚检测到高电平状态 ( SD = “1” )，链路将会断开。注意：要在 LED_1 ( 引脚 #24 ) 上启用 100BaseFX 信号检测，请设置 SD_EN = “1” |

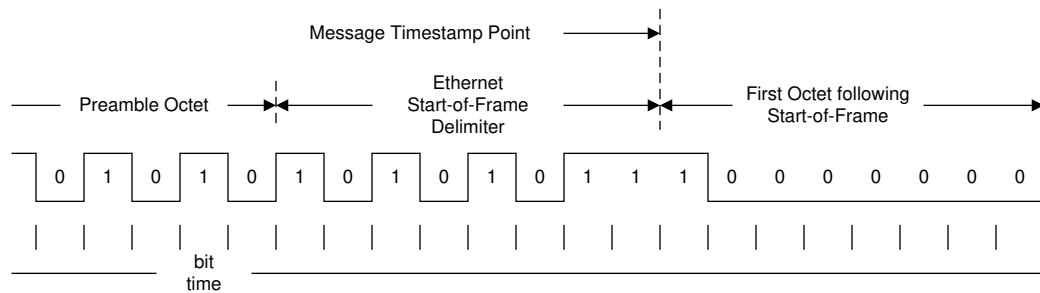

### 2.3.5 调试帧起始检测

SFD 上的 IEEE 1588 指示脉冲可以被传送至下列任一引脚：LED\_0、LED\_1 (GPIO1)、COL (GPIO2)、RX\_D3 (GPIO3)、INT/PWDN\_N 和 CRS。可通过寄存器 0x003F 来调整脉冲的确切时序。

图 2-13. IEEE 1588 消息时间戳点

下列三个寄存器可用于控制 IEEE 1588 发送和接收指示的路由：

1. 0x003E：将发送和接收指示路由到 LED\_0 (GPIO1)、COL (GPIO2)、CRS 和 INT/PWDN\_N

2. 0x0462/0x0463：IO MUX GPIO 控制寄存器 1/2，可实现额外的引脚选择和 GPIO 控制的集中位置

在寄存器 IOCTRLx 中启用/设置 RX\_SFD 和 TX\_SFD 引脚后，写入以下两个寄存器：

- 程序（寄存器 0x0456 = 值 0x000A）

- 程序（寄存器 0x04A0 = 值 0x1080）

- 请注意，寄存器 0x04A0 将启用“位 7 : WOL”。这有助于提高 SFD 检测的精度，但并非必须更改。这不会导致 PHY 检测 WoL 数据包，因为 WoL 功能需要额外的寄存器配置。

**备注**

必须执行软件复位才能加载这些寄存器值（寄存器 0x001F = 值 0x4000）。

### 2.3.6 合规性

可以进行 IEEE 合规性测量以验证信令特性。有关这些测量以及如何正确配置的详细信息，请参阅应用手册[如何配置 DP8382x 以进行以太网合规性测试](#)。

## 2.4 MII 运行状况检查

本节深入介绍器件运行状况检查，用于确保器件的 MII 部分正常运行。

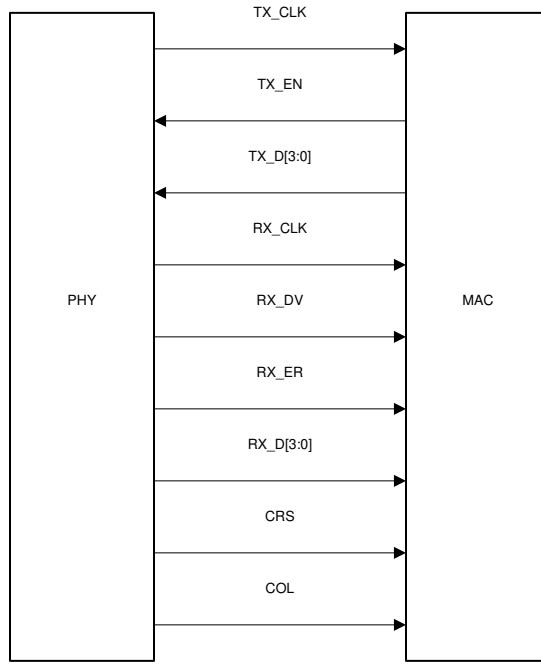

### 2.4.1 MII 检查

媒体独立接口是一个同步 4 位宽半字节数据接口，用于将 PHY 连接到 MAC。MII 完全符合 IEEE 802.3-2002 第 22 条。

表 2-14 中总结了 MII 信号。

表 2-14. MII 信号

| 功能      | 引脚        |

|---------|-----------|

| 数据信号    | TX_D[3:0] |

|         | RX_D[3:0] |

| 发送和接收信号 | TX_EN     |

|         | RX_DV     |

| 线路状态信号  | CRS       |

|         | COL       |

| 时钟      | TX_CLK    |

|         | RX_CLK    |

图 2-14. MII 信令

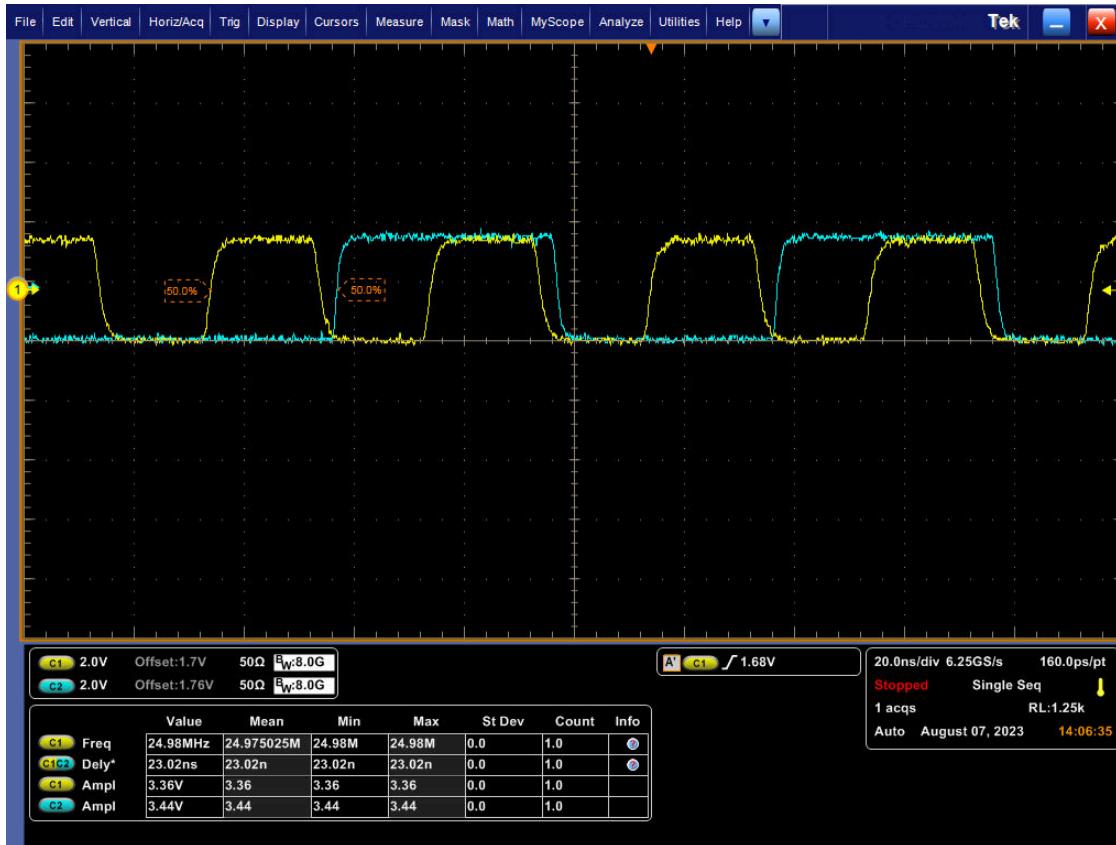

参考下面的波形来验证 100BASE-Tx MII 模式下的预期 MAC 数据和时钟信号。表 2-15 显示了从数据表获取的显示在波形中的规格。如果 PHY 未建立链接或链接速率为 10Mbps，则 MII 信令需要为 2.5MHz；如果链接速率为 100Mbps，则需要为 25MHz。请注意，TX\_CLK 和 RX\_CLK 都是 PHY 的输出。

如果怀疑 MAC 总线 (TX 或 RX) 有问题，请探测布线接收器侧的线路，确保满足接收器的建立时间和保持时间以及 VIH/VIL 要求。违反这些规范的典型症状是，当 PHY 指示干净的流量 (Reg 0x15) 时，MAC 上出现数据包错误。

表 2-15. 100M MII 接收时序

| 测试条件                                     | 最小值 | 典型值 | 最大值 | 单位 |

|------------------------------------------|-----|-----|-----|----|

| RX_CLK 高电平/低电平时间                         | 16  | 20  | 24  | ns |

| RX_D[3:0]、RX_ER、RX_DV 相对于 RX_CLK 上升的延迟时间 | 10  |     | 30  | ns |

表 2-16. 100M MII 传输时序

| 测试条件                                 | 最小值 | 典型值 | 最大值 | 单位 |

|--------------------------------------|-----|-----|-----|----|

| TX_CLK 高电平/低电平时间                     | 16  | 20  | 24  | ns |

| TX_D[3:0]，TX_ER、TX_EN 设置为 TX_CLK     | 10  |     |     | ns |

| TX_D[3:0]，来自 TX_CLK 的 TX_ER、TX_EN 保持 | 0   |     |     | ns |

表 2-17. 10M MII 接收时序

| 测试条件                                     | 最小值 | 典型值 | 最大值 | 单位 |

|------------------------------------------|-----|-----|-----|----|

| RX_CLK 高电平/低电平时间                         | 160 | 200 | 240 | ns |

| RX_D[3:0]、RX_ER、RX_DV 相对于 RX_CLK 上升的延迟时间 | 100 |     | 300 | ns |

表 2-18. 10M MII 传输时序

| 测试条件                             | 最小值 | 典型值 | 最大值 | 单位 |

|----------------------------------|-----|-----|-----|----|

| TX_CLK 高电平/低电平时间                 | 190 | 200 | 240 | ns |

| TX_D[3:0]，TX_ER、TX_EN 设置为 TX_CLK | 25  |     |     | ns |

表 2-18. 10M MII 传输时序 (续)

| 测试条件                                 | 最小值 | 典型值 | 最大值 | 单位 |

|--------------------------------------|-----|-----|-----|----|

| TX_D[3:0]，来自 TX_CLK 的 TX_ER、TX_EN 保持 | 0   |     |     | ns |

图 2-15. MII 的 RX\_CLK 和 RX\_D0 时序 (蓝色波形 (通道 2) = RX\_CLK, 紫色波形 (通道 3) = RX\_D0 )

#### 2.4.2 RMII 检查

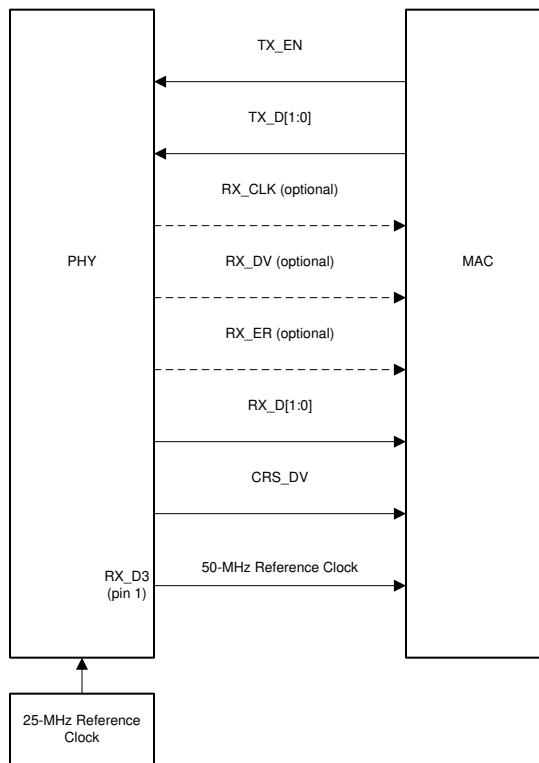

DP83822 包含了简化媒体独立接口 (RMII) 协会提供的 RMII 规范中指定的 RMII。从架构上讲，RMII 规范在 MII 的任一侧提供了一个额外的调节层，但在没有 MII 的情况下可实现。DP83822 提供两种类型的 RMII 工作模式：RMII 住工作模式和 RMII 从工作模式。

RMII 主工作模式下，通过连接 XI 引脚的 25MHz CMOS 级振荡器或连接 XI 与 XO 引脚的 25MHz 晶体为 DP83822 供电。

在 RMII 从工作模式下，DP83822 由连接到 XI 引脚的 50MHz CMOS 电平振荡器供电，并且与 MAC 共用同一个时钟。

以三个 GPIO 中的任何一个为基准的 50MHz 输出时钟连接到 MAC。

#### 备注

如果通过自举配置 RMII 主模式，则将在 RX\_D3 (GPIO3) 上自动启用 50MHz 输出时钟。

RMII 规范具有以下特性：

- 支持 100BASE-FX、100BASE-TX 和 10BASE-T。

- 从 MAC 到 PHY (或来自外部源) 的单个时钟基准

- 提供独立的 2 位宽发送和接收数据路径

- 使用与 MII 接口相同的 CMOS 信号电平

该模式下，发送与接收路径均采用 50MHz 内部基准时钟，每个时钟周期可传输两比特数据。

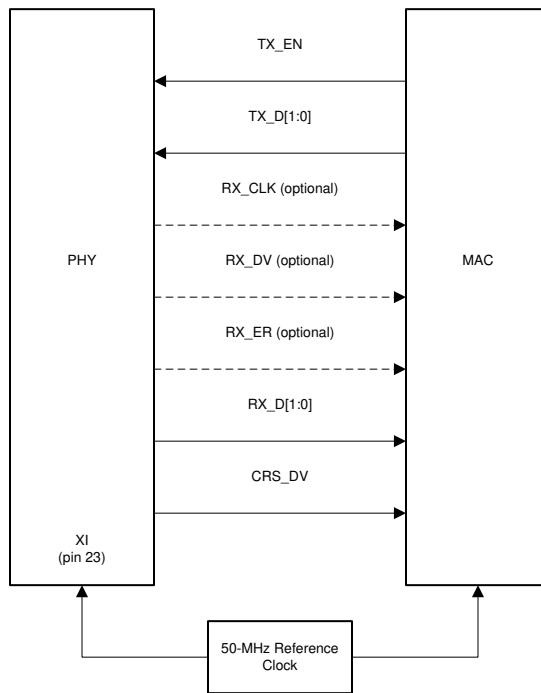

表 2-19 中总结了 RMII 信号。

表 2-19. RMII 信号

| 功能      | 引脚        |

|---------|-----------|

| 数据信号    | TX_D[1:0] |

|         | RX_D[1:0] |

| 发送和接收信号 | TX_EN     |

|         | CRS_DV    |

图 2-16. RMII 从信令

图 2-17. RMII 主信令

**备注**

有关在 RMII 中继器模式下使用 DP83822 的信息，请参阅 [DP83822 RMII 中继器模式](#)。

表 2-20. RMII 发送时序

| 测试条件                                            | 最小值 | 典型值 | 最大值 | 单位 |

|-------------------------------------------------|-----|-----|-----|----|

| XI 时钟周期                                         | 20  |     |     | ns |

| <b>TX_D[1:0]</b> 和 TX_EN 数据相对于 XI 上升沿的建立时间      | 1.4 |     |     | ns |

| <b>TX_D[1:0]</b> 和 TX_EN 数据相对于 XI 上升沿的保持时间      | 2   |     |     | ns |

| RMII 主时钟 (RX_D3 时钟) 周期                          | 20  |     |     |    |

| 占空比                                             | 35  | 65  | %   |    |

| <b>TX_D[1:0]</b> 和 TX_EN 数据相对于 RMII 主时钟上升沿的建立时间 | 4   |     |     | ns |

| <b>TX_D[1:0]</b> 和 TX_EN 数据相对于 RMII 主时钟上升沿的保持时间 | 2   |     |     | ns |

表 2-21. RMII 接收时序

| 测试条件                                            | 最小值 | 典型值 | 最大值 | 单位 |

|-------------------------------------------------|-----|-----|-----|----|

| XI 时钟周期                                         | 20  |     |     | ns |

| <b>TX_D[1:0]</b> 和 TX_EN 数据相对于 XI 上升沿的建立时间      | 1.4 |     |     | ns |

| <b>TX_D[1:0]</b> 和 TX_EN 数据相对于 XI 上升沿的保持时间      | 2   |     |     | ns |

| RMII 主时钟 (RX_D3 时钟) 周期                          | 20  |     |     |    |

| 占空比                                             | 35  | 65  | %   |    |

| <b>TX_D[1:0]</b> 和 TX_EN 数据相对于 RMII 主时钟上升沿的建立时间 | 4   |     |     | ns |

表 2-21. RMII 接收时序 (续)

| 测试条件                                     | 最小值 | 典型值 | 最大值 | 单位 |

|------------------------------------------|-----|-----|-----|----|

| TX_D[1:0] 和 TX_EN 数据相对于 RMII 主时钟上升沿的保持时间 | 2   |     |     | ns |

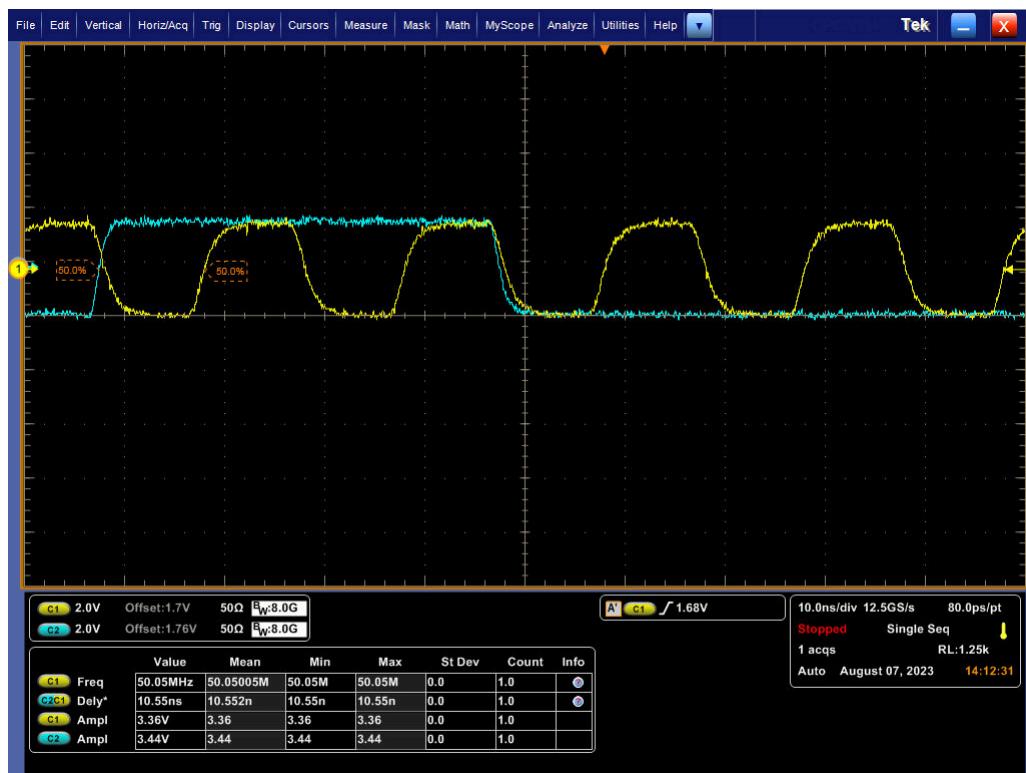

TX\_D[1:0] 上的数据以 RMII 主模式和从模式下的 50MHz 时钟为基准锁存在 PHY 上。RX\_D[1:0] 上的数据以 50MHz 时钟为基准提供。此外，CRS\_DV 可被配置为 RX\_DV 信号。它可以通过一种更简单的方法恢复接收数据，而无需将 RX\_DV 与 CRS\_DV 指示分开。

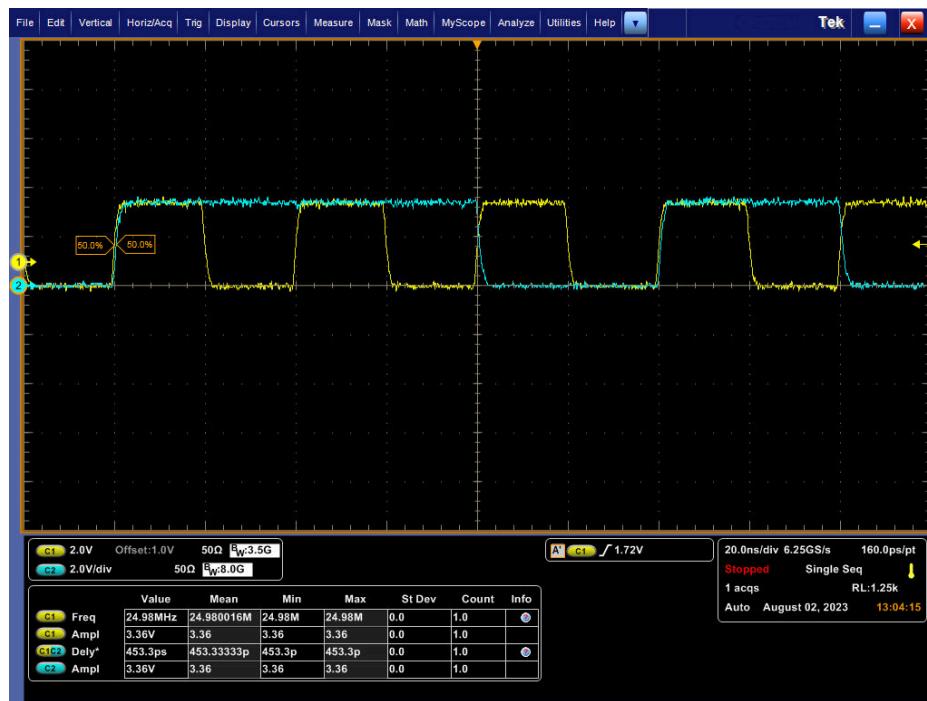

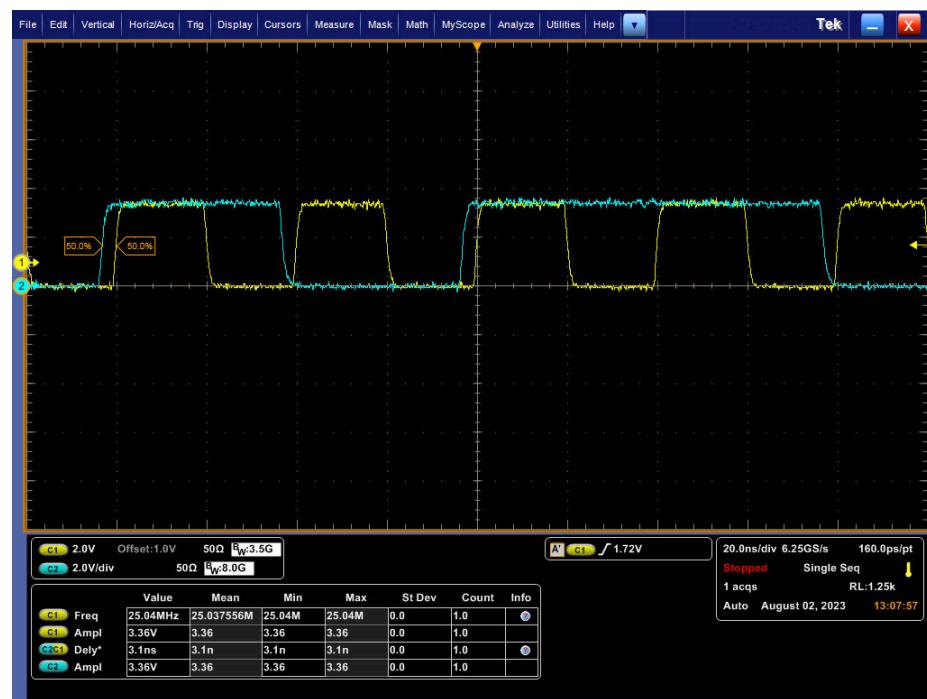

图 2-18. RMII 的 RX\_CLK 和 RX\_D0 时序 (黄色波形 (通道 1) = RX\_CLK, 蓝色波形 (通道 2) = RX\_D0 )

有关简化媒体独立接口的更多信息，请参阅“[DP83822 低功耗耐用型 10/100Mbps 以太网物理层收发器](#)”数据表的简化媒体独立接口(RMII)部分。

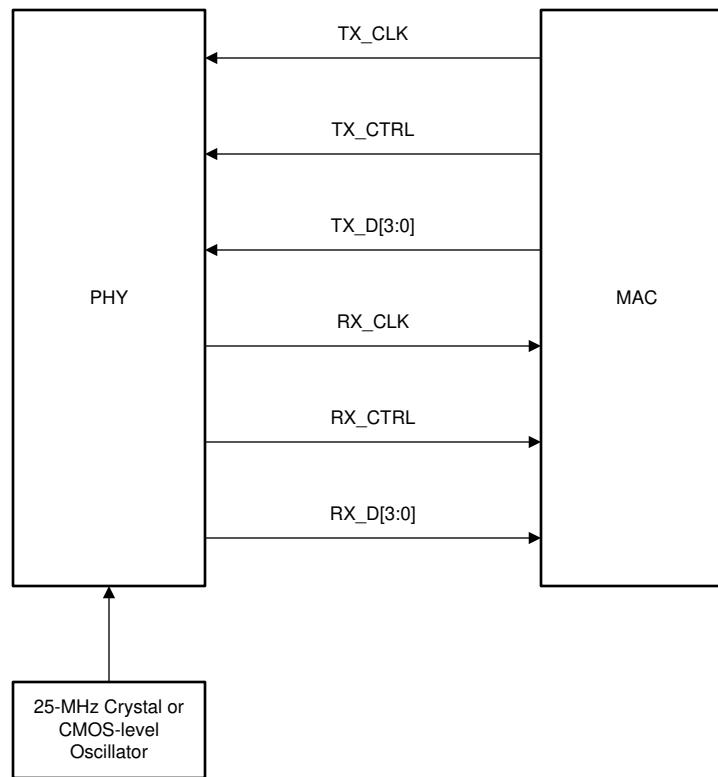

#### 2.4.3 RGMII 检查

表 2-22 中总结了 RGMII 信号。

表 2-22. RGMII 信号

| 功能      | 引脚        |

|---------|-----------|

| 数据信号    | TX_D[3:0] |

|         | RX_D[3:0] |

| 发送和接收信号 | TX_CTRL   |

|         | RX_CTRL   |

| 时钟      | TX_CLK    |

|         | RX_CLK    |

图 2-19. RGMII 信令

为了使 MAC 能够从 PHY 发送和接收正确的数据，必须选择正确的 RGMII 模式，使得 PHY 和 MAC 不会同时处于 TX 和 RX 側的对齐模式或移位模式。表 2-23 列出了正确的 RGMII 延迟配置。

参考下面的波形来验证 RGMII 模式下的预期 MAC 数据和时钟信号。表 2-23 显示了从器件特定数据表获取的显示在波形中的规格。

表 2-23. RGMII 移位配置

| MAC 配置         | 所需的 PHY 配置     |

|----------------|----------------|

| RX 側的 RGMII 对齐 | RX 側的 RGMII 移位 |

| RX 側的 RGMII 移位 | RX 側的 RGMII 对齐 |

| TX 側的 RGMII 对齐 | TX 側的 RGMII 移位 |

| TX 側的 RGMII 移位 | TX 側的 RGMII 对齐 |

图 2-20. RGMII 对齐模式下的 RX\_CLK 和 RX\_D0 时序 ( 黄色波形 ( 通道 1 ) = RX\_CLK , 蓝色波形 ( 通道 2 ) = RX\_D0 )

图 2-21. RGMII RX 移位模式下的 RX\_CLK 和 RX\_D0 时序 ( 黄色波形 ( 通道 1 ) = RX\_CLK , 蓝色波形 ( 通道 2 ) = RX\_D0 )

对于 RGMII RX 移位模式，请确认 RX\_CLK 移位 3.5ns；对于 RGMII TX 时钟移位，请确认 TX\_CLK 移位 3.5ns。

表 2-24. RGMII 输入时序规格

| 参数                        | 测试条件                                   | 最小值 | 典型值 | 最大值 | 单位 |

|---------------------------|----------------------------------------|-----|-----|-----|----|

| T <sub>cyc</sub>          | TX_CLK/时钟周期时长                          | 36  | 40  | 44  | ns |

| T <sub>setup(align)</sub> | TX_D[3:0], TX_CTRL 设置至 TX_CLK ( 对齐模式 ) | 1   | 2   |     | ns |

| T <sub>hold(align)</sub>  | TX_D[3:0], TX_CTRL 保持至 TX_CLK ( 对齐模式 ) | 1   | 2   |     | ns |

表 2-25. RGMII 输出时序规格

| 参数                           | 测试条件                                             | 最小值  | 典型值 | 最大值 | 单位 |

|------------------------------|--------------------------------------------------|------|-----|-----|----|

| T <sub>skew(align)</sub>     | RX_D[3:0], RX_CLK 后的 RX_CTRL 延迟 ( 对齐模式 )         | -500 | 0   |     | ps |

| T <sub>setup(shift)</sub>    | RX_D[3:0], RX_CLK 后的 RX_CTRL 延迟 ( 已启用移位模式，默认设置 ) | 1.2  | 2   |     | ns |

| T <sub>cyc</sub>             | RX_CLK/时钟周期时长                                    | 36   | 40  | 44  | ns |

| Duty_G                       | RX_CLK/占空比                                       | 40   | 50  | 60  | %  |

| T <sub>r/T<sub>f</sub></sub> | RX_CLK/上升下降时间 ( 20% 至 80% )                      |      |     | 750 | ps |

## 2.5 环回和 PRBS

### 2.5.1 环回模式

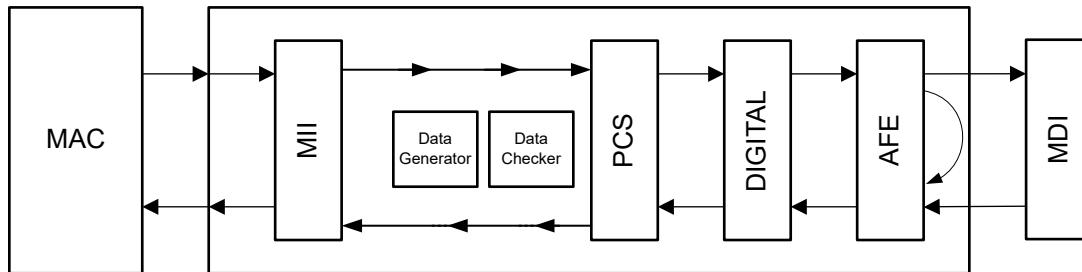

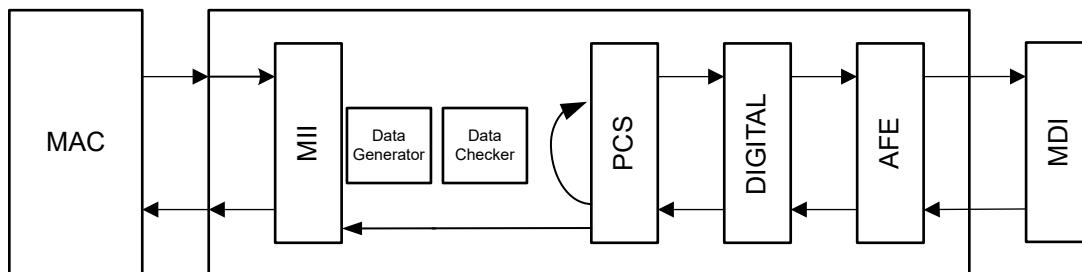

提供了多个环回测试选项，可用于测试和验证 PHY 中的各种功能块。通过启用环回模式，您可以使用 xMII/PCS/Digital/AFE 环回检查 MAC 与 PHY 之间的连接，以及使用反向环回检查 PHY 与 MDI 之间的连接。

图 2-22. MAC 侧模拟环回模式示例

图 2-23. 方框图、反向（电缆侧）环回模式

建议使用模拟环回来检查 MAC 和 PHY 之间的完整数据路径，而反向环回与链路伙伴一起使用以验证 PHY 和 MDI ( 链路伙伴 ) 之间的数据路径。

该器件还包含内部 PRBS 内置自检 (BIST) 电路，可适应电路内测试或诊断。可以使用各种环回模式执行 BIST，以通过生成包含可变内容的封包化数据来隔离数据路径特定部分的任何问题。提供了脚本来启用数据生成器和校验器以及各种环回模式。

图 2-24. 具有环回功能的数据生成器和校验器

### 2.5.2 通过 MAC 发送和接收数据包

如果可以使用 MAC 生成和检查数据包，并且 PHY 有一个具有反向环回功能的工作链路伙伴，请按如下方式验证完整数据路径：

1. 为 PHY 供电并将其连接到 MAC 和一个正常工作的链路伙伴。

2. 在链路伙伴上启用反向环回。

3. 将测试数据包从 MAC 发送到 PHY。

4. 验证 MAC 是否接收相同的测试数据包。

如果 MAC 接收到相同的测试数据包而未出现问题，则通过 MAC → PHY → 链路伙伴 (MDI) 的完整数据路径是有效的。如果此测试未通过，则执行模拟环回以隔离数据路径上的问题（在运行模拟环回之前断开电缆侧连接）：

1. 为 PHY 供电并将其连接到 MAC。

2. 在 PHY 上启用模拟环回（写入寄存器  $0x0016 = 0x0108$ ）。

3. 将测试数据包从 MAC 发送到 PHY。

4. 验证 MAC 是否接收相同的测试数据包。

如果 MAC 接收到相同的测试数据包，则通过 MAC → PHY 的数据路径有效，并且问题已与 MDI 数据路径隔离。如果此测试未通过，则问题可能出在 MAC 接口上。要检查 MAC 接口，请参见 [MII 检查](#)。

下面是执行模拟环回的寄存器读取和写入的示例序列：

```

// Analog Loopback

begin

001F 8000 //Hard Reset

0000 2100 //Disables Auto-Neg, Selects 100 Mbps

0016 0108 //Select Analog Loopback

030B 3380 //This helps PRBS LOCK

0016 3108 //Enables PRBS Checker Config & Packet Generation Enable

//After you write '3108' the register should Read 3b04. (Bit 11 & 9 go high)

001B 807D //Lock Error Counter's Value

001B

//after running this test check register 0010 bit 0 should be 1

end

```

### 2.5.3 通过 BIST 发送和接收数据包

如果无法通过 MAC 生成和检查数据包，请使用外部数据包生成器或内部 PRBS 数据包生成和检查功能来验证数据路径。使用 PRBS 和正常工作的链路伙伴执行反向环回，如下所示：

1. 为 PHY 供电并将其连接到链路伙伴。

2. 在 PHY 上启用 PRBS 数据包生成（将 0x16 写入 5000）。

3. 在链路伙伴上启用反向环回

4. 等待至少一秒钟，然后检查 PHY 上的 PRBS 锁定状态（读取寄存器 0x17[11:10]）。

如果寄存器 0x17[11] 为高电平，则通过 PHY → MDI 的数据路径有效。如果此测试未通过，则问题可能出在 PHY 的内部数据路径或 MDI 上。要验证内部数据路径，请使用以下脚本执行带有模拟环回的 PRBS。如果内部数据路径有效，则问题将与 MDI 隔离（假设链路伙伴正常工作）。

以下代码是使用两个 DP83822 PHY 时，为执行 BIST 而进行的寄存器读取和写入的示例序列：

```

// Reverse Loopback on PHY

begin

001F 8000 //Hard Reset

0000 2100 //Disables Auto-Neg, Selects 100 Mbps

0016 7100 //Enables PRBS packet generation

0016 // check PRBS lock status on bit 10 high

end

// Reverse Loopback on Link Partner

begin

001F 8000 //Hard Reset

0000 2100 //Disables Auto-Neg, Selects 100 Mbps

0016 0110 //Select Reverse Loopback

end

```

### 3 工具和参考

#### 3.1 DP83822 寄存器访问

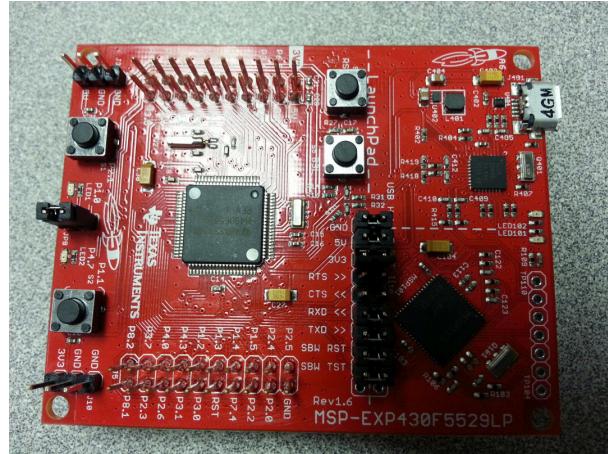

如果应用中不能轻松访问寄存器，可从 TI 获取 USB-2-MDIO GUI，它可与 MSP430 LaunchPad 搭配使用，并可通过 TI 网上商店购买。GUI 支持读取和写入寄存器以及运行脚本文件。它可与 DP83822 和 TI 以太网产品系列中的其他器件搭配使用。USB-2-MDIO 用户指南和 GUI 可从以下位置下载：<http://www.ti.com.cn/tool/cn/usb-2-mdio>。

图 3-1. USB-2-MDIO GUI

图 3-2. MSP430 LaunchPad

下面是一个示例脚本，也可以在“Help”菜单的 USB-2-MDIO GUI 中找到：

```

// This is how you make a comment. All scripts must start with 'begin'

begin

// To read a register, all you need to do is put down the 4 digit

// HEX value of the registers (from 0000 to FFFF)

// Example to read registers 0001, 000A, and 0017

0001

000A

0017

// To write a register, all you need to do is put down the 4 digit

// HEX value of the register (from 0000 to FFFF) followed by the

// HEX you desire to configure the register to (from 0000 to FFFF)

// Example to write 2100 to register 0000 and

// Example to write 0110 to register 0016

0000 2100

0016 0110

// You must end the script by adding 'end' once you are finished

end

```

由 IEEE 802.3 定义的串行管理接口是单主总线。MDC 时钟由总线主控（通常是以太网 MAC）生成。要使用 USB-2-MDIO GUI，必须在 MSP430 LaunchPad 与 DP83822 MDIO 和 MDC 引脚之间直接建立连接。

- MSP430 引脚 4.2 → PHY 的 MDIO 引脚

- MSP420 引脚 4.1 → PHY 的 MDC 引脚

## 3.2 Linux 上的软件和驱动程序调试

PHY 在 Linux 系统上运行所需的两个基本元件是器件树和驱动程序文件，DP83822 驱动程序可在此处找到。以下是器件树外观的示例格式。

```

mdio0 {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@0 {

reg = <0>;

rx-internal-delay-ps = <1>;

tx-internal-delay-ps = <1>;

};

};

```

---

### 备注

可以在以下路径中找到示例绑定文件：[root/Documentation/devicetree/bindings/net/ti,dp83822.yaml](#)。

---

### 3.2.1 普通端子输出和解决方案

使用终端命令“dmesg | grep mdio”，从软件的角度来看，可能会有几条线索显示是什么原因导致 PHY 无法正常工作。

```

$ dmesg | grep "mdio"

```

可能的输出之一如下所示：

```

$ mdio_bus xxx.ethernet-x: MDIO device at address 8 is missing

```

该消息指示 PHY 未在 MDIO 总线上找到，这可能是由多个问题引起的。一种常见原因是器件树缺失或不正确，但也可能是由于 PHY 无法正常工作或 SMI 连接不良。

一旦可以在 MDIO 总线上检测到 PHY，另一个常见错误消息如下所示：

```

$ Generic PHY xxx.ethernet-x: attached PHY driver [Generic PHY]

```

该消息指示相应 PHY 的驱动程序文件未正确加载或根本不存在，并且加载到通用驱动程序中的 Linux 很可能无法与 PHY 配合使用。在这种情况下，请验证驱动程序是否已成功编译并已添加到 Linux，并确保驱动程序与所使用的 PHY 型号相匹配。

最后，可能会显示如下类似消息：

```

$ am65-cpsw-nuss c000000.ethernet eth3: PHY [c000f00.mdio:05] driver [TI DP83822] (irq= POLL)

```

该消息显示 PHY 已加载正确的驱动程序并成功检测到。运行 ifconfig 验证网络接口是否存在。

当 PHY 成功识别为网络适配器时的示例 ifconfig 输出：

```

root@j7-evm:~# ifconfig

eth0: flags=4099<UP,BROADCAST,MULTICAST> mtu 1500 metric 1

ether 24:76:25:a2:62:8b txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

lo: flags=73<UP,LOOPBACK,RUNNING> mtu 65536 metric 1

inet 127.0.0.1 netmask 255.0.0.0

inet6 ::1 prefixlen 128 scopeid 0x10<host>

loop txqueuelen 1000 (Local Loopback)

RX packets 82 bytes 6220 (6.0 KiB)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 82 bytes 6220 (6.0 KiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

```

下一步是验证数据传输是否成功。

## 4 总结

本应用手册提供了评估新应用和确认预期功能的建议流程。这些分步建议有助于简化 DP83822 设计的电路板启动和初始评估。

## 5 参考资料

有关 EMC.EMI 合规性测试的硬件和软件配置的信息，请参阅以下文档。

德州仪器 (TI) , [如何通过 IEEE 以太网合规性测试](#)应用报告。

德州仪器 (TI) , [如何配置 DP838xx 进行以太网合规性测试](#)应用报告。

## 6 修订历史记录

| Changes from Revision * (December 2023) to Revision A (July 2025) | Page |

|-------------------------------------------------------------------|------|

| • 更新了整个文档中的表格、图和交叉参考的编号格式更新了文档的整体结构，以提高可读性。 .....                 | 1    |

| • 添加了“电源斜升时序序列检查”部分。 .....                                        | 3    |

| • 添加了节 <a href="#">2.2.1.1</a> .....                              | 4    |

| • 添加了“探测 Rbias 引脚”部分。将 Rbias 从 2.7V 更新为 1V。 .....                 | 5    |

| • 添加了节 <a href="#">2.3.1</a> .....                                | 11   |

| • 将 MSE 链路质量范围表从十进制更新为十六进制。 .....                                 | 14   |

| • 添加了 <a href="#">合规性</a> 一节。 .....                               | 17   |

| • 添加了 <a href="#">RMII 检查</a> 部分 .....                            | 19   |

| • 添加通过 <a href="#">MAC</a> 发送和接收数据包部分 .....                       | 26   |

| • 添加了 <a href="#">摘要</a> 部分 .....                                 | 31   |

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#))、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025 , 德州仪器 (TI) 公司

最后更新日期 : 2025 年 10 月