*Application Note*

# 如何进行 TI PCIe Gen5 转接驱动器调优

Nasser Mohammadi, Evan Su

## 摘要

PCI-Express ( 或 PCIe ) 5.0 链路在 16GHz 时提供 36dB 的总损耗预算。通常情况下，很多系统的 PCIe 链路会超出损耗预算，要么虽然能减少可用损耗预算但实现方案不甚理想，要么找不到可减少损耗预算的理想方案。具有集成信号调节功能的 TI PCIe Gen5 转接驱动器可以降低通道损耗引起的确定性抖动，增加损耗预算，并最终将 PCIe 5.0 链路的覆盖范围提高多达 45%。本应用手册提供了有关使用 DS320PR810 和 DS320PR1601 提高信号完整性和扩覆盖范围展的指导。PCIe 还适用于分别具有集成多路复用器和解复用器的 SN75LVPE5421 和 SN75LVPE5412 等相关器件。

## 内容

|                             |           |

|-----------------------------|-----------|

| <b>1 引言</b>                 | <b>2</b>  |

| <b>2 器件概述</b>               | <b>2</b>  |

| 2.1 接收器均衡                   | 4         |

| 2.2 转接驱动器线性度                | 5         |

| 2.3 带有线性转接驱动器的 PCIe 链路      | 5         |

| 2.4 转接驱动器 EQ 调优             | 8         |

| <b>3 优化 CTLE 和增益选择的通用指南</b> | <b>12</b> |

| <b>4 PCIe 热复位</b>           | <b>13</b> |

| <b>5 总结</b>                 | <b>15</b> |

| <b>6 参考文献</b>               | <b>15</b> |

| <b>7 修订历史记录</b>             | <b>16</b> |

## 插图清单

|                                                       |    |

|-------------------------------------------------------|----|

| 图 2-1. DS320PR810 方框图                                 | 2  |

| 图 2-2. DS320PR1601 方框图                                | 3  |

| 图 2-3. PCIe 链路图                                       | 5  |

| 图 2-4. 具有 20dB 前置通道损耗、20dB 至 25dB 后置通道损耗的 PCIe 链路分析示例 | 6  |

| 图 2-5. 具有 30dB 前置通道损耗、20dB 至 25dB 后置通道损耗的 PCIe 链路分析示例 | 7  |

| 图 2-6. 具有 35dB 前置通道损耗、20dB 至 25dB 后置通道损耗的 PCIe 链路分析示例 | 7  |

| 图 2-7. PCI-SIG AIC RX 校准规范                            | 8  |

| 图 2-8. PCI-SIG 系统 RX 校准规范                             | 8  |

| 图 2-9. PCIe Gen5 SI、CBB 和 CLB 电路板                     | 9  |

| 图 2-10. RX 合规性方框图                                     | 9  |

| 图 2-11. AIC 测试概述                                      | 10 |

| 图 4-1. 转接驱动器 RX 检测功能                                  | 13 |

| 图 4-2. 转接驱动器 PD 引脚的反相 PERST# 分配示例                     | 14 |

| 图 4-3. 具有两个输入信号的 PD 控制逻辑示例                            | 14 |

## 表格清单

|                                      |    |

|--------------------------------------|----|

| 表 2-1. TI PCIe Gen5 转接驱动器的通用 EQ 指数增强 | 4  |

| 表 2-2. 转接驱动器前后的 PCIe TX 预设值          | 5  |

| 表 2-3. 前置通道和后置通道损耗的器件性能              | 10 |

## 商标

所有商标均为其各自所有者的财产。

## 1 引言

在设计基于线性转接驱动器的线路卡时，调优 PCIe Gen5 线性转接驱动器是主要任务之一。线性特性很重要。PCIe 协商需要链路训练，以便在前置转接驱动器和后置转接驱动器（前置或后置通道损耗）曲线中实现适当的信号条件。为了实现这一目标，根复合体（RC）和端点（EP）之间会交换不同级别的预冲和后冲（或去加重），从而补偿整体通道损耗曲线。线性转接驱动器必须充当无缝实体，并在其线性区域中工作，以增强高频内容而又不会压缩信号。不正确的调优会压缩或过度均衡这些信号，从而导致性能下降和/或难以进行链路训练。由于该器件采用线性方式工作，因此转接驱动器两侧的连续时间线性均衡（CTLE）和决策反馈均衡（DFE）可以正常进行训练。

本应用手册讨论了转接驱动器与 PCIe 协商相关的主要特性，并提供了前置和后置通道损耗分析，以帮助微调和简化转接驱动器 CTLE 设置。本文档包含验证和系统级结果，提供了转接驱动器放置建议，概述了可能的 PCIe 链路扩展，并使用真实系统示例提供了转接驱动器分步调优说明。全面了解转接驱动器的功能、限制和调优步骤后，系统设计人员可更好地使用线性转接驱动器来扩展 PCIe 5.0 链路的覆盖范围。

## 2 器件概述

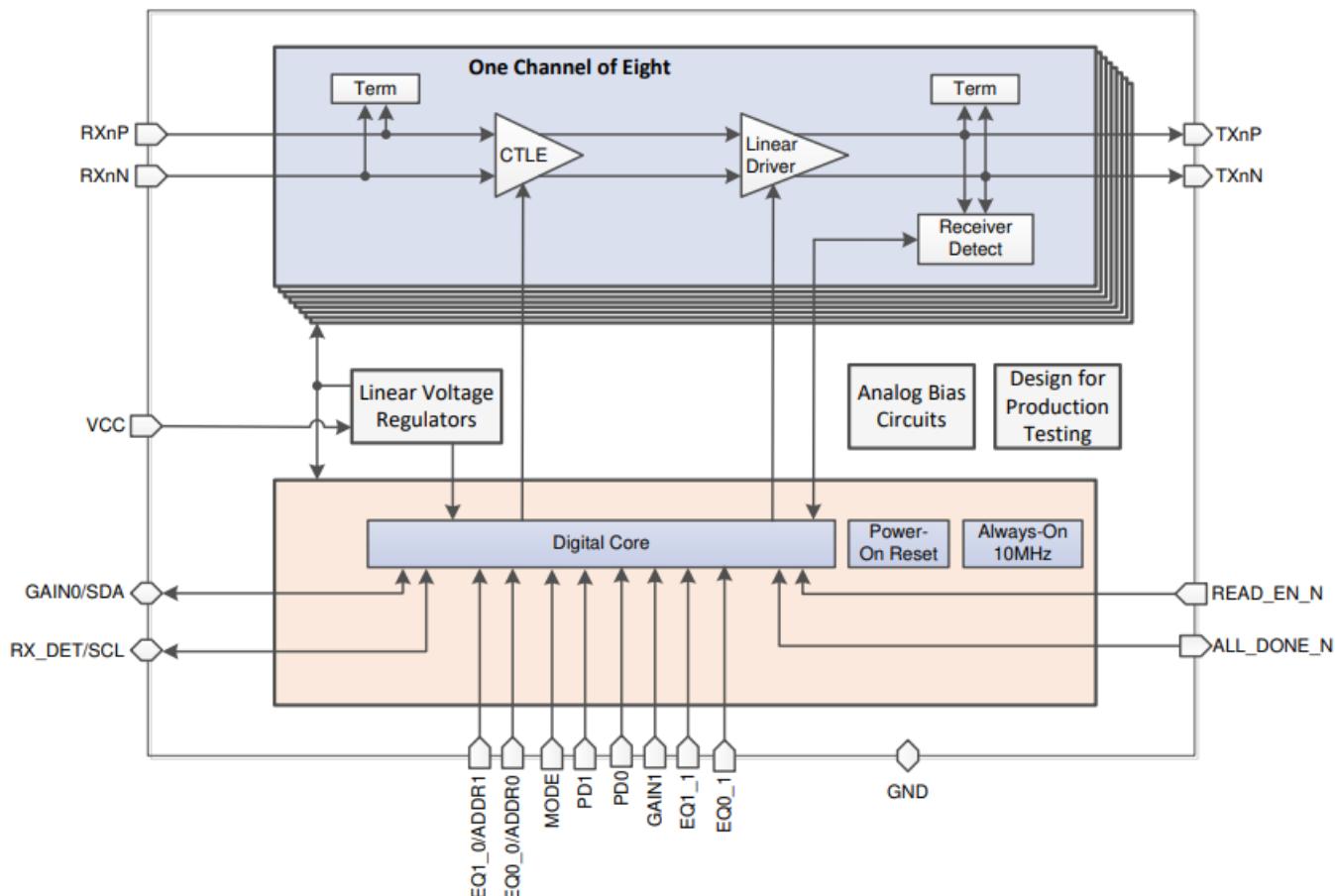

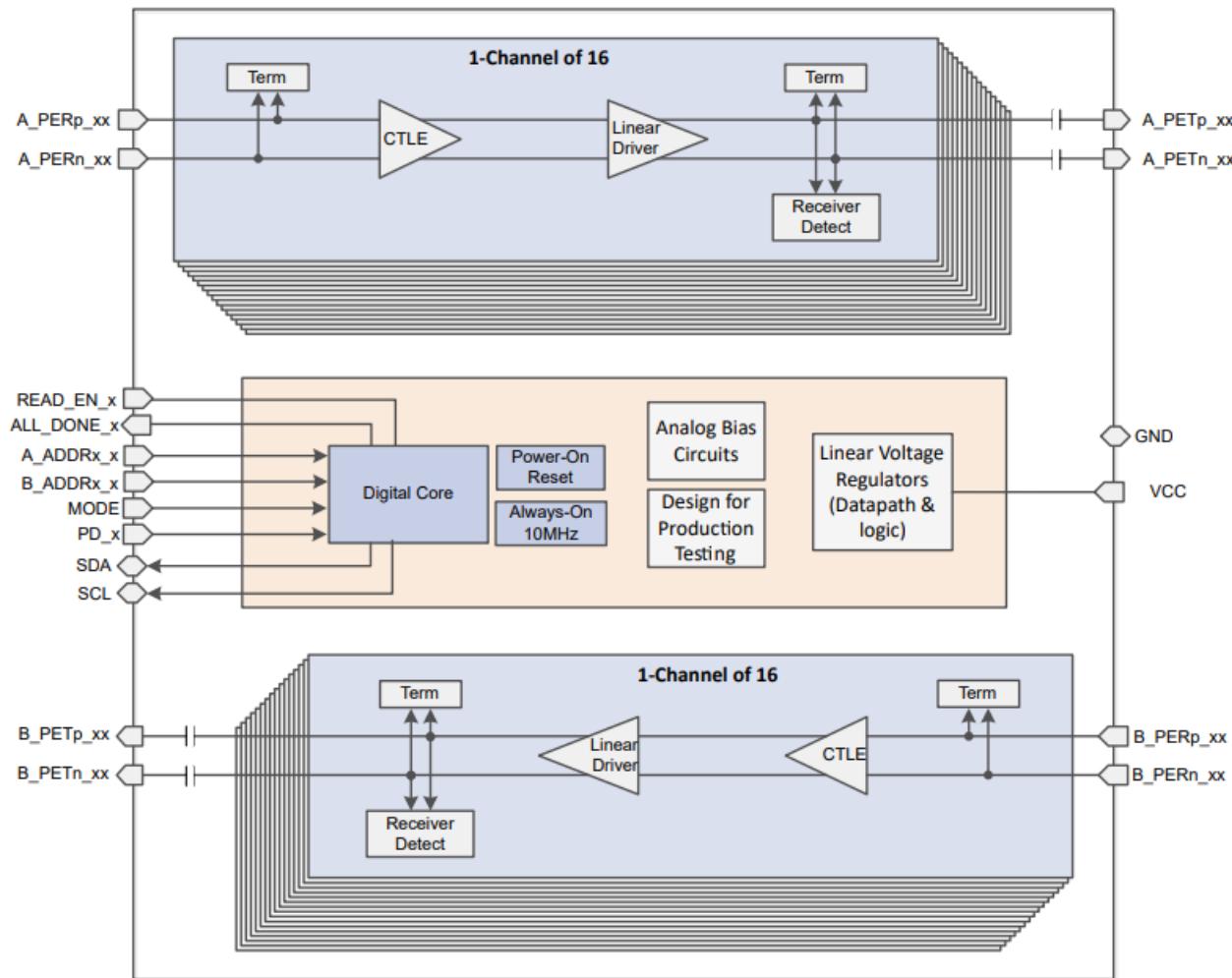

DS320PR810、DS320PR1601 和其他 PCIe Gen5 转接驱动器会放大受 ISI（符号间干扰）影响的传入信号的高频内容。这种放大是在增加极小 RMS 抖动的情况下完成的。PCIe Gen5 转接驱动器也支持 Gen4 和更低的速度。此外，这些器件与协议无关，可用于 SAS 和其他应用。

图 2-1. DS320PR810 方框图

图 2-2. DS320PR1601 方框图

## 2.1 接收器均衡

PCIe Gen5 转接驱动器具有一个连续时间线性均衡器 (CTLE) , 它运用高频增强和低频衰减功能来帮助均衡无源通道的频率制约型插入损耗。该器件具有 20 种均衡 (EQ) 升压和 5 种增益设置。增益设置为平坦增益 , 在整个带宽范围内均匀地增加信号强度。整体数据路径平坦增益 ( 直流和交流 ) 可以通过 SMBus/I2C 寄存器编程。大多数系统的默认建议为 0dB。设置转接驱动器的平坦增益和均衡时 , 必须确保直流和高频下的输出信号摆幅分别不超过器件的直流和交流线性范围。有关更多详细信息 , 请参阅编程指南。

表 2-1 介绍了 TI 的 PCIe Gen5 转接驱动器架构带来的 EQ 增强。每个 EQ 指数设置的实际增强 ( 以 dB 为单位 ) 相似 , 但不同的 PCIe Gen5 转接驱动器之间并不相同。有关完整的详细信息 , 请参阅 [各个器件数据表](#) 的特性说明中的表格。

表 2-1 仅用于说明 ; 进行设计时 , 请参阅器件数据表。

**表 2-1. TI PCIe Gen5 转接驱动器的通用 EQ 指数增强**

| 均衡选择  | 典型 EQ 增强       |                 |

|-------|----------------|-----------------|

|       | 8GHz 时的增益 (dB) | 16GHz 时的增益 (dB) |

| EQ 指数 |                |                 |

| 0     | 2.0            | 3.0             |

| 1     | 3.5            | 5.0             |

| 2     | 5.0            | 7.0             |

| 3     | 7.0            | 9.0             |

| 4     | 8.0            | 12.0            |

| 5     | 9.0            | 16.0            |

| 6     | 9.8            | 17.0            |

| 7     | 10.2           | 18.0            |

| 8     | 10.8           | 18.5            |

| 9     | 11.2           | 19.0            |

| 10    | 11.8           | 19.5            |

| 11    | 12.2           | 20.0            |

| 12    | 12.8           | 20.5            |

| 13    | 13.2           | 21.0            |

| 14    | 13.8           | 21.5            |

| 15    | 14.2           | 22.0            |

| 16    | 14.8           | 22.5            |

| 17    | 15.2           | 23.0            |

| 18    | 15.6           | 23.5            |

| 19    | 16.0           | 24.0            |

## 2.2 转接驱动器线性度

数据路径的线性度经过专门设计，可在保持接收器均衡有效的同时保留任何传输均衡。它能够实现无障碍的 PCIe 5.0 链路训练，可自动优化链路根复合体和端点侧的 PCIe TX 和 RX 均衡功能。表 2-2 所示为在通过转接驱动器传递预设之前和 PCIe TX 预设被重新驱动之后的典型 PCIe TX 预设值（预冲和去加重等级）。该数据是在遵循 PCI-Express 5.0 Base 规范的情况下测得的。请注意，预冲和后冲都完全在所需限值范围内。

表 2-2. 转接驱动器前后的 PCIe TX 预设值

| 预设 | PCIe 预设限值 |            | 在转接驱动器之后测量的典型值 |         |

|----|-----------|------------|----------------|---------|

|    | 推荐的预冲     | 推荐的后冲      | 预冲 (dB)        | 后冲 (dB) |

| P0 | 0         | -6 ± 1.5   | 0              | -5.69   |

| P1 | 0         | -3.5 ± 1.0 | 0              | -3.34   |

| P2 | 0         | -4.4 ± 1.5 | 0              | -3.9    |

| P3 | 0         | -2.5 ± 1.0 | 0              | -2.41   |

| P4 | 0         | 0          | 0              | 0       |

| P5 | 1.9 ± 1.0 | 0          | 1.97           | 0       |

| P6 | 2.5 ± 1.5 | 0          | 2.42           | 0       |

| P7 | 3.5 ± 1.0 | -6.0 ± 1.5 | 3.43           | -5.36   |

| P8 | 3.5 ± 1.0 | -3.5 ± 1.0 | 3.37           | -3.36   |

| P9 | 3.5 ± 1.0 | 0          | 3.36           | 0       |

## 2.3 带有线性转接驱动器的 PCIe 链路

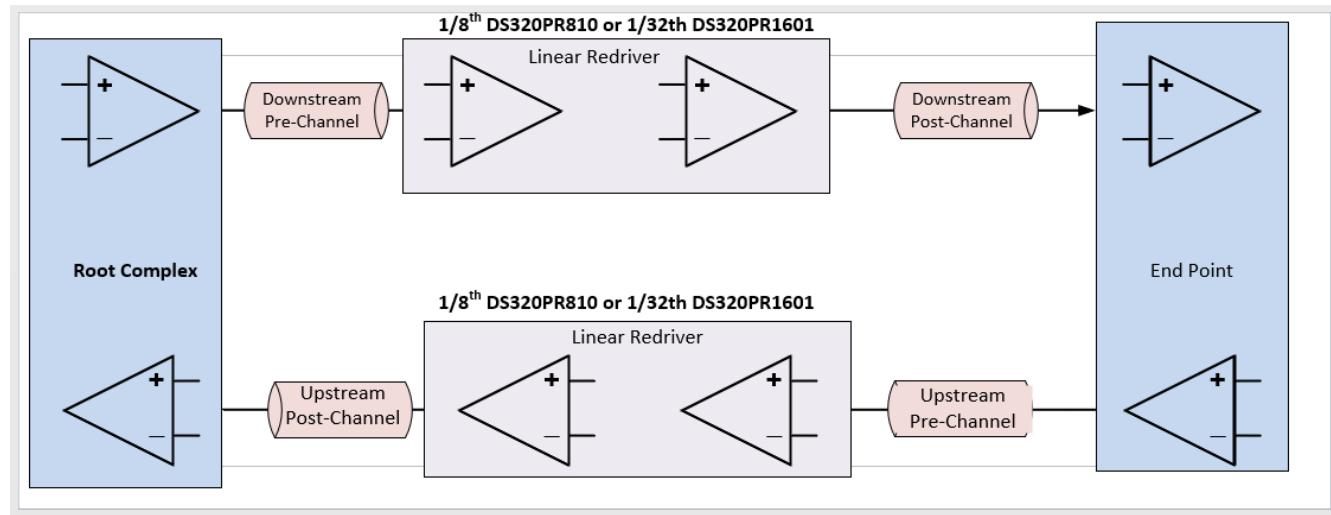

PCI-Express (PCIe) 链路通常具有 4 通道 (x4)、8 通道 (x8) 和 16 通道 (x16) 等宽度类型。PCIe 根复合体 (RC) 和 PCIe 端点 (EP) 之间的双向通信通过下游（从 RC 到 EP）和上游（从 EP 到 RC）通道进行。

图 2-3. PCIe 链路图

PCIe 发送器 (TX) 和转接驱动器之间的传输介质是前置通道，而转接驱动器和 PCIe 接收器 (RX) 之间的通道是后置通道，这说明了通道相对于转接驱动器的位置。需要注意的是，前置通道损耗补偿通过 PCIe TX 均衡和转接驱动器 CTLE 实现。

对于接近或超过 36dB 总系统损耗预算的系统，建议使用更高等级的低损耗材料，例如 Megtron-6，并建议配置转接驱动器以使 CPU 和转接驱动器之间的损耗约为 27dB 至 36dB，从而让转接驱动器能够补偿额外的系统损耗。

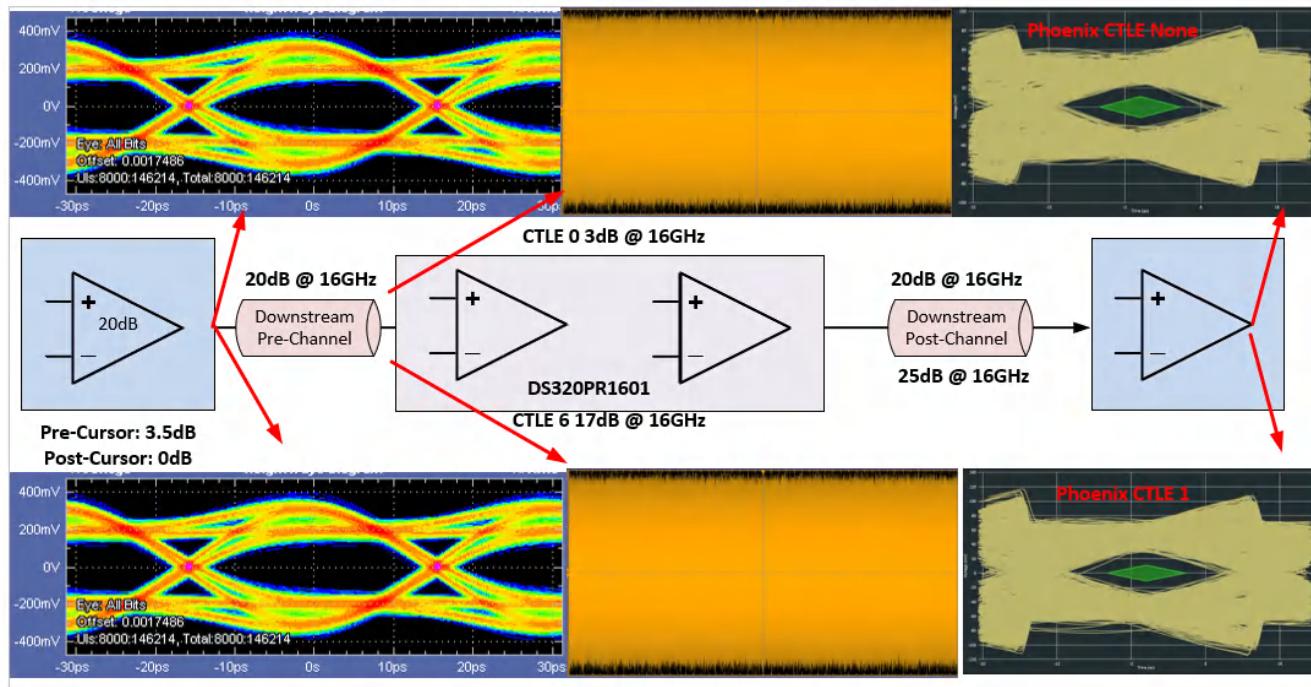

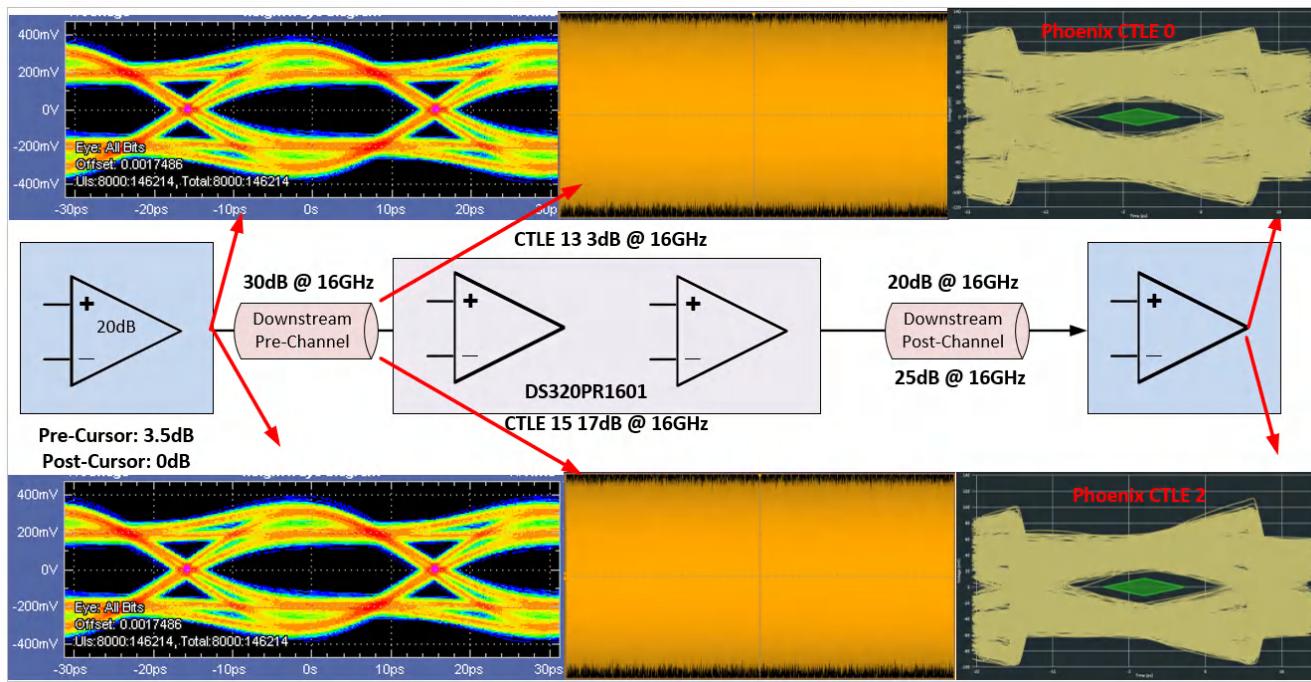

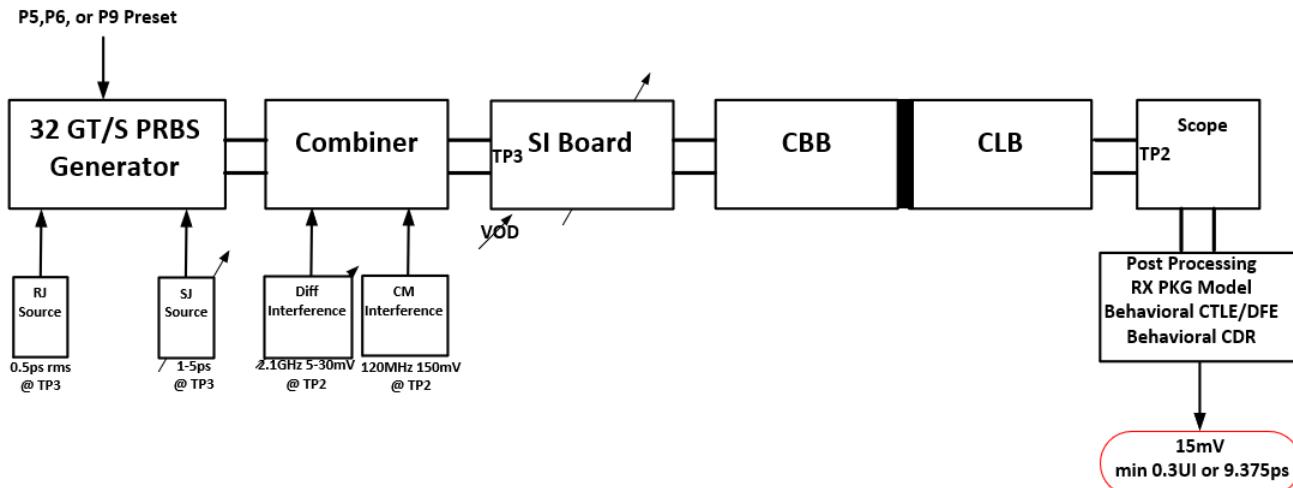

为了检查 RX EQ 合规性，这里使用 Phoenix 实用程序进行后处理，以检查眼图裕度是否符合 PCIe Gen5 要求。该后处理涉及 PCIe Gen5 RX 封装补偿、行为 CTLE/DFE 和 CDR 实现。这需要 15mV 的垂直眼图张开度和至少为 0.3UI 或 9.375ps 的水平眼图张开度。这里使用具有 P9 预设和 800mVpp 振幅的 BERT 进行了一系列测试，以展示转接驱动器 ISI 或 DJ 补偿功能。这些测试中使用了不同的前置通道和后置通道损耗。

如图 2-3 所示，当前置通道和后置通道损耗为 20dB 时，CTLE 设置为 0 的 Gen5 转接驱动器可以满足 PCI-SIG 要求。

### 备注

1. 前置通道损耗包括根复合体或端点封装损耗加上器件之前的 PCB 迹线损耗。

2. 在第二种情况下，我们使用相同的前置通道损耗，但使用了更高的 CTLE (EQ 指数 6) 来补偿 25dB 的后置通道损耗。后置通道损耗通常由 PCIe 接收器通过自适应 CTLE、DFE 和协商 TX 均衡功能来处理。在这种情况下，额外的增益可提供过均衡来补偿更高的 25dB 后置通道损耗。

图 2-4. 具有 20dB 前置通道损耗、20dB 至 25dB 后置通道损耗的 PCIe 链路分析示例

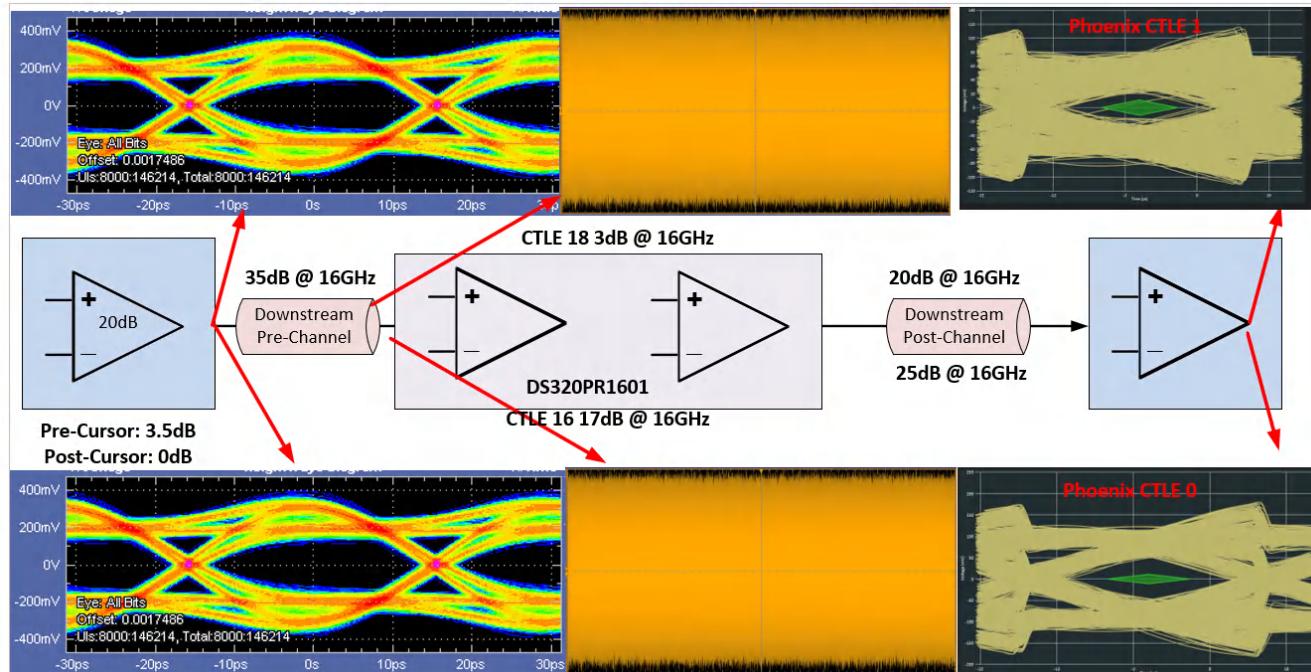

在图 2-5 和图 2-6 中，我们使用更高的前置通道损耗 (30dB)，而后置通道损耗变化范围则与之前相同。转接驱动器主要补偿前置通道损耗，并可执行边际过补偿以解决前置通道损耗增加问题。

图 2-5. 具有 30dB 前置通道损耗、20dB 至 25dB 后置通道损耗的 PCIe 链路分析示例

图 2-6. 具有 35dB 前置通道损耗、20dB 至 25dB 后置通道损耗的 PCIe 链路分析示例

如图所示，转接驱动器会补偿输入上因传输介质低通滤波效应而导致的 ISI ( 符号间干扰 )。RC 或 EP 都可以补偿其他因素导致的应力眼图：随机抖动 (RJ)、正弦抖动 (SJ)、阻抗不连续性引起的反射、布线长度不匹配引起的偏斜以及差模和共模干扰。

## 2.4 转接驱动器 EQ 调优

在大多数情况下，PCIe Gen5 转接驱动器需要进行 CTLE 设置调优，才能提供令人满意的眼图张开度。建议将直流增益保留为默认设置 0dB。有关直流增益和均衡设置的直接影响，请参阅[采用 DS320PR810 进行 PCI Express 合规性测试](#)。

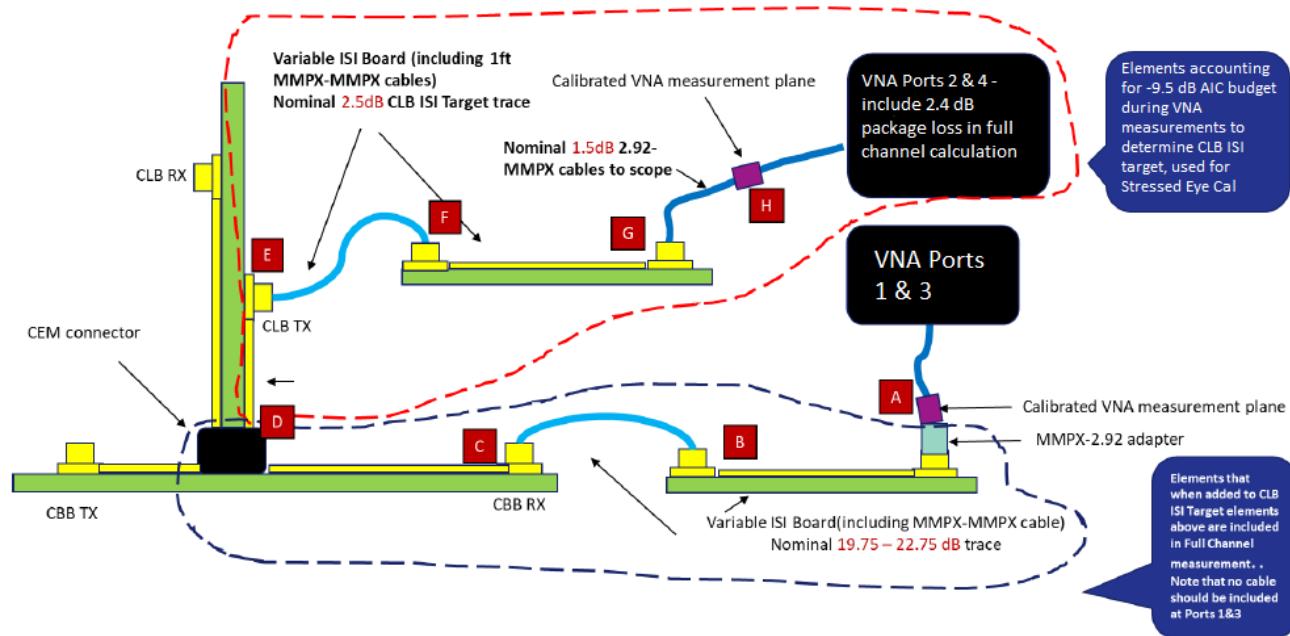

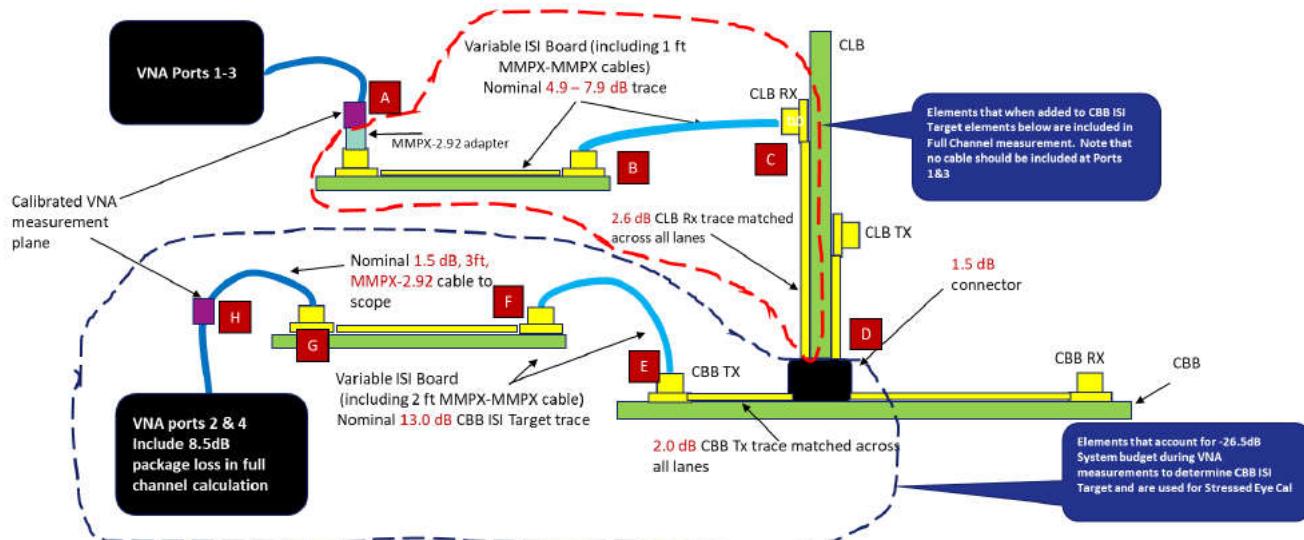

接收器链路均衡合规性在系统或插件卡上完成，以验证应力条件下 1E-12 处的互操作性。首先，执行不同的参数校准，以便为不同的系统或 AIC 应用提供相同的环境。以下设置用于满足 RX EQ 合规性。图像由 PCI-SIG 提供。

图 2-7. PCI-SIG AIC RX 校准规范

图 2-8. PCI-SIG 系统 RX 校准规范

### 备注

无论是在系统还是 AIC 场景中，PCIe 感知 BERT 都会使用 VNA 端口 1 和 3 以及该块来通过协议将链路伙伴的一个信道置于环回模式。使用经过校准的应力眼图，需要实现 1E-12 BER 一个或更少错误。

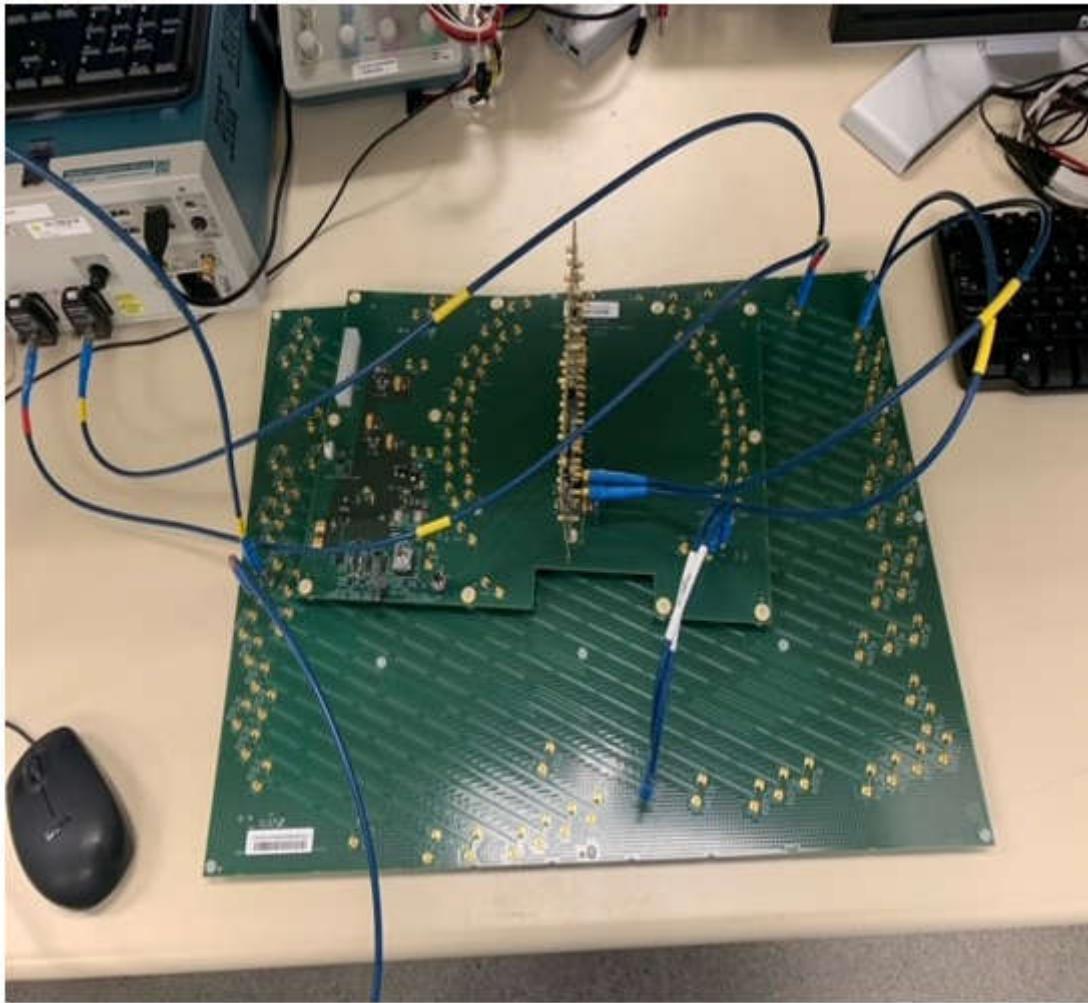

图 2-9. PCIe Gen5 SI、CBB 和 CLB 电路板

图 2-10. RX 合规性方框图

### 2.4.1 参数校准的详细说明

1. 振幅或 VOD 校准：振幅校准是在 TP3 处使用混合时钟和低频模式以 32Gbps 来完成的。在这种情况下，必须使用 P1 至 P9 预设来确认 PCIe Gen5 合规性。

2. RJ 校准在 TP3 处执行。P4 处使用 PCIe 校准模式以及 SigTest Phoenix 5.1.04 RJ\_SJ\_CAL 模板来分析 RJ。TP3 处的目标 RJ 为 0.5ps rms。

3. SJ 校准与 RJ 相似，目标值为 1ps 至 5ps。

4. 插入损耗校准在 TP2 处执行。[图 2-7](#) 和 [图 2-8](#) 展示了信号路径内不同元件的损耗目标以及 CBB/CLB 和 ISI 损耗电路板设置。

5. AIC DMI ( 差模干扰 ) 在 TP2 处执行，TP2 处的总通道损耗为 31.8dB。Phoenix 使用 4.2dB 来表示 AIC 封装损耗。P4 预设和用 2.1GHz 信号调制的 DMI/CMI 模式用于在 TP2 处实现目标 5mV 至 30mV DMI。

6. CMI 与 DMI 相同，也在 TP2 处执行。使用 120MHz CMI 来实现 150mV 的目标值。

7. TX EQ 校准：BERT 根据噪声值进行校准。使用 P5/6/8/9 预设，以可在 TP2 处产生最佳眼图面积为依据，来选择最佳 CTLE 和预设。

8. 插入损耗从 36dB 开始以 0.5dB 为步长递减，DMI 以 3mV 为增量递增，SJ 以 10mUI 为增量递增，SJ 以 10mV 为增量递增，而器件 CTLE 增益范围为 7 到 12，以实现最佳眼高 (EH) 和眼宽 (EW)。

[表 2-3](#) 中的 DS320PR1601 性能矩阵展示了使用刚刚讨论的 RX 均衡方法时各种前置通道和后置通道组合的器件性能。

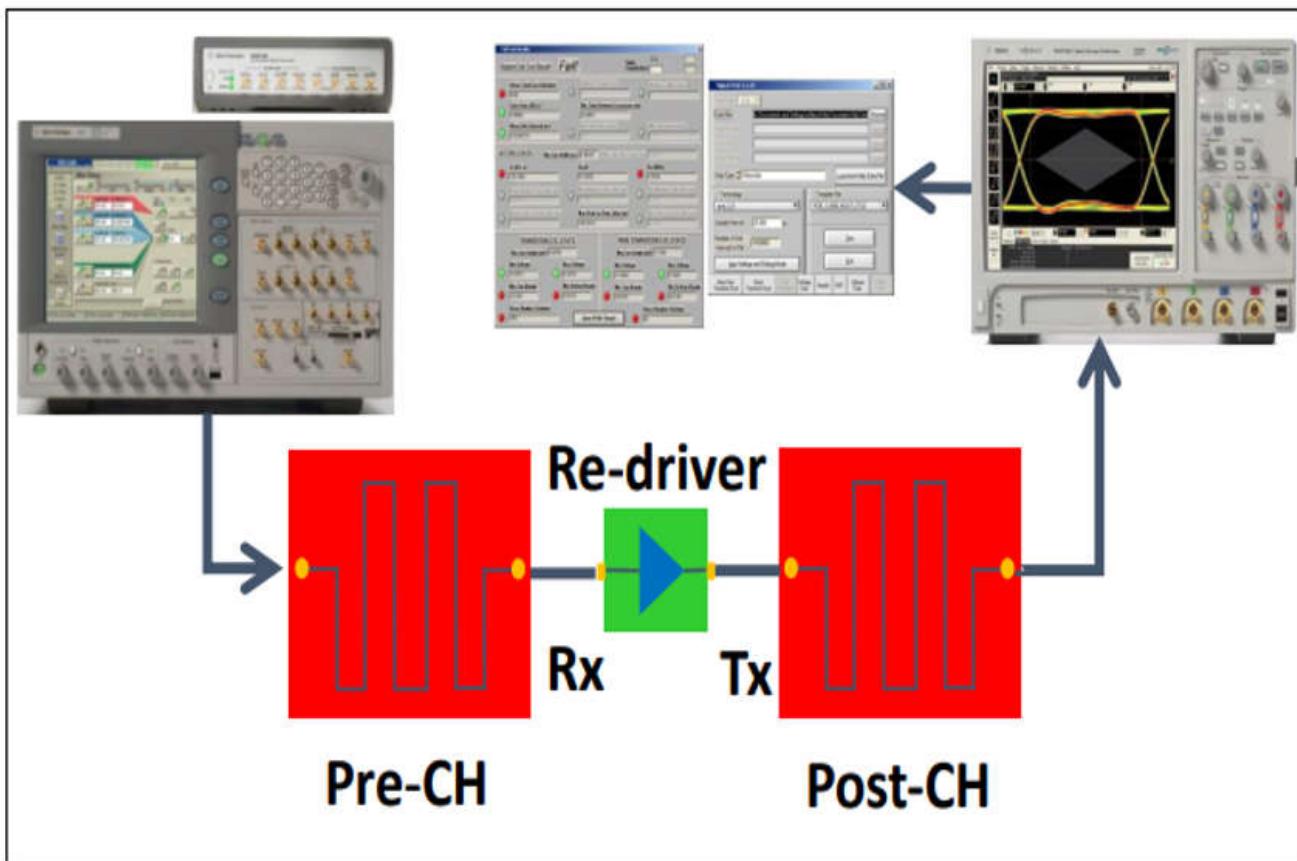

图 2-11. AIC 测试概述

[表 2-3](#) 展示了完成校准并在 AIC 模式下运行后，使用 PCIe Gen5 RX 均衡方法时各种前置通道和后置通道组合的器件性能

表 2-3. 前置通道和后置通道损耗的器件性能

| 前置通道损耗 (dB) | 后置通道损耗 (dB) | EQ 指数/直流增益/预设 | 眼宽 (UI) | 眼高 (mV) |

|-------------|-------------|---------------|---------|---------|

| 10          | 32          | 2/L2/P6       | 0.39    | 35.74   |

**表 2-3. 前置通道和后置通道损耗的器件性能 (续)**

| 前置通道损耗 (dB) | 后置通道损耗 (dB) | EQ 指数/直流增益/预设 | 眼宽 (UI) | 眼高 (mV) |

|-------------|-------------|---------------|---------|---------|

| 14          | 26          | 2/L2/P6       | 0.41    | 46      |

| 14          | 32          | 7/L2/P6       | 0.35    | 36.83   |

| 18          | 22          | 2/L4/P6       | 0.4     | 72.5    |

| 18          | 26          | 3/L2/P6       | 0.4     | 48.21   |

| 22          | 18          | 1/L2/P6       | 0.44    | 67.7    |

| 22          | 22          | 3/L2/P6       | 0.39    | 40.91   |

| 22          | 26          | 7/L2/P6       | 0.43    | 48      |

| 26          | 18          | 3/L2/P5       | 0.37    | 33.1    |

| 26          | 22          | 4/L2/P6       | 0.4     | 39.7    |

| 26          | 26          | 4/L2/P6       | 0.36    | 28.4    |

| 29          | 18          | 4/L2/P6       | 0.35    | 39.7    |

| 29          | 22          | 4/L2/P6       | 0.34    | 29.59   |

### 3 优化 CTLE 和增益选择的通用指南

以下步骤提供了有关选择转接驱动器 CTLE 设置的一般指导：

1. 非常需要使用实际介质、连接器、通孔、根复合体、端点和转接驱动器 S 参数模型来执行信号完整性分析。其目的是提供裕度以满足误码率和眼图尺寸的高要求。

2. 了解整体通道介质损耗曲线。温度、湿度、信噪比和串扰都需要额外的裕度才能实现稳定运行。

3. 每个端点或根复合体都需要一定的 IO 裕度。最好增加裕度，以确保在 PVT 范围内无差错运行。

4. 转接驱动器主要在其输入端提供升压以补偿信号损失。另一方面，它的输出信号调节受到限制。当其输出存在高损耗（后置通道损耗）时，边际信号调节有两种选项：

- a. 以 1 至 2 个步长对输入信号进行过均衡，这样输入信号就不会被压缩。

- b. 提供平坦增益以增加眼高。

5. 在了解前置通道和后置通道损耗后，使用表 2-3 来选择起始 CTLE 设置。不同的根复合体、端点或 BIOS 版本在性能上可能有所不同。因此，可能需要在表 2-3 中所示的推荐值上进行微调。

6. 表 2-3 是使用 PCIe 推荐的 SI 电路板测量的。实际应用可能具有不同的损耗曲线。因此，该表中提到的 CTLE 索引可用作实际应用的良好起点。

7. 验证下游转接驱动器的 CTLE 设置。如果测试实际系统，从最初选择的 CTLE 设置（同时保持最初选择的上游转接器的 CTLE 设置）上下扫描下游转接驱动器的 CTLE 设置，以确定允许系统成功连接的 CTLE 设置范围，或者在执行系统仿真或测量眼图时满足预定义的最低眼图波罩标准。

8. 验证上游转接驱动器的 CTLE 设置。从最初选择的 CTLE 设置（同时保持下游转接器之前所选的 CTLE 设置）上下扫描上游转接驱动器的 CTLE 设置，以确定允许系统成功连接的 CTLE 设置范围，或者满足预定义的最低眼图波罩标准。

9. 另一种通用的系统调优方法如下：

- a. 确定转接驱动器用例是系统格式还是 AIC 格式。这可以确定转接驱动器与 PCIe 链路的哪一端（根复合体或端点）最相关，目前称为主链路伙伴。

- b. 在主链路伙伴的下游方向执行 TX 合规性测试。目标是让下游转接驱动器补偿前置通道损耗：其直接输出需要尽可能精确地再现主链路伙伴最初传输的信号。实现这一点后，下游转接驱动器的 CTLE 设置就可以被冻结。

- c. 接下来，在上游方向执行 IOMT 或通道裕度测试。目标是对上游转接驱动器进行调优，使主链路伙伴接收到的信号具有可接受的质量。此过程可以使用不同的工具和标准。成功的上游调优需要使接收到的信号不仅符合所有要求，而且具有足够的裕度来补偿某些水平的噪声、应力和其他不可预见的影响。

- d. 由于物理或软件限制，这种整体方法并非总是可行，但它是最全面的转接驱动器调优方法，如果可能，建议您使用。

## 4 PCIe 热复位

在转接驱动器在 I<sup>2</sup>C 模式下运行并可以通过外部控制器配置的应用中，在带电环境下执行转接驱动器调优是很常见的情况，这种情况下，转接驱动器和其他系统元件会保持功率，并且可以直接将新的 EQ 设置写入器件。这很方便，与对 EEPROM 进行更改或在器件在引脚模式下运行时重新配置电路板硬件相比，不需要下电上电。

但是，如果转接驱动器测试程序涉及带电 PCIe 链路，那么在通过通道裕度和类似测试评估信号质量之前，请务必对链路执行热复位。向转接驱动器发送信号的 PCIe 发送器以及转接驱动器将信号输出到的 PCIe 接收器都具有自己与信号调节相关的设置，这些设置在链路训练过程中会自动协商和校准。例如，发送器会自动评估应用于传输数据的各种 PCIe 预设，并选择一个预设来使用。当链路处于正常运行状态 (L0) 时更改转接驱动器设置后，通道的电磁特性现在会有所不同，但发送器不会动态重新评估和重新协商其所选的 PCIe 预设作为响应。初始协商中保留的 PCIe 预设设置对新的通道条件可能不太适合。为了解决此问题，执行热复位会导致链路重新协商，并且由于系统电源保持不变，转接驱动器将保留其调整后的 EQ 设置。根据所测试系统的类型，可以通过在 CPU 配置软件中运行相关的 PCIe 协议命令来执行热复位，也可以通过执行操作系统或 BIOS 的热重启来执行热复位。

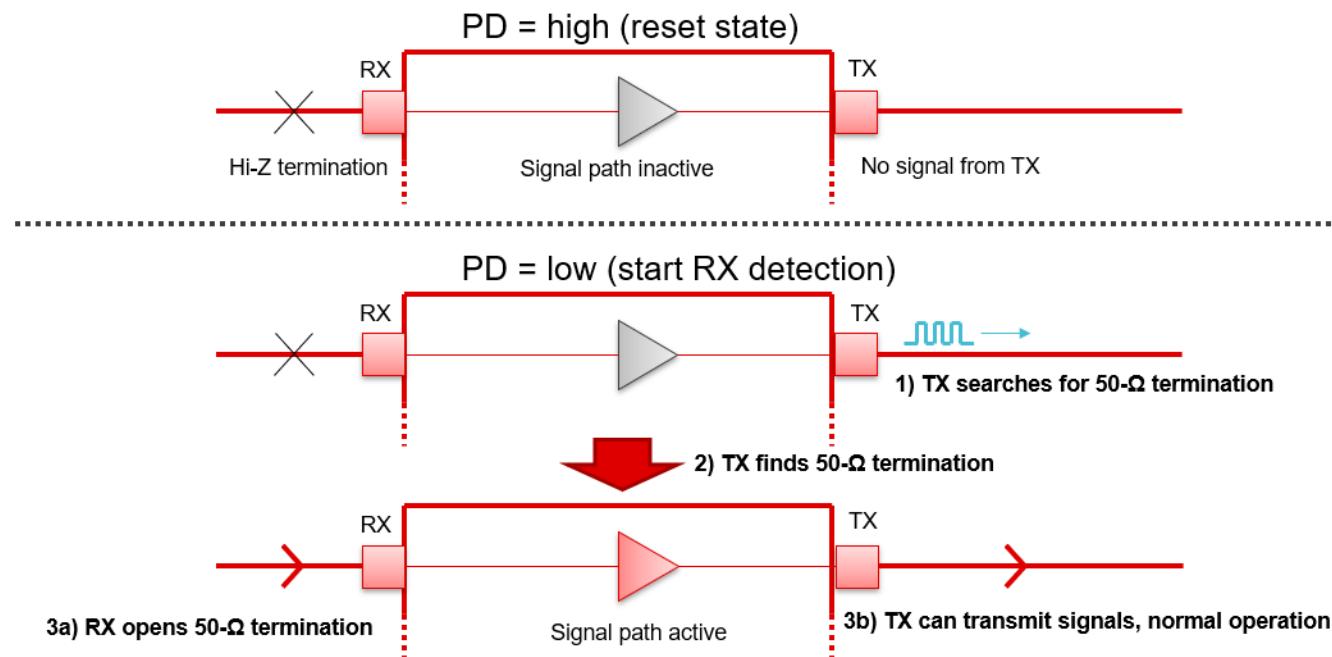

尽管热复位在协议级别执行，与协议无关的转接驱动器相对较少参与，但通过操纵 PD 引脚，确保在热复位和类似条件下与其他 PCIe 器件同步清除并重新激活转接驱动器的 RX 检测子系统的电路板设计会很有帮助。转接驱动器 RX 检测相对于 PD 引脚的操作如图 4-1 所示。

图 4-1. 转接驱动器 RX 检测功能

转接驱动器位于链路的中间，充当 RX 检测时序的中间人，仅当另一侧的转接驱动器 TX 引脚成功检测到所面对的器件中的 50 Ω 端接时，才显示转接驱动器 RX 引脚上的 50 Ω 端接。RX 连接到转接驱动器 TX 的器件只有在内部启动完全完成并且准备好开始 PCIe 协商后，才会启用 50 Ω 端接。如果转接驱动器在热复位后没有清除 RX 端接，并且等待适当的条件来开启它们，则根复合体可能会立即看到转接驱动器的端接（在开始看的那一刻），然后在端点可能未完全就绪时即开始 PCIe 协商。这会增加出现链路问题的风险。

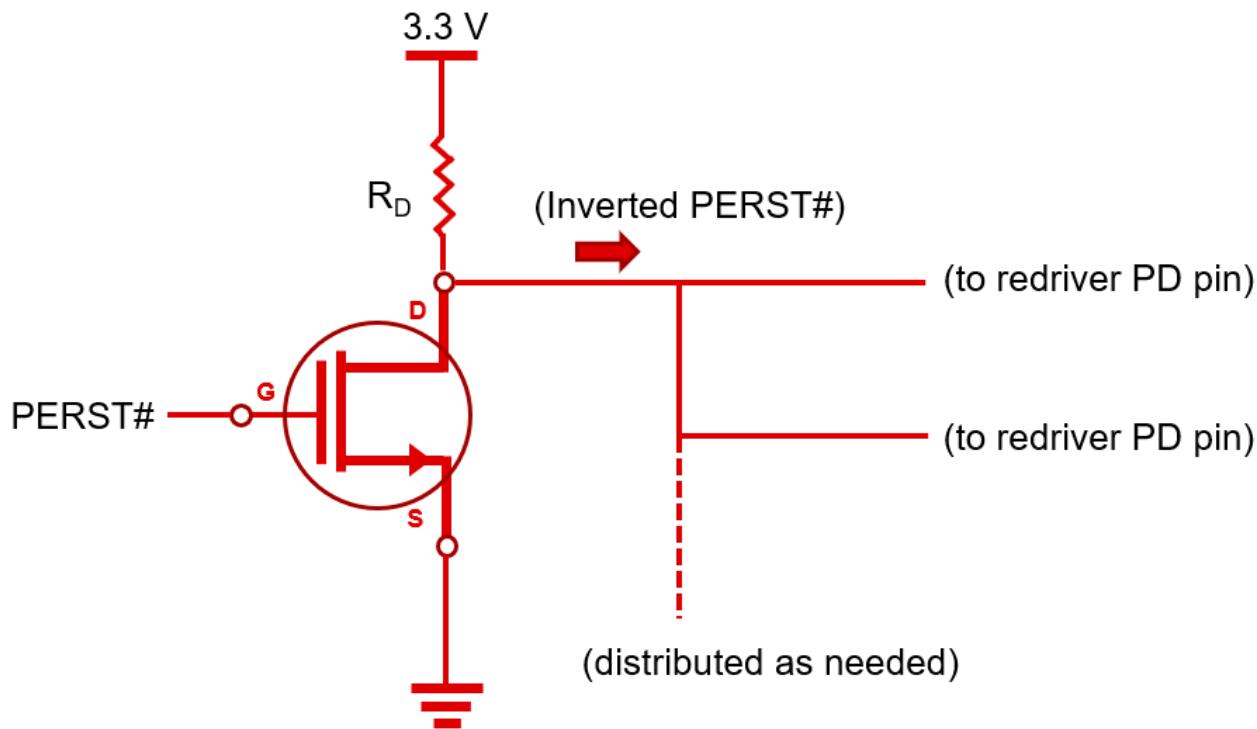

通过将 PD 引脚连接到 PCIe PERST# 信号的反相版，可以将转接驱动器 RX 检测过程与 PCIe 协议的控制同步。当链路处于复位状态（热复位或上电复位）时，PERST# 保持低电平，在此期间，与 PD 的反相连接会将转接驱动器保持在复位状态并清除 RX 端接。低电平到高电平的转换会向所有 PCIe 器件指示链路过程需要启动，转接驱动器的作用是开始搜索 TX 引脚处的端接。

在典型应用中，PERST# 会从根复合体路由到端点。将其转移到逆变器并将反相信号路由到转接驱动器引脚或多个转接驱动器引脚通常不会给电路板布局带来不便。逆变器的实现方案由设计人员自行决定，但基本的 MOSFET

逆变器或逆变器 IC 都可能适用。确保逆变器实现方案的输入和输出电压与 PERST# 信号和 PD 引脚兼容。图 4-2 展示了一个示例，说明了如何将 PERST# 反相并分配给转接驱动器 PD 引脚。

图 4-2. 转接驱动器 PD 引脚的反相 PERST# 分配示例

在初始系统上电期间，此 PD 配置方案的另一个好处会显现出来：由于 PERST# 最初保持低电平，转接驱动器可以保持在复位状态，直到 PERST# 转换触发它，以便开始与其他系统元件同步进行 RX 检测。如果通过硬接线进行接地连接来将 PD 拉至低电平，则转接驱动器会在其相对快速的上电序列完成后立即开始 RX 检测。在 PERST# 转换之前的这一早期阶段，某些 PCIe 端点可能会在其自身的上电序列完全完成之前出现错误或未同步的端接，然后转接驱动器可以对其进行检测和操作。导致出现与热复位情况类似的情况，根复合体可以看到转接驱动器出现错误的提早端接，出现链路问题的可能性也会更高。

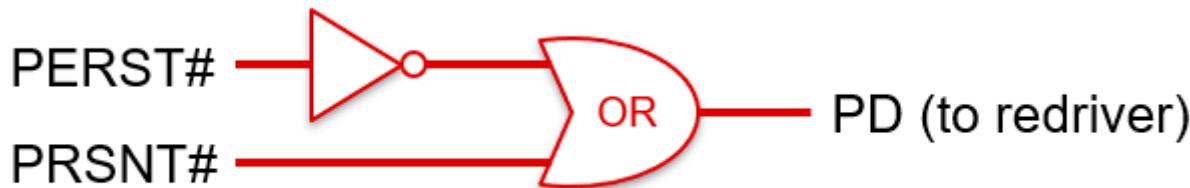

如果除了反相 PERST# 外，PD 引脚还被其他信号控制，例如连接到 PRSNT# 以实现热插拔功能，那么使用逻辑或门对多个控制信号进行仲裁会更安全，如图 4-3 的示例所示。如果不详细了解生成每个控制信号的机制，就很难预测将这些信号连接到 PD 引脚处的同一节点时是否能够正常工作，或者是否存在冲突，导致电压不正确和其他问题。

图 4-3. 具有两个输入信号的 PD 控制逻辑示例

## 5 总结

PCIe Gen5 转接驱动器需要进行调优才能成功集成到新系统中。在创建测试设置和接收器性能评估方法时必须小心谨慎，但是这些过程也有既定的指导原则、硬件和实用程序。测试开始后，大多数应用都可以通过仅调整 EQ 指数来实现成功调优，直到结果令人满意且符合 PCIe 标准。本文档中提供的数据有助于在总体损耗曲线中选择转接驱动器的位置，并从起始 CTLE 设置开始测试，从而缩短所需的时间和精力。调优完成后，PCIe Gen5 转接驱动器即可发挥其预期作用，成为扩展 PCIe 链路覆盖范围并维持其质量的简单方法。

## 6 参考文献

- 德州仪器 (TI) , [DS320PR810 用于 PCIe 5.0、CXL 1.1 的八通道线性转接驱动器 数据表](#)。

- 德州仪器 (TI) , [DS320PR1601 32Gbps、16 通道、PCIe® 5.0、CXL 2.0 线性转接驱动器 数据表](#)。

- 德州仪器 (TI) , [SN75LVPE5412 具有 1:2 多路信号分离器的 PCIe® 5.0 32Gbps 4 通道线性转接驱动器 数据表](#)。

- 德州仪器 (TI) , [SN75LVPE5421 具有 2:1 多路复用器的 PCIe® 5.0 32Gbps 4 通道线性转接驱动器 数据表](#)。

- 德州仪器 (TI) , [采用 DS320PR810 进行 PCI Express 合规性测试 应用手册](#)。

## 7 修订历史记录

### Changes from Revision A (August 2023) to Revision B (January 2026)

|                               | Page |

|-------------------------------|------|

| • 针对较大系统损耗添加了转接驱动器位置建议。 ..... | 5    |

| Changes from Revision * (August 2023) to Revision A (December 2024) | Page |

|---------------------------------------------------------------------|------|

| • 更新了整个文档中的表格、图和交叉参考的编号格式.....                                      | 1    |

| • 增加了 <i>PCIe 热复位</i> 一节.....                                       | 13   |

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#))、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2026 , 德州仪器 (TI) 公司

最后更新日期 : 2025 年 10 月