# 设计指南: TIDA-050026-23882 适用于多端口应用的 24 端口(2 对)电源设备 参考设计

# **TEXAS INSTRUMENTS**

## 说明

此参考设计 采用 适合 24 端口(2 对) PSE 系统的评估 模块,该模块包含硬件套件、系统固件图像和系统固件 GUI。硬件套件包含主板 (PSEMTHR24EVM-081)、 MSP430 子卡 (PSEMCUDAUEVM-082) 和 PSE 子卡 (TPS23882EVM-084)。如需评估该系统(硬件和软件 均含在内),还需要 USB2ANY 和 MSP-FET 适配器。

#### 为了进行 EVM 测试,已使用预生产固件对

PSEMCUDAUEVM-082 上的 MSP430F5234 进行了编程。在评估之前,请按照此用户指南中的说明从 TI.com 获取最新固件。

#### 资源

| TIDA-050026-23882 | 设计文件夹 |

|-------------------|-------|

| TPS23882EVM-084   | 工具文件夹 |

| PSEMTHR24EVM-081  | 工具文件夹 |

| PSEMCUDAUEVM-082  | 工具文件夹 |

| TPS23882          | 产品文件夹 |

| MSP430F5234       | 产品文件夹 |

| CSD19538Q3A       | 产品文件夹 |

Search Our E2E<sup>™</sup> support forums

#### 特性

- 板载功率监控

- 24(2对)端口系统,可扩展至48端口系统

- 具有可配置 GUI 和可选主机接口(I<sup>2</sup>C 或 UART)的高度灵活系统

- 多端口电源管理

- 多电源

- 支持传统供电设备 (PD)

## 应用

- 校园网交换机和分支交换机

- 录像机

- 边缘路由器

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

A

#### 1 System Description

This reference design provides a competitive and alternative solution.

In a multiport PSE system, the system-level software is the biggest challenge. The software handles complicated situations and addresses the following challenges:

- The power supply is usually not able to support all ports with a full load due to size and cost constraints. The system software manages the port power with priority to keep the total power consumption below the power budget.

- There are multiple power supplies in the system. These power supplies could be in sharing mode or backup mode. The system software shuts down low-priority ports fast enough to keep the total power consumption below the remaining power budget.

- There are some legacy PD devices that do not present the standard PoE PD signature. The system software finds a way to supply power to these devices.

- System software limits the port power based on the PD class levels or host configuration.

- When there are load-step changes on multiple ports, the system software acts quickly enough to keep the power consumption below the power budget.

# 1.1 Key System Specifications

| PARAMETER                        | SPECIFICATIONS      | DETAILS                                   |

|----------------------------------|---------------------|-------------------------------------------|

| Input voltage                    | 44 V–57 V           |                                           |

| Port power limit                 | 2 W–60 W            | > 30 W is considered as nonstandard power |

| Compliance                       | IEEE 802.3bt Type 3 |                                           |

| PD class level supported         | Class 0 to class 4  |                                           |

| Number of power supply supported | 1–2                 | In sharing mode and redundant mode        |

| Max port number supported        | 48                  | Referred to RJ45 ports                    |

#### 表 1. Key System Specifications

# 1.2 Description

This reference design features the TPS23882 daughtercard, the octal channel, the TPS23882 device, and the IEEE802.3bt ready PoE PSE controller. When paired with the PSE motherboard PSEMTHR24-081 (sold separately) and MCU daughtercard PSEMCUDAUEVM-082 (sold separately), users can evaluate the TPS23882 device and PSE system firmware solution.

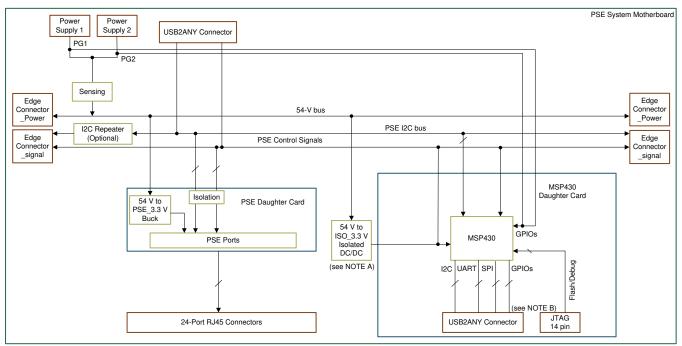

The full PoE evaluation ecosystem includes the following:

- PSEMTHR24EVM-081: motherboard for 24-port PoE PSE applications (sold separately)

- PSEMCUDAUEVM-082: MSP430 daughtercard for 24-port PoE PSE applications (sold separately)

- TPS23882EVM-084: TPS23882 daughtercard for 24 port Type 3 (2 pair) PSE PoE PSE applications (sold separately)

- USB2ANY interface adapter: used with PSE system firmware GUI for I<sup>2</sup>C/UART interaction with the PSEMCUDAU-082 daughtercard (sold separately)

- MSP-FET programmer: used with Uniflash GUI for programming the MSP430 device

- PSE system firmware code image (request access to the code image through TIDA-050026-23882 folder or PSEMCUDAUEVM-082 tool folder)

٠

- PSE system firmware GUI (request access to the code image through TIDA-050026-23882 folder or PSEMCUDAUEVM-082 tool folder)

- 注: The MSP430F5234 on PSEMCUDAUEVM-082 has been programmed with pre-production firmware for EVM testing purposes. Please follow the instructions in this user's guide to flash the latest firmware from TIDA-050026-23882 folder or PSEMCUDAUEVM-082 tool folder before evaluation.

# 2 System Overview

# 2.1 Block Diagram

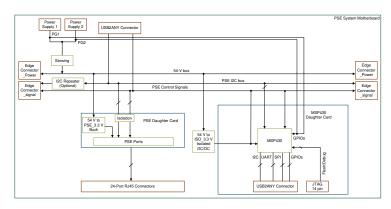

#### 图 1. TIDA-050026-23882 Block Diagram

- A The 54-V to 3.3-V isolated DC/DC is for demonstration purposes only. It is not needed in a real system.

- B Only connect a USB2ANY connector or JTAG to avoid GND loops.

# 2.2 Design Considerations

#### 2.2.1 Input Power

#### 2.2.1.1 Vpwr

DC input voltage is provided through J1 and J3. This board supports a dual power source in sharing mode and redundant mode. If the power supplies are in redundant mode, make sure the main power supply is connected to J1 and a backup power supply is connected to the J3 connector.

The minimum PSE port voltage is 44 VDC for Type 1, 50 V for Type 2 and Type 3, and 52 V for Type 4. The maximum DC voltage at VPWR is 57 V for all types. During evaluation, choose the appropriate DC power supply for the different type environment.

#### System Overview

#### 2.2.1.2 3.3 V

A local 3.3 V for local devices (labeled as 3.3 V) is provided by the onboard LM5017 buck converter. The LM5017 device provides a basic power-on sequence and provides a well-controlled and consistent startup to prevent erratic operation. In addition to 44 V to 57 V, the TPS238x requires 3.3 V for the digital circuitry and each TPS2388x device consumes 6-mA typical and 12-mA maximum.

# 2.2.1.3 3.3 V\_ISO

The reference design kit provides galvanic isolation between PoE power side and host side using digital isolators. The host side power is provided by 3.3 V\_ISO.

## 2.2.2 Communication Interface

## 2.2.2.1 PSE fC Communication

The board provides two I<sup>2</sup>C interfaces communicating to PSE:

- 1. J10 on the motherboard (PSEMTHR24EVM-081) provides I<sup>2</sup>C access to all PSE devices directly. The TPS2388x GUI can communicate to PSE devices with the USB2ANY interface adapter.

- 2. J11 and J12 on the motherboard (PSEMTHR24EVM-081) provides I<sup>2</sup>C access and system control signal to the MSP430 daughtercard.

## 2.2.2.2 MCU - Host Communication

The MSP430 daughtercard provides I<sup>2</sup>C/UART communication port to host through J12 to J14 on MSP430 daughtercard (PSEMCUDAUEVM-082). The PSE system GUI provides host configurations to the PSE system.

Host interface user's guide can be accessed from TIDA-050026-23882 folder or PSEMCUDAUEVM-082 tool folder.

#### 2.2.3 MSP430F523x Hardware Design

| PIN NUMBER<br>MSP430F5234 (48RGZ) TERMINAL FUNCTION |      | FUNCTION                                                                  | COMMENT                                   |

|-----------------------------------------------------|------|---------------------------------------------------------------------------|-------------------------------------------|

| COMMUNICATION                                       |      |                                                                           |                                           |

| 22                                                  | P3.0 | I <sup>2</sup> C SDA USCI_B0                                              | I <sup>2</sup> C to PSEs                  |

| 23                                                  | P3.1 | I <sup>2</sup> C SCL USCI_B0                                              | I <sup>2</sup> C to PSEs                  |

| 30                                                  | P4.1 | I <sup>2</sup> C SDA USCI_B1                                              | I <sup>2</sup> C to host                  |

| 31                                                  | P4.2 | I <sup>2</sup> C SCL USCI_B1                                              | I <sup>2</sup> C to host                  |

| 33                                                  | P4.4 | UART TX USCI_A1                                                           | UART to host (debug only)                 |

| 34 P4.5                                             |      | UART RX USCI_A1                                                           | UART to host (debug only)                 |

| 21                                                  | P2.7 | SPI CLK USCI_A0                                                           | SPI to host (reserved)                    |

| 24 P3.2 SPI slave TX enab                           |      | SPI slave TX enable, USCI_A0                                              | SPI to host (reserved)                    |

| 25 P3.3                                             |      | UART TX,USCI_A0 or SPI slave in, master out                               | UART to host TX or SPI to host (reserved) |

| 26 P3.4                                             |      | UART RX, USCI_A0 or SPI slave out, master in                              | UART to host RX or SPI to host (reserved) |

| HARDWARE INTERRUPT                                  | •    | *                                                                         |                                           |

| 13                                                  | P1.0 | PSE INT                                                                   | Connect to PSE INT pin                    |

| 16 P1.3 OC Alert                                    |      | Connect to external current sensing circuit if not used, connect to 3.3 V |                                           |

#### 表 2. MSP430 GPIO Pin Assignment

4 适用于多端口应用的 24 端口(2 对)电源设备 参考设计

| PIN NUMBER<br>MSP430F5234 (48RGZ) | TERMINAL | FUNCTION                                        | COMMENT                                                                                                                                                                                            |  |  |

|-----------------------------------|----------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 18                                | P1.5     | Power supply 1                                  | Connect to power supply 1 power good signal. In<br>RPS mode, P1.5 must be connected to main power<br>supply. If there's only one power supply, the<br>power good signal must be connected to P1.5. |  |  |

| 19                                | P1.6     | Power supply 2                                  | Connect to power supply 2 power good signal, if not<br>used, connect to GND. In RPS mode, P1.6 must be<br>connected to backup power supply                                                         |  |  |

| 20                                | P1.7     | Disable all ports                               | This is for hardware disable ports(Reserved)                                                                                                                                                       |  |  |

| GENERAL I/O                       |          |                                                 |                                                                                                                                                                                                    |  |  |

| 4                                 | P5.0     | RESET                                           | PSE RESET Connect to PSE RESET pin                                                                                                                                                                 |  |  |

| 17                                | P1.4     | OSS                                             | PSE OSS Connect to PSE OSS pin                                                                                                                                                                     |  |  |

| 46                                | P6.0     | Interrupt pin to host                           |                                                                                                                                                                                                    |  |  |

| 35                                | P4.6     | BSL mode indication to host                     | MCU configures as output. If MCU is in BSL mode<br>output high. If in normal operation mode, output low                                                                                            |  |  |

| 48                                | P6.2     | Guard-band indication                           | Need an external LED                                                                                                                                                                               |  |  |

| 47 P6.1                           |          | Selection between I <sup>2</sup> C and SPI/UART | (Need to pullup or pulldown)                                                                                                                                                                       |  |  |

| PROGRAM DOWNLOAD A                | ND DEBUG |                                                 | +                                                                                                                                                                                                  |  |  |

| 44                                | PJ.3     | ТСК                                             | JTAG clock input                                                                                                                                                                                   |  |  |

| 43                                | PJ.2     | TMS                                             | JTAG state control                                                                                                                                                                                 |  |  |

| 42                                | PJ.1     | TDI/TCLK                                        | JTAG data input, TCLK input                                                                                                                                                                        |  |  |

| 41                                | PJ.0     | TDO                                             | JTAG data output                                                                                                                                                                                   |  |  |

| 40                                |          | TEST/SBWTCK                                     | Enable JTAG pins                                                                                                                                                                                   |  |  |

| 45                                |          | RSTDVCC/SBWTDIO                                 | External reset                                                                                                                                                                                     |  |  |

| EXTERNAL CRYSTAL                  | r.       | 1                                               |                                                                                                                                                                                                    |  |  |

| 7                                 | P5.4     | XTIN                                            | External low frequency clock (use if needed)                                                                                                                                                       |  |  |

| 8                                 | P5.5     | XTOUT                                           | External low frequency clock (use if needed)                                                                                                                                                       |  |  |

| 表 2. MSP430 GPIO Pin Assignment (continued | 表 2. | P430 | GPIO | Pin | Assignment | (continued |

|--------------------------------------------|------|------|------|-----|------------|------------|

|--------------------------------------------|------|------|------|-----|------------|------------|

Pre-configure the host interface protocol through hardware as  $\frac{1}{2}$  3 shows.

# 表 3. Host Interface Protocol

|                  | P6.1 | CS(P3.2)   |

|------------------|------|------------|

| l <sup>2</sup> C | high | Don't care |

| UART             | low  | low        |

| SPI (Reserved)   | low  | high       |

# 2.3 Highlighted Products

# 2.3.1 TPS23882

The TPS2388x device is the main IC to handle PoE functions to deliver power to PDs through Ethernet cable.

The TPS23882 is an 8-channel power sourcing equipment (PSE) controller engineered to insert power onto Ethernet cables in accordance with the IEEE 802.3bt standard. The PSE controller can detect powered devices (PDs) that have a valid signature, determine the power requirements of the devices according to their classification, and apply power. The TPS23882 improves on the TPS2388 with reduced current sense resistors, selectable Autonomous operation, SRAM programmability, programmable power limiting, capacitance measurement, and compatibility with TI's FirmPSE system firmware (see Device

#### System Overview

www.ti.com.cn

Comparison Table). Dedicated per port ADCs provide continuous port current monitoring and the ability to perform parallel classification measurements for faster port turn on times. A 1.25A port current limit and adjustable power limiting allows for the support of non-standard applications above 60W sourced. The 200 m $\Omega$  current sense resistor and external FET architecture allow designs to balance size, efficiency, thermal, and solution cost requirements. Port remapping and pin-to-pin compatibility with the TPS2388/80/81 devices eases migration from previous generation PSE designs and enables interchangeable 2-layer PCB designs to accommodate different system PoE power configurations.

## 2.3.2 MSP430F523x

The TI MSP family of ultra-low-power microcontrollers consists of several devices featuring different sets of peripherals targeted for various applications. The architecture, combined with extensive low-power modes, is optimized to achieve extended battery life in portable measurement applications. The device features a powerful 16-bit RISC CPU, 16-bit registers, and constant generators that contribute to maximum code efficiency. The digitally controlled oscillator (DCO) allows the device to wake up from lowpower modes to active mode in  $3.5 \,\mu s$  (typical). The MSP430F524x series are microcontroller configurations with four 16-bit timers, a high-performance 10-bit ADC, two USCIs, a hardware multiplier, DMA, a comparator, and an RTC module with alarm capabilities. The MSP430F523x series microcontrollers include all of the peripherals of the MSP430F524x series except for the ADC.

MSP430F523x is the main controller to control PSE devices(TPS2388x) through the  $I^2C$  bus and also communicates to host CPU through  $I^2C$  or UART to receive configurations and report system status.

## 2.3.3 ISO7741

The ISO7741 isolator is used to isolate I<sup>2</sup>C signals between PSE devices and the MCU.

The ISO774x devices are high-performance, quadchannel digital isolators with 5000 VRMS (DW package) and 3000 VRMS (DBQ package) isolation ratings per UL 1577. This family of devices has reinforced insulation ratings according to VDE, CSA, TUV and CQC. The ISO774x devices provide high electromagnetic immunity and low emissions at low power consumption, while isolating CMOS or LVCMOS digital I/Os. Each isolation channel has a logic input and output buffer separated by a double capacitive silicon dioxide (SiO2) insulation barrier. This device comes with enable pins which can be used to put the respective outputs in high impedance for multi-master driving applications and to reduce power consumption. The ISO7740 device has all four channels in the same direction, the ISO7741 device has three forward and one reverse-direction channels, and the ISO7742 device has two forward and two reverse-direction channels. If the input power or signal is lost, default output is high for devices without suffix F and low for devices with suffix F.

#### 2.3.4 ISO7731

The ISO7731 digital isolator is used to isolate control signals (OSS, RESET, INT) between MSP430 and PSE devices.

The ISO773x devices are high-performance, triple channel digital isolators with 5000 VRMS (DW package) and 3000 VRMS (DBQ package) isolation ratings per UL 1577.

This family of devices has reinforced insulation ratings according to VDE, CSA, TUV, and CQC.

The ISO773x family of devices provides high electromagnetic immunity and low emissions at low power consumption, while isolating CMOS or LVCMOS digital I/Os. Each isolation channel has a logic input and output buffer separated by a silicon dioxide (SiO2) insulation barrier. This device comes with enable pins which can be used to put the respective outputs in high impedance for multi-master driving applications and to reduce power consumption. The ISO7730 device has all three channels in the same direction and the ISO7731 device has two forward and one reverse-direction channel. If the input power or signal is lost, the default output is high for devices without suffix F and low for devices with suffix F. See the device *Functional Modes* section for further details.

Used in conjunction with isolated power supplies, this device helps prevent noise currents on a data bus or other circuits from entering the local ground and interfering with or damaging sensitive circuitry. Through innovative chip design and layout techniques, electromagnetic compatibility of the ISO773x device has been significantly enhanced to ease system-level ESD, EFT, surge, and emissions compliance.

# 2.3.5 CSD19538

This 100-V, 49-m $\Omega$ , SON 3.3-mm × 3.3-mm NexFET<sup>TM</sup> power MOSFET is designed to minimize conduction losses and reduce the board footprint in PoE applications.

#### System Overview

#### 2.3.6 LM5017

The LM5017 device is used to generate 3.3 V to supply PSE devices.

The LM5017 is a 100-V, 600-mA synchronous step-down regulator with integrated high-side and low-side MOSFETs. The constant on-time (COT) control scheme employed in the LM5017 device requires no loop compensation, provides excellent transient response, and enables very high step-down ratios. The on-time varies inversely with the input voltage resulting in nearly constant frequency over the input voltage range. A high-voltage startup regulator provides bias power for internal operation of the IC and for integrated gate drivers. A peak current limit circuit protects against overload conditions. The undervoltage lockout (UVLO) circuit allows the input undervoltage threshold and hysteresis to be independently programmed. Other protection features include thermal shutdown and bias supply undervoltage lockout (VCC UVLO).

## 2.3.7 LM5020

The LM5020 device is used to generate isolated LM5020 to supply MSP430 and isolators.

The LM5020 high-voltage pulse-width modulation (PWM) controller contains all of the features needed to implement single-ended primary power converter topologies. Output voltage regulation is based on current-mode control, which eases the design of loop compensation while providing inherent line feed-forward. The LM5020 device includes a high-voltage start-up regulator that operates over a wide-input range up to 100 V. The PWM controller is designed for high-speed capability including an oscillator frequency range to 1 MHz and total propagation delays less than 100 ns. Additional features include an error amplifier, precision reference, line undervoltage lockout, cycle-by-cycle current limit, slope compensation, softstart, oscillator synchronization capability and thermal shutdown.

#### 2.3.8 LM5050

The LM5050 device is used to support 2 power supplies in the system to work in backup mode.

The LM5050-1 and LM5050-1-Q1 high-side ORing FET controller operates in conjunction with an external MOSFET as an ideal diode rectifier when connected in series with a power source. This ORing controller allows MOSFETs to replace diode rectifiers in power distribution networks thus reducing both power loss and voltage drops.

The LM5050-1 and LM5050-1-Q1 controllers provide charge pump MOSFET gate drive for an external Nchannel MOSFET and a fast response comparator to turn off the FET when current flows in the reverse direction. The LM5050-1 and LM5050-1-Q1 can connect power supplies ranging from 5 V to 75 V and can withstand transients up to 100 V.

#### 2.3.9 INA240

The INA240 amplifier is used to measure the total current from the input to support fast shutdown in an event of load step change.

The INA240 device is a voltage-output, current-sense amplifier with enhanced PWM rejection that can sense drops across shunt resistors over a wide common-mode voltage range from -4 V to 80 V, independent of the supply voltage. The negative common-mode voltage allows the device to operate below ground, accommodating the flyback period of typical solenoid applications. Enhanced PWM rejection provides high levels of suppression for large common-mode transients ( $\Delta$ V/ $\Delta$ t) in systems that use PWM signals (such as motor drives and solenoid control systems). This feature allows for accurate

current measurements without large transients and associated recovery ripple on the output voltage. This device operates from a single 2.7-V to 5.5-V power supply, drawing a maximum of 2.4 mA of supply current. Four fixed gains are available: 20 V/V, 50 V/V, 100 V/V, and 200 V/V. The low offset of the zero-drift architecture enables current sensing with maximum drops across the shunt as low as 10-mV full-scale.

#### 2.3.10 REF3425

The REF3425 device is used to provide a threshold to output the INA240 and generate a signal to MCU for overcurrent alert.

The REF34xx device is a low temperature drift (6 ppm/°C), low-power, high-precision CMOS voltage reference, featuring  $\pm 0.05\%$  initial accuracy, low operating current with power consumption less than 95  $\mu$ A. This device also offers very low output noise of 3.8  $\mu$ Vp-p /V, which enables its ability to maintain high signal integrity with high-resolution data converters in noise critical systems. With a small SOT-23 package, the REF34xx offers enhanced specifications and pin-to-pin replacement for MAX607x and ADR34xx. The REF34xx family is compatible to most of the ADC and DAC such as the ADS1287, ADUCM360, and ADS1112 devices. Stability and system reliability are further improved by the low output-voltage hysteresis of the device and low long-term output voltage drift. Furthermore, the small size and low operating current of the devices (95  $\mu$ A) can benefit portable and battery-powered applications.

# 2.3.11 TPS3890

The TPS3890 device is used to monitor the existence of the power supply and generate power good signal to MCU. The MCU can adjust the total power budget of the system.

The TPS3890 device is a precision voltage supervisor with low-quiescent current that monitors system voltages as low as 1.15 V, asserting an open-drain RESET signal when the SENSE voltage drops below a preset threshold or when the manual reset (MR) pin drops to a logic low. The RESET output remains low for the user-adjustable delay time after the SENSE voltage and manual reset (MR) return above the respective thresholds. The TPS3890 family uses a precision reference to achieve 1% threshold accuracy. The reset delay time can be user-adjusted between 40  $\mu$ s and 30 s by connecting the CT pin to an external capacitor. The TPS3890 device has a very low quiescent current of 2.1  $\mu$ A and is available in a small 1.5-mm x 1.5-mm package, making the device well-suited for battery-powered and space-constrained applications.

# 3 Hardware, Software, Testing Requirement and Test Result

# 3.1 Required Hardware and Software

#### 3.1.1 Hardware

The following hardware is required to get started with the reference design:

- PSEMTHR24EVM-081: motherboard for 24 port PoE PSE applications (sold separately)

- PSEMCUDAUEVM-082: MSP430 daughtercard for 24 Port PoE PSE applications (sold separately)

- TPS23882EVM-084: TPS23882 daughtercard for 24-port Type 3 (2 pair) PoE PSE applications (sold separately)

- USB2ANY interface adapater: used with PSE system firmware GUI for I<sup>2</sup>C/UART interaction with PSEMCUDAU-082 daughtercard (sold separately)

- MSP-FET programmer: used with the Uniflash GUI for programming the MSP430 device

#### 3.1.2 Software

- FirmPSE code image (request access to the code image through the TIDA-050026-23882 folder or the PSEMCUDAUEVM-082 tool folder)

- FirmPSE GUI (request access to the GUI through the TIDA-050026-23882 folder or the

Hardware, Software, Testing Requirement and Test Result

PSEMCUDAUEVM-082 tool folder)

## 3.2 Testing and Results

# 3.2.1 Test Setup

#### 3.2.1.1 Hardware Setup

2 shows the hardware test setup of the ecosystem.

# 3.2.1.2 LED, Test Point, Jumper and Connector Settings

# 3.2.1.2.1 EVM LEDs

$\frac{1}{8}$  4 lists the EVM LEDs and their descriptions.

# 表 4. EVM LEDs

| LED              | COLOR         | DESCRIPTION                                                        |  |  |  |

|------------------|---------------|--------------------------------------------------------------------|--|--|--|

| PSEMTHR24EVM-081 |               |                                                                    |  |  |  |

| J15, J55         | Green, Yellow | There is one green and yellow LED on each RJ45 port                |  |  |  |

| PSEMCUDAUEVM-082 |               |                                                                    |  |  |  |

| D1               | Green         | The total power consumption is within the pre-configured guardband |  |  |  |

## 3.2.1.2.2 EVM Test Points

表 5 lists the EVM test points.

| ТР                   | LABEL    | DESCRIPTION                           |

|----------------------|----------|---------------------------------------|

| PSEMTHR24EVM-081     | F        |                                       |

| TP1                  | 55VDC    | VPWR                                  |

| TP2                  | GND      | VPWR ground                           |

| TP3                  | OC-ALERT | System over current alert signal      |

| TP4                  | SDA      | I <sup>2</sup> C data                 |

| TP5                  | SCL      | I <sup>2</sup> C clock                |

| TP6                  | PG1      | Power good signal for power supply #1 |

| TP7                  | PG2      | Power good signal for power supply #2 |

| TP8                  | PSE_3.3V | 3.3 V for PSE devices                 |

| TP9                  | GND      | PSE_3.3V ground                       |

| TP10                 | 3.3V_ISO | Isolated 3.3V for MSP430              |

| TP11                 | 3.3V     | 3.3 V for debug                       |

| TPS12 , TP13         | GND_ISO  | 3.3V_ISO ground                       |

| TP14                 | OSS      | OSS signal from MCU to PSE            |

| TPS23882EM-084       |          |                                       |

| TP1                  | PSE_3.3  | 3.3 V for PSE devices                 |

| TP2                  | VPWR     | VPWR for PSE devices                  |

| TP3, TP4, TP14, TP19 | GND      | VPWR and PSE_3.3V ground              |

| TP5                  | 3.3V_ISO | Isolated 3.3 V                        |

| TP6                  | RESET    | Reset signal from MCU                 |

| TP7                  | OSS      | OSS signal from MCU                   |

| TP8                  | INT      | INT signal to MCU                     |

| TP9                  | SDA      | I <sup>2</sup> C data from/to MCU     |

| TP10                 | SCL      | I <sup>2</sup> C clock from MCU       |

| TP11                 | PSE_RST  | Reset signal to PSE                   |

| TP12                 | PSE_OSS  | OSS signal to PSE                     |

| TP13                 | PSE_INT  | INT signal from PSE                   |

| TP15                 | GND_ISO  | 3.3V_ISO ground                       |

| TP16                 | PSE_SCL  | I <sup>2</sup> C clock signal to PSE  |

| TP17                 | PSE_SDAI | I <sup>2</sup> C data to PSE          |

| TP18                 | PSE_SDAO | I <sup>2</sup> C data from PSE        |

#### 表 5. EVM Test Points

适用于多端口应用的 24 端口(2 对)电源设备参考设计 13

# 3.2.1.2.3 EVM Jumpers

$\frac{1}{8}$  6 lists the EVM test jumpers and their descriptions.

| JUMPER                                                        | DEFAULT PIN POSITION | DESCRIPTION                            |

|---------------------------------------------------------------|----------------------|----------------------------------------|

| PSEMTHR24EVM-081                                              |                      |                                        |

| J13                                                           | 1-2                  | 3.3 V comes from PSE daughtercard      |

| J14                                                           | 1-2                  | Connect 3.3V_ISO to supply the circuit |

| J17, J22, J38, J43, J19, J23, J32, J28, J52, J47,<br>J31, J26 | 1-2                  | Enable port LED                        |

| J45, J42, J24, J21, J44, J49, J53, J30, J33, J51, J54         | 1-2                  | Enable port LED                        |

| J57, J62, J78, J83, J59, J63, J72, J68, J92, J87, J71, J66    | 1-2                  | Enable port LED                        |

| J85, J82, J64, J61, J84, J80, J89, J93, J70, J91, J94         | 1-2                  | Enable port LED                        |

| TPS23882EVM-084                                               |                      |                                        |

| J3                                                            | 1-2, 3-4             | PSE devices' address configuration     |

#### 表 6. EVM Test Jumpers

# 3.2.1.2.4 EVM Input and Output Connectors

表 7 lists the EVM input and output connectors.

| CONNECTOR                    | DESCRIPTION                                                                                                                                  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| PSEMTHR24EVM-081             |                                                                                                                                              |

| J1, J3                       | DC power supply input (44-57 V VDC, 41 A)                                                                                                    |

| J2, J4, J6, J7               | Edge connector for DC bus when connecting 2 boards together                                                                                  |

| J5                           | Power to PSE daughtercard                                                                                                                    |

| J8, J9                       | Edge connector for PSE signals (I <sup>2</sup> C, OSS, RESET and INT) when connecting 2 boards together                                      |

| J10                          | Connector to USB2ANY for direct I <sup>2</sup> C access to PSE devices(for debug purpose only)                                               |

| J11                          | Connectors to PSE daughter for PSE signals (I <sup>2</sup> C, OSS, RESET and INT)                                                            |

| J12                          | Connectors to MSP430 daughter for PSE signals (I <sup>2</sup> C, OSS, RESET and INT), system level signals (OC-ALERT, PG) and isolated 3.3 V |

| J15, J55                     | PSE ports magjacks                                                                                                                           |

| J34, J35, J36, J74, J75, J76 | PSE port connector to PSE daughter card                                                                                                      |

| J95, J96                     | For MSP430 daughter card mechanical mounting purpose                                                                                         |

| TPS23882EM-084               |                                                                                                                                              |

| J1                           | Pair with J5 on motherboard                                                                                                                  |

| J4                           | Pair with J11 on motherboard                                                                                                                 |

| J5                           | Pair with J34, J35, J36, J74, J75, J76 on motherboard                                                                                        |

| PSEMCUDAUEVM-082             |                                                                                                                                              |

| J1                           | JTAG connector                                                                                                                               |

| J3, J7, J8, J9               | Extended GPIO access                                                                                                                         |

| J11                          | Pair with J12 on motherboard                                                                                                                 |

| J12, J13, J14                | USB2ANY connector (30 pin)                                                                                                                   |

| J17, J18                     | For MSP430 daughter card mechanical mouting purpose                                                                                          |

# 3.2.1.3 System Firmware GUI Setup

## 3.2.1.3.1 PSE System Firmware GUI Installation

TI's PSE system firmware GUI is used with the PSE system EVM kit (PSEMTHR24EVM-081, PSEMCUDAUEVM-082, TPS23882EVM-084) to configure the system, generate the code image and flash to MSP430 device. Download the PSE system firmware GUI from TIDA-050026-23882 folder or PSEMCUDAUEVM-082 tool folder.

# 3.2.1.3.2 PSE System Firmware GUI Operation

Start the PSE system firmware GUI by double clicking the GUI icon and clicking the Start button. A window similar to 🕅 3 appears. The Offline mode is selected by default.

| PSE | System Firmware GUI                 | File Optio | ons Tools  | Help            |                                             |         |                   | -      | D ×          |

|-----|-------------------------------------|------------|------------|-----------------|---------------------------------------------|---------|-------------------|--------|--------------|

| ≡м  | enu                                 |            |            |                 |                                             |         |                   |        |              |

| #   | Firmware Configuration              |            |            | Mod             | ONLINE OFFLINE                              | 1 Load  | 2 Configure ····· | Review | & Generate   |

| •   |                                     |            | MSP430 Fin | mware Platform: | MSP430F5234                                 | •       |                   |        |              |

| ۹   |                                     |            |            |                 |                                             |         |                   |        |              |

| ß   |                                     |            |            |                 |                                             |         |                   |        |              |

|     |                                     |            |            |                 | •                                           |         |                   |        |              |

|     |                                     |            |            | Dr              | ag & Drop                                   |         |                   |        |              |

|     |                                     |            | or browse  |                 | te hex file config with image coo<br>Browse | de here |                   |        |              |

|     |                                     |            |            |                 |                                             |         |                   |        |              |

|     | 0                                   |            |            |                 |                                             |         |                   |        |              |

|     | Help<br>USB2ANY/OneDemo device Hard |            |            |                 |                                             |         |                   |        | OUI Composer |

## 图 3. GUI Startup

Select the MSP430 device you want to start with and then load the PSE system firmware code image (access from TIDA-050026-23882 folder or PSEMCUDAUEVM-082 tool folder). When finished, click *Proceed* to go to the configuration page.

| PSE        | System Firmware GUI                | File Op        | tions Too                                 | ols Help             | _)                                                                                                       |

|------------|------------------------------------|----------------|-------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------|

| ≡ ме       | ะกม                                |                |                                           |                      |                                                                                                          |

| #          | Firmware Configuration             |                |                                           | Mode                 | CNLINE OFFLINE 1 Load (2) Configure (3) Review & Generate                                                |

| =          |                                    |                |                                           | MSP430 Firmwar       | vare Platform: MSP430F5234                                                                               |

| ٩          |                                    | Hex            | File Upload: The                          | firmware hex file ma | matches the MSP430F5234 firmware schema!                                                                 |

| Ø          |                                    |                | PSE_Mar                                   | nager.txt            | Remove                                                                                                   |

|            |                                    |                | ware Verification                         | _                    | ¥                                                                                                        |

|            |                                    | Load           | i Default S/M Cor<br>I Default Device C   | configuration -      | ÷                                                                                                        |

|            |                                    |                | I PPM Configurati<br>I Port Configuration |                      | ¥                                                                                                        |

|            |                                    | * Los          |                                           |                      | Firmware Image - Browse<br>project. In other cases, load has file directly from Hax File Upload section. |

|            | 0                                  | Change PSE SRA |                                           |                      | Proceed                                                                                                  |

| <b>F</b> 9 | Help<br>USB2ANY/OneDemo device Har | Change PSE SRA | M Parity code -                           | Browse               | Powered By GUI Compose"                                                                                  |

#### 图 4. GUI Device Selection and Image Load

The configurations are split into four sections: system configuration, PPM (Port Power Management) configuration, device configuration, and port configuration.

The system configuration is applied to the whole system. This tab is always available on the to the right of the GUI. The following parameters can be configured through the system configuration tab:

Legacy detection functions

Legacy devices released prior to the PoE standard can be powered through the Ethernet cable. The PSE system firmware detects these legacy PDs and powers on with protection.

Use of external sensing circuit

The external sensing circuit is used to measure the total power consumption of the system. When the current exceeds the power budget, the MCU shuts down low priority ports. This increases the system response to the load step change.

- System bootup setting

- 1. Turn on the PSE port as soon as the power is up.

- 2. Turn on the PSE port after the PoE enable command is sent from the host

- Port overload retry mode

- 1. Re-enable immediately: after overload happens, the port is re-enabled immediately. If the overload still presents, it will try at most five times and shuts down the port if the overload is not removed within five retries. The port is re-enabled after the PD is removed from the port and reconnects to the port.

- 2. Re-enable after PD is disconnected and connected: after overload happens, the port is disabled immediately and is re-enabled after the PD is removed from the port and reconnects to the port.

- 3. Timer controlled: the port is re-enabled immediately after overload happens. The port keeps retrying for a period (controller by timer) and is disabled after the timer expires. The port is re-enabled after the PD is removed from the port and reconnects to the port.

- OSS signal source (from MCU or CPLD):In a multi-power supply system, when one power supply has

faults and the remaining power supply is not able to supply the current power consumption, turn off low priority ports to protect the remaining power supply. The OSS function of the PSE is used to fast shutdown the low priority ports. There are 2 sources to generate the OSS signal:

- 1. MSP430 generates the OSS signal

- 2. CPLD generates the OSS signal

- Interrupt mask

The interrupt mask in 85 can be configured to enable interrupt events to notify the host through the MSP430 P6.0.

| I | Firmware Configuration Firmw       | are Platform: MSP430F5234 Version: E0 | 000002 Mod | e ONLINE OFFLINE 1 Load                               | Configure 3 Review & Gene                                                                     |

|---|------------------------------------|---------------------------------------|------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------|

|   | PPM Config   Dev                   | vice Config 💭 Port Conf               | ig         |                                                       | System Configuration                                                                          |

|   | Power Limit Mode Class Based Limit | Power Policy Dynamic                  | •          | Mutti Power Supply Mode Power supply in Back up Moc • | Legacy Enable O Capacitance Value                                                             |

|   | Total Power Supply Number          | Power Supply 1 (Main) (Watt)          |            | Power Supply 2 (Backup) (Watt)                        | EXT Sense Enable<br>PSE System BootUp Setting<br>Turn On Immediately                          |

|   | 2 •<br>Guard Band (mWatt)          | 500                                   | ٥          | 400 \$                                                | Retry Mode O                                                                                  |

|   | 30000 \$                           |                                       |            |                                                       | OSS Source Total Ports  MCU GPIO Drive  24                                                    |

| l |                                    |                                       |            |                                                       | Interrupt Mask                                                                                |

|   |                                    |                                       |            |                                                       | PSE SRAM Fault     PSE TSD     PSE Supply Fault     Port Tstart Fault                         |

|   | Reset to Default                   |                                       |            | Proceed                                               | Port Overload Fault Port Short Circuit Fa     Port Communication Error     Powered By GUI Com |

图 5. GUI System Configuration and PPM Configuration

PPM configuration is applied to the port power management mechanism. The following parameters can be configured through the PPM configuration tab:

- Power limit mode:class limit mode and port limit mode

- 1. Class limit mode:in class limit mode, the port power is limited by the PD's class level. For example, if the PD is class 8, the port power limit(PCUT) is set to 90W.

- 2. Port limit mode:in port limit mode, the port power is limited by the host. The host should set port power limit before the port is powered on.

- Power policy: static and dynamic mode

- 1. Static mode:in static mode, the port power allocation is set to port power limit. In class limit mode, port power allocation is class level power of the PD and in port limit mode, the port power allocation is the port power limit configured from the host.

- 2. Dynamic mode: in dynamic mode, the port power allocation equals to the port's actual consumed power. It allocates the port's unused power to other ports.

- Multi-power supply mode: RPS and sharing mode:

- Redundant power supply (RPS) mode:in RPS mode, the total power budget equals to main power supply's power budget when both main power supply and backup power supply are connected. The total power budget equals to backup power supply's power budget when the main power supply is disconnected.

- 2. Sharing power supply mode:in sharing mode, the total power budget equals to the sum of two power supplies' power budget when both power supplies are connected. The total power budget equals to remaining power supply's power budget if one of the power supplies is disconnected.

- Total number of power supplies and the power budget of each power supply. If there's only one power supply, the power good signal must be connected to P1.5.

- Power guard band: when the total allocated power < total power budget guard band, there's no more low priority ports to be turned on and the guard band LED will turn on.

Device configuration is mainly used to configure the mapping between the PSE device channels and the logical RJ45 ports. When mapping a 4-pair port, only channels within the same quad (channel 1–4 or channel 5–8) can be mapped to one 4-pair port.

| Firmware | e Configurat | ion Firmw    | vare Platform: N | /SP430F523 | 4 Version: E | 0000002   | Mode: 0   |           | OFFLINE   | Load •••••• 2 Configure ••••• 3 Review & C                                                               | ener |

|----------|--------------|--------------|------------------|------------|--------------|-----------|-----------|-----------|-----------|----------------------------------------------------------------------------------------------------------|------|

| B PPM    | Config       | 🗐 De         | vice Config      | C          | Port Co      | nfig      |           |           |           | System Configuration                                                                                     |      |

|          | Device Chan  | inel Mapping | 9 (0)            |            |              |           |           | Validat   | e & Save  | Legacy Enable ③    ●<br>Legacy Mode    Power Value                                                       |      |

|          | ⊘ Valid      | Channel 1    | Channel 2        | Channel 3  | Channel 4    | Channel 5 | Channel 6 | Channel 7 | Channel 8 | Capacitance • 30 W                                                                                       | •    |

|          | Device 1     | 13           | 13               | 14         | 14           | 15        | 15        | 16        | 16        | PSE System BootUp Setting                                                                                |      |

|          | Device 2     | 17           | 17               | 18         | 18           | 1         | 1         | 2         | 2         | C<br>Retry Mode ⊙<br>Re-enable port in ▼                                                                 |      |

|          | Device 3     | 3            | 3                | 4          | 4            | 5         | 5         | 6         | 6         | OSS Source Total Ports O                                                                                 |      |

|          | Device 4     | 19           | 19               | 20         | 20           | 21        | 21        | 22        | 22        | MCU GPIO Drive  24 Interrupt Mask                                                                        | ¢    |

|          |              |              |                  |            |              |           |           |           |           | <ul> <li>PSE SRAM Fault</li> <li>PSE TSD</li> <li>PSE Supply Fault</li> <li>Port Tstart Fault</li> </ul> |      |

| Reset to | o Default    |              |                  |            |              |           |           |           | Proceed - | Port Overload Fault 🗹 Port Short Circui                                                                  |      |

图 6. GUI Device Configuration

The *Port Configuration* is applied to the port by port settings, such as port PoE enable and disable, port priority, and port power limit (only in port limit mode).

| ≡ ме   | System Firmware GUI File Options Tools Help                                                  |                                                                         |                                                                                                                                                                                                                                                                |

|--------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *      | Firmware Configuration Firmware Platform: MSP430F5234 Version: E0000002 Mode:                | ONLINE OFFLINE 1 Load ···                                               | 2 Configure 3 Review & Gen                                                                                                                                                                                                                                     |

| •      | 🗄 PPM Config 🛛 Device Config 💭 Port Config                                                   |                                                                         | System Configuration                                                                                                                                                                                                                                           |

| a<br>C | RJ45 Port Config () Hold Cttl and select multiple ports to configure and apply same settings | Selected RJ45 Port -  Physical Channel: 12,13 Port Enable Priority High | Legacy Enable O<br>Legacy Mode Power Value<br>Capacitance 30 W<br>EXT Sense Enable PSE System BootUp Setting<br>PSE System BootUp Setting<br>Turn On Immediately •<br>Retry Mode O<br>Re-enable port in •<br>OSS Source Total Ports O<br>MCU GPIO Drive • 24 • |

|        |                                                                                              |                                                                         | Interrupt Mask                                                                                                                                                                                                                                                 |

When everything has been configured, click the *Proceed* button. The summary page displays all of the configurations being set compared to the factory default configurations. When everything is verified, you can generate the hex file or flash the code to the MSP430 device directly.

| 图 8 GUI  | Configuration | Summary |

|----------|---------------|---------|

| B 0. 001 | Conniguration | Summary |

| -      | System and PPM Config | uration Summary     |               |                            |                                       |                           |

|--------|-----------------------|---------------------|---------------|----------------------------|---------------------------------------|---------------------------|

|        |                       | System Configuratio | n             |                            | PPM Configuration                     |                           |

| $\Box$ | Config                | Default             | User          | Config                     | Default                               | User                      |

|        | Legacy Enable         | ON                  |               | Power Limit Mode           | Class Based Limit                     | Class Based Limit         |

|        | Legacy Mode           | ON                  | Capacitance • | Power Policy               | Dynamic                               | Dynamic                   |

|        | Power Value           | 30 W                | 30 W 🔻        | Multi Power Supply<br>Mode | Power supply in Back up<br>Mode [RPS] | Power supply in Back up ? |

|        |                       |                     |               | v Device Config            |                                       |                           |

When configurations are reviewed, the GUI can generate the default code image and program the device directly through **MSP-FET**.

| F | Firmware  | Configuration Fir    | Import Project Version | m E0000002 Mode: ONLIN |                            | Configure                             | Review & Ger              |

|---|-----------|----------------------|------------------------|------------------------|----------------------------|---------------------------------------|---------------------------|

|   |           | System and PPM Confi | -                      |                        |                            |                                       |                           |

|   |           |                      | System Configuration   |                        |                            | PPM Configuration                     |                           |

|   | $\square$ | Config               | Default                | User                   | Config                     | Default                               | User                      |

|   |           | Legacy Enable        | ON                     |                        | Power Limit Mode           | Class Based Limit                     | Class Based Limit         |

|   |           | Legacy Mode          | ON                     | Capacitance •          | Power Policy               | Dynamic                               | Dynamic                   |

|   |           | Power Value          | 30 W                   | 30 W 🔹                 | Multi Power Supply<br>Mode | Power supply in Back up<br>Mode [RPS] | Power supply in Back up t |

|   |           |                      |                        | Review                 | Device Config              |                                       |                           |

图 9. GUI Program Device and Generate Hex

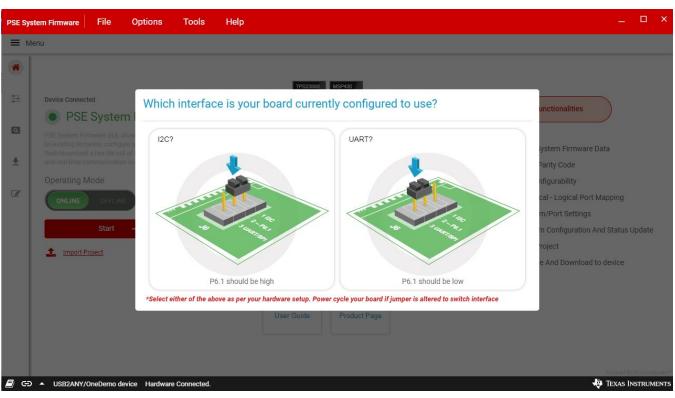

When the code is successfully flashed to the MSP430, the system will be up and running. MSP-FET can be disconnected from the laptop or PC. Connect the USB2ANY (with 30-pin ribbon cable) to a laptop or PC and the GUI will be in online mode after selecting host interface protocol.

#### 图 10. Host Interface Protocol Selection in Online Mode

When the device is connected to GUI, real-time changes can be made on the configuration page and status page shows the real time system status. The status page shows the system, device, and port real-time status. The user can also change the system configuration in the configuration page: each change is converted to a host command to the MSP430 MCU. The user can also press the *Save Configuration* button to save the current configuration as the default setting.

| 图 | 11. | GUI | Status | Page |

|---|-----|-----|--------|------|

|---|-----|-----|--------|------|

| System State       | IS |       |               |     |    |                |     |                                   |             | Auto Read S               | Status : Readi |

|--------------------|----|-------|---------------|-----|----|----------------|-----|-----------------------------------|-------------|---------------------------|----------------|

| RJ45 Port Config ( | D  |       |               |     |    |                |     |                                   |             |                           |                |

| 1                  | 2  | 3     | 4             | 5   | 6  | 7              | 8   | Selected Port - 1                 | Port I2C A  | ddress - 0x22 Physical Ch | annels - 12,13 |

|                    |    |       |               |     |    |                |     | Port Status<br>Port On/Off        | •           | Port Consumed Power       | 0 mW           |

| 9                  | 10 | 11    | 12            | 13  | 14 | 15             | 16  |                                   | oen Circuit | Port Priority             | High           |

|                    |    |       |               |     |    |                |     | Classification<br>Port Faults     | Unknown     |                           |                |

|                    |    |       |               |     |    |                |     | Overload Fault                    | •           | Short Fault               | •              |

| 17                 | 18 | 19    | 20            | 21  | 22 | 23             | 24  | Start Fault<br>Port Fault Counter | •           |                           |                |

|                    |    |       |               |     |    |                |     | Disconnect Counter                | 0           | Invalid Signature Counter | 0              |

|                    |    |       |               |     |    |                |     | Overload Counter                  | 0           | Power Deny Counter        | 0              |

|                    |    |       |               |     |    |                |     | Short Counter                     | 0           |                           |                |

| Device Faults      |    |       |               |     |    | System Statu   | S   |                                   |             |                           |                |

| SRAM Fault         |    | [2] \ | VPUV/VDUV Fau | H ( | 0  | Guard Band Ale | ert | <ul> <li>Input Voltage</li> </ul> | 49 V        | Total Allocated Power     | 7673 mW        |

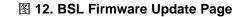

The BSL firmware update page provides the field firmware upgrade functions that the firmware can be upgraded through the same I<sup>2</sup>C or UART port as the normal communication. This is beneficial to firmware upgrade after the product is released to customers.

| PSE S      | System Firmware File Options Tools                | Help                                 |                                                                                    |                                                                |  |  |

|------------|---------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|

|            | Menu                                              |                                      |                                                                                    |                                                                |  |  |

| *          | BSL Firmware Update                               |                                      |                                                                                    |                                                                |  |  |

| - <u>t</u> |                                                   | (i) Upload the Firmware              | File and Click 'Update System                                                      | n Software'                                                    |  |  |

| q          |                                                   |                                      |                                                                                    |                                                                |  |  |

| ٠          | •                                                 |                                      | U U                                                                                | ease uncheck if you want to exclude any of the below two steps |  |  |

| I          | Drag & Dr                                         | ор                                   | <ul> <li>Enable BSL Mode(Step 1)</li> <li>Verify Loaded Program(Step 5)</li> </ul> |                                                                |  |  |

|            | or browse for the complete hex file con<br>Browse |                                      | Upr                                                                                | date System Software                                           |  |  |

|            | 1                                                 | 23                                   |                                                                                    |                                                                |  |  |

|            | Entered BSL<br>Mode                               | Password Mass Erase<br>Verified Done | Firmware Program<br>Load Verified                                                  | Powered By GU Compose                                          |  |  |

| <i>E</i> e | USB2ANY/OneDemo device Hardware Connected.        |                                      |                                                                                    | 🐺 Texas Instrument                                             |  |  |

22 适用于多端口应用的 24 端口(2 对)电源设备 参考设计

ZHCA962-October 2019

Before using BSL page to update the MSP430 firmware, BSL code needs to be flashed to MSP430 if it hasn't been flashed. Download Uniflash from ti.com and use it to flash the BSL code by following the steps:

Select MCU device to MSP430F5234.

| 图 | 13. | MCU | Device | Selection | Page |

|---|-----|-----|--------|-----------|------|

|---|-----|-----|--------|-----------|------|

| 🛃 UniFlash                                                                               | <u></u> | ΠX         |

|------------------------------------------------------------------------------------------|---------|------------|

| UniFlash Session - About                                                                 | ? Help  | 🔅 Settings |

|                                                                                          |         |            |

| Detected Devices                                                                         |         |            |

| Detect My Device Connected devices will automatically appear here! [More Info] Start Now |         |            |

| ✓ New Configuration                                                                      |         |            |

| Selected Device: MSP430F5234                                                             |         | ~ ×        |

| Selected Connection: 🖤 TI MSP430 USB1                                                    |         | ~ ×        |

| 3 Start Edit                                                                             |         |            |

| ✓ Create Session From Existing Target Configuration File                                 |         |            |

| Select a .coxml file to create a new session.                                            |         |            |

|                                                                                          |         |            |

Configure the flash section.

🛃 UniFlash × UniFlash Session -About ? Help 🔹 Settings Configured Device : TI MSP430 USB1 > MSP430F5234 [more info] [download ccxml] MSP430 Program Find and Configure Settings and Utilities Settings & Utilities I More Info Pin Option Q Search: Enter Property ID Or Name To Search For Settings and Buttons × Memory Download Standalone Command Line Target Voltage (mV): 3300 Allow Read/Write/Erase access to BSL memory Erase Options: O Erase main memory only O Erase main and information memory • Erase main, information and protected information memory O Erase and download necessary segments only (Differential Download) O Replace written memory locations, retain unwritten memory locations O By Address Range (specify below) ▼ Erase Console ≡ Clear X Close

# 图 14. Configure Settings and Utilities Page

Load BSL code and flash to MSP430.

Hardware, Software, Testing Requirement and Test Result

www.ti.com.cn

| 图 15. Select and Load Images Pa | 图 | 15. Select | and | Load | Images | Page |

|---------------------------------|---|------------|-----|------|--------|------|

|---------------------------------|---|------------|-----|------|--------|------|

| 🗲 UniFlash                        |                                                                                                                                                                                           |                |          | ×    |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|------|

| UniFlash Session -                | About                                                                                                                                                                                     | ? Help         | 🄹 Setti  | ings |

| Configured Device : TI MSP430 USB | 1 ➤ MSP430F5234 [more info] [download ccxml]                                                                                                                                              |                | MSP4     | 430  |

| Program                           | Select and Load Images                                                                                                                                                                    |                |          |      |

| Settings & Utilities              | Flash Image(s)                                                                                                                                                                            |                |          |      |

| Memory                            | MSP430F522x_J2C.txt Size: 7.75                                                                                                                                                            | KB   Binary: [ | <b>x</b> |      |

| Standalone Command Line           | Available Action(s) - 1 Image Selected  Load Image Verify Image  Reset Actions  [Click here to query available reset options]  Run Actions  Run Target After Program Load/Flash Operation |                |          |      |

|                                   | ▼ Quick Settings                                                                                                                                                                          |                |          | •    |

| Console                           |                                                                                                                                                                                           | ≡ Clear        | × cl     | iose |

|                                   |                                                                                                                                                                                           |                |          |      |

In the debug page, user's can read and write raw data to MSP430 following host interface protocol and to each PSE device's registers by providing I<sup>2</sup>C address and register number. The password is "C430".

Design Files

#### www.ti.com.cn

## 图 16. Debug Page

| PSE S    | SE System Firmware File Options Tools Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |