# 时钟噪声对 DAC 性能影响系统分析

FANLONG LI

## 摘要

数模转换器 DAC 是无线通信系统中的核心器件。随着技术的发展, DAC 所能支持的输出频率和工作时钟越来越高, 例如目前 TI 推出的高速, 高集成射频采样 AD/DA (AFE7689) 能支持输出/输入到 5.2G, DAC 能支持高达 9G 的采样率。随着能支持频率的不断提高, 意味着 AD/DA 越来越接近于天线端, 其性能也将直接影响着整个系统的性能。随着支持的工作时钟的提高, 意味着其对时钟性能会更加敏感, 例如时钟上的杂散, 底噪在 AD/DA 的输出端将如何变化? 类似问题已经成为客户系统设计时候必须考虑的问题。如何量化这些影响从而给客户正确的指导, 对我们推介 AD/DA 也显得尤为重要。本文将理论和实际测试相结合来分析时钟噪声对 DAC 性能和客户系统指标的影响, 为客户进行系统设计以及我们推介 AD/DA 提供指导。

Key words: 无线通信系统 DAC 时钟噪声 系统分析 波形质量 (EVM)

## 目录

|                                          |           |

|------------------------------------------|-----------|

| <b>1 时钟噪声对 DAC 影响的表征</b> .....           | <b>3</b>  |

| 1.1 时钟随机噪声对 DAC 的影响 .....                | 3         |

| 1.2 时钟杂散对 DAC/ADC 的影响 .....              | 3         |

| <b>2 时钟噪声对 DAC 性能影响的理论分析</b> .....       | <b>4</b>  |

| 2.1 时钟随机噪声对 DAC 性能影响理论分析 .....           | 4         |

| <b>3 时钟固定杂散对 ADC/DAC 性能影响的理论分析</b> ..... | <b>6</b>  |

| 3.1 ADC/DAC 采样系统模型 .....                 | 6         |

| 3.2 DAC 采样系统中对信号有影响的时钟噪声积分带宽 .....       | 7         |

| <b>4 时钟噪声对 DAC 的系统指标影响分析</b> .....       | <b>8</b>  |

| 4.1 时钟随机噪声对 DAC 的 EVM 影响分析 .....         | 8         |

| 4.1.1 EVM 定义及其和时钟相位噪声之间关系 .....          | 8         |

| 4.1.2 相位噪声对 EVM 影响的计算工具 .....            | 9         |

| 4.1.3 DAC 采样系统中时钟相位噪声对 EVM 影响计算结论 .....  | 9         |

| 4.2 时钟固定杂散噪声对 DAC SFDR 影响分析 .....        | 9         |

| <b>5 时钟噪声对 DAC 影响的一个实际案例</b> .....       | <b>10</b> |

| 5.1 时钟随机噪声对 TX EVM 影响 .....              | 10        |

| 5.2 时钟固定杂散噪声对 DAC SFDR 影响 .....          | 10        |

| <b>6 参考文献</b> .....                      | <b>11</b> |

## 图

|                                                                 |    |

|-----------------------------------------------------------------|----|

| <b>Figure 1</b> 时钟理想 (左) 和非理想 (右) <b>DAC</b> 数字输入.....          | 3  |

| <b>Figure 2</b> 时钟理想 (左) 和非理想 (右) <b>DAC</b> 模拟输出.....          | 3  |

| <b>Figure 3</b> 时钟的抖动引发 <b>DAC</b> 输出模拟量的抖动 .....               | 4  |

| <b>Figure 4</b> 时钟中存在一个固定抖动示意图.....                             | 6  |

| <b>Figure 5</b> 带有固定时钟杂散的 <b>DAC</b> 采样过程.....                  | 7  |

| <b>Figure 6</b> 均匀时钟噪声和时钟杂散之间的等效过程 .....                        | 7  |

| <b>Figure 7</b> 误差矢量信号定义示意图 (左) 和 QPSK 星座图 (右) .....            | 8  |

| <b>Figure 8</b> 梯形法计算时钟均匀噪声过程示意图 .....                          | 9  |

| <b>Figure 9</b> 时钟随机噪声对 <b>EVM</b> 影响的实际测试.....                 | 10 |

| <b>Figure 10</b> 时钟上的 <b>spur</b> 到 <b>DAC</b> 的输出的转换的实际测试..... | 10 |

## 1 时钟噪声对 DAC 影响的表征

本文将时钟噪声分为两大类，一类是随机噪声即通常所说的相噪，一类是杂散 spur，下面将分别进行论述。

### 1.1 时钟随机噪声对 DAC 的影响

时钟随机噪声，我们通常用时钟抖动/相噪来衡量，该类噪声服从高斯统计特性。

尽管 ADC/DAC 的实现电路/硬件架构完全不同，但时钟对其影响所表现的特性完全类似。下面以 DAC 为例来加以说明。

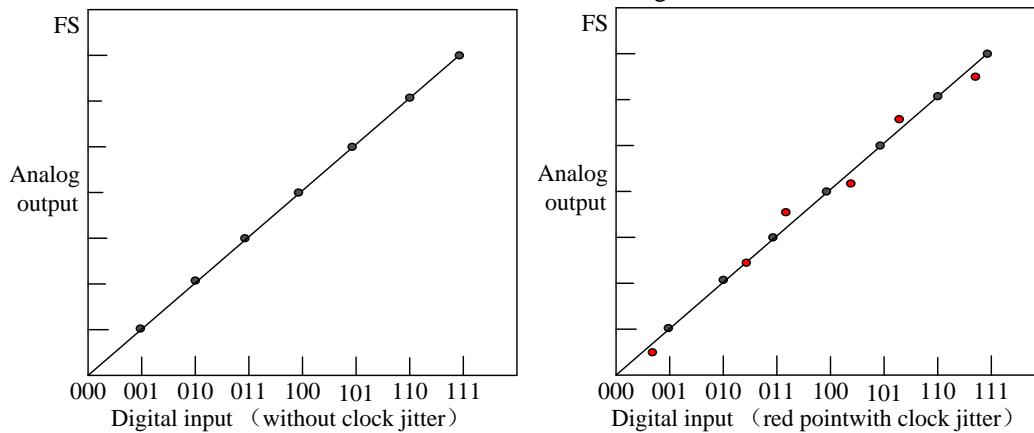

如果没有考虑到时钟抖动的影响，那么理想的 DAC 其传输函数应该是严格的等间距的也就是说数字信号的输入时刻的严格固定的，如下图 Figure 1 左图所示是一个单极限理想的 3bitDAC，假设时钟抖动，那么数字信号输入的时刻就不可能严格固定，可能提前也可能滞后，从而出现了抖动如 Figure 1 中右图所示。

**Figure 1 时钟理想（左）和非理想（右）DAC 数字输入**

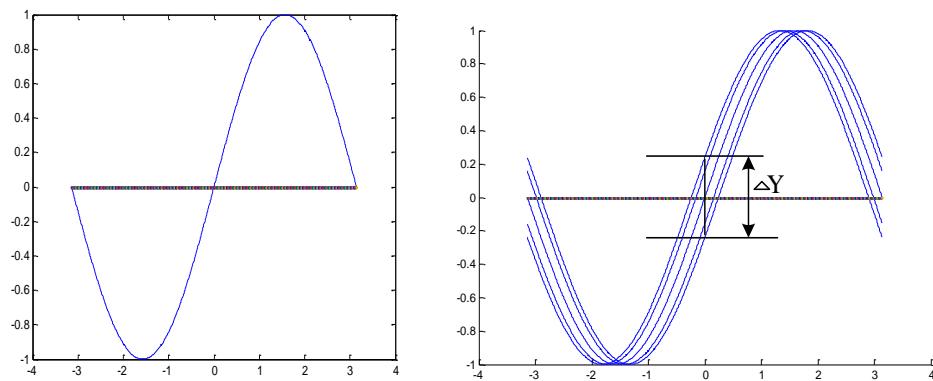

DAC 的量化经过成型滤波器后就可以得到模拟输出，如果没有抖动，那么输出模拟信号的幅度将是固定的如下图 2 左图所示，如果时钟抖动那么输出的模拟先后的幅度将会有一个  $\Delta Y$  的变化，如下图 2 右图所示，这就是一种噪声，随着时钟抖动的随机性，则这种抖动也呈现一种随机性，在第二节会详细分析这类时钟上的噪声是如何转换到 DAC 的输出端的，并如何呈现出对系统指标的影响。

**Figure 2 时钟理想（左）和非理想（右）DAC 模拟输出**

### 1.2 时钟杂散对 DAC/ADC 的影响

时钟杂散不具有随机特性，特表征的是固定特性，其主要影响的就是 DAC/ADC 的 SFDR。第二节中会详细分析固定的时钟杂散对 DAC/ADC 的影响和具体的表征形式。

## 2 时钟噪声对 DAC 性能影响的理论分析

### 2.1 时钟随机噪声对 DAC 性能影响理论分析

从 1 节中可以看到由于时钟的抖动使得 DAC 的输出产生了一个随机的变量  $\Delta y$  即为随机噪声，该噪声会降低输出信号的信噪比，下面推导  $\Delta y$  的表达式从而推导出对信号的影响。

首先从相位噪声和时钟抖动之间的关系开始。下面公式 2-1 给出了相位的噪声和时钟抖动之间的关系[1]。

$$\sigma_\theta^2 = \omega_{clk}^2 \sigma_t^2 \quad (2-1)$$

式中  $\sigma_\theta^2$  = 相位噪声的 RMS 值 用弧度表示。

$\sigma_t^2$  = 时钟的抖动的 RMS 值，单位是秒。

$\omega_{clk}^2$  = 时钟的频率单位是弧度/秒。

由式 2-1 中可以看出，如果抖动相同，那么高频信号的噪声要严重得多。时钟  $\sigma_\theta$  噪声是相噪在整个频率范围内的积分，同时定义时钟的信噪比为：

$$SNR_{clk} (dB) = -10 \log(\sigma_\theta^2)$$

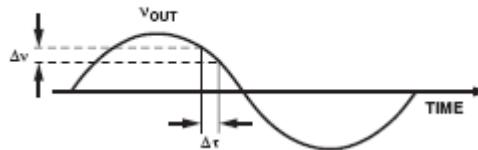

从上一节可以看到已知的是时钟的抖动，即横坐标  $\Delta t$ ，需要求出的噪声是横坐标的， $\Delta y$  可以用如下的示意图来展开求解。

Figure 3 时钟的抖动引发 DAC 输出模拟量的抖动

利用导数的关系，已知微变的  $\Delta \tau$  可以求出微变的  $\Delta v$ ：

$$\begin{aligned} \Delta v(t) &= \Delta t \times v'_{out}(t) \\ E\{\Delta v^2(t)\} &= E\{\Delta t^2 \times v'_{out}^2(t)\} \\ E\{\Delta v^2(t)\} &= E\{\Delta t^2\} \times E\{v'_{out}^2(t)\} \end{aligned}$$

可以得到：

$$\sigma_{err}^2 = \sigma_t^2 \times E\{v'_{out}(t)\} \text{ 这里 } \sigma_t^2 \text{ 是 } (rms \quad seconds)^2$$

已知噪声就可以计算出时钟的抖动引起了信噪比的恶化：

$$SNR_{sig} = \frac{\text{signal\_power}}{\text{noise\_power}} = \frac{\sigma_{out}^2}{\sigma_{err}^2} = \frac{1}{\sigma_t^2} \frac{E\{v_{out}^2(t)\}}{E\{v'_{out}^2(t)\}} \quad (2-2)$$

为了简单起见，我们假设输出是一个单音，可以根据公式 2-2 计算出 SNR，即：

$$v_{out}(t) = A \sin \omega_0 t$$

$$v'_{out}(t) = Aw_0 \cos \omega_0 t$$

因此可以计算出相应的均方差为：

$$E\{v_{out}^2(t)\} = \frac{A^2}{2}$$

$$E\{v_{out}(t)\} = \frac{w^2_0 A^2}{2}$$

利用 2-2 可以计算出单音的信噪比:

$$SNR_{sig} = \frac{1}{\sigma_t^2} \frac{\frac{A^2}{2}}{\frac{w^2_0 A^2}{2}} = \frac{1}{\sigma_t^2} \frac{1}{w^2_0} = \frac{1}{4\pi^2 f^2_0 \sigma_t^2}$$

用 dB 表示:

$$SNR_{sig}(dB) = -20 \log(2\pi f_0 \sigma_t) \quad (2-3)$$

在采样的系统中, 更注重的是时钟和采用信号的频点之间的关系, 那么可以将公式 (2-3) 表示为:

$$SNR_{sig} = \frac{1}{\sigma_t^2} \frac{\frac{A^2}{2}}{\frac{w^2_0 A^2}{2}} = \frac{1}{\sigma_t^2} \frac{1}{w^2_0} = \frac{1}{\sigma_\theta^2} \left( \frac{f_{clk}}{f_{sig}} \right)^2 = SNR_{clk} \left( \frac{f_{clk}}{f_{sig}} \right)^2 \quad (2-4)$$

参考文献【2】对于带通信号公式 (2-4) 可以表示为:

$$SNR_{sig} = \frac{1}{\sigma_t^2} \frac{\frac{A^2}{2}}{\frac{w^2_0 A^2}{2}} = \frac{1}{\sigma_t^2} \frac{1}{w^2_0} = \frac{1}{\sigma_\theta^2} \frac{f_{clk}^2}{(f^2_0 + \frac{BW^2}{12})} = SNR_{clk} \frac{f_{clk}^2}{(f^2_0 + \frac{BW^2}{12})}$$

实际系统中, 例如 CDMA 系统, 应用中心频点在 147MHZ, 而对一个载波而言带宽为 1.23M, 所以完全可以用式 (2-4) 来代替式。

在实际的运用中更习惯用 dBc 来表示信噪比, 则 (2-4) 用 dB 表示:

$$SNR_{sig}(dB) = SNR_{clk}(dB) + 20 \log f_{clk}(dB) - 20 \log(f_0)(dB) \quad (2-5)$$

对于 DAC 我们需要考虑信号的 sinc 效应, 所以基于公式 (2-5) 需要进一步转换。按照 Sinc 的公式并结合 2-4 式, 我们可以得到 DAC 是信噪比的表现形式。

$$\frac{N}{S} = \sigma_\theta^2 \left( \frac{f_{sig}}{f_{clk}} \right)^2 \quad (2-6)$$

考虑到 sinc 效应即  $\frac{\sin(\frac{\pi f_{sig}}{f_{clk}})}{\frac{\pi f_{sig}}{f_{clk}}}$  上式变换为:

$$\frac{N}{S} = \sigma_\theta^2 \left( \frac{\sin(\frac{\pi f_{sig}}{f_{clk}})}{\pi} \right)^2 \quad (2-7)$$

$$SNR_{sig}(dB) = SNR_{clk}(dB) + 20 \log \left( \frac{\pi}{\sin \left( \frac{\pi f_{sig}}{f_{clk}} \right)} \right) (dB)$$

从 2-7 中可以看出，时钟上的噪声随着输出频率的增加，对 DAC 信噪比的影响几乎保持不变。

### 3 时钟固定杂散对 ADC/DAC 性能影响的理论分析

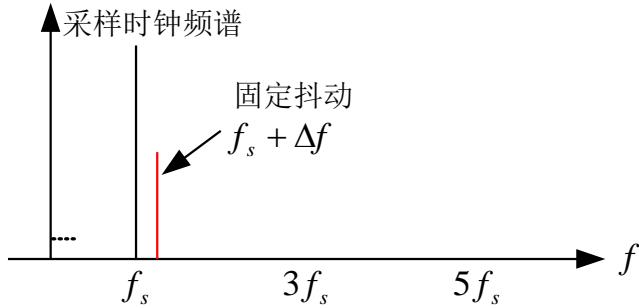

这里提出这样一个问题：如果 ADC/DAC 的时钟在离中心频点有一个固定的杂散，那么这个杂散是如何体现 ADC/DAC 输出端呢？下图 4 表示的是在距离时钟频点  $\Delta f$  处存在一个固定的杂散，那么输出信号的频谱会是什么样的呢？下面进行理论分析。

Figure 4 时钟中存在的一个固定抖动示意图

#### 3.1 ADC/DAC 采样系统模型

任何一个连续信号  $x_a(t)$  采样后的信号可以表示如下：

$$x(nT_s) = x_a(t) \Big|_{t=nT_s} = x_a(t) \times p(t) \quad (3-1)$$

$$p(t) = \sum_{-\infty}^{+\infty} \delta(t - nT_s)$$

从 3-1 式可以知道采样的过程在时域上是被采样信号和冲击串函数相乘，冲击串函数的周期为  $T_s = \frac{1}{f_s}$ 。两个信号在时域的乘积其在频域对应的是卷积。所以采样的过程在频域内就是一个卷积的过程。知道时钟的频点为  $f_s$ ，那么对应的冲击串的 Fourier 变换为：

$$P(j\Omega) = \frac{2\pi}{T_s} \sum_{k=-\infty}^{\infty} \delta(\Omega - k\Omega_s) \quad (3-2)$$

$$\Omega_s = \frac{2\pi}{T_s} = 2\pi f_s$$

那么对于一个有固定时钟抖动的冲击串可以表示为：

$$P(j\Omega) = \frac{2\pi}{T_{s1}} \sum_{k=-\infty}^{\infty} \delta(\Omega - k\Omega_{s1}) + \frac{2\pi}{T_{s2}} \alpha \sum_{k=-\infty}^{\infty} \delta(\Omega - k\Omega_{s1} - k2\pi\Delta f) \quad (3-3)$$

$$\Omega_{s1} = \frac{2\pi}{T_{s1}} = 2\pi f_{s1} \quad \Omega_{s2} = \frac{2\pi}{T_{s2}} = 2\pi(f_{s1} + \Delta f)$$

式中 3-3 中  $\alpha$  表示一个比例系数。假设连续信号的 Fourier 变换为  $X_s(j\Omega)$ 。那么如果用带有杂散的时钟如 2-8 所以作为采样的时钟，输出的信号可以表示为：

$$X_s(j\Omega) = X_a(j\Omega) * \left[ \frac{2\pi}{T_{s1}} \sum_{k=-\infty}^{\infty} \delta(\Omega - k\Omega_{s1}) + \frac{2\pi}{T_{s2}} \alpha \sum_{k=-\infty}^{\infty} \delta(\Omega - k\Omega_{s1} - k2\pi\Delta f) \right]$$

即：

$$X(e^{j\omega}) = \frac{1}{T_s} \sum_{k=-\infty}^{\infty} X_a(j2\pi f - j2\pi k f_s) + \frac{\alpha}{T_s} \sum_{k=-\infty}^{\infty} X_a(j2\pi f - j2\pi k(f_s + \Delta f)) \quad (3-4)$$

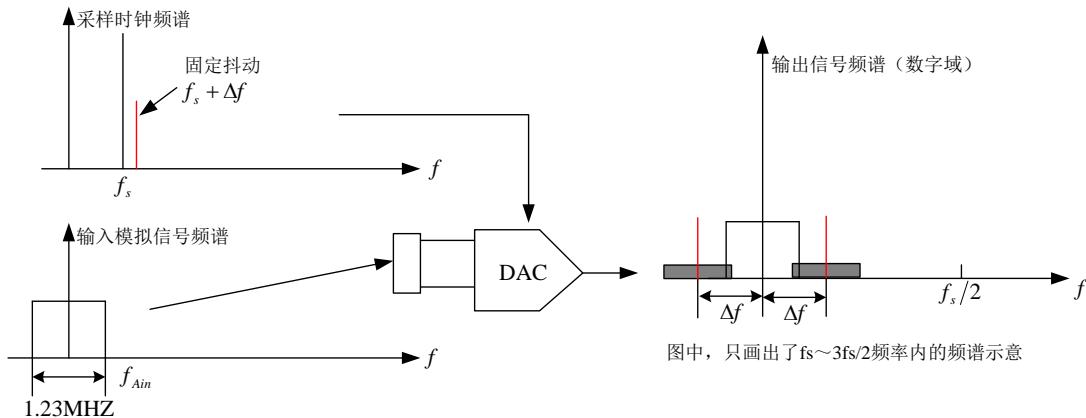

由 3-4 可以看出，在偏离时钟  $\Delta f$  处的杂散也会等间隔的体现到输出的信号上，如下图 5 是一个以 CDMA 信号为例，时钟带有固定杂散的 DAC 采样过程。

Figure 5 带有固定时钟杂散的 DAC 采样过程

### 3.2 DAC 采样系统中对信号有影响的时钟噪声积分带宽

从图 5 可以看到如果杂散在偏离时钟  $(-2B, +2B)$  的范围内其中  $B$  为信号的带宽，那么采样后将落入信号带内从而影响了带内指标。时钟的相位噪声，可以等效为无穷多个固定的抖动如下图 6 所示，所以在计算相位噪声中对信号影响的集中在  $(-B, B)$  内，考虑到时钟的相位均匀噪声用单边来表示，所以积分的上下限为：

- 下限：信号在时域的帧周期。如果时钟的抖动小于帧周期，其缓慢变化可以理解为固定的相位，则对最终信号的解调没有影响。例如以 20M LTE 为例，通常，其帧的周期 10ms 对应的频率为 100HZ，所以真正对信号有影响的时钟下限 100HZ 开始。

- 上限：信号的带宽的一半，只有该部分噪声才会落入到信号带内，例如 20M LTE 信号为 10M。所以 LTE 的积分范围为 [100HZ, 10M]。

Figure 6 均匀时钟噪声和时钟杂散之间的等效过程

## 4 时钟噪声对 DAC 的系统指标影响分析

### 4.1 时钟随机噪声对 DAC 的 EVM 影响分析

#### 4.1.1 EVM 定义及其和时钟相位噪声之间关系

前面的几个章节理论分析了 DAC 采样时钟噪声对信号的影响，主要体现在对信号影响的大小和对信号影响的积分带宽。所有噪声最终体现对信号的系统指标的影响，对于 DAC 的随机噪声，其影响就体现在波形质量 EVM 上。

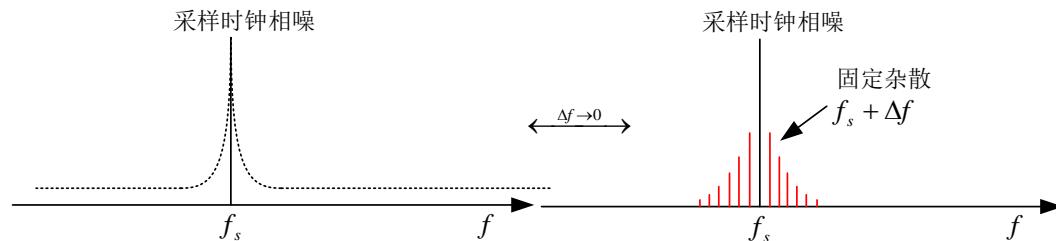

EVM 的定义如下图左图所示，通过 EVM 的定义，需要推导出在 DAC 采样系统中和相位噪声关系。这里结合一个 QPSK 的星座图来进行推导，如下图右所示，对其他的调制方式一样适用。

Figure 7 误差矢量信号示意图（左）和 QPSK 星座图（右）

EVM 定义为误差矢量和参考矢量之间的比值，如下式所示：

$$EVM = \sqrt{\frac{\int (x(t) - s(t))^2 dt}{\int x(t)^2 dt}} \quad (4-1)$$

式中， $x(t)$  为矢量 reference signal， $s(t)$  为矢量输入信号。EVM 定义结合 QPSK 星座图可以得到 EVM 表达式。

设圆的半径为  $R$ ，按照 EVM 的定义和三角公式可以得到  $E^2 = 2 \cdot R^2 - 2 \cdot R^2 \cdot \cos(\phi)$ 。当  $\phi$  很小时，满足 Taylor 式： $\cos(\phi) = 1 - \frac{\phi^2}{2}$ ，就可以得到以下关系：

$$EVM = \phi = 100\% \cdot \left( \frac{\pi}{180} \right) \cdot (RMS \text{ phase error in degree}) \quad (4-2)$$

公式 4-2 说明了相位噪声的弧度大小和 EVM 之间的关系，为了从实际相位噪声图中计算出相位噪声的 RMS 值，也将相位噪声的 RMS 表达式给出如下 4-3 所示：

$$RMS = \frac{180}{\pi} \cdot \sqrt{2 \cdot \int_0^{\infty} L(f) df} \quad (\text{单位为度}),$$

$$EVM = 100\% \times \sqrt{2 \cdot \int_0^{\infty} L(f) df} \quad (4-3)$$

公式 4-3 说明了信号相位噪声的弧度值就是其对应波形质量（EVM）值。

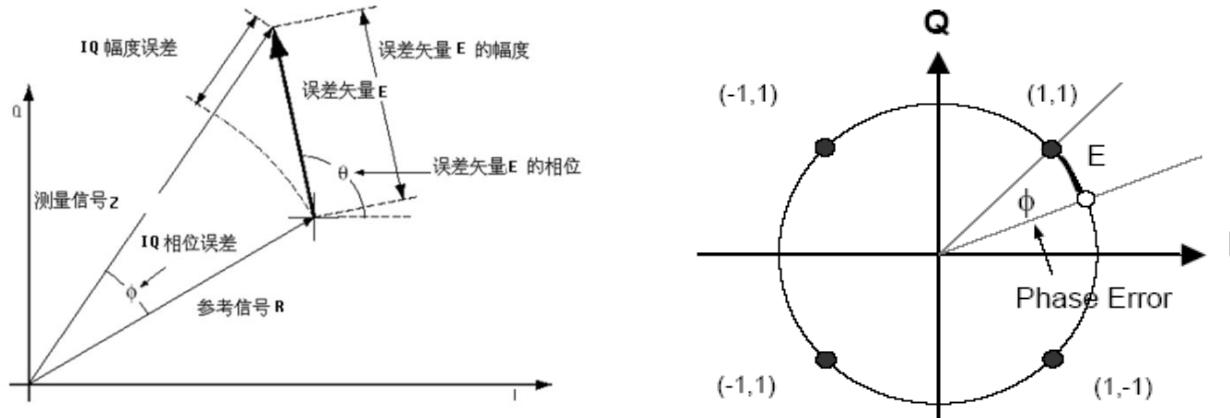

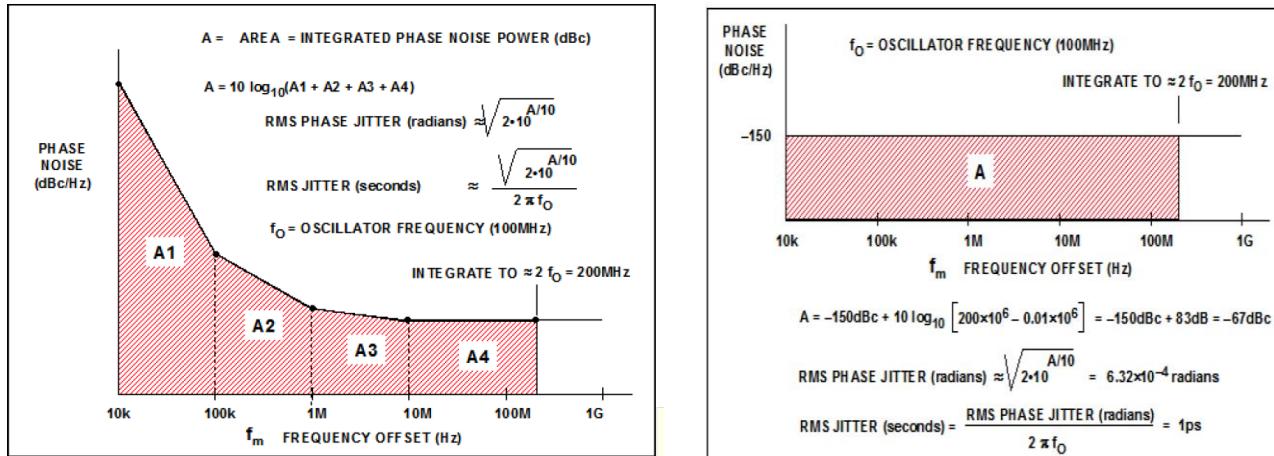

#### 4.1.2 相位噪声对 EVM 影响的计算工具

参考公式 4-3 相位噪声（弧度）就是相噪谱密度的积分，所以计算相位噪声最简单的方法是采样“梯形方法”（Trapezium method），如下图 8 所示，在计算各块面积时候先将 dBc 转换为线性，最后算出总的面积后取双边带噪声可以计算出总的相噪声弧度值。

$$\int_{f_0}^{f_1} L(f) df = \frac{1}{2} \cdot \Delta x \cdot [f(x_2) + f(x_1)]$$

Figure 8 梯形法计算时钟均匀噪声过程示意图

#### 4.1.3 DAC 采样系统中时钟相位噪声对 EVM 影响计算结论

综上所述，计算时钟的相位噪声对 DAC 的影响的整体思路为：

- 第一步，先测试出时钟的噪声，然后按照公式 2-7 转化成 DAC 输出信号的噪声；

- 第二步，结合 3.2 节来确定影响信号的积分带宽。

- 第三步，利用 4.1.2 中的计算方法计算对应积分带宽内的时钟抖动弧度值，该抖动值即为信号的波形质量（EVM）。

通常的会用 EXCEL 表格给出如下图所示的计算工具。

| =10*LOG10(0.5*(100-10)*(10^(K2/10)+10^(L2/10))) |       |      |       |        |      |      |          |            |          |          |         |         |              |      |             |      |

|-------------------------------------------------|-------|------|-------|--------|------|------|----------|------------|----------|----------|---------|---------|--------------|------|-------------|------|

| K                                               | L     | M    | N     | O      | P    | Q    | R        | S          | T        | U        | V       | W       | X            | Y    | Z           |      |

| 10HZ                                            | 100HZ | 1KHZ | 10KHZ | 100KHZ | 1MHz | 10M  | Jitter0  | Jitter1    | Jitter2  | Jitter3  | Jitter4 | Jitter5 | Jitter total | EVM  |             |      |

| -56                                             | -75   | -102 | -116  | -116   | -136 | -152 | -39.4135 | -48.459218 | -65.2983 | -66.4576 | -59.42  | -66.35  | 0.000130611  | 1.62 | 1.59947E-06 | 0.18 |

#### 4.2 时钟固定杂散噪声对 DAC SFDR 影响分析

参考 3.1 节对于时钟上的固定杂散，其体现在 AD/DA 的输出端的两个指标：

- 位置信息：其偏离主信号的位置和在时钟上偏离时钟信号的位置相同。

- 幅度信息：其幅度和均匀噪声一样按照公式 2-7 进行转换。

## 5 时钟噪声对 DAC 影响的一个实际案例

### 5.1 时钟随机噪声对 TX EVM 影响

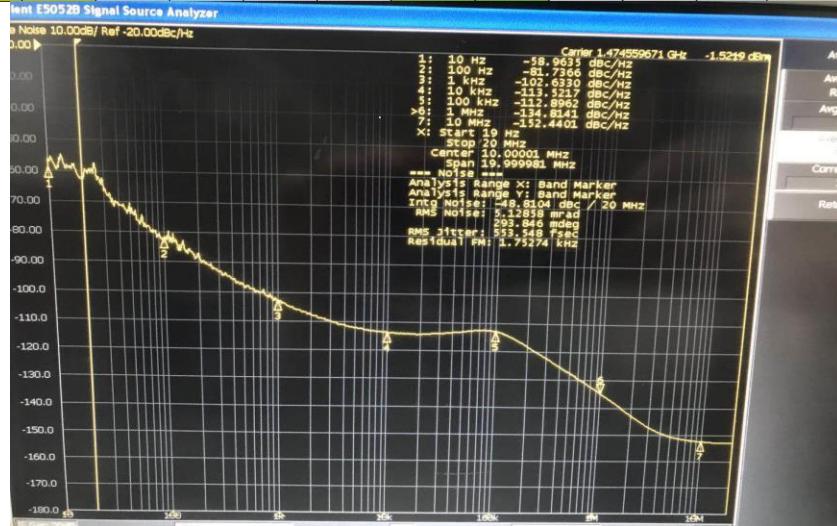

按照 4.1.2 中介绍的梯形法, 理论计算出 EVM 的是 1.14%, 实际测试中如下图所示为  $0.512^2=1.02\%$  其吻合的很好, 注意图中测试的是单边带的值, 实际计算的时候需要用双边带。

| K     | L     | M      | N      | O      | P      | Q      | R        | S          | T        | U        | V       | W       | X            | Y    |

|-------|-------|--------|--------|--------|--------|--------|----------|------------|----------|----------|---------|---------|--------------|------|

| 10HZ  | 100HZ | 1KHZ   | 10KHZ  | 100KHZ | 1MHZ   | 10M    | Jitter0  | Jitter1    | Jitter2  | Jitter3  | Jitter4 | Jitter5 | Jitter total | EVM  |

| -58.9 | -81.7 | -102.6 | -113.5 | -112.8 | -134.8 | -152.4 | -42.3451 | -55.132717 | -65.7285 | -63.5935 | -56.24  | -65.18  | 6.47269E-05  | 1.14 |

Figure 9 时钟随机噪声对 EVM 影响的实际测试

### 5.2 时钟固定杂散噪声对 DAC SFDR 影响

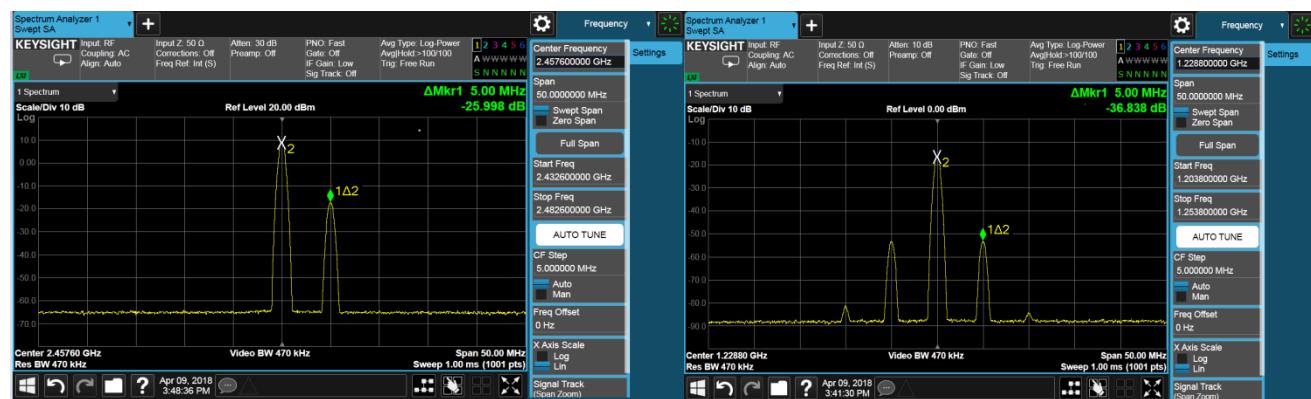

该例子是在评估提供给射频 RF DAC (RFDAC38RF8X) 的外部采样时钟 2457.6M 时候出现了较大的 spur, 对此客户表示担心。为了说服客户, 给 DAC 的时钟最终如何转换到 DAC 的输出, 同时 dBc 的如何变化理论分析和实际测试在该案例中就显得尤为重要。

前面公式 2-7 已经论述了时钟噪声对 DAC 影响理论分析, 这里直接给出在本案例中的实际测试结果。

下图中左图是测试时钟芯片的输出在 5MHz 的偏移地方有一个 26dBc 的 spur, 给 RFDAC 转换输出的射频在 1228.8MHz, 按照公式 2-7, 理论上我们会有 10dB 改善, 实际中我们测试到 36.8dBc 如右图所示, 其值和理论分析吻合的很好。

Figure 10 时钟上的 spur 到 DAC 的输出的转换的实际测

## 6 参考文献

- 【1】 “Clock (CLK) Jitter and Phase Noise Conversion” Application notes 3359 MAXIM, 2004;

- 【2】 Paul Smith “Little known characteristics of phase noise” Application notes 741 ADI , 2004;

## 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息，包括但不限于与评估模块有关的参考设计和材料（总称“TI 资源”），旨在帮助设计人员开发整合了 TI 产品的应用；如果您（个人，或如果是代表贵公司，则为贵公司）以任何方式下载、访问或使用了任何特定的 TI 资源，即表示贵方同意仅为该等目标，按照本通知的条款进行使用。

TI 所提供的 TI 资源，并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明；也未导致 TI 承担任何额外的义务或责任。TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意，在设计应用时应自行实施独立的分析、评价和判断，且应全权负责并确保应用的安全性，以及您的应用（包括应用中使用的所有 TI 产品）应符合所有适用的法律法规及其他相关要求。你就您的应用声明，您具备制订和实施下列保障措施所需的一切必要专业知识，能够（1）预见故障的危险后果，（2）监视故障及其后果，以及（3）降低可能导致危险的故障几率并采取适当措施。您同意，在使用或分发包含 TI 产品的任何应用前，您将彻底测试该等应用和该等应用所用 TI 产品的功能而设计。除特定 TI 资源的公开文档中明确列出的测试外，TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的应用时，才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何 TI 知识产权的任何其他明示或默示的许可，也未授予您 TI 或第三方的任何技术或知识产权的许可，该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用 TI 产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系“按原样”提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述，包括但不限于对准确性或完整性、产权保证、无屡发故障保证，以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索，包括但不限于因组合产品所致或与之有关的申索，也不为您辩护或赔偿，即使该等产品组合已列于 TI 资源或其他地方。对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿，不管 TI 是否获悉可能会产生上述损害赔偿，TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品（<http://www.ti.com/sc/docs/stdterms.htm>）、评估模块和样品（<http://www.ti.com/sc/docs/samptersms.htm>）的标准条款。

邮寄地址：上海市浦东新区世纪大道 1568 号中建大厦 32 楼，邮政编码：200122

Copyright © 2018 德州仪器半导体技术（上海）有限公司