# 正确使用 TPS65150 的错误检测延时功能

Alpha Han

Sales and Application/China Auto

## ABSTRACT

TPS65150 是一个常用的 LCD bias 的电源方案，能够通过单芯片产生单极性 TFT LCD 需要的全部偏置电源，包括 VS (AVDD) , VGH, VGL 和 VCOM。同时 TPS65150 具有一个非常好的可调整的错误检测功能，但是在使用中由于设计者对可调整的上电时序和错误检测功能的理解误差，造成在实际使用中可能会产生一些低概率的失效事件。

本文主要讨论 TPS65150 上电时序中上电延时和错误检测时间的定义和控制，同时也会简单涉及 LCD 上电时序异常造成的一些影响。

---

## Contents

|                                 |   |

|---------------------------------|---|

| 1. TPS65150 错误模式的定义 .....       | 2 |

| 2. TPS65150 错误检测的时间设置 .....     | 2 |

| 3. VGH (CPI) 和 VGL 延时时间设置 ..... | 3 |

| 4. TPS65150 错误模式详解 .....        | 3 |

| 5. LCD 上电时序对 TPS65150 的影响 ..... | 6 |

| 6. 设计稳健的错误检测时间 .....            | 8 |

| 7. 结论 .....                     | 8 |

| 8. 参考文献 .....                   | 8 |

## Figures

|                                          |   |

|------------------------------------------|---|

| Figure 1:EVM Cdly2=100nF 开机 .....        | 4 |

| Figure 2:EVM Cdly2=100nF 开机 1 .....      | 4 |

| Figure 3:EVM Cdly2=100nF,CPI=1x 开机 ..... | 5 |

| Figure 4:EVM 默认状态开机，Vs 加 8 Ω 负载 .....    | 5 |

| Figure 5:短时间短路 VGH 到 GND .....           | 6 |

| Figure 6:长时间短路 VGH 到 GND .....           | 6 |

| Figure 7:LCD 上下电时序要求 .....               | 7 |

| Figure 8:短时间短路 VGH 到 GND .....           | 7 |

| Figure 9:长时间短路 VGH 到 GND .....           | 8 |

## 1. TPS65150 错误模式的定义

根据 TPS65150 datasheet 的描述，错误模式主要包含两个方面，第一是没有延时的错误模式，包括 boost 升压输出过压和芯片本身过温，在这种错误下，TPS65150 会立刻进入错误模式；第二种是有延时的错误，当这种错误的持续时间超过定义的延时  $T_d(FDLY)$  后，TPS65150 才会进入错误模式，这种错误包含 boost 升压输出  $V_S$ ，正的电荷泵（charger pump）输出  $V_{GH}$  和负的电荷泵输出  $V_{GL}$  超出调整范围。

在这里，需要注意的是超出调整范围的描述，对于  $V_S$ ， $V_{GL}$ ， $V_{GH}$  这三路输出，指的是输出电压小于设计值的一个比例，下面表 1 和表 2 列出了这三路电源电压上升和下降的 PG(Power Good) 检测电压。对于电压上升和下降，TPS65150 有 2% 的电压迟滞。另外  $V_{GH}$  和  $V_{GL}$  输出电压超过设计值的情况，TPS65150 并没有做错误检测。

从错误模式的定义可以看出，延时的错误模式检测可以过滤掉一些短时间的瞬时的负载降低，同时能够检测出长时间的输出电压偏低，保护 TPS65150。

| Output   | MIN | TYP | MAX | UNIT |

|----------|-----|-----|-----|------|

| $V_S$    | 88  | 91  | 96  | %    |

| $V_{GH}$ | 89  | 92  | 95  | %    |

| $V_{GL}$ | 87  | 91  | 95  | %    |

表 1: 电压上升 PG 检测范围

| Output   | MIN | TYP | MAX | UNIT |

|----------|-----|-----|-----|------|

| $V_S$    | 86  | 89  | 94  | %    |

| $V_{GH}$ | 87  | 90  | 93  | %    |

| $V_{GL}$ | 85  | 89  | 93  | %    |

表 2: 电压下降 PG 检测范围

## 2. TPS65150 错误检测的时间设置

TPS65150 的错误检测时间  $T_d$  (FDLY) 可以通过 FDLY 引脚上连接一个电容  $C$  (FDLY) 到电源输入  $V_{in}$  来实现，当然可以把 FDLY 引脚直接连接到  $V_{in}$ ，关闭有延时的错误检测功能。这个时候，TPS65150 不会检测  $V_S$ ， $V_{GH}$  和  $V_{GL}$  的低于 PG 的电压状态。 $T_d$  (FDLY) 可以通过下面的公式来计算。

$$T_d(FDLY) = R(FDLY) C(FDLY)$$

- $R(FDLY)=450Kohm$  (内部连接到 FDLY 引脚的阻抗)

- $C(FDLY)$  是外部连接到 FDLY 引脚的电容

需要注意的是  $R(FDLY)$  是有一个误差范围的，而且这个误差范围相对还比较大，参考下面的表 3，这一点在后面会有用到。

| PARAMETER | MIN | TYP | MAX | UNIT      |

|-----------|-----|-----|-----|-----------|

| $R(FDLY)$ | 250 | 450 | 650 | $k\Omega$ |

表 3:  $R(FDLY)$  电阻的范围

### 3. VGH (CPI) 和 VGL 延时时间设置

TPS65150 的 VGH 和 VGL 的延时  $T_d(DLY1)$  和  $T_d(DLY2)$  可以通过 DLY1 和 DLY2 引脚上连接一个电容  $C(DLY1)$  和  $C(DLY2)$  到地来实现，具体的延时时间可以通过下面的公式来计算。从 datasheet 来看， $V_{ref}$  的精度是比较高的，在实际的计算中基本可以忽略。但是需要注意的是  $I(DLY1)$  和  $I(DLY2)$  是有一个误差范围的，而且这个误差范围相对还比较大，参考下面的表 4，这一点在后面会有用到。

$$T_d(DLY1) = \frac{C(DLY1)V_{ref}}{I(DLY1)} \quad T_d(DLY2) = \frac{C(DLY2)V_{ref}}{I(DLY2)}$$

- $V_{ref}=1.213V$ (内部参考电压), 1.205V(最小), 1.219V(最大)

- $I(DLY1)=5\mu A$ (DLY1 引脚输出电流)

- $I(DLY2)=5\mu A$ (DLY2 引脚输出电流)

| PARAMETER | MIN | TYP | MAX | UNIT    |

|-----------|-----|-----|-----|---------|

| $I(DLY1)$ | 3   | 5   | 7   | $\mu A$ |

| $I(DLY2)$ | 3   | 5   | 7   | $\mu A$ |

表 4:  $I(DLY1)$ ,  $I(DLY2)$  电流的范围

还需要注意的是，DLY2 实际上控制的是正的电荷泵 CPI 的启动时间，而不是 VGH 的启动时间，VGH 还受 CTRL 引脚控制。当 CTRL 开机直接拉高的情况下，VGH 在 CPI 输出达到设置值之后会被使能。

TPS65150 的错误检测功能实际上也是检测 CPI 的电压而不是 VGH 的电压。

### 4. TPS65150 错误模式详解

TPS65150 可调整时间的错误检测模式在开机的时候就使能了，也就是说当 TPS65150 检测到输入电压大于 UVLO 的电压之后 ( $Vi>VIT+$ )，TPS65150 可调整时间的错误检测功能就使能了。 $Vi$  上升时  $VIT+$  典型电压是 1.7V，最大电压是 1.9V。在开机过程中当错误检测延时时间到了设置值之后，如果输出的三路电源没有同时达到 PG 的条件，TPS65150 就会进入错误模式。

下面的波形是在 TPS65150 的 EVM 上测试的，EVM 默认配置如下： $Vi=5V$ ,  $Vs=9.9V$ ,  $VGH=22.9V$ ,  $VGL=-6.2V$ ,  $Td(FDLY)=45mS(typ)$ ,  $Td(DLY1)=2.4mS (typ)$  和  $Td(DLY2)=2.4mS(typ)$ ,  $CPI=2x$  (两倍的 Charger pump),  $CTRL=H$ , No load, 不一样的测试条件标示在图的下方。

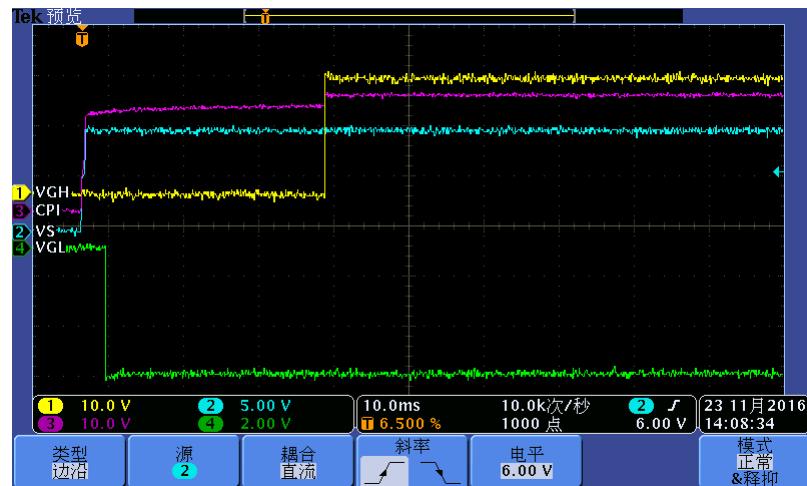

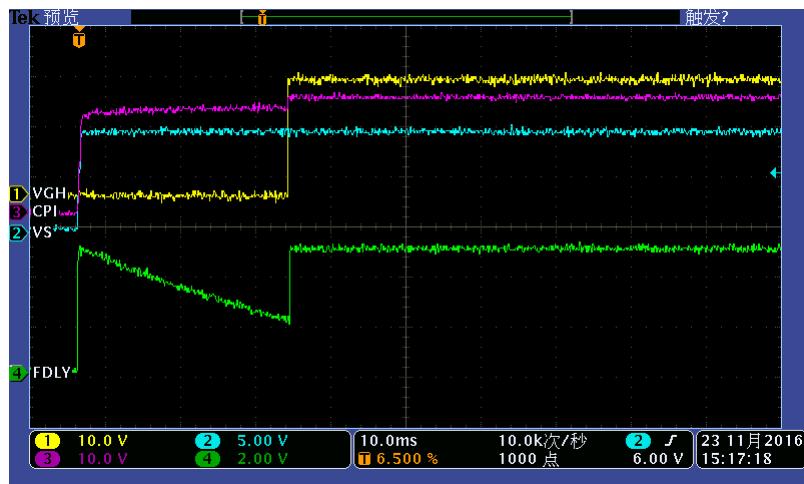

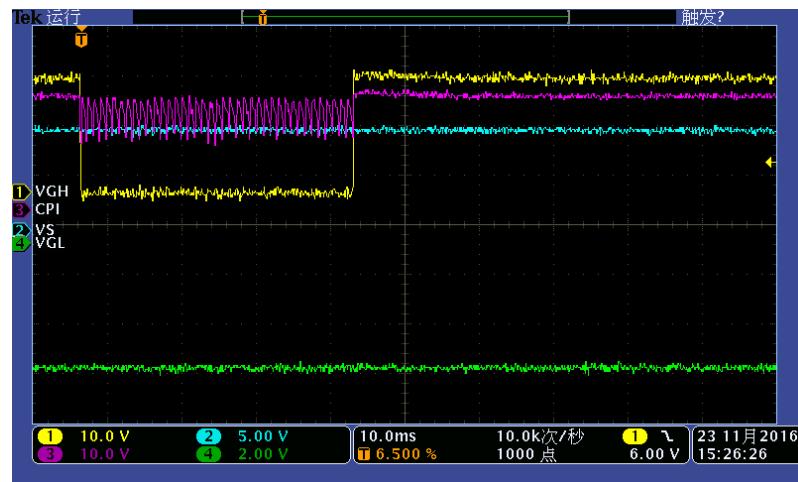

Figure1 是 TPS65150 修改 Cdly2=100nF 的开机过程, 从 Figure1 可以看到 VGL 大概在 Vs 起来后 2.4mS 打开, VGH 在 VGL 后 29mS 打开。从这里看看到, VGH 的打开延时时间和典型的 24mS 还是有蛮大区别的, 因为 TPS65150 的 DLY2 的电流有一个比较大的误差范围, 计算下来,  $T_d(DLY2)=24mS(typ)$ ,  $T_d(DLY2)=17mS(min)$ ,  $T_d(DLY2)=40mS(max)$ 。Figure2 是在 Figure1 的基础上同时测试了 FDLY 引脚的波形, 从 Figure2 上可以明显看出在开机过程中, FDLY 引脚通过内部  $450k\Omega$  电阻放电的过程, 这个过程从 TPS65150 上电之后就开始了。同时也可以看到当错误条件都消失后, FDLY 引脚电压快速恢复默认状态。

Figure 1:EVM Cdly2=100nF 开机

CH1:VGH,CH2:VS,CH3:CPI,CH4:VGL

Figure 2:EVM Cdly2=100nF 开机 1

CH1:VGH,CH2:VS,CH3:CPI,CH4:FDLY

Figure3 是把 EVM 的正电荷泵设置在 1 倍的模式, 这样 CPI 就达不到设置的 24V, 所以会进入错误模式。从这张图里可以看到从  $VI>VIT+$ 大概  $49mS$  后, TPS65150 进入错误模式, 同时还可以看到因为 CPI 的电压一直没有能够输出到配置值, VGH 在进入错误模式之前, 一直维持为 0, 没有打开。进入错误模式后, VGH 上有一个脉冲, 这个应该是 TPS65150 关断过程中, VGH 被打开了一下所致。

Figure 3:EVM Cdly2=100nF,CPI=1x 开机

CH2:VS,CH3:VGH,CH4:VGL

为了更加清楚的显示 VGH, VGL 的延时影响, 我们在 Vs 输出上加 8ohm 的负载, 减慢 Vs 的上升, 我们得到 Figure4, 从 Figure4 上可以明显的看到, VGL 的打开时间相对 Figure1 有明显的延时, 因为 VGL 的延时是从 Vs 输出满足 PG 的条件开始的。

Figure 4:EVM 默认状态开机, Vs 加 8 Ω 负载

CH1:VGH,CH2:VS,CH3:CPI,CH4:VGL

对于运行过程中的可调整时间的错误检测模式, 相对比较好理解。如果错误持续的时间短于错误延时的时间, TPS65150 能够恢复到正常的状态, 如果错误持续的时间长于错误延时的时间, TPS65150 会进入错误锁定状态, 这时候就要关断 TPS65150 的输入电压, 再重新上电, 才能清除错误状态。

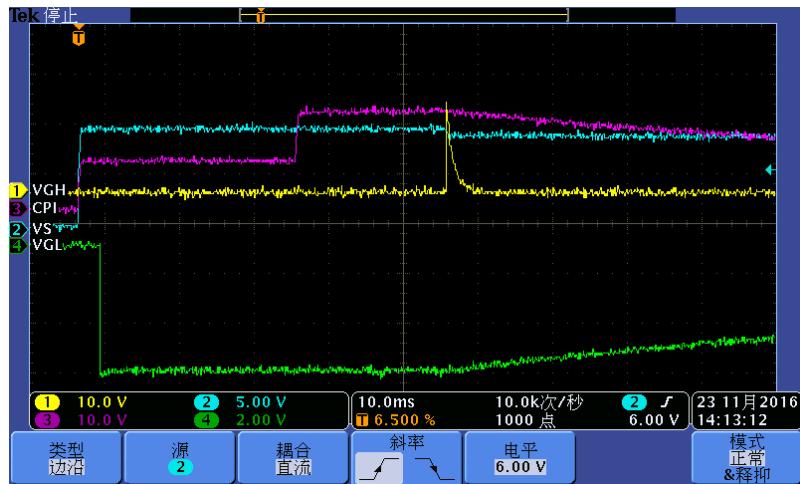

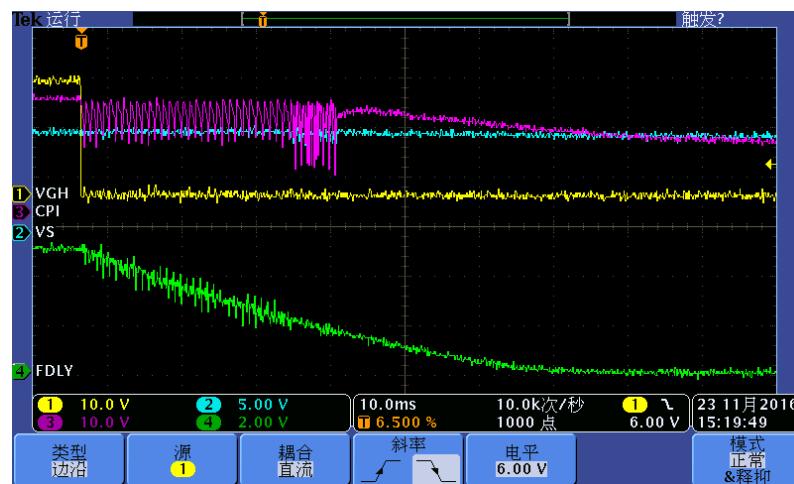

Figure5 是把 VGH 短时间短路到地的波形, 可以看到 TPS65150 能够正常恢复。

Figure 5: 短时间短路 VGH 到 GND

CH1: VGH, CH2: VS, CH3: CPI, CH4: VGL

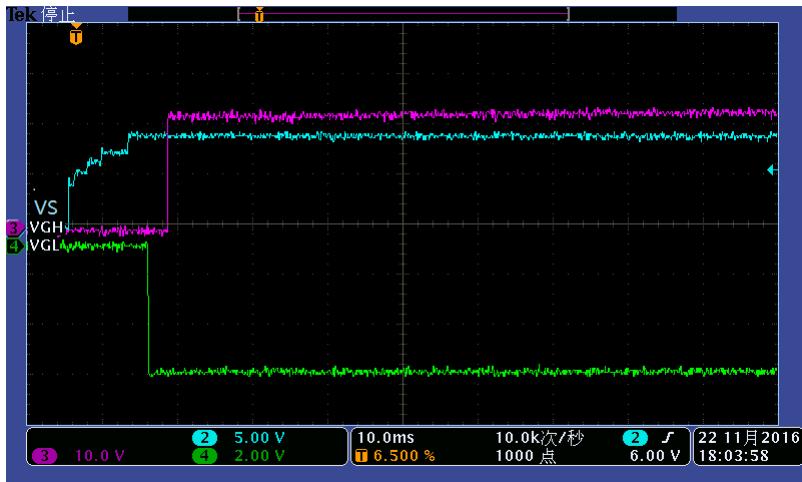

Figure 6 是把 VGH 长时间短路到地的波形，可以看到 TPS65150 不能正常恢复，进入了错误状态。

Figure 6: 长时间短路 VGH 到 GND

CH1: VGH, CH2: VS, CH3: CPI, CH4: VGL

## 5. LCD 上电时序对 TPS65150 的影响

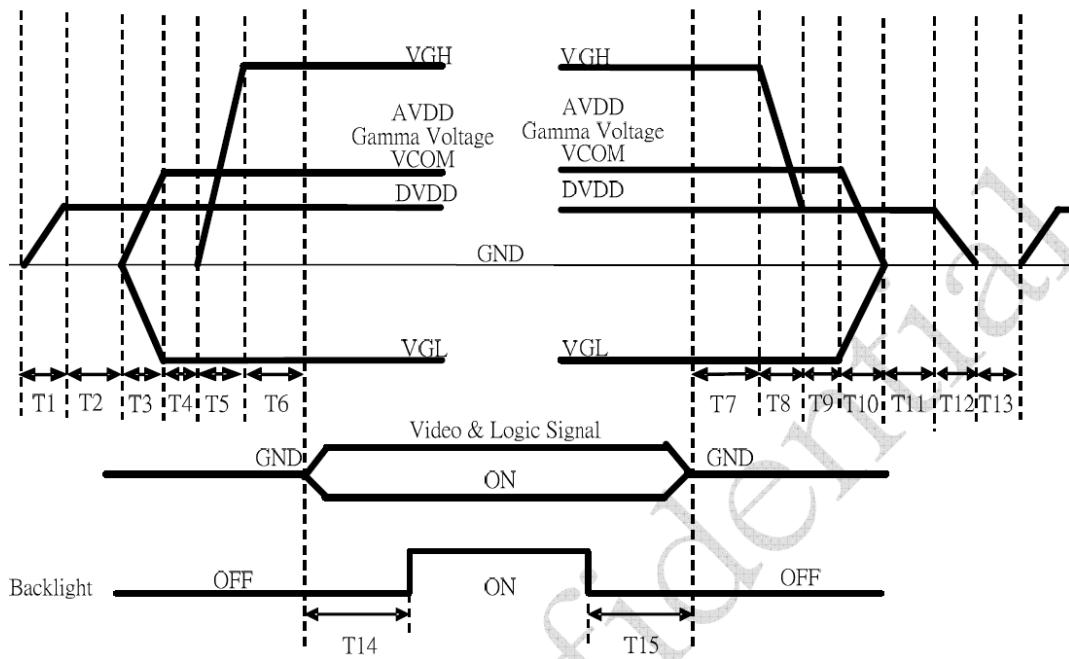

在实际的项目设计过程中，我们发现，保持正确的 LCD 上电时序对于正确使用 TPS65150 也是一个很重要的部分。下 Figure7 是现在市面上一个常见的 LCD 模块的时序要求，在实际的 TPS65150 的调试过程中，我们发现如果 DVDD 的打开时间比 AVDD(Vs)晚，在上电过程中，这个 LCD 模块 AVDD 上的电流消耗会比 DVDD 正常先上电时高出好几倍，造成 TPS65150 的 VS 上升缓慢，VGL 和 VGH 都会相应的延时打开。

Power On : DVDD→AVDD/VGL→VGH→Video & Logic Signal→Backlight

Power Off : Backlight→Video & Logic Signal→VGH→AVDD/VGL→DVDD

Figure 7:LCD 上下电时序要求

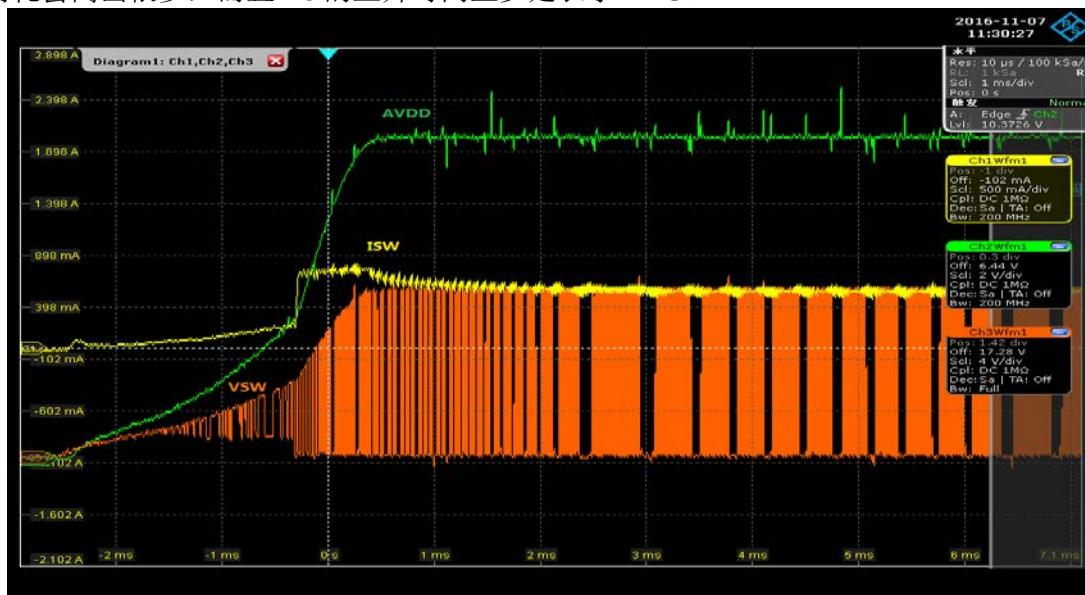

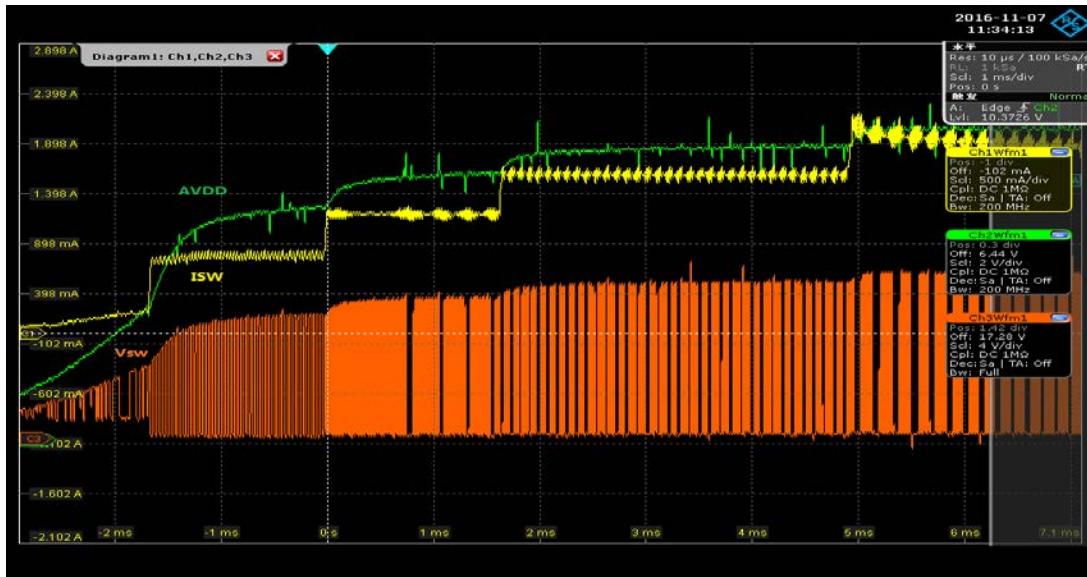

下面 Figure8 和 Figure9 是在相同的 LCD 模块和相同的 TPS65150 的设计情况下, 修改 DVDD 的上电时序测试到的波形。从这两张图, 可以明显的看到, 当 LCD 模块异常上电的时候, AVDD (VS) 上的电流消耗会高出很多, 而且 Vs 的上升时间至少延长了 7mS。

Figure 8:短时间短路 VGH 到 GND

Figure 9:长时间短路 VGH 到 GND

## 6. 设计稳健的错误检测时间

从上文的讨论，我们可以看到 TPS65150 的错误检测功能在开机的时候就存在，然而错误检测延时的设计以及 VGH, VGL 使能的延时设计有很大的误差，另外根据负载大小的不一样，也会影响 VS, VGH, VGL 的使能时间，所以需要小心设计 TPS65150 的延时功能。

首先可以根据 LCD 要求的时序，设计 VGL 和 VGH 的延时时间，这个时候需要充分考虑 I(DLY1)和 I(DLY2)的误差范围，其次需要考虑 boost 的上升时间。经验上来说可以把错误检测的最长时间  $Td(FDLY)(MIN)$  设置得比  $VGH+VGL$  的最大延时( $Td(DLY1)+ Td(DLY2)$ ) ( $MAX$ )大 5 倍，同时  $Td(FDLY)$  ( $MIN$ )比( $Td(DLY1)+ Td(DLY2)$ ) ( $MAX$ )长 10ms，也就是建议同时满足下面两个条件：

$$Td(FDLY)(MIN) \geq ((Td(DLY1)+ Td(DLY2)) (MAX) * 5$$

$$Td(FDLY)(MIN) \geq ((Td(DLY1)+ Td(DLY2)) (MAX) + 10ms$$

## 7. 结论

TPS65150 是一个简单易用的 LCD 偏置电压生成方案，同时它具有非常好的错误检测延时功能。因为 TPS65150 本身的设计和参数误差，以及系统不同的负载需求，设计一个稳健的错误检测时间就显得比较重要。通过选择恰当的 VGH, VGL 使能延时和错误检测延时电容，我们可以设计出一个稳健的 TPS65150 错误检测功能。

## 8. 参考文献

1. TPS65150 datasheet (SLVS576B) <http://www.ti.com/litv/pdf/slvs576b>

2. TPS65150 EVM Guide(SLVUAG5A) <http://www.ti.com/docs/toolsw/folders/print/tps65150evm-697.html>

## 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息，包括但不限于与评估模块有关的参考设计和材料（总称“TI 资源”），旨在帮助设计人员开发整合了 TI 产品的应用；如果您（个人，或如果是代表贵公司，则为贵公司）以任何方式下载、访问或使用了任何特定的 TI 资源，即表示贵方同意仅为该等目标，按照本通知的条款进行使用。

TI 所提供的 TI 资源，并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明；也未导致 TI 承担任何额外的义务或责任。TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意，在设计应用时应自行实施独立的分析、评价和判断，且应全权负责并确保应用的安全性，以及您的应用（包括应用中使用的所有 TI 产品）应符合所有适用的法律法规及其他相关要求。你就您的应用声明，您具备制订和实施下列保障措施所需的一切必要专业知识，能够（1）预见故障的危险后果，（2）监视故障及其后果，以及（3）降低可能导致危险的故障几率并采取适当措施。您同意，在使用或分发包含 TI 产品的任何应用前，您将彻底测试该等应用和该等应用所用 TI 产品的功能。除特定 TI 资源的公开文档中明确列出的测试外，TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的应用时，才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何 TI 知识产权的任何其他明示或默示的许可，也未授予您 TI 或第三方的任何技术或知识产权的许可，该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用 TI 产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系“按原样”提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述，包括但不限于对准确性或完整性、产权保证、无屡发故障保证，以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索，包括但不限于因组合产品所致或与之有关的申索，也不为您辩护或赔偿，即使该等产品组合已列于 TI 资源或其他地方。对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿，不管 TI 是否获悉可能会产生上述损害赔偿，TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (<http://www.ti.com/sc/docs/stdterms.htm>)、评估模块和样品 (<http://www.ti.com/sc/docs/samptersms.htm>) 的标准条款。

邮寄地址：上海市浦东新区世纪大道 1568 号中建大厦 32 楼，邮政编码：200122

Copyright © 2017 德州仪器半导体技术（上海）有限公司