# LMK0480X 功能特点及应用

---

Anjin Du

China Telecom Application Team

## 摘要

LMK0480X 是目前被业界广泛采用的时钟去抖芯片。本文主要介绍了 LMK0480X 系列时钟的工作原理和功能特点，重点讨论了这些功能在实际应用中需要注意的设计细节。

## 目录

|     |                          |    |

|-----|--------------------------|----|

| 1   | LMK0480X 系列产品的主要特点 ..... | 2  |

| 2   | 时钟的去抖和分发 .....           | 3  |

| 3   | Holdover 功能 .....        | 6  |

| 4   | 数字模拟延时 .....             | 9  |

| 4.1 | 模拟延时： .....              | 9  |

| 4.2 | 数字延时： .....              | 10 |

| 5   | 通道隔离 .....               | 11 |

| 6   | 器件的供电 .....              | 13 |

| 7   | 结论 .....                 | 14 |

| 8   | 参考资料 .....               | 14 |

## 图

|                              |   |

|------------------------------|---|

| Figure 1 LMK0480X 内部框图 ..... | 3 |

|------------------------------|---|

|                                     |    |

|-------------------------------------|----|

| Figure 2 锁相环框图 .....                | 4  |

| Figure 3 LMK0480X 各阶段的相噪框图 .....    | 6  |

| Figure 4 Holdover 内部框图 .....        | 6  |

| Figure 5 Exit holdover 状态的示意图 ..... | 8  |

| Figure 6 上电时参考时钟和 holdover 关系 ..... | 9  |

| Figure 7 模式延时框图 .....               | 10 |

| Figure 8 数字延时框图 .....               | 10 |

| Figure 9 SYNC 信号的功能示意 .....         | 10 |

| Figure 10 SYNC 信号的内部框图 .....        | 11 |

| Figure 11 LMK0480X 的管脚分配 .....      | 12 |

| Figure 12 LMK0480X 的供电分配 .....      | 13 |

## 表

|                                 |    |

|---------------------------------|----|

| Table 1 LMK0480X 频率覆盖范围 .....   | 3  |

| Table 2 锁相环各个部分的传递函数 .....      | 5  |

| Table 3 LMK0480X 各个通道间的隔离 ..... | 12 |

## 1 LMK0480X 系列产品的主要特点

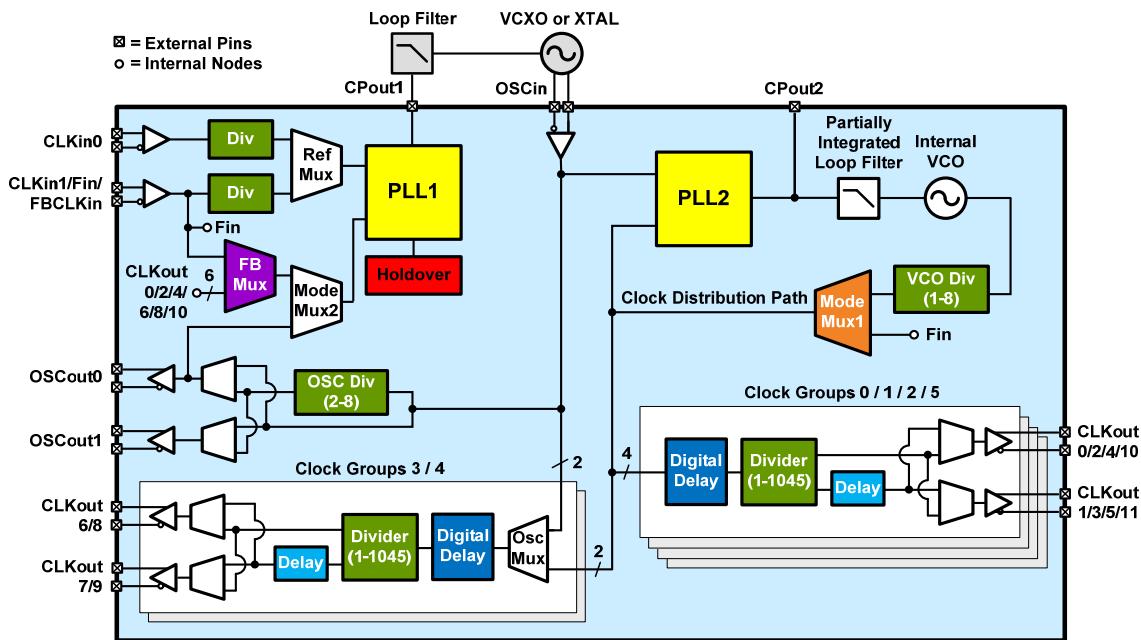

LMK0480X 系列产品是德州仪器 2011 年推出的时钟去抖产品，广泛应用于无线基站、有线网络、广播设备当中。LMK0480X 产品采用了双锁相环级联的创新架构，在实现系统参考时钟去抖功能的同时，生成和分发系统各功能模块所需的时钟。其它主要的功能还包括：

- 两路参考输入，支持自动切换

- 总共七组独立 divider，第一级锁相环有两对输出（一组 divider），第二级锁相环支持 12 对时钟输出（6 组 divider）

- Holdover 功能，保证在参考源切换时输出时钟稳定

- Zero Delay 功能，保证输出时钟和输入参考的相位对齐

- 模拟和数字延时，确保输出时钟相位的精确调整

下面是 LMK0480X 的内部框图：

Figure 1 LMK0480X 内部框图

根据内部集成 VCO 的频率覆盖范围不同，LMK0480X 系列产品分为的四款产品，如下表：

| Device   | VCO Frequency    |

|----------|------------------|

| LMK04803 | 1840 to 2030 MHz |

| LMK04805 | 2148 to 2370 MHz |

| LMK04806 | 2370 to 2600 MHz |

| LMK04808 | 2750 to 3072 MHz |

Table 1 LMK0480X 频率覆盖范围

下面章节中我们将着重介绍 LMK0480X 的主要功能以及在实际应用中遇到的问题。

## 2 时钟的去抖和分发

在通信系统中，为了保证传输的准确性，一般都要求整个系统的时钟要同步到相同的时钟源。当

这个时钟源通过光纤、背板或者接插件传输到各个板卡时，或多或少都会引入一些噪声，造成时钟源抖动的增加。与此同时，随着板卡处理信号带宽的增加，系统对于时钟的抖动要求越来越高，远端提供的时钟参考源不能直接用于系统，必须首先提高参考时钟源的性能，即所谓的时钟去抖。利用锁相环实现时钟去抖是一种经济而有效的方法。

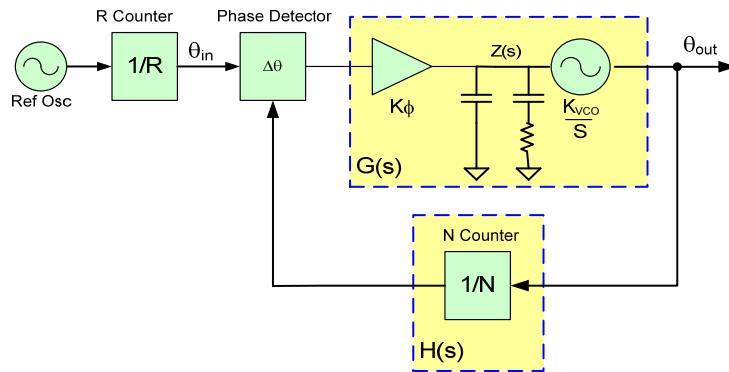

回顾一下锁相环的原理，得到锁相环各个组成部分的传递函数，如 figure2 所示。可以看出，相对于环路带宽，参考频率的噪声传递函数呈现低通特性，而对于 VCO/VCXO，其噪声传递函数则是高通特性。利用锁相环去抖，就是设计一个环路带宽比较窄的滤波器（几十 Hz），尽量多的滤除来自参考频率的噪声，降低参考频率噪声对后级的影响；同时，需要注意到环路带宽之外的噪声很大程度上取决于 VCO/VCXO 的性能，所以选择什么样性能的 VCO/VCXO，也决定了最终时钟性能的好坏，一般在时钟去抖的部分都会选择性能比较好的 VCXO。命名这个锁相环为 PLL1。

Figure 2 锁相环框图

$$\frac{\theta_{out}}{\theta_{in}} = \frac{G(s)}{1 + [G(s) \cdot H(s)]} = \frac{K_\phi \cdot Z(s) \cdot \frac{K_{VCO}}{s}}{1 + \left[ K_\phi \cdot Z(s) \cdot \frac{K_{VCO}}{s} \cdot \frac{1}{N} \right]}$$

| Source               | Transfer Function                                                               | Low Freq. Approx.              | High Freq. Approx.     |

|----------------------|---------------------------------------------------------------------------------|--------------------------------|------------------------|

| VCO                  | $\frac{1}{1 + \left[ G(s) \cdot \frac{1}{N} \right]}$                           | $1/G(s)$ ,<br>$ 1/G(s) ^2$     | 1                      |

| Reference Oscillator | $\frac{1}{R} \cdot \frac{G(s)}{1 + \left[ G(s) \cdot \frac{1}{N} \right]}$      | $N/R$ ,<br>$(N/R)^2$           | $G(s)$ ,<br>$ G(s) ^2$ |

| R counter            | $\frac{G(s)}{1 + \left[ G(s) \cdot \frac{1}{N} \right]}$                        | N,<br>$N^2$                    | $G(s)$ ,<br>$ G(s) ^2$ |

| N counter            | $\frac{G(s)}{1 + \left[ G(s) \cdot \frac{1}{N} \right]}$                        | N,<br>$N^2$                    | $G(s)$ ,<br>$ G(s) ^2$ |

| Phase Detector       | $\frac{1}{K_\phi} \cdot \frac{G(s)}{1 + \left[ G(s) \cdot \frac{1}{N} \right]}$ | $N/K_\phi$ ,<br>$(N/K_\phi)^2$ | $G(s)$ ,<br>$ G(s) ^2$ |

**Table 2 锁相环各个部分的传递函数**

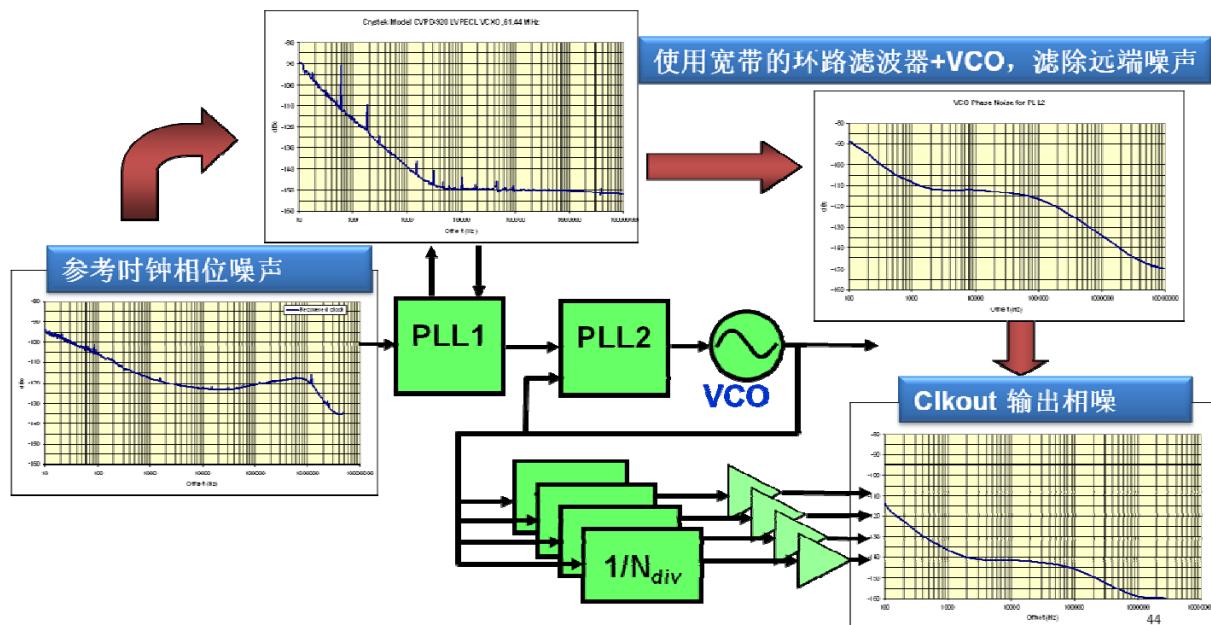

目前的板卡越来越复杂，不同的功能模块需要不同的时钟，例如在目前的无线 RRU 中，ADC 需要 245.76MHz，DAC 需要 983.04MHz，SERDES 需要 153.6MHz，本振参考需要 61.44MHz。这就带来另外一个需要设计者考虑的问题，怎样生成这些多种类的时钟？首先这么多种类的时钟不可能由同一个 VCXO 通过分频得到，因为频率较高的 VCXO 成本较高，同时高频 VCXO 抗振动、撞击性能不好。一个变通的方法就是用一个射频 VCO 去跟踪锁定低频 VCXO，由射频 VCO 分频得到系统需要的各种时钟。在这级 PLL 中，环路带宽应该适当放宽到几百 KHz，因为 VCXO 在几百 KHz 以内的近端噪声比 VCO 要好，VCO 在几 MHz 处的性能比 VCXO 好。把环路带宽设计到几百 KHz，可以得到最佳的输出抖动性能。命名这个锁相环为 PLL2。

当 PLL1 和 PLL2 两级锁相环级联时，就同时解决了时钟的去抖和生成以及分发。下图就是在各个不同阶段时钟相噪特性。不难发现，经过 LMK0480X 时钟器件的处理，输出时钟的抖动特性得到了很大提升。

使用窄带的环路滤波器和VCXO，滤除参考的近端相噪

Figure 3 LMK0480X 各阶段的相噪框图

### 3 Holdover 功能

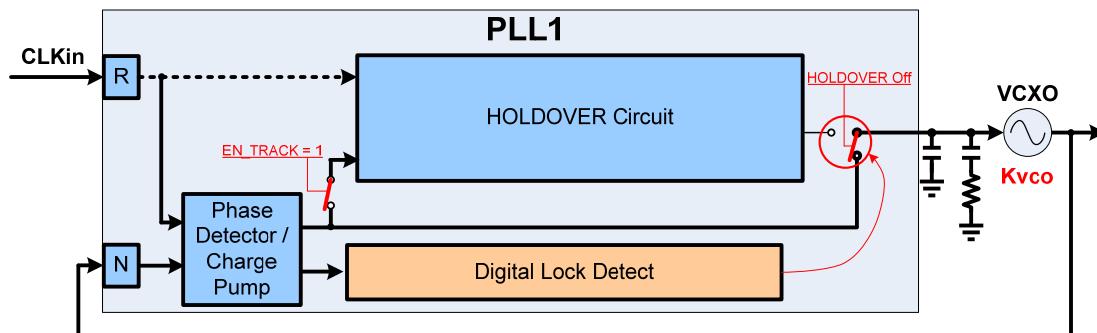

在实际的应用当中，给时钟芯片提供的参考时钟可能由于各种原因出现偏移或者丢失，从而导致时钟芯片失锁，使得输出的时钟误差比较大，进而导致整个板卡误码甚至系统的紊乱。为了避免这个问题的出现，系统要求时钟芯片即便在参考丢失或者出现比较大的偏移时，仍然能够输出一个比较稳定的时钟。LMK0480X 系列芯片 holdover 功能可以实现在参考时钟源切换时输出的时钟比较稳定，下面的框图介绍了 holdover 的主要原理。

Figure 4 Holdover 内部框图

当锁相环锁定的时候，锁相环的鉴相器输出电压控制 VCXO 的振荡频率；同时 holdover 电路会跟踪记录鉴相器输出的压控电压，同时实时更新 holdover 电路的输出，使其等于鉴相器输出的压控电压；当 CLKin 参考丢失时，锁相环的锁定指示检测到锁相环失锁，VCXO 的压控电压会切换到 holdover 电路的输出电压，同时 holdover 电路不再跟踪鉴相器的压控电压，从而实现了输出频率的稳定；当 CLKin 恢复时，芯片不会立即切换到鉴相器输出的电压，而是等到 VCXO N 分频之后输出的频率 (Nout) 和 CLKin R 分频之后的频率 (Rout) 相位误差连续多次小于特定的误差范围，才会退出 holdover 并切换到鉴相器的输出，从而保证芯片退出 holdover 并重新进入跟踪、锁定过程也不会产生时钟的跳变。

进入 holdover 状态以后，可以通过下面公式计算 LMK0480X 的 holdover 频率误差，其中 Kv 是 VCXO 的压控灵敏度，Fosc 是 VCXO 频率，0.0064V 是 LMK0480X 器件在 holdover 下的输出电压误差。

$$F_{\text{error\_ppm}} = 1e6 * 0.0064 (\text{V}) * Kv (\text{Hz/V}) / F_{\text{osc}} (\text{ppm})$$

在 LMK0480X 的 holdover 电路设计中，为保证 holdover 电路的准确工作，同时也为了避免器件频繁地进入、退出 holdover 工作状态，LMK0480X 内部有一个 holdover 状态机，在器件处于失锁状态时（如刚上电），通过 EN\_Track 可以打开或关断 holdover 使能功能，在 holdover 使能电路工作时，进一步可通过 PLL1\_DLD\_CNT 和 HOLDOVER\_DLD\_CNT 两个参数约束进入、退出 holdover 的条件。

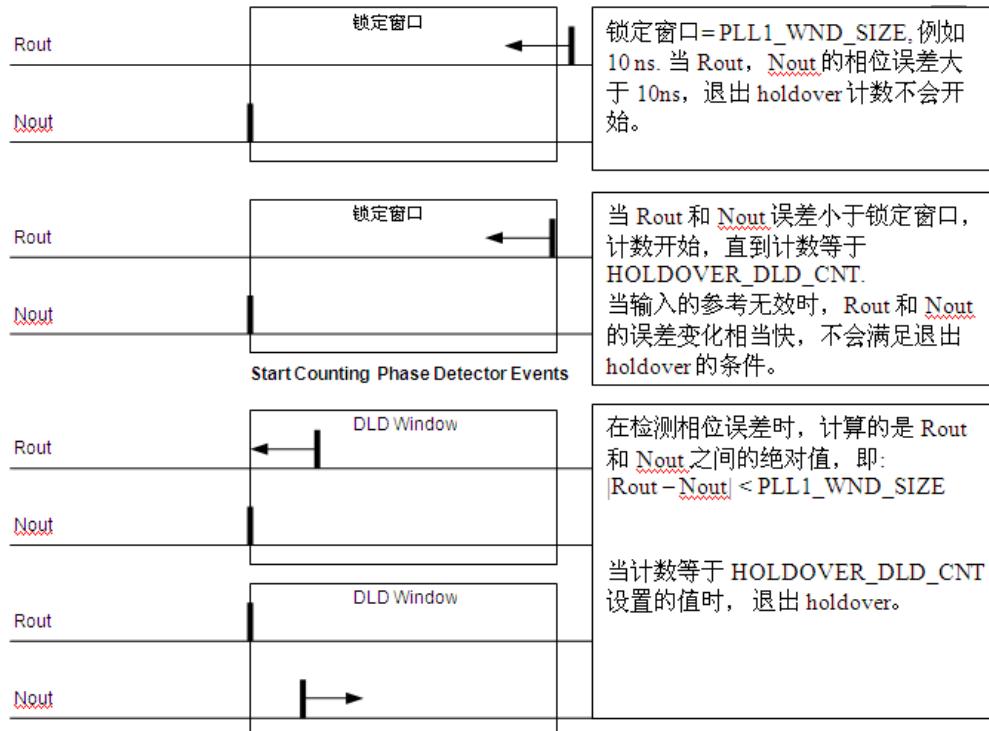

PLL1\_DLD\_CNT 是判决进入锁定时，Rout 和 Nout 的相位误差必须连续 PLL1\_DLD\_CNT 个周期小于一定的门限值；HOLDOVER\_DLD\_CNT 是判决退出 holdover 时，Rout 和 Nout 的相位误差必须连续 HOLDOVER\_DLD\_CNT 个周期小于一定的门限值。下图描述了退出 holdover 过程，PLL 进入锁定的过程类似。

Figure 5 Exit holdover 状态的示意图

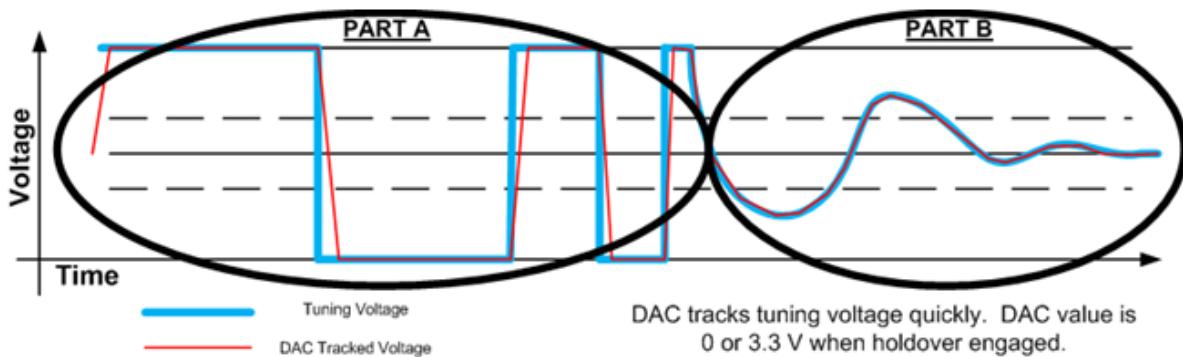

当 LMK0480X 开始工作时, 本地时钟 VCXO 跟踪并尝试锁定 CLKin 输入信号, 同时 holdover 电路也开始跟踪 VCXO 的压控电压, 若 holdover\_DLD\_CNT 和 PLL1\_DLD\_CNT 值设置比较小, 此时器件很容易进入锁定状态 ( 伪锁定状态 ), 但通常 CLKin 或 VCXO 在刚开始工作时并不稳定, CLKin 的输入并不在 VCXO 的频率调整范围, 因此器件重新失锁并进入 holdover 状态, 并且此时 holdover 输出电压可能为 3.3V 或 0V ,

在这之后, CLKin 的频率渐趋稳定, CLKin 的频率和 VCXO 的频率不能再满足退出 holdover 的条件, 即出现器件无法退出 holdover, 也无法锁定; 压控电压被拉到 3.3V 或者 0V。如下图 PartA 部分所示。因此, 在 holdover 功能电路设计中, 通常适当的增加 PLL1\_DLD\_CNT 和 HOLDOVER\_DLD\_CNT 的值, 使得退出和锁定的判决条件更为苛刻, 只有当 CLKin 稳定时, 才会退出 holdover, 进入锁定。如下图 PartB 部分所示。

Figure 6 上电时参考时钟和 holdover 关系

## 4 数字模拟延时

越来越多的应用，尤其是系统中包含多颗 ADC/DAC，要求这些器件的时钟需要同步；同时由于 PCB 板面积比较大，使得时钟器件到各个器件的传输线走线的长度不尽相同，造成了这些器件的采样时钟不同步。为了解决这些问题，LMK0480X 提供了数字延时和模拟延时，能够精确的控制这些走线的相位；同时器件还提供了 zero-delay 这个功能，可以确保器件输出和参考输入之间的相位同步，满足一些特定场合的需要。

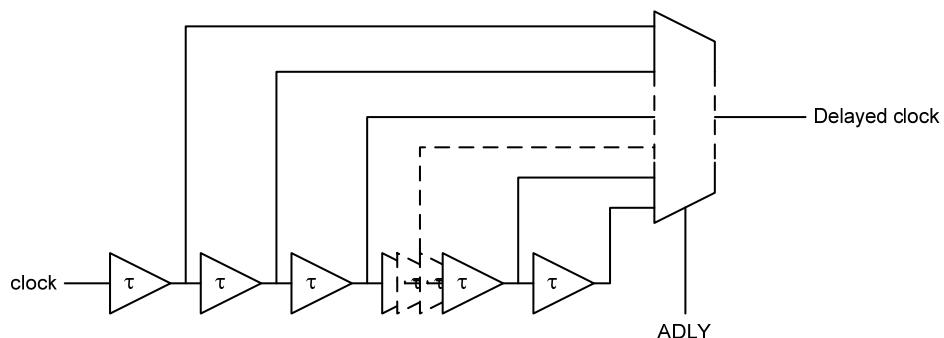

### 4.1 模拟延时

模拟延时就是在 divider 和输出 buffer 之间集成了一些固定延时电路，通过开关选择信号经过的路径来实现不同的模拟延时。模拟延时的步进为 25ps，24 步，共计 575ps 的延时范围。同时在应用中需要注意，每个通道模拟延时的开启会增加器件 5mA 的电流，同时输出相噪在偏离 10MHz 处会有大概 10dB 的恶化。下面是模拟延时实现的原理框图。

Figure 7 模式延时框图

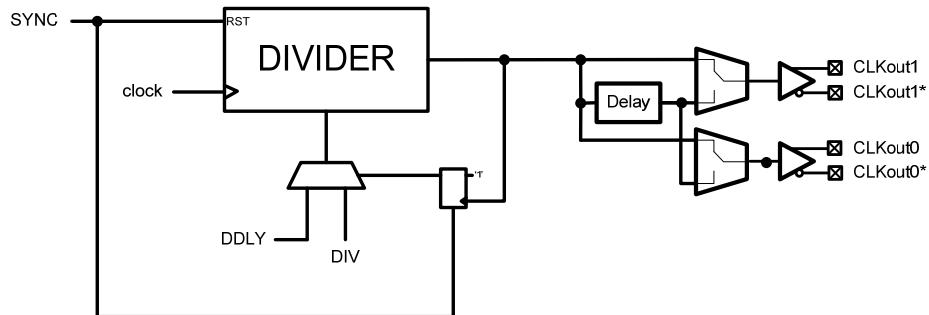

## 4.2 数字延时

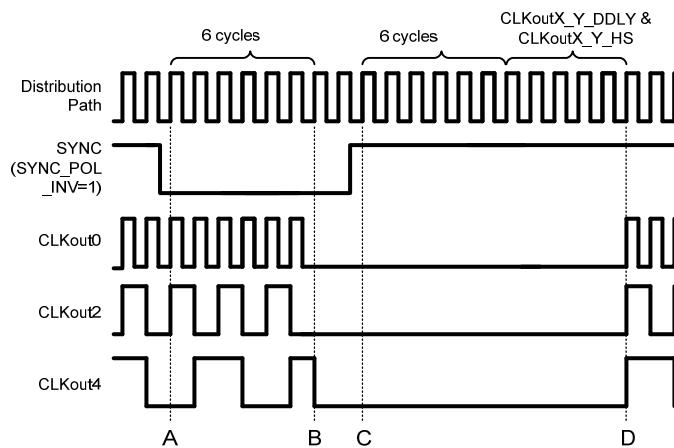

数字延时相对模拟延时要复杂一些，主要是通过 SYNC 信号的上升沿和下降沿来同步所有时钟或做相应的延时调整，如下图：

Figure 8 数字延时框图

当芯片检测到 SYNC 下降沿时，触发一次相位调整，六个 VCO 周期以后，所有时钟停止输出；当 SYNC 出现上升沿并且六个 VCO 周期之后，所有的输出无论分频器设置为多少，同时输出各自时钟的上升沿，实现所有时钟的同步。如果各路时钟的数字延时值 (DDLY) 不同，则各自延时对应的延时周期，然后输出时钟，实现数字延时。

Figure 9 SYNC 信号的功能示意

从上图中可以看到，在数字延时过程中，对应的输出会中断一定的 VCO 周期来实现时钟的同步，在实际应用当中这种中断可能会影响电路性能。为此，LMK0480X 在每路输出当中，都设有 NO\_SYNC\_CLKout\_X\_Y bit，当此寄存器位使能时，对应的输出不响应 SYNC 信号，输出时钟不中断，也不做相位调整。另外一个比较实际的应用场景是，系统需要调整两个时钟的相对延时，比方调

整 CLKout2 相对与 CLKout1 的延时，同时又希望 CLKout1 的输出不中断。在这种情况下，首先应当使能 NO\_SYNC\_CLKout\_0\_1 bit，使 CLKout1 不响应 SYNC，同时选择使能 SYNC\_QUAL，选择 SYNC\_QUAL 时钟为 CLKout1，即选择 CLKout1 作为相位调整的基准时钟，最后设置 CLKout2 相对 CLKout1 的相对时延。这些设置完成之后，就可以通过 SYNC 实现 CLKout2 相对于 CLKout1 的时延调整，同时又不影响 CLKout1 的输出。

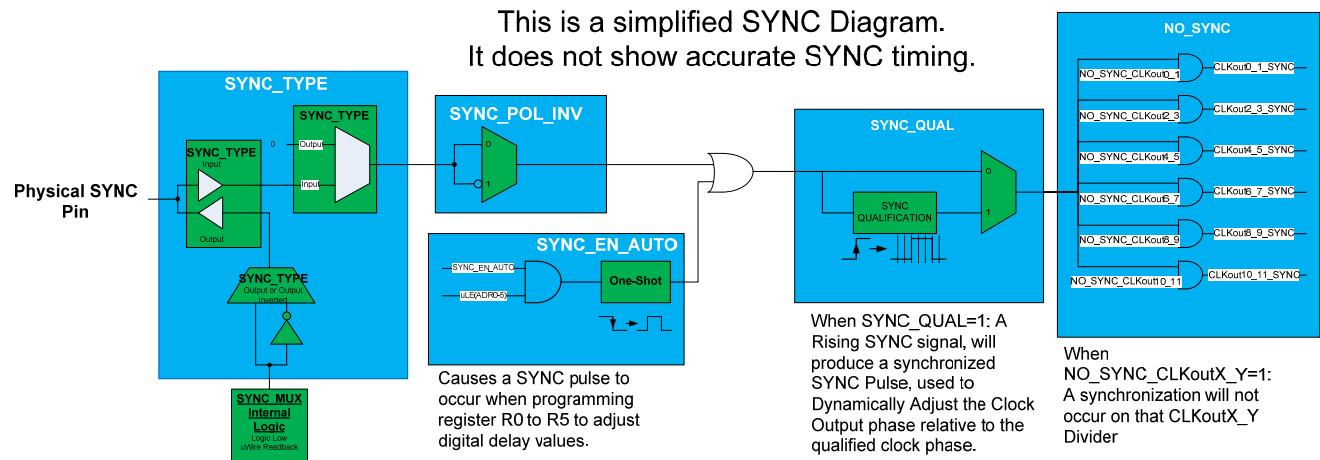

这里多次提到了 SYNC 信号，SYNC 信号是 LMK0480X 产品实现时延调整重要手段。以下是 SYNC 信号产生的简明框图，产生 SYNC 信号的主要方式包括：

- 外部输入信号到 SYNC 管脚；

- 通过控制总线 enable/disable SYNC\_POL\_INV bit；

- 通过配置 R30 寄存器；

- 当 En\_SYNC\_Auto = 1 时，配置寄存器 R0 ~ R5；

Figure 10 SYNC 信号的内部框图

## 5 通道隔离

实际应用中，时钟芯片输出到各个功能模块电路的时钟频率可能完全不同。如果时钟频率之间的隔离不是很好，发生时钟频率之间的相互泄漏，可能导致各个功能模块功能或性能的下降；比方说，如果 ADC 的时钟泄漏到 DAC 的时钟上，则最终在 DAC 的输出可能造成特定频点的固定杂散，使得设备的发射满足不了系统的发射频谱模板。

下表是 LMK0480X 芯片各个通道间的相互隔离，测试频率是 322MHz。其中绿色是指在通道之间

的隔离在 90dBc 以上；红色是指通道间的隔离在 70dBc 以下，黄色通道之间的隔离介于两者之间。

|          |      | Observe Channel (CLKoutX) |        |        |        |        |        |        |        |        |        |        |        |

|----------|------|---------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

|          |      | 0                         | 1      | 2      | 3      | 4      | 5      | 6      | 7      | 8      | 9      | 10     | 11     |

| Stimulus | 0    |                           |        | 89.05  | 92.86  | 95.06  | 88.05  | 85.9   | 86.75  | 88.26  | 88.95  | 80.45  | 76.35  |

|          | 1    |                           |        | -75.25 | -76.85 | -77.95 | -77.5  | -83.9  | -78.15 | -87.9  | -79.6  | -76.75 | -79.5  |

|          | 2    | -85.65                    | -78.15 |        |        | -85.25 | -85.5  | -78.8  | -86.55 | -79.85 | -79.7  | -79.6  | -79.2  |

|          | 3    | 89.2                      | 87.6   |        |        | 68.85  | 81.3   | 88.85  | 90.85  | 88.85  | 87.8   | 91.65  | 89.75  |

|          | 4    | -75.5                     | -73.7  | -77    | -65.1  |        |        | -81.35 | -79.5  | -71.2  | -89.25 | -75.1  | -73.35 |

|          | 5    | -78.95                    | -81.25 | -70.6  | -71.2  |        |        | -75.05 | -75.75 | -76.9  | -75.75 | -77.3  | -79.65 |

|          | 6    | -89.05                    | -92.85 | -87.25 | -84.95 | -80.95 | -87    |        |        | -74.3  | -80.5  | -83.15 | -86.15 |

|          | 7    | -92.25                    | -87.3  | -95.85 | -91.6  | -96.75 | -90.4  |        |        | -57.8  | -86.85 | -87.05 | -84.85 |

|          | 8    | -88.05                    | -92.2  | -91.8  | -89.25 | -89.85 | -86.75 | -66.65 | -55.15 |        |        | -83.65 | -84.9  |

|          | 9    | -92.7                     | -92.65 | -96.0  | -95.45 | -97.7  | -92.8  | -73.05 | -65.05 |        |        | -65.15 | -71.55 |

|          | 10   | -80.8                     | -82.85 | -94.5  | -97.1  | -98.2  | -91.8  | -92.8  | -90.7  | -87.5  | -84.45 |        |        |

|          | 11   | -70.35                    | -92.4  | -91.05 | -90    | -95.0  | -98.4  | -98.15 | -95.05 | -70.55 | -74.6  |        |        |

|          | OSC0 | 104.4                     | 97.9   | 94.05  | 93.3   | 104.5  | 81.85  | 97.85  | 95.8   | 98.35  | 95.7   | 105.05 | 102.95 |

|          | OSC1 | -84.65                    | -81.6  | -86.5  | -85.3  | -89.7  | -82.05 | -91.05 | -92.35 | -84.15 | -83.75 | -97.9  | -94.6  |

Table 3 LMK0480X 各个通道间的隔离

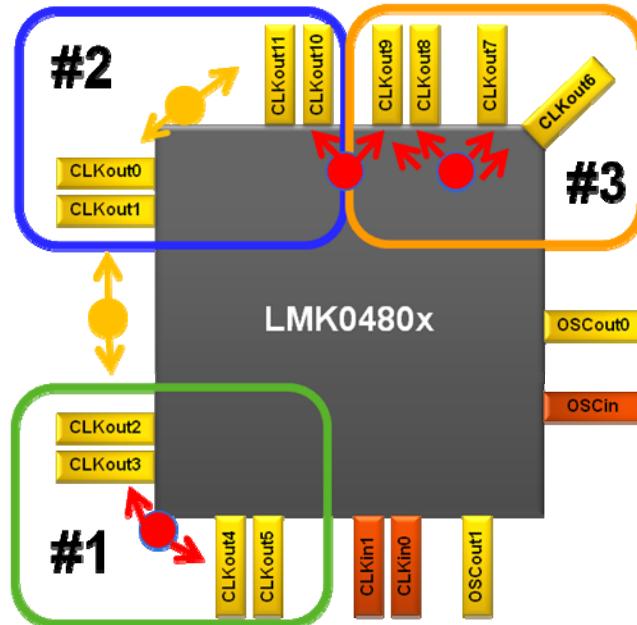

根据上面表格的测试结果，结合 LMK0480X 的管脚分布，为了得到最佳的通道隔离性能，推荐以

下的管脚分配原则：对于那些对隔离敏感的时钟，比方 ADC/DAC/LO 时钟，建议选择#1 中的输出

通道；对于隔离次敏感的时钟，比方 SERDES 时钟，建议选择#2 中的输出通道；对于数字芯片，如

CPU/FPGA/DSP，可以选择#3 中的输出通道，因为这类时钟对于隔离一般要求不高。

Figure 11 LMK0480X 的管脚分配

另外，对于提高芯片的隔离，在电路应用设计中，还可以应用以下几种方法：

- 相同的输出频率尽量要使用靠近的输出管脚，供电电路也可以共享；

- 尽可能多的使用 LVDS 输出格式，不仅因为 LVDS 的耗电最小，同时 LVDS 输出时钟对别的通道的干扰也最小；

- 当需要使用 LVCMS 输出时，尽可能不要使用 Norm/Norm 这种输出格式，这个因为当输出选择 Norm/Norm 时，两路单端输出同相，对供电电流的瞬态要求很高，造成了供电电源纹波的恶化，同时也对别的通道造成干扰。建议使用 Norm/Inv 或者 LVPECL 差分线中的一端作为单端使用。

## 6 器件的供电

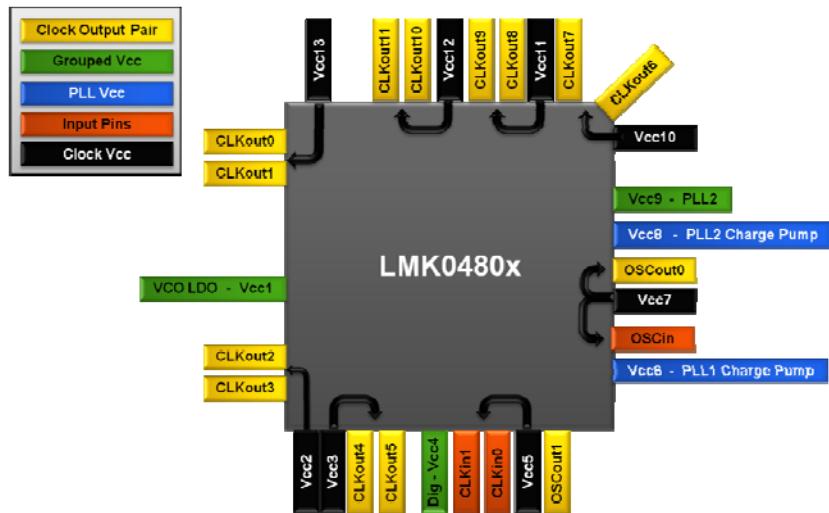

LMK0480X 芯片只需单 3.3V 供电，并且内部集成了 LDO，所以对于供电电源芯片的 LDO 要求并不苛刻。但良好的供电设计，尤其是如何整合整个芯片的去耦设计，对于芯片的最终性能起着重要的作用。LMK0480X 的供电管脚分布如下，主要分为输入时钟供电，输出时钟供电，内部 VCO 供电以及 charge pump 供电。

- VCC6/VCC8 给 PLL1 和 PLL2 的 charge pump 供电，需要独立的去耦电路；

- 其他输出管脚的供电电路，根据输出频率的不同，整合相同输出频率的管脚共享去耦电路，建议每路供电增加独立的瓷珠，隔离噪声；

- 一般不建议在瓷珠和供电管脚之间增加去耦电容，防止将地面的噪声重新耦合到其它供电管脚；但输出频率小于 10MHz 或使用 LVCMSO Norm/Normal 时除外。

## 7 结论

LMK0480X 是一颗高集成度的模拟锁相环芯片，由于优越的相噪和隔离度性能、同时增加了许多独特的功能，如高精度的 holdover、数字和模拟时延调整等，可以广泛而灵活地应用在对时钟指标规格要求较高的场景。通过本文对 LMK0480X 主要功能的介绍，总结了这些重要功能在实际应用中需要注意的细节。通过这些完善的设计，可以更好的应用 LMK0480X，使得 LMK0480X 达到最佳性能，同时保证电路设计的可靠性。

## 8 参考资料

LMK04800 datasheet

LMK0480X training material, Timothy Toroni, 2011.

## 重要声明

德州仪器(TI) 及其下属子公司有权根据 **JESD46** 最新标准, 对所提供的产品和服务进行更正、修改、增强、改进或其它更改, 并有权根据 **JESD48** 最新标准中止提供任何产品和服务。客户在下订单前应获取最新的相关信息, 并验证这些信息是否完整且是最新的。所有产品的销售都遵循在订单确认时所提供的TI 销售条款与条件。

TI 保证其所销售的组件的性能符合产品销售时 TI 半导体产品销售条件与条款的适用规范。仅在 TI 保证的范围内, 且 TI 认为有必要时才会使用测试或其它质量控制技术。除非适用法律做出了硬性规定, 否则没有必要对每种组件的所有参数进行测试。

TI 对应用帮助或客户产品设计不承担任何义务。客户应对其使用 TI 组件的产品和应用自行负责。为尽量减小与客户产品和应用相关的风险, 客户应提供充分的设计与操作安全措施。

TI 不对任何 TI 专利权、版权、屏蔽作品权或其它与使用了 TI 组件或服务的组合设备、机器或流程相关的 TI 知识产权中授予的直接或隐含权限作出任何保证或解释。TI 所发布的与第三方产品或服务有关的信息, 不能构成从 TI 获得使用这些产品或服务的许可、授权、或认可。使用此类信息可能需要获得第三方的专利权或其它知识产权方面的许可, 或是 TI 的专利权或其它知识产权方面的许可。

对于 TI 的产品手册或数据表中 TI 信息的重要部分, 仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况下才允许进行复制。TI 对此类篡改过的文件不承担任何责任或义务。复制第三方的信息可能需要服从额外的限制条件。

在转售 TI 组件或服务时, 如果对该组件或服务参数的陈述与 TI 标明的参数相比存在差异或虚假成分, 则会失去相关 TI 组件或服务的所有明示或暗示授权, 且这是不正当的、欺诈性商业行为。TI 对任何此类虚假陈述均不承担任何责任或义务。

客户认可并同意, 尽管任何应用相关信息或支持仍可能由 TI 提供, 但他们将独自负责满足与其产品及在其应用中使用 TI 产品相关的所有法律、法规和安全相关要求。客户声明并同意, 他们具备制定与实施安全措施所需的全部专业技术和知识, 可预见故障的危险后果、监测故障及其后果、降低有可能造成人身伤害的故障的发生机率并采取适当的补救措施。客户将全额赔偿因在此类安全关键应用中使用任何 TI 组件而对 TI 及其代理造成任何损失。

在某些场合中, 为了推进安全相关应用有可能对 TI 组件进行特别的促销。TI 的目标是利用此类组件帮助客户设计和创立其特有的可满足适用的功能安全性标准和要求的终端产品解决方案。尽管如此, 此类组件仍然服从这些条款。

TI 组件未获得用于 **FDA Class III** (或类似的生命攸关医疗设备) 的授权许可, 除非各方授权官员已经达成了专门管控此类使用的特别协议。

只有那些 TI 特别注明属于军用等级或“增强型塑料”的 TI 组件才是设计或专门用于军事/航空应用或环境的。购买者认可并同意, 对并非指定面向军事或航空航天用途的 TI 组件进行军事或航空航天方面的应用, 其风险由客户单独承担, 并且由客户独自负责满足与此类使用相关的所有法律和法规要求。

TI 已明确指定符合 **ISO/TS16949** 要求的产品, 这些产品主要用于汽车。在任何情况下, 因使用非指定产品而无法达到 **ISO/TS16949** 要求, TI 不承担任何责任。

| 产品            | 应用                                                                                         |

|---------------|--------------------------------------------------------------------------------------------|

| 数字音频          | <a href="http://www.ti.com.cn/audio">www.ti.com.cn/audio</a>                               |

| 放大器和线性器件      | <a href="http://www.ti.com.cn/amplifiers">www.ti.com.cn/amplifiers</a>                     |

| 数据转换器         | <a href="http://www.ti.com.cn/dataconverters">www.ti.com.cn/dataconverters</a>             |

| DLP® 产品       | <a href="http://www.dlp.com">www.dlp.com</a>                                               |

| DSP - 数字信号处理器 | <a href="http://www.ti.com.cn/dsp">www.ti.com.cn/dsp</a>                                   |

| 时钟和计时器        | <a href="http://www.ti.com.cn/clockandtimers">www.ti.com.cn/clockandtimers</a>             |

| 接口            | <a href="http://www.ti.com.cn/interface">www.ti.com.cn/interface</a>                       |

| 逻辑            | <a href="http://www.ti.com.cn/logic">www.ti.com.cn/logic</a>                               |

| 电源管理          | <a href="http://www.ti.com.cn/power">www.ti.com.cn/power</a>                               |

| 微控制器 (MCU)    | <a href="http://www.ti.com.cn/microcontrollers">www.ti.com.cn/microcontrollers</a>         |

| RFID 系统       | <a href="http://www.ti.com.cn/rfidsys">www.ti.com.cn/rfidsys</a>                           |

| OMAP 应用处理器    | <a href="http://www.ti.com/omap">www.ti.com/omap</a>                                       |

| 无线连通性         | <a href="http://www.ti.com.cn/wirelessconnectivity">www.ti.com.cn/wirelessconnectivity</a> |

|               | 德州仪器在线技术支持社区 <a href="http://www.deyisupport.com">www.deyisupport.com</a>                  |

邮寄地址: 上海市浦东新区世纪大道 1568 号, 中建大厦 32 楼 邮政编码: 200122

Copyright © 2013 德州仪器 半导体技术 (上海) 有限公司